Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 14x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 44-QFN (8x8)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f884-e-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 4: 44-PIN QFN ALLOCATION TABLE (PIC16F884/887)

| IADL       |            |           |             | CATION TAL      | (        |             | ·· <i>,</i> |           |         |                 |

|------------|------------|-----------|-------------|-----------------|----------|-------------|-------------|-----------|---------|-----------------|

| O/I        | 44-Pin QFN | Analog    | Comparators | Timers          | ECCP     | EUSART      | MSSP        | Interrupt | Pull-up | Basic           |

| RA0        | 19         | AN0/ULPWU | C12IN0-     | _               | _        | _           | _           | _         | _       | _               |

| RA1        | 20         | AN1       | C12IN1-     | _               | _        | _           | _           | _         | _       | _               |

| RA2        | 21         | AN2       | C2IN+       | _               | _        | _           | _           | _         | _       | VREF-/CVREF     |

| RA3        | 22         | AN3       | C1IN+       | _               | _        | _           | _           | _         | _       | VREF+           |

| RA4        | 23         | _         | C10UT       | T0CKI           | _        | _           | _           | _         | _       | _               |

| RA5        | 24         | AN4       | C2OUT       | _               | _        | _           | SS          | _         | _       | _               |

| RA6        | 33         | _         | _           | _               | _        | _           | _           | _         | _       | OSC2/CLKOUT     |

| RA7        | 32         | _         | _           | _               | _        | _           | _           | _         |         | OSC1/CLKIN      |

| RB0        | 9          | AN12      | _           | _               | _        | _           | _           | IOC/INT   | Υ       | —               |

| RB1        | 10         | AN10      | C12IN3-     | _               | _        | _           | _           | IOC       | Y       | _               |

| RB2        | 11         | AN8       | _           | _               | _        | _           | _           | IOC       | Y       | _               |

| RB3        | 12         | AN9       | C12IN2-     |                 | _        | _           |             | IOC       | Y       | PGM             |

| RB4        | 14         | AN11      | _           | _               | _        | _           | _           | IOC       | Y       |                 |

| RB5        | 15         | AN13      | _           | T1G             |          |             |             | IOC       | Y       | _               |

| RB6        | 16         | — —       |             | -               | _        |             |             | IOC       | Y       | ICSPCLK         |

| RB7        | 17         | _         |             | _               | _        |             |             | IOC       | Y       | ICSPDAT         |

| RC0        | 34         |           |             | T10S0/T1CKI     | _        | <del></del> |             | 100       | ı       | ICGI DAI        |

| RC1        | 35         | _         |             | T10SI           | CCP2     | _           | _           | _         |         | _               |

| RC2        | 36         | _         |             | 11031           | CCP1/P1A | _           | _           | _         |         | _               |

|            |            | _         | <u> </u>    | _               |          | _           | SCK/SCL     | _         |         | _               |

| RC3        | 37<br>42   | _         | _           |                 | _        | _           | SDI/SDA     | _         |         | _               |

| RC4<br>RC5 | 42         | _         |             | _               | _        |             | SDO         | _         | _       |                 |

|            |            | _         |             |                 | _        |             | 300         | _         |         | _               |

| RC6        | 44         | _         |             | _               | _        | TX/CK       | _           | _         |         | _               |

| RC7        | 1          | _         |             | _               |          | RX/DT       |             | _         | _       | _               |

| RD0        | 38         | _         | _           | _               | _        | _           | _           | _         |         | _               |

| RD1        | 39         | _         | _           | <del>-</del>    | _        | _           |             | _         |         | _               |

| RD2        | 40         | _         | _           | _               | _        | _           | _           | _         |         | _               |

| RD3        | 41         | _         |             | _               | _        | _           | _           | _         |         | _               |

| RD4        | 2          | _         | _           | _               | _        |             | _           | _         | _       | _               |

| RD5        | 3          | _         |             | _               | P1B      | _           | _           | _         | _       | _               |

| RD6        | 4          | _         | _           | _               | P1C      | _           | _           | _         |         | _               |

| RD7        | 5          |           |             | _               | P1D      | _           | _           | _         | _       | _               |

| RE0        | 25         | AN5       | _           | <del>-</del>    | _        | _           | _           | _         |         | _               |

| RE1        | 26         | AN6       |             | _               | _        | _           | _           | _         | _       | _               |

| RE2        | 27         | AN7       |             | _               | _        | _           | _           |           |         |                 |

| RE3        | 18         | _         |             | _               | _        |             | _           | _         | Y(1)    | MCLR/VPP        |

| _          | 7          | _         | _           | _               | _        | _           | _           | _         | _       | VDD             |

|            | 8          | _         |             | _               | _        |             | _           | _         |         | VDD             |

| _          | 28         | _         | _           | _               | _        | _           | _           | _         | _       | VDD             |

|            | 6          | _         |             | _               | _        | _           | _           | _         | _       | Vss             |

| _          | 30         | _         | _           | _               | _        | _           | _           | _         | -       | Vss             |

|            | 31         | _         |             | _               | _        |             | _           | _         | -       | Vss             |

|            | 13         | _         |             | _               | _        | _           | _           | _         | _       | NC (no connect) |

|            | 29         | _         |             |                 | _        |             | _           |           |         | NC (no connect) |

|            |            |           |             | mad MOLD sandia |          |             |             |           |         | ·               |

**Note 1:** Pull-up activated only with external  $\overline{\text{MCLR}}$  configuration.

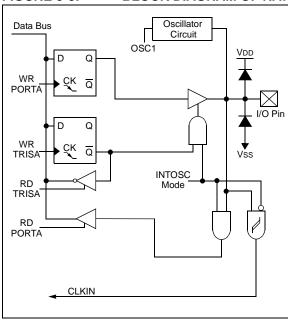

### 3.2.3.8 RA7/OSC1/CLKIN

Figure 3-8 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a crystal/resonator connection

- · a clock input

FIGURE 3-8: BLOCK DIAGRAM OF RA7

TABLE 3-1: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name       | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Register on Page |

|------------|--------|--------|--------|--------|--------|--------|---------|--------|------------------|

| ADCON0     | ADCS1  | ADCS0  | CHS3   | CHS2   | CHS1   | CHS0   | GO/DONE | ADON   | 104              |

| ANSEL      | ANS7   | ANS6   | ANS5   | ANS4   | ANS3   | ANS2   | ANS1    | ANS0   | 41               |

| CM1CON0    | C10N   | C1OUT  | C10E   | C1POL  |        | C1R    | C1CH1   | C1CH0  | 89               |

| CM2CON0    | C2ON   | C2OUT  | C2OE   | C2POL  | I      | C2R    | C2CH1   | C2CH0  | 90               |

| CM2CON1    | MC1OUT | MC2OUT | C1RSEL | C2RSEL | _      | _      | T1GSS   | C2SYNC | 92               |

| PCON       | _      | _      | ULPWUE | SBOREN | _      | _      | POR     | BOR    | 37               |

| OPTION_REG | RBPU   | INTEDG | T0CS   | T0SE   | PSA    | PS2    | PS1     | PS0    | 31               |

| PORTA      | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1     | RA0    | 40               |

| SSPCON     | WCOL   | SSPOV  | SSPEN  | CKP    | SSPM3  | SSPM2  | SSPM1   | SSPM0  | 177              |

| TRISA      | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1  | TRISA0 | 40               |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

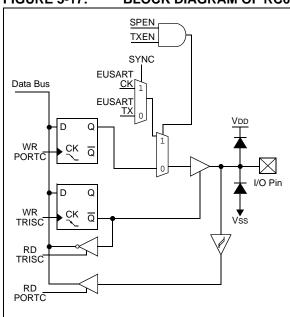

### 3.5.7 RC6/TX/CK

Figure 3-17 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an asynchronous serial output

- a synchronous clock I/O

### FIGURE 3-17: BLOCK DIAGRAM OF RC6

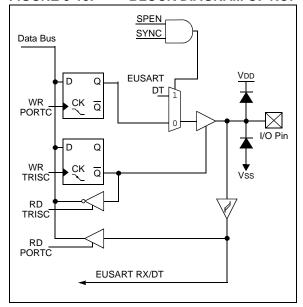

#### 3.5.8 RC7/RX/DT

Figure 3-18 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- · an asynchronous serial input

- a synchronous serial data I/O

FIGURE 3-18: BLOCK DIAGRAM OF RC7

TABLE 3-3: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

|         |        | _      |         |         | _       |        |        |        |                     |

|---------|--------|--------|---------|---------|---------|--------|--------|--------|---------------------|

| Name    | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

| CCP1CON | P1M1   | P1M0   | DC1B1   | DC1B0   | CCP1M3  | CCP1M2 | CCP1M1 | CCP1M0 | 122                 |

| CCP2CON | _      | _      | DC2B1   | DC2B0   | CCP2M3  | CCP2M2 | CCP2M1 | CCP2M0 | 123                 |

| PORTC   | RC7    | RC6    | RC5     | RC4     | RC3     | RC2    | RC1    | RC0    | 54                  |

| PSTRCON | _      | _      | _       | STRSYNC | STRD    | STRC   | STRB   | STRA   | 144                 |

| RCSTA   | SPEN   | RX9    | SREN    | CREN    | ADDEN   | FERR   | OERR   | RX9D   | 158                 |

| SSPCON  | WCOL   | SSPOV  | SSPEN   | CKP     | SSPM3   | SSPM2  | SSPM1  | SSPM0  | 177                 |

| T1CON   | T1GINV | TMR1GE | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 81                  |

| TRISC   | TRISC7 | TRISC6 | TRISC5  | TRISC4  | TRISC3  | TRISC2 | TRISC1 | TRISC0 | 54                  |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

### 3.6 PORTD and TRISD Registers

PORTD<sup>(1)</sup> is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISD (Register 3-12). Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 3-5 shows how to initialize PORTD.

Reading the PORTD register (Register 3-11) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

**Note 1:** PORTD is available on PIC16F884/887 only.

The TRISD register (Register 3-12) controls the PORTD pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISD register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### **EXAMPLE 3-5: INITIALIZING PORTD**

BANKSEL PORTD ;

CLRF PORTD ;Init PORTD

BANKSEL TRISD ;

MOVLW B'00001100' ;Set RD<3:2> as inputs

MOVWF TRISD ;and set RD<7:4,1:0>

;as outputs

### REGISTER 3-11: PORTD: PORTD REGISTER

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RD7   | RD6   | RD5   | RD4   | RD3   | RD2   | RD1   | RD0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 RD<7:0>: PORTD General Purpose I/O Pin bit

1 = Port pin is > VIH 0 = Port pin is < VIL

#### REGISTER 3-12: TRISD: PORTD TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 TRISD<7:0>: PORTD Tri-State Control bit

1 = PORTD pin configured as an input (tri-stated)

0 = PORTD pin configured as an output

### 4.6 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bit of the OSCCON register.

### 4.6.1 SYSTEM CLOCK SELECT (SCS) BIT

The System Clock Select (SCS) bit of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bit of the OSCCON register = 0, the system clock source is determined by configuration of the FOSC<2:0> bits in the Configuration Word Register 1 (CONFIG1).

- When the SCS bit of the OSCCON register = 1, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<2:0> bits of the OSCCON register. After a Reset, the SCS bit of the OSCCON register is always cleared.

Note:

Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS bit of the OSCCON register. The user can monitor the OSTS bit of the OSCCON register to determine the current system clock source.

# 4.6.2 OSCILLATOR START-UP TIME-OUT STATUS (OSTS) BIT

The Oscillator Start-up Time-out Status (OSTS) bit of the OSCCON register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word Register 1 (CONFIG1), or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes.

### 4.7 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device.

This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC as the clock source and go back to Sleep without waiting for the primary oscillator to become stable.

Note: Executing a SLEEP instruction will abort the oscillator start-up time and will cause the OSTS bit of the OSCCON register to remain clear.

When the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) is enabled (see Section 4.4.1 "Oscillator Start-up Timer (OST)"). The OST will suspend program execution until 1024 oscillations are counted. Two-Speed Start-up mode minimizes the delay in code execution by operating from the internal oscillator as the OST is counting. When the OST count reaches 1024 and the OSTS bit of the OSCCON register is set, program execution switches to the external oscillator.

# 4.7.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Word Register 1) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 0.

- FOSC<2:0> bits in the Configuration Word Register 1 (CONFIG1) configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- · Wake-up from Sleep.

If the external clock oscillator is configured to be anything other than LP, XT or HS mode, then Two-speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

### **REGISTER DEFINITIONS: OPTION REGISTER**

REGISTER 5-1: OPTION\_REG: OPTION REGISTER

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       | •     |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 RBPU: PORTB Pull-up Enable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual PORT latch values

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of INT pin0 = Interrupt on falling edge of INT pin

bit 5 TOCS: TMR0 Clock Source Select bit

1 = Transition on T0CKI pin

0 = Internal instruction cycle clock (Fosc/4)

bit 4 T0SE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on TOCKI pin

0 = Increment on low-to-high transition on T0CKI pin

bit 3 **PSA:** Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 **PS<2:0>:** Prescaler Rate Select bits

| BIT VALUE | TMR0 RATE | WDT RATE |

|-----------|-----------|----------|

| 000       | 1:2       | 1:1      |

| 001       | 1:4       | 1:2      |

| 010       | 1:8       | 1:4      |

| 011       | 1:16      | 1:8      |

| 100       | 1:32      | 1:16     |

| 101       | 1:64      | 1:32     |

| 110       | 1:128     | 1:64     |

| 111       | 1:256     | 1:128    |

Note 1: A dedicated 16-bit WDT postscaler is available. See Section 14.5 "Watchdog Timer (WDT)" for more information.

TABLE 5-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMERO

| Name       | Bit 7    | Bit 6                  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register on Page |

|------------|----------|------------------------|--------|--------|--------|--------|--------|--------|------------------|

| TMR0       | Timer0 M | Timer0 Module Register |        |        |        |        |        |        | 75               |

| INTCON     | GIE      | PEIE                   | TOIE   | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 32               |

| OPTION_REG | RBPU     | INTEDG                 | T0CS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 77               |

| TRISA      | TRISA7   | TRISA6                 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 40               |

**Legend:** -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Timer0 module.

### 8.10 Comparator Voltage Reference

The comparator voltage reference module provides an internally generated voltage reference for the comparators. The following features are available:

- Independent from Comparator operation

- Two 16-level voltage ranges

- · Output clamped to Vss

- · Ratiometric with VDD

- Fixed Reference (0.6V)

The VRCON register (Register 8-5) controls the voltage reference module shown in Figure 8-8.

The voltage source is selectable through both ends of the 16 connection resistor ladder network. Bit VRSS of the VRCON register selects either the internal or external voltage source.

The PIC16F882/883/884/886/887 allows the CVREF signal to be output to the RA2 pin of PORTA under certain configurations only. For more details, see Figure 8-9.

### 8.10.1 INDEPENDENT OPERATION

The comparator voltage reference is independent of the comparator configuration. Setting the VREN bit of the VRCON register will enable the voltage reference.

#### 8.10.2 OUTPUT VOLTAGE SELECTION

The CVREF voltage reference has two ranges with 16 voltage levels in each range. Range selection is controlled by the VRR bit of the VRCON register. The 16 levels are set with the VR<3:0> bits of the VRCON register.

The CVREF output voltage is determined by the following equations:

### **EQUATION 8-1: CVREF OUTPUT VOLTAGE**

```

VRR = 1 (low range):

CVREF = (VR < 3:0 > /24) \times VLADDER

VRR = 0 (high range):

CVREF = (VLADDER/4) + (VR < 3:0 > \times VLADDER/32)

VLADDER = VDD or ([VREF+] - [VREF-]) or VREF+

```

The full range of VSS to VDD cannot be realized due to the construction of the module. See Figure 8-8.

#### 8.10.3 OUTPUT CLAMPED TO Vss

The CVREF output voltage can be set to Vss with no power consumption by clearing the FVREN bit of the VRCON register.

This allows the comparator to detect a zero-crossing while not consuming additional CVREF module current.

ote: Depending on the application, additional components may be required for a zero cross circuit. Reference TB3013, "Using the ESD Parasitic Diodes on Mixed Signal Microcontrollers" (DS93013), for more information.

### 8.10.4 OUTPUT RATIOMETRIC TO VDD

The comparator voltage reference is VDD derived and therefore, the CVREF output changes with fluctuations in VDD. The tested absolute accuracy of the Comparator Voltage Reference can be found in **Section 17.0** "Electrical Specifications".

#### 8.10.5 FIXED VOLTAGE REFERENCE

The Fixed Voltage Reference is independent of VDD, with a nominal output voltage of 0.6V. This reference can be enabled by setting the FVREN bit of the SRCON register to '1'. This reference is always enabled when the HFINTOSC oscillator is active.

## 8.10.6 FIXED VOLTAGE REFERENCE STABILIZATION PERIOD

When the Fixed Voltage Reference module is enabled, it will require some time for the reference and its amplifier circuits to stabilize. The user program must include a small delay routine to allow the module to settle. See **Section 17.0** "Electrical Specifications" for the minimum delay requirement.

# 8.10.7 VOLTAGE REFERENCE SELECTION

Multiplexers on the output of the voltage reference module enable selection of either the CVREF or Fixed Voltage Reference for use by the comparators.

Setting the C1RSEL bit of the CM2CON1 register enables current to flow in the CVREF voltage divider and selects the CVREF voltage for use by C1. Clearing the C1RSEL bit selects the fixed voltage for use by C1.

Setting the C2RSEL bit of the CM2CON1 register enables current to flow in the CVREF voltage divider and selects the CVREF voltage for use by C2. Clearing the C2RSEL bit selects the fixed voltage for use by C2.

When both the C1RSEL and C2RSEL bits are cleared, current flow in the CVREF voltage divider is disabled minimizing the power drain of the voltage reference peripheral.

DS40001291H-page 132

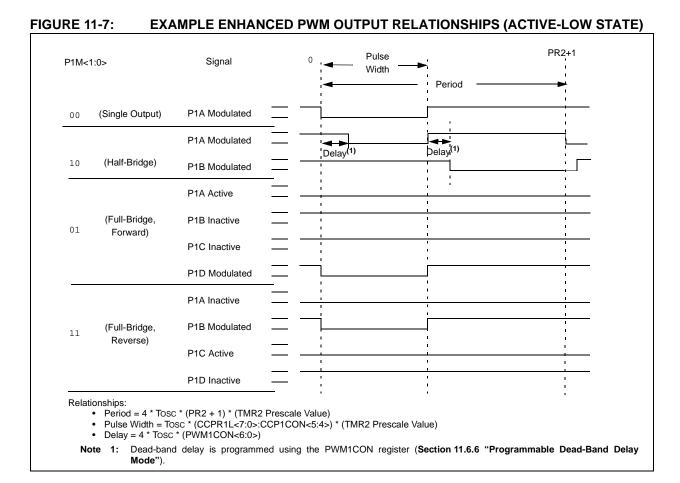

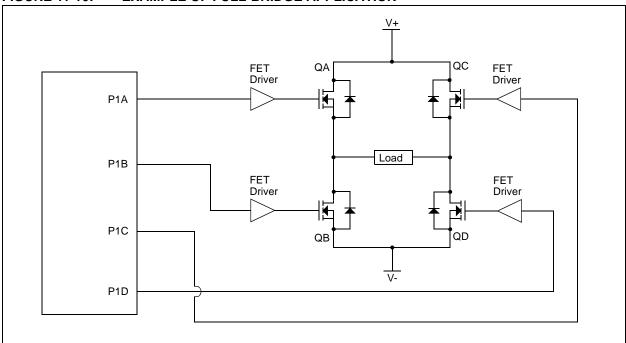

### 11.6.2 FULL-BRIDGE MODE

In Full-Bridge mode, all four pins are used as outputs. An example of Full-Bridge application is shown in Figure 11-10.

In the Forward mode, pin CCP1/P1A is driven to its active state, pin P1D is modulated, while P1B and P1C will be driven to their inactive state as shown in Figure 11-11.

In the Reverse mode, P1C is driven to its active state, pin P1B is modulated, while P1A and P1D will be driven to their inactive state as shown Figure 11-11.

P1A, P1B, P1C and P1D outputs are multiplexed with the PORT data latches. The associated TRIS bits must be cleared to configure the P1A, P1B, P1C and P1D pins as outputs.

FIGURE 11-10: EXAMPLE OF FULL-BRIDGE APPLICATION

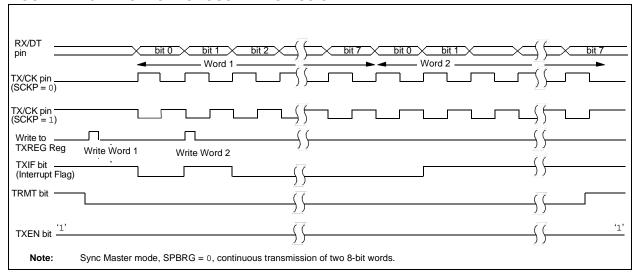

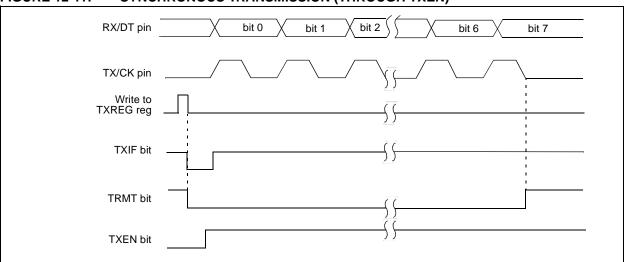

FIGURE 12-10: SYNCHRONOUS TRANSMISSION

FIGURE 12-11: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

TABLE 12-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name    | Bit 7                         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register on Page |

|---------|-------------------------------|--------|--------|--------|--------|--------|--------|--------|------------------|

| BAUDCTL | ABDOVF                        | RCIDL  | _      | SCKP   | BRG16  | _      | WUE    | ABDEN  | 159              |

| INTCON  | GIE                           | PEIE   | T0IE   | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 32               |

| PIE1    | _                             | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 33               |

| PIR1    | _                             | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 35               |

| RCREG   | EUSART Receive Data Register  |        |        |        |        |        |        |        |                  |

| RCSTA   | SPEN                          | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 158              |

| SPBRG   | BRG7                          | BRG6   | BRG5   | BRG4   | BRG3   | BRG2   | BRG1   | BRG0   | 160              |

| SPBRGH  | BRG15                         | BRG14  | BRG13  | BRG12  | BRG11  | BRG10  | BRG9   | BRG8   | 160              |

| TRISC   | TRISC7                        | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 54               |

| TXREG   | EUSART Transmit Data Register |        |        |        |        |        |        |        |                  |

| TXSTA   | CSRC                          | TX9    | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 157              |

**Legend:** x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Transmission.

#### REGISTER 13-3: SSPCON2: SSP CONTROL REGISTER 2

| R/W-0 | R-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|---------|-------|-------|-------|-------|-------|-------|

| GCEN  | ACKSTAT | ACKDT | ACKEN | RCEN  | PEN   | RSEN  | SEN   |

| bit 7 |         |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 **GCEN:** General Call Enable bit (in I<sup>2</sup>C Slave mode only)

1 = Enable interrupt when a general call address (0000h) is received in the SSPSR

0 = General call address disabled

bit 6 ACKSTAT: Acknowledge Status bit (in I<sup>2</sup>C Master mode only)

In Master Transmit mode:

1 = Acknowledge was not received from slave

0 = Acknowledge was received from slave

bit 5 **ACKDT:** Acknowledge Data bit (in I<sup>2</sup>C Master mode only)

In Master Receive mode:

Value transmitted when the user initiates an Acknowledge sequence at the end of a receive

1 = Not Acknowledge

0 = Acknowledge

bit 4 **ACKEN:** Acknowledge Sequence Enable bit (in I<sup>2</sup>C Master mode only)

In Master Receive mode:

1 = Initiate Acknowledge sequence on SDA and SCL pins, and transmit ACKDT data bit. Automatically cleared by hardware.

0 = Acknowledge sequence idle

bit 3 RCEN: Receive Enable bit (in I<sup>2</sup>C Master mode only)

1 = Enables Receive mode for I<sup>2</sup>C

0 = Receive idle

bit 2 **PEN:** Stop Condition Enable bit (in I<sup>2</sup>C Master mode only)

SCK Release Control:

1 = Initiate Stop condition on SDA and SCL pins. Automatically cleared by hardware.

0 = Stop condition Idle

bit 1 RSEN: Repeated Start Condition Enabled bit (in I<sup>2</sup>C Master mode only)

1 = Initiate Repeated Start condition on SDA and SCL pins. Automatically cleared by hardware.

0 = Repeated Start condition Idle

bit 0 SEN: Start Condition Enabled bit (in I<sup>2</sup>C Master mode only)

In Master mode:

1 = Initiate Start condition on SDA and SCL pins. Automatically cleared by hardware.

0 = Start condition Idle

In Slave mode:

1 = Clock stretching is enabled for both slave transmit and slave receive (stretch enabled)

0 = Clock stretching is disabled

**Note 1:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the Idle mode, this bit may not be set (no spooling) and the SSPBUF may not be written (or writes to the SSPBUF are disabled).

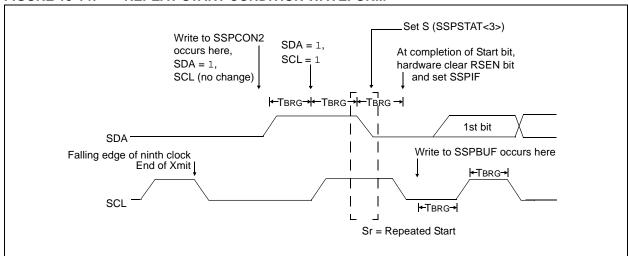

# 13.4.7 I<sup>2</sup>C™ MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2 register) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be de-asserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG, while SCL is high. Following this, the RSEN bit (SSPCON2 register) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit (SSPSTAT register) will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

**Note 1:** If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data "1".

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode), or eight bits of data (7-bit mode).

### 13.4.7.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur).

Note: Because queuing of events is not allowed, writing of the lower five bits of SSPCON2 is disabled until the Repeated Start condition is complete.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                         |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                                                                                                                             |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                     |

| Status Affected: | None                                                                                                                                                                                                                                                                                                           |

| Description:     | The contents of register 'f' are decremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.  If the result is '1', the next instruction is executed. If the result is '0', then a NOP is executed instead, making it a 2-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [ label ] INCFSZ f,d                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are incremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.  If the result is '1', the next instruction is executed. If the result is '0', a NOP is executed instead, making it a 2-cycle instruction. |  |  |  |  |  |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                        |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [label] GOTO k                                                                                                                                                              |  |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                        |  |  |  |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                             |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                        |  |  |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch. The 11-bit immediate value is loaded into PC bits <10:0>. The upper bits of PC are loaded from PCLATH<4:3>. GOTO is a 2-cycle instruction. |  |  |  |  |  |  |  |

| IORLW            | Inclusive OR literal with W                                                                                  |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] IORLW k                                                                                            |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                          |  |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow (W)$                                                                                 |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                            |  |  |  |  |  |  |

| Description:     | The contents of the W register are OR'ed with the 8-bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |  |

| INCF             | Increment f                                                                                                                                                    |  |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ label ] INCF f,d                                                                                                                                             |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                             |  |  |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                            |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                              |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are incremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |  |  |  |  |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                           |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ label ] IORWF f,d                                                                                                                                             |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                              |  |  |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                        |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |  |  |  |  |

| Description:     | Inclusive OR the W register with register 'f'. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |  |  |  |  |  |  |  |

| MOVF             | Move f                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ label ] MOVF f,d                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' is moved to a destination dependent upon the status of 'd'. If $d=0$ , destination is W register. If $d=1$ , the destination is file register 'f' itself. $d=1$ is useful to test a file register since status flag Z is affected. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|                  | After Instruction  W = value in FSR  register  Z = 1                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| MOVWF            | Move W to f                                |  |  |  |  |  |  |  |  |

|------------------|--------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [ label ] MOVWF f                          |  |  |  |  |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                        |  |  |  |  |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                      |  |  |  |  |  |  |  |  |

| Status Affected: | None                                       |  |  |  |  |  |  |  |  |

| Description:     | Move data from W register to register 'f'. |  |  |  |  |  |  |  |  |

| Words:           | 1                                          |  |  |  |  |  |  |  |  |

| Cycles:          | 1                                          |  |  |  |  |  |  |  |  |

| Example:         | MOVW OPTION<br>F                           |  |  |  |  |  |  |  |  |

|                  | Before Instruction                         |  |  |  |  |  |  |  |  |

|                  | OPTION = 0xFF                              |  |  |  |  |  |  |  |  |

|                  | W = 0x4F                                   |  |  |  |  |  |  |  |  |

|                  | After Instruction                          |  |  |  |  |  |  |  |  |

|                  | OPTION = 0x4F                              |  |  |  |  |  |  |  |  |

|                  | W = 0x4F                                   |  |  |  |  |  |  |  |  |

|                  |                                            |  |  |  |  |  |  |  |  |

| MOVLW            | Move literal to W                                                                         |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ label ] MOVLW k                                                                         |  |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                       |  |  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                       |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                      |  |  |  |  |  |  |  |

| Description:     | The 8-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                         |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                         |  |  |  |  |  |  |  |

| Example:         | MOVLW 0x5A                                                                                |  |  |  |  |  |  |  |

|                  | After Instruction $W = 0x5A$                                                              |  |  |  |  |  |  |  |

| NOP              | No Operation  |  |  |  |  |

|------------------|---------------|--|--|--|--|

| Syntax:          | [ label ] NOP |  |  |  |  |

| Operands:        | None          |  |  |  |  |

| Operation:       | No operation  |  |  |  |  |

| Status Affected: | None          |  |  |  |  |

| Description:     | No operation. |  |  |  |  |

| Words:           | 1             |  |  |  |  |

| Cycles:          | 1             |  |  |  |  |

| Example:         | NOP           |  |  |  |  |

|                  |               |  |  |  |  |

|                  |               |  |  |  |  |

### 17.4 DC Characteristics: PIC16F882/883/884/886/887-E (Extended)

| DC CHA | RACTERISTICS                 | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for extended |      |      |         |     |                                               |  |  |  |

|--------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|---------|-----|-----------------------------------------------|--|--|--|

| Param  | Davies Characteristics       | Min                                                                                                                                                        | T 4  | Max  | l luita |     | Conditions                                    |  |  |  |

| No.    | Device Characteristics       | Min.                                                                                                                                                       | Тур† | Max. | Units   | VDD | Note                                          |  |  |  |

| D020E  | Power-down Base              | _                                                                                                                                                          | 0.05 | 9    | μА      | 2.0 | WDT, BOR, Comparators, VREF and               |  |  |  |

|        | Current (IPD) <sup>(2)</sup> | _                                                                                                                                                          | 0.15 | 11   | μА      | 3.0 | T1OSC disabled                                |  |  |  |

|        |                              | _                                                                                                                                                          | 0.35 | 15   | μА      | 5.0 | ]                                             |  |  |  |

| D021E  |                              | _                                                                                                                                                          | 1    | 28   | μА      | 2.0 | WDT Current <sup>(1)</sup>                    |  |  |  |

|        |                              | _                                                                                                                                                          | 2    | 30   | μΑ      | 3.0 |                                               |  |  |  |

|        |                              | _                                                                                                                                                          | 3    | 35   | μΑ      | 5.0 |                                               |  |  |  |

| D022E  |                              | _                                                                                                                                                          | 42   | 65   | μΑ      | 3.0 | BOR Current <sup>(1)</sup>                    |  |  |  |

|        |                              |                                                                                                                                                            | 85   | 127  | μΑ      | 5.0 |                                               |  |  |  |

| D023E  |                              |                                                                                                                                                            | 32   | 45   | μΑ      | 2.0 | Comparator Current <sup>(1)</sup> , both      |  |  |  |

|        |                              | _                                                                                                                                                          | 60   | 78   | μΑ      | 3.0 | comparators enabled                           |  |  |  |

|        |                              | _                                                                                                                                                          | 120  | 160  | μΑ      | 5.0 |                                               |  |  |  |

| D024E  |                              |                                                                                                                                                            | 30   | 70   | μΑ      | 2.0 | CVREF Current <sup>(1)</sup> (high range)     |  |  |  |

|        |                              |                                                                                                                                                            | 45   | 90   | μΑ      | 3.0 |                                               |  |  |  |

|        |                              | _                                                                                                                                                          | 75   | 120  | μА      | 5.0 |                                               |  |  |  |

| D025E* |                              |                                                                                                                                                            | 39   | 91   | μΑ      | 2.0 | CVREF Current <sup>(1)</sup> (low range)      |  |  |  |

|        |                              |                                                                                                                                                            | 59   | 117  | μΑ      | 3.0 |                                               |  |  |  |

|        |                              |                                                                                                                                                            | 98   | 156  | μΑ      | 5.0 |                                               |  |  |  |

| D026E  |                              |                                                                                                                                                            | 3.5  | 18   | μΑ      | 2.0 | T1OSC Current <sup>(1)</sup> , 32.768 kHz     |  |  |  |

|        |                              |                                                                                                                                                            | 4.0  | 21   | μΑ      | 3.0 |                                               |  |  |  |

|        |                              |                                                                                                                                                            | 5.0  | 24   | μΑ      | 5.0 |                                               |  |  |  |

| D027E  |                              |                                                                                                                                                            | 0.30 | 12   | μΑ      | 3.0 | A/D Current <sup>(1)</sup> , no conversion in |  |  |  |

|        |                              |                                                                                                                                                            | 0.36 | 16   | μΑ      | 5.0 | progress                                      |  |  |  |

| D028E  |                              |                                                                                                                                                            | 90   | 130  | μΑ      | 3.0 | VP6 Reference Current                         |  |  |  |

|        |                              | _                                                                                                                                                          | 125  | 170  | μΑ      | 5.0 |                                               |  |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

- **Note 1:** The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral  $\Delta$  current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

- 2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### 17.8 AC Characteristics: PIC16F882/883/884/886/887 (Industrial, Extended)

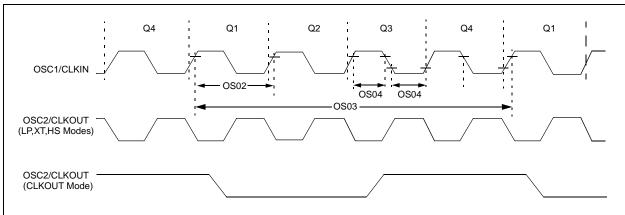

FIGURE 17-4: CLOCK TIMING

TABLE 17-1: CLOCK OSCILLATOR TIMING REQUIREMENTS

Standard Operating Conditions (unless otherwise stated) Operating temperature -40°C  $\leq$  TA  $\leq$  +125°C **Param** Characteristic Units Sym. Min. Typ† Max. **Conditions** No. External CLKIN Frequency(1) **OS01** Fosc DC 37 kHz LP Oscillator mode DC 4 MHz XT Oscillator mode DC 20 MHz HS Oscillator mode DC 20 EC Oscillator mode MHz Oscillator Frequency(1) 32.768 kHz LP Oscillator mode 0.1 4 MHz XT Oscillator mode 1 20 MHz HS Oscillator mode DC 4 MHz RC Oscillator mode OS02 External CLKIN Period<sup>(1)</sup> Tosc 27 LP Oscillator mode XT Oscillator mode 250 ns 50 HS Oscillator mode ns 50 EC Oscillator mode ns Oscillator Period<sup>(1)</sup> 30.5 LP Oscillator mode μS 250 10,000 XT Oscillator mode ns 1.000 HS Oscillator mode 50 ns 250 RC Oscillator mode ns Instruction Cycle Time(1) OS03 200 DC Tcy = 4/Fosc TCY TCY ns OS04\* External CLKIN High. TosH. 2 LP oscillator μS TosL External CLKIN Low 100 ns XT oscillator 20 ns HS oscillator OS05<sup>3</sup> External CLKIN Rise, LP oscillator TosR, 0 ns External CLKIN Fall TosE 0 XT oscillator ns ns HS oscillator

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### **TABLE 17-2: OSCILLATOR PARAMETERS**

Standard Operating Conditions (unless otherwise stated)

Operating Temperature -40°C ≤ TA ≤ +125°C

Param Sym Characteristic Freq. Min Tynt Max Units Conditions

| Param<br>No. | Sym.                              | Characteristic                                         | Freq.<br>Tolerance | Min. | Typ† | Max. | Units | Conditions                                                                                                                                       |

|--------------|-----------------------------------|--------------------------------------------------------|--------------------|------|------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| OS06         | TWARM                             | Internal Oscillator Switch when running <sup>(3)</sup> | _                  | _    | _    | 2    | Tosc  | Slowest clock                                                                                                                                    |

| OS07         | Tsc                               | Fail-Safe Sample Clock<br>Period <sup>(1)</sup>        | _                  | _    | 21   | _    | ms    | LFINTOSC/64                                                                                                                                      |

| OS08         | HFosc                             | Internal Calibrated                                    | ±1%                | 7.92 | 8.0  | 8.08 | MHz   | VDD = 3.5V, 25°C                                                                                                                                 |

|              | HFINTOSC Frequency <sup>(2)</sup> |                                                        | ±2%                | 7.84 | 8.0  | 8.16 | MHz   | $2.5V \le VDD \le 5.5V$ , $0^{\circ}C \le TA \le +85^{\circ}C$                                                                                   |

|              |                                   |                                                        | ±5%                | 7.60 | 8.0  | 8.40 | MHz   | $2.0V \le VDD \le 5.5V$ ,<br>- $40^{\circ}C \le TA \le +85^{\circ}C \text{ (Ind.)}$ ,<br>- $40^{\circ}C \le TA \le +125^{\circ}C \text{ (Ext.)}$ |

| OS09*        | LFosc                             | Internal Uncalibrated<br>LFINTOSC Frequency            | _                  | 15   | 31   | 45   | kHz   |                                                                                                                                                  |

| OS10*        | Tiosc                             | HFINTOSC Oscillator                                    | _                  | 5.5  | 12   | 24   | μS    | $VDD = 2.0V, -40^{\circ}C \text{ to } +85^{\circ}C$                                                                                              |

|              | ST                                | Wake-up from Sleep                                     | _                  | 3.5  | 7    | 14   | μS    | $VDD = 3.0V, -40^{\circ}C \text{ to } +85^{\circ}C$                                                                                              |

|              |                                   | Start-up Time                                          | _                  | 3    | 6    | 11   | μS    | $VDD = 5.0V, -40^{\circ}C \text{ to } +85^{\circ}C$                                                                                              |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- 2: To ensure these oscillator frequency tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible.  $0.1~\mu F$  and  $0.01~\mu F$  values in parallel are recommended.

- 3: By design.

TABLE 17-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET PARAMETERS

Standard Operating Conditions (unless otherwise stated) Operating Temperature -40°C  $\leq$  TA  $\leq$  +125°C **Param** Sym. Characteristic Min. Typ† Max. Units **Conditions** No. 30 **TMCL** MCLR Pulse Width (low) 2  $VDD = 5V, -40^{\circ}C \text{ to } +85^{\circ}C$ μS 5 VDD = 5VμS 31 VDD = 5V,  $-40^{\circ}C$  to  $+85^{\circ}C$ TWDT Watchdog Timer Time-out 10 16 29 ms Period (No Prescaler) VDD = 5V10 16 31 ms 32 Oscillation Start-up Timer 1024 (Note 3) Tost Tosc Period<sup>(1, 2)</sup> 33\* **T**PWRT Power-up Timer Period 40 65 140 ms 34\* Tioz I/O High-impedance from 2.0 μS MCLR Low or Watchdog Timer Reset 35 Brown-out Reset Voltage **VBOR** 2.0 2.2 V BOR4V bit = 0 (Note 4) 3.6 4.0 4.4 ٧ BOR4V bit = 1,  $-40^{\circ}$ C to  $+85^{\circ}$ C (Note 4) 4.0 4.5 ٧ BOR4V bit = 1, -40°C to +125°C 3.6 (Note 4) 36\* VHYST Brown-out Reset Hysteresis 50 mV 37\* **T**BOR Brown-out Reset Minimum 100 μS VDD ≤ VBOR **Detection Period**

- Note 1: Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- 2: By design.

- 3: Period of the slower clock.

- 4: To ensure these voltage tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### 19.1 Package Marking Information (Continued)

44-Lead TQFP (10x10x1 mm)

Legend: XX...X Customer-specific information

Year code (last digit of calendar year) ΥY Year code (last 2 digits of calendar year) WWWeek code (week of January 1 is week '01')

NNN Alphanumeric traceability code

(e3) Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (@3) can be found on the outer packaging for this package.

Note: In the event the full Microchip part number cannot be marked on one line, it will

be carried over to the next line, thus limiting the number of available characters for customer-specific information.

### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

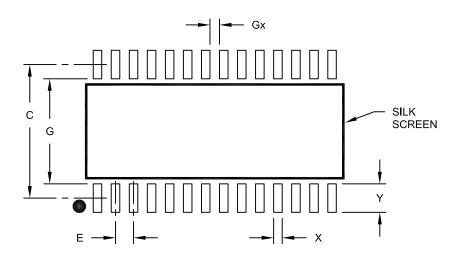

### RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |      |      |      |

|--------------------------|-------------|------|------|------|

| Dimension                | MIN         | NOM  | MAX  |      |

| Contact Pitch            | 1.27 BSC    |      |      |      |

| Contact Pad Spacing      | С           |      | 9.40 |      |

| Contact Pad Width (X28)  | Х           |      |      | 0.60 |

| Contact Pad Length (X28) | Υ           |      |      | 2.00 |

| Distance Between Pads    | Gx          | 0.67 |      |      |

| Distance Between Pads    | G           | 7.40 |      |      |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A