Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 14x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-TQFP                                                                  |

| Supplier Device Package    | 44-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f884-e-pt |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

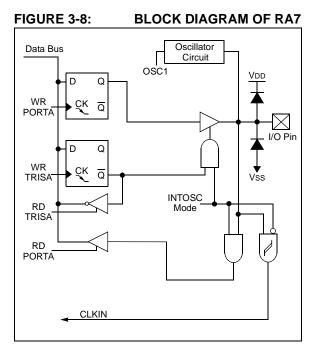

#### 3.2.3.8 RA7/OSC1/CLKIN

Figure 3-8 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a crystal/resonator connection

- · a clock input

### TABLE 3-1: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name       | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|------------|--------|--------|--------|--------|--------|--------|---------|--------|---------------------|

| ADCON0     | ADCS1  | ADCS0  | CHS3   | CHS2   | CHS1   | CHS0   | GO/DONE | ADON   | 104                 |

| ANSEL      | ANS7   | ANS6   | ANS5   | ANS4   | ANS3   | ANS2   | ANS1    | ANS0   | 41                  |

| CM1CON0    | C10N   | C10UT  | C10E   | C1POL  |        | C1R    | C1CH1   | C1CH0  | 89                  |

| CM2CON0    | C2ON   | C2OUT  | C2OE   | C2POL  |        | C2R    | C2CH1   | C2CH0  | 90                  |

| CM2CON1    | MC1OUT | MC2OUT | C1RSEL | C2RSEL |        | _      | T1GSS   | C2SYNC | 92                  |

| PCON       | _      | _      | ULPWUE | SBOREN |        | _      | POR     | BOR    | 37                  |

| OPTION_REG | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1     | PS0    | 31                  |

| PORTA      | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1     | RA0    | 40                  |

| SSPCON     | WCOL   | SSPOV  | SSPEN  | CKP    | SSPM3  | SSPM2  | SSPM1   | SSPM0  | 177                 |

| TRISA      | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1  | TRISA0 | 40                  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

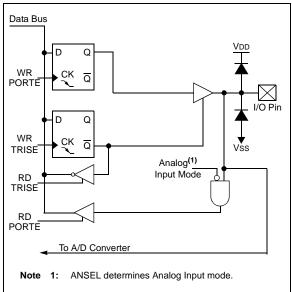

## 3.7.1 RE0/AN5<sup>(1)</sup>

This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

Note 1: RE0/AN5 is available on PIC16F884/887 only.

## 3.7.2 RE1/AN6<sup>(1)</sup>

This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

Note 1: RE1/AN6 is available on PIC16F884/887 only.

## 3.7.3 RE2/AN7<sup>(1)</sup>

This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

Note 1: RE2/AN7 is available on PIC16F884/887 only.

#### FIGURE 3-21: BLOCK DIAGRAM OF RE<2:0>

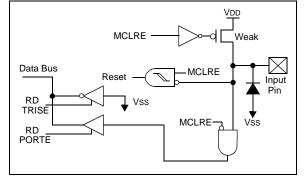

## 3.7.4 RE3/MCLR/VPP

Figure 3-22 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose input

- as Master Clear Reset with weak pull-up

### FIGURE 3-22: BLOCK DIAGRAM OF RE3

## 6.7 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- Timer1 interrupt enable bit of the PIE1 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TTMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

## 6.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- · PEIE bit of the INTCON register must be set

The device will wake-up on an overflow and execute the next instruction. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine (0004h).

### 6.9 ECCP Capture/Compare Time Base

The ECCP module uses the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPRxH:CCPRxL register pair on a configured event.

In Compare mode, an event is triggered when the value CCPRxH:CCPRxL register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Special Event Trigger.

See Section 11.0 "Capture/Compare/PWM Modules (CCP1 and CCP2)" for more information.

## 6.10 ECCP Special Event Trigger

If an ECCP is configured to trigger a special event, the trigger will clear the TMR1H:TMR1L register pair. This special event does not cause a Timer1 interrupt. The ECCP module may still be configured to generate a ECCP interrupt.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

Timer1 should be synchronized to the Fosc to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Special Event Trigger from the ECCP, the write will take precedence.

For more information, see Section 11.0 "Capture/ Compare/PWM Modules (CCP1 and CCP2)".

## 6.11 Comparator Synchronization

The same clock used to increment Timer1 can also be used to synchronize the comparator output. This feature is enabled in the Comparator module.

When using the comparator for Timer1 gate, the comparator output should be synchronized to Timer1. This ensures Timer1 does not miss an increment if the comparator changes.

For more information, see **Section 8.0 "Comparator Module**".

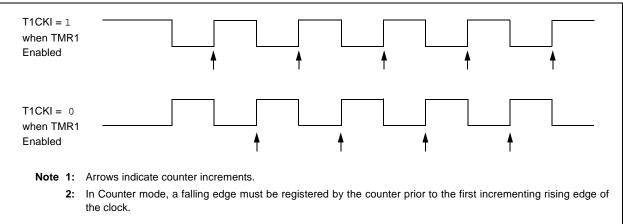

#### FIGURE 6-2: TIMER1 INCREMENTING EDGE

## 6.12 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 6-1, is used to control Timer1 and select the various features of the Timer1 module.

## **REGISTER DEFINITIONS: TIMER1 CONTROL**

## REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0                 | R/W-0                 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-----------------------|-----------------------|---------|---------|---------|--------|--------|--------|

| T1GINV <sup>(1)</sup> | TMR1GE <sup>(2)</sup> | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7                 |                       |         |         |         |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | T1GINV: Timer1 Gate Invert bit <sup>(1)</sup>                                                                                                                |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Timer1 gate is active-high (Timer1 counts when gate is high)</li> <li>0 = Timer1 gate is active-low (Timer1 counts when gate is low)</li> </ul> |

| bit 6   | TMR1GE: Timer1 Gate Enable bit <sup>(2)</sup>                                                                                                                |

|         | $\frac{\text{If TMR1ON} = 0}{1000}$                                                                                                                          |

|         | This bit is ignored<br>If TMR1ON = 1:                                                                                                                        |

|         | 1 = Timer1 counting is controlled by the Timer1 Gate function                                                                                                |

|         | 0 = Timer1 is always counting                                                                                                                                |

| bit 5-4 | T1CKPS<1:0>: Timer1 Input Clock Prescale Select bits                                                                                                         |

|         | 11 = 1:8 Prescale Value                                                                                                                                      |

|         | 10 = 1:4 Prescale Value<br>01 = 1:2 Prescale Value                                                                                                           |

|         | 00 = 1:1 Prescale Value                                                                                                                                      |

| bit 3   | T1OSCEN: LP Oscillator Enable Control bit                                                                                                                    |

|         | 1 = LP oscillator is enabled for Timer1 clock                                                                                                                |

|         | 0 = LP oscillator is off                                                                                                                                     |

| bit 2   | T1SYNC: Timer1 External Clock Input Synchronization Control bit                                                                                              |

|         | <u>TMR1CS = 1:</u><br>1 = Do not synchronize external clock input                                                                                            |

|         | 0 = Synchronize external clock input                                                                                                                         |

|         | $\underline{TMR1CS} = 0:$                                                                                                                                    |

| 1 1 4   | This bit is ignored. Timer1 uses the internal clock                                                                                                          |

| bit 1   | TMR1CS: Timer1 Clock Source Select bit                                                                                                                       |

|         | 1 = External clock from T1CKI pin (on the rising edge)<br>0 = Internal clock (Fosc/4)                                                                        |

| bit 0   | TMR10N: Timer1 On bit                                                                                                                                        |

|         | 1 = Enables Timer1                                                                                                                                           |

|         | 0 = Stops Timer1                                                                                                                                             |

| Note 1: | T1GINV bit inverts the Timer1 gate logic, regardless of source.                                                                                              |

| 2.      | TMR1GE bit must be set to use either $\overline{116}$ pip or C20UT as selected by the T1GSS bit of the CM2CON1                                               |

2: TMR1GE bit must be set to use either T1G pin or C2OUT, as selected by the T1GSS bit of the CM2CON1 register, as a Timer1 gate source.

## **REGISTER DEFINITIONS: TIMER2 CONTROL**

## REGISTER 7-1: T2CON: TIMER2 CONTROL REGISTER

| U-0                   | R/           | /W-0                 | R/W-0            | R/W-0         | R/W-0          | ) R       | /W-0        | R/W-0              | R/W-0   |  |

|-----------------------|--------------|----------------------|------------------|---------------|----------------|-----------|-------------|--------------------|---------|--|

| —                     | TOL          | JTPS3                | TOUTPS2          | TOUTPS1       | TOUTP          | S0 TN     | IR2ON       | T2CKPS1            | T2CKPS0 |  |

| bit 7                 |              |                      |                  |               |                |           |             |                    | bit 0   |  |

| Lowende               |              |                      |                  |               |                |           |             |                    |         |  |

| Legend:<br>R = Readab | la hit       |                      | W = Writable     | hit           | II – I Inin    | nplemente | d hit road  | 1 as 'O'           |         |  |

| -n = Value a          |              |                      | '1' = Bit is set | UIL           |                | s cleared | a bit, read | x = Bit is unknown |         |  |

|                       |              |                      |                  |               | 0 – Dit i      | s cleared |             |                    |         |  |

| bit 7                 | Unim         | plement              | ed: Read as '    | 0'            |                |           |             |                    |         |  |

| bit 6-3               | TOUT         | TPS<3:0>             | -: Timer2 Outp   | out Postscale | er Select bits | 5         |             |                    |         |  |

|                       |              | = 1:1 Po             | -                |               |                |           |             |                    |         |  |

|                       | 0001         | = 1:2 Po             | stscaler         |               |                |           |             |                    |         |  |

|                       | 0010         | = 1:3 Po             | stscaler         |               |                |           |             |                    |         |  |

|                       |              | = 1:4 Po             |                  |               |                |           |             |                    |         |  |

|                       |              | = 1:5 Po             |                  |               |                |           |             |                    |         |  |

|                       |              | = 1:6 Po             |                  |               |                |           |             |                    |         |  |

|                       |              | = 1:7 Po<br>= 1:8 Po |                  |               |                |           |             |                    |         |  |

|                       |              | = 1.0 P0             |                  |               |                |           |             |                    |         |  |

|                       |              | = 1:10 P             |                  |               |                |           |             |                    |         |  |

|                       |              | = 1:11 P             |                  |               |                |           |             |                    |         |  |

|                       |              | = 1:12 P             |                  |               |                |           |             |                    |         |  |

|                       | 1100         | = 1:13 P             | ostscaler        |               |                |           |             |                    |         |  |

|                       | 1101         | = 1:14 P             | ostscaler        |               |                |           |             |                    |         |  |

|                       |              | = 1:15 P             |                  |               |                |           |             |                    |         |  |

|                       | 1111         | = 1:16 P             | ostscaler        |               |                |           |             |                    |         |  |

| bit 2                 | TMR          | 20N: Tim             | er2 On bit       |               |                |           |             |                    |         |  |

|                       | 1 = T        | Fimer2 is            | on               |               |                |           |             |                    |         |  |

|                       | 0 = <b>T</b> | Fimer2 is            | off              |               |                |           |             |                    |         |  |

| bit 1-0               | T2CK         | (PS<1:0>             | Timer2 Cloc      | k Prescale S  | Select bits    |           |             |                    |         |  |

|                       | 00 =         | Prescaler            | r is 1           |               |                |           |             |                    |         |  |

|                       | 01 =         | Prescaler            | is 4             |               |                |           |             |                    |         |  |

|                       | 1x =         | Prescaler            | r is 16          |               |                |           |             |                    |         |  |

|                       | . פוו        |                      |                  |               |                |           |             |                    |         |  |

| TABLE 7-1             | . 30         | ININAR Y             | ' OF ASSOC       |               | IER2 REG       | ISTERS    |             |                    |         |  |

| Name   | Bit 7   | Bit 6       | Bit 5          | Bit 4       | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Register<br>on Page |

|--------|---------|-------------|----------------|-------------|---------|--------|---------|---------|---------------------|

| INTCON | GIE     | PEIE        | T0IE           | INTE        | RBIE    | TOIF   | INTF    | RBIF    | 32                  |

| PIE1   | —       | ADIE        | RCIE           | TXIE        | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 33                  |

| PIR1   | —       | ADIF        | RCIF           | TXIF        | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 35                  |

| PR2    | Timer2  | Module Per  | iod Register   |             |         |        |         |         | 83                  |

| TMR2   | Holding | Register fo | r the 8-bit TI | MR2 Registe | er      |        |         |         | 83                  |

| T2CON  | —       | TOUTPS3     | TOUTPS2        | TOUTPS1     | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 84                  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module.

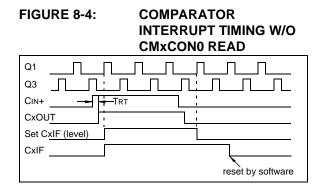

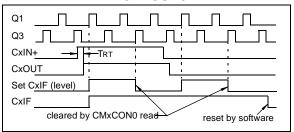

## 8.4 Comparator Interrupt Operation

The comparator interrupt flag can be set whenever there is a change in the output value of the comparator. Changes are recognized by means of a mismatch circuit which consists of two latches and an exclusiveor gate (see Figures 8-2 and 8-3). One latch is updated with the comparator output level when the CMxCON0 register is read. This latch retains the value until the next read of the CMxCON0 register or the occurrence of a Reset. The other latch of the mismatch circuit is updated on every Q1 system clock. A mismatch condition will occur when a comparator output change is clocked through the second latch on the Q1 clock cycle. At this point the two mismatch latches have opposite output levels which is detected by the exclusive-or gate and fed to the interrupt circuitry. The mismatch condition persists until either the CMxCON0 register is read or the comparator output returns to the previous state.

- Note 1: A write operation to the CMxCON0 register will also clear the mismatch condition because all writes include a read operation at the beginning of the write cycle.

- **2:** Comparator interrupts will operate correctly regardless of the state of CxOE.

The comparator interrupt is set by the mismatch edge and not the mismatch level. This means that the interrupt flag can be reset without the additional step of reading or writing the CMxCON0 register to clear the mismatch registers. When the mismatch registers are cleared, an interrupt will occur upon the comparator's return to the previous state, otherwise no interrupt will be generated.

Software will need to maintain information about the status of the comparator output, as read from the CMxCON0 register, or CM2CON1 register, to determine the actual change that has occurred.

The CxIF bit of the PIR2 register is the comparator interrupt flag. This bit must be reset in software by clearing it to '0'. Since it is also possible to write a '1' to this register, an interrupt can be generated.

The CxIE bit of the PIE2 register and the PEIE and GIE bits of the INTCON register must all be set to enable comparator interrupts. If any of these bits are cleared, the interrupt is not enabled, although the CxIF bit of the PIR2 register will still be set if an interrupt condition occurs.

COMPARATOR INTERRUPT TIMING WITH CMxCON0 READ

- Note 1: If a change in the CMxCON0 register (CxOUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CxIF of the PIR2 register interrupt flag may not get set.

- 2: When either comparator is first enabled, bias circuitry in the comparator module may cause an invalid output from the comparator until the bias circuitry is stable. Allow about 1  $\mu$ s for bias settling then clear the mismatch condition and interrupt flags before enabling comparator interrupts.

### REGISTER 13-1: SSPSTAT: SSP STATUS REGISTER

| R/W-0                   | R/W-0                                                                                                                | R-0                                             | R-0                          | R-0                | R-0                   | R-0                  | R-0             |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------|--------------------|-----------------------|----------------------|-----------------|--|--|--|--|

| SMP                     | CKE                                                                                                                  | D/A                                             | Р                            | S                  | R/W                   | UA                   | BF              |  |  |  |  |

| bit 7                   |                                                                                                                      |                                                 |                              |                    |                       | •                    | bit (           |  |  |  |  |

|                         |                                                                                                                      |                                                 |                              |                    |                       |                      |                 |  |  |  |  |

| Legend:<br>R = Readable | hit                                                                                                                  | W = Writable bit                                |                              | II – Unimplomo     | ented bit, read as    | <u>ن</u> ٥'          |                 |  |  |  |  |

| -n = Value at P         |                                                                                                                      | '1' = Bit is set                                |                              | '0' = Bit is clear | -                     | x = Bit is unknov    |                 |  |  |  |  |

|                         | UK                                                                                                                   |                                                 |                              |                    | eu                    |                      | WII             |  |  |  |  |

| bit 7                   | SMP: Sample                                                                                                          | bit                                             |                              |                    |                       |                      |                 |  |  |  |  |

|                         | SPI Master mo                                                                                                        |                                                 |                              |                    |                       |                      |                 |  |  |  |  |

|                         | •                                                                                                                    | sampled at end of<br>sampled at middle          | •                            |                    |                       |                      |                 |  |  |  |  |

|                         | SPI Slave mod                                                                                                        |                                                 |                              |                    |                       |                      |                 |  |  |  |  |

|                         |                                                                                                                      | cleared when SPI                                | is used in Slave             | e mode             |                       |                      |                 |  |  |  |  |

|                         | $\frac{\ln I^2 C \text{ Master } c}{1 = \text{Slew rate}}$                                                           | o <u>r Slave mode:</u><br>control disabled fo   | r standard sne               | ed mode (100 kH:   | z and 1 MHz)          |                      |                 |  |  |  |  |

|                         |                                                                                                                      | control enabled fo                              | •                            | ,                  | - 4.14 - 11112)       |                      |                 |  |  |  |  |

| bit 6                   | CKE: SPI Cloc                                                                                                        | k Edge Select bit                               |                              |                    |                       |                      |                 |  |  |  |  |

|                         | $\frac{CKP = 0}{1  Data transmiss}$                                                                                  | nitted on falling ed                            | las of SCK                   |                    |                       |                      |                 |  |  |  |  |

|                         |                                                                                                                      | nitted on rising ed                             |                              |                    |                       |                      |                 |  |  |  |  |

|                         | <u>CKP = 1:</u>                                                                                                      |                                                 |                              |                    |                       |                      |                 |  |  |  |  |

|                         |                                                                                                                      | nitted on rising ed                             | 0                            |                    |                       |                      |                 |  |  |  |  |

| bit 5                   | 0 = Data transmitted on falling edge of SCK<br>$\overline{DIA}$ : Data/Address bit (I <sup>2</sup> C mode only)      |                                                 |                              |                    |                       |                      |                 |  |  |  |  |

|                         | 1 = Indicates th                                                                                                     | nat the last byte re                            | ceived or trans              |                    |                       |                      |                 |  |  |  |  |

|                         |                                                                                                                      | nat the last byte re                            | ceived or trans              | mitted was addre   | SS                    |                      |                 |  |  |  |  |

| bit 4                   | P: Stop bit<br>(I <sup>2</sup> C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.) |                                                 |                              |                    |                       |                      |                 |  |  |  |  |

|                         |                                                                                                                      | hat a Stop bit has I                            |                              |                    |                       | cicarcu.)            |                 |  |  |  |  |

|                         | 0 = Stop bit wa                                                                                                      | s not detected las                              | t                            |                    | ,                     |                      |                 |  |  |  |  |

| bit 3                   | S: Start bit                                                                                                         |                                                 |                              |                    |                       |                      |                 |  |  |  |  |

|                         |                                                                                                                      | r. This bit is cleared<br>nat a Start bit has l |                              |                    |                       | cleared.)            |                 |  |  |  |  |

|                         |                                                                                                                      | is not detected las                             |                              |                    | on Resel)             |                      |                 |  |  |  |  |

| bit 2                   | <b>R/W</b> : Read/Wr                                                                                                 | ite bit information                             | (I <sup>2</sup> C mode only) | )                  |                       |                      |                 |  |  |  |  |

|                         | This bit holds the                                                                                                   | he R/W bit informa                              | tion following th            | ne last address m  | atch. This bit is o   | nly valid from the a | ddress match to |  |  |  |  |

|                         | In I <sup>2</sup> C Slave m                                                                                          |                                                 | ACK DIL                      |                    |                       |                      |                 |  |  |  |  |

|                         | 1 = Read                                                                                                             |                                                 |                              |                    |                       |                      |                 |  |  |  |  |

|                         | 0 = Write<br>In I <sup>2</sup> C Master r                                                                            | node:                                           |                              |                    |                       |                      |                 |  |  |  |  |

|                         | 1 = Transmit                                                                                                         | is in progress                                  |                              |                    |                       |                      |                 |  |  |  |  |

|                         |                                                                                                                      | is not in progress                              | SEN, PEN, RC                 | EN. or ACKEN w     | ill indicate if the N | ISSP is in Idle mod  | de.             |  |  |  |  |

| bit 1                   | -                                                                                                                    | dress bit (10-bit l <sup>2</sup>                |                              |                    |                       |                      |                 |  |  |  |  |

|                         | 1 = Indicates the                                                                                                    | nat the user needs                              | to update the a              | address in the SS  | PADD register         |                      |                 |  |  |  |  |

| <b>h</b> it 0           |                                                                                                                      | bes not need to be                              | updated                      |                    |                       |                      |                 |  |  |  |  |

| bit 0                   | BF: Buffer Full<br>Receive (SPL a                                                                                    | Status bit<br>ind I <sup>2</sup> C modes):      |                              |                    |                       |                      |                 |  |  |  |  |

|                         | 1 = Receive co                                                                                                       | mplete, SSPBUF                                  |                              |                    |                       |                      |                 |  |  |  |  |

|                         |                                                                                                                      | ot complete, SSPB                               | UF is empty                  |                    |                       |                      |                 |  |  |  |  |

|                         | <u>Transmit (I<sup>2</sup>C r</u><br>1 = Data transi                                                                 | <u>node only):</u><br>nit in progress (do       | es not include               | the ACK and Stor   | bits), SSPBUF i       | s full               |                 |  |  |  |  |

|                         | 0 = Data transi                                                                                                      |                                                 |                              |                    |                       |                      |                 |  |  |  |  |

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. The buffer full bit BF of the SSPSTAT register indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP Interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 13-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable, and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP STATUS register (SSPSTAT register) indicates the various status conditions.

## 13.3.2 ENABLING SPI I/O

To enable the serial port, SSP Enable bit SSPEN of the SSPCON register must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCON registers, and then set the <u>SSPEN</u> bit. This configures the SDI, SDO, SCK and <u>SS</u> pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> bit cleared

- SCK (Master mode) must have TRISC<3> bit cleared

- SCK (Slave mode) must have TRISC<3> bit set

- SS must have TRISA<5> bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

### EXAMPLE 13-1: LOADING THE SSPBUF (SSPSR) REGISTER

| LOOP | GOTO  | SSPSTAT, BF<br>LOOP<br>SSPBUF, W | ;Has data been received (transmit complete)?<br>;No<br>;WREG reg = contents of SSPBUF |

|------|-------|----------------------------------|---------------------------------------------------------------------------------------|

|      | MOVWF | RXDATA                           | ;Save in user RAM, if data is meaningful                                              |

|      |       | TXDATA, W<br>SSPBUF              | ;W reg = contents of TXDATA<br>;New data to xmit                                      |

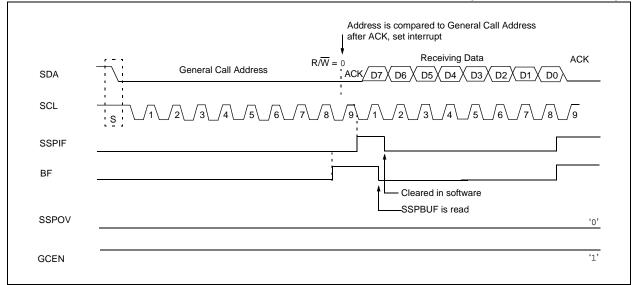

#### 13.4.2 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that, the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address, which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the I<sup>2</sup>C protocol. It consists of all 0's with R/W = 0.

The general call address is recognized (enabled) when the General Call Enable (GCEN) bit is set (SSPCON2 register). Following a Start bit detect, eight bits are shifted into the SSPSR and the address is compared against the SSPADD. It is also compared to the general call address and fixed in hardware. If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF bit is set (eighth bit), and on the falling edge of the ninth bit (ACK bit), the SSPIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF. The value can be used to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match, and the UA bit is set (SSPSTAT register). If the general call address is sampled when the GCEN bit is set, and while the slave is configured in 10-bit address mode, then the second half of the address is not necessary. The UA bit will not be set, and the slave will begin receiving data after the Acknowledge (Figure 13-9).

### FIGURE 13-9: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE (7 OR 10-BIT ADDRESS)

## 14.11 In-Circuit Debugger

The PIC16F882/883/884/886/887-ICD can be used in any of the package types. The devices will be mounted on the target application board, which in turn has a 3 or 4-wire connection to the ICD tool.

When the debug bit in the Configuration Word (CONFIG<13>) is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> ICD 2. When the microcontroller has this feature enabled, some of the resources are not available for general use. See Table 14-10 for more detail.

Note: The user's application must have the circuitry required to support ICD functionality. Once the ICD circuitry is enabled, normal device pin functions on RB6/ICSPCLK and RB7/ICSPDAT will not be usable. The ICD circuitry uses these pins for communication with the ICD2 external debugger.

For more information, see "Using *MPLAB*<sup>®</sup> *ICD* 2" (DS51265), available on Microchip's web site (www.microchip.com).

#### 14.11.1 ICD PINOUT

The devices in the MemHigh family carry the circuitry for the In-Circuit Debugger on-chip and on existing device pins. This eliminates the need for a separate die or package for the ICD device. The pinout for the ICD device is the same as the devices (see **Section 1.0 "Device Overview"** for complete pinout and pin descriptions). Table 14-10 shows the location and function of the ICD related pins on the 28 and 40 pin devices.

| Pin           | (PDIP)            | Name     | Tuno      | Pull-up | Description                             |  |

|---------------|-------------------|----------|-----------|---------|-----------------------------------------|--|

| PIC16F884/887 | PIC16F882/883/886 | Name     | Name Type |         | Description                             |  |

| 40            | 28                | ICDDATA  | TTL       | —       | In-Circuit Debugger Bidirectional data  |  |

| 39            | 27                | ICDCLK   | ST        | —       | In-Circuit Debugger Bidirectional clock |  |

| 1             | 1                 | MCLR/Vpp | ΗV        | _       | Programming voltage                     |  |

| 11,32         | 20                | Vdd      | Р         | _       |                                         |  |

| 12,31         | 8,19              | Vss      | Р         | _       |                                         |  |

Legend: TTL = TTL input buffer, ST = Schmitt Trigger input buffer, P = Power, HV = High Voltage

## 16.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 16.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 16.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 16.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 16.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

## 17.8 AC Characteristics: PIC16F882/883/884/886/887 (Industrial, Extended)

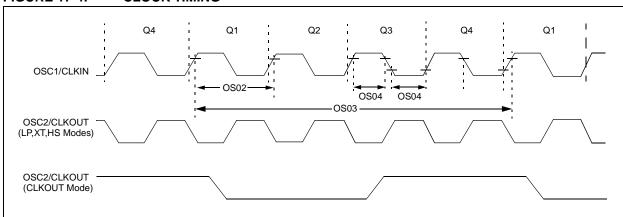

## FIGURE 17-4: CLOCK TIMING

## TABLE 17-1: CLOCK OSCILLATOR TIMING REQUIREMENTS

| Param<br>No. | Sym.                                 | Characteristic                          | Min. | Тур†   | Max.   | Units              | Conditions         |

|--------------|--------------------------------------|-----------------------------------------|------|--------|--------|--------------------|--------------------|

| OS01         | Fosc                                 | External CLKIN Frequency <sup>(1)</sup> | DC   |        | 37     | kHz                | LP Oscillator mode |

|              |                                      |                                         | DC   | _      | 4      | MHz                | XT Oscillator mode |

|              |                                      |                                         | DC   | _      | 20     | MHz                | HS Oscillator mode |

|              |                                      |                                         | DC   | —      | 20     | MHz                | EC Oscillator mode |

|              |                                      | Oscillator Frequency <sup>(1)</sup>     | —    | 32.768 |        | kHz                | LP Oscillator mode |

|              |                                      |                                         | 0.1  | —      | 4      | MHz                | XT Oscillator mode |

|              |                                      |                                         | 1    | —      | 20     | MHz                | HS Oscillator mode |

|              |                                      |                                         | DC   | _      | 4      | MHz                | RC Oscillator mode |

| OS02 Tosc    | External CLKIN Period <sup>(1)</sup> | 27                                      | _    | •      | μS     | LP Oscillator mode |                    |

|              |                                      |                                         | 250  | _      | •      | ns                 | XT Oscillator mode |

|              |                                      |                                         | 50   | _      | •      | ns                 | HS Oscillator mode |

|              |                                      |                                         | 50   | _      | •      | ns                 | EC Oscillator mode |

|              |                                      | Oscillator Period <sup>(1)</sup>        | —    | 30.5   |        | μS                 | LP Oscillator mode |

|              |                                      |                                         | 250  | _      | 10,000 | ns                 | XT Oscillator mode |

|              |                                      |                                         | 50   | _      | 1,000  | ns                 | HS Oscillator mode |

|              |                                      |                                         | 250  | _      | _      | ns                 | RC Oscillator mode |

| OS03         | Тсү                                  | Instruction Cycle Time <sup>(1)</sup>   | 200  | TCY    | DC     | ns                 | TCY = 4/FOSC       |

| OS04*        | TosH,                                | External CLKIN High,                    | 2    | —      |        | μS                 | LP oscillator      |

|              | TosL                                 | External CLKIN Low                      | 100  | _      | —      | ns                 | XT oscillator      |

|              |                                      |                                         | 20   | —      | —      | ns                 | HS oscillator      |

| OS05*        | TosR,                                | External CLKIN Rise,                    | 0    | —      | •      | ns                 | LP oscillator      |

|              | TosF                                 | External CLKIN Fall                     | 0    | —      | •      | ns                 | XT oscillator      |

|              |                                      |                                         | 0    | _      | •      | ns                 | HS oscillator      |

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and

Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for

all devices.

are not tested.

†

Note 1:

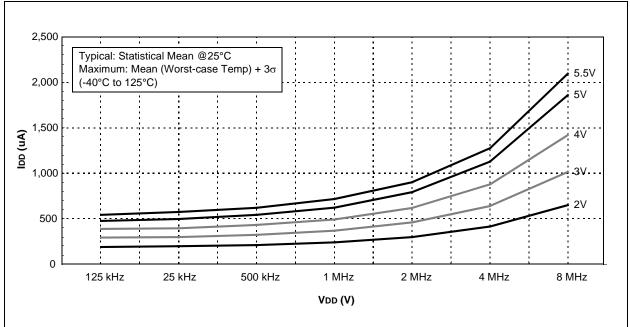

## FIGURE 18-11: TYPICAL IDD vs. Fosc OVER VDD (HFINTOSC MODE)

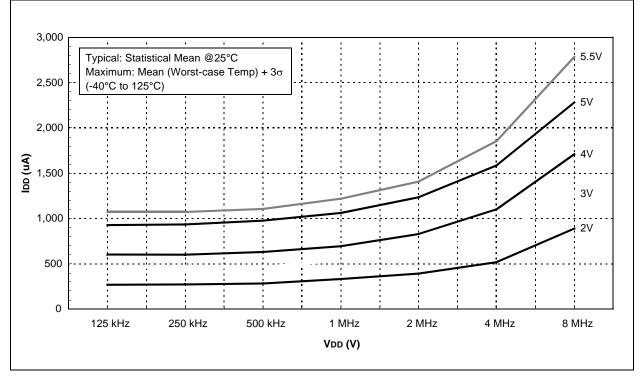

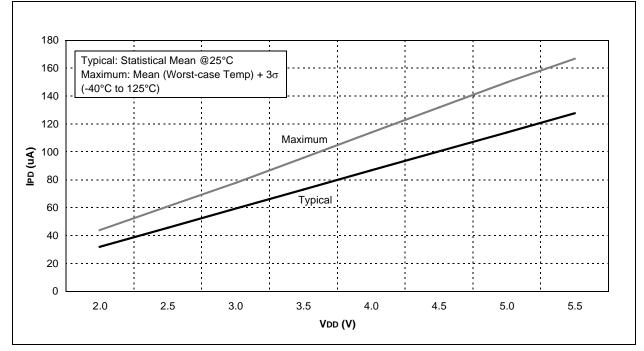

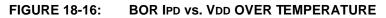

## FIGURE 18-15: COMPARATOR IPD vs. VDD (BOTH COMPARATORS ENABLED)

## 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

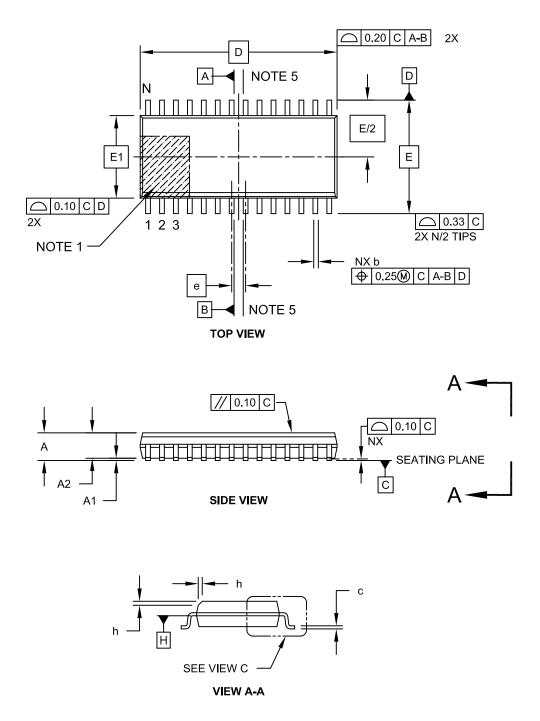

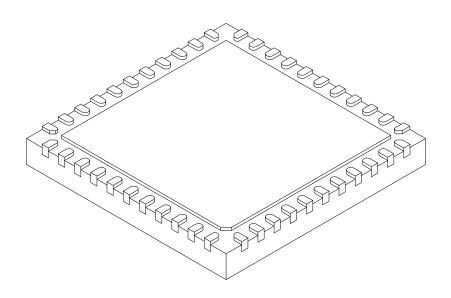

## 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                   |    | MILLIMETERS |      |      |

|-------------------------|----|-------------|------|------|

| Dimension Limits        |    | MIN         | NOM  | MAX  |

| Number of Pins          | N  | 44          |      |      |

| Pitch                   | е  | 0.65 BSC    |      |      |

| Overall Height          | A  | 0.80        | 0.90 | 1.00 |

| Standoff                | A1 | 0.00        | 0.02 | 0.05 |

| Terminal Thickness      | A3 | 0.20 REF    |      |      |

| Overall Width           | E  | 8.00 BSC    |      |      |

| Exposed Pad Width       | E2 | 6.25        | 6.45 | 6.60 |

| Overall Length          | D  | 8.00 BSC    |      |      |

| Exposed Pad Length      | D2 | 6.25        | 6.45 | 6.60 |

| Terminal Width          | b  | 0.20        | 0.30 | 0.35 |

| Terminal Length         | L  | 0.30        | 0.40 | 0.50 |

| Terminal-to-Exposed-Pad | K  | 0.20        | -    | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension. usually without tolerance. for information purposes only.

Microchip Technology Drawing C04-103C Sheet 2 of 2

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, flexPWR, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC<sup>32</sup> logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

The Embedded Control Solutions Company and mTouch are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, ECAN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, KleerNet, KleerNet logo, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, RightTouch logo, REAL ICE, SQI, Serial Quad I/O, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2006-2015, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-63277-237-4

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.