Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 14x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 44-QFN (8×8)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f884-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

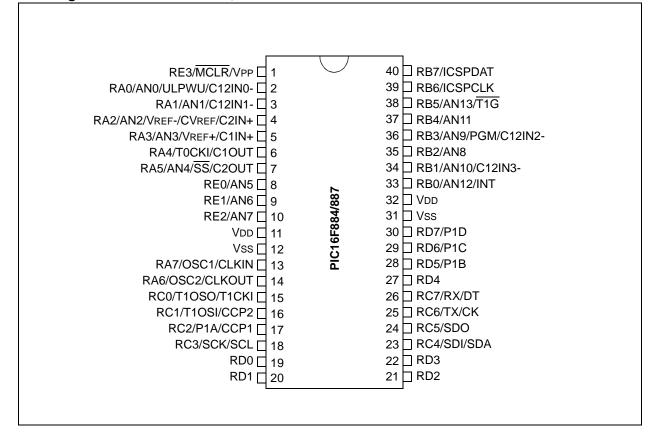

### Pin Diagrams - PIC16F884/887, 40-Pin PDIP

## 3.0 I/O PORTS

There are as many as 35 general purpose I/O pins available. Depending on which peripherals are enabled, some or all of the pins may not be available as general purpose I/O. In general, when a peripheral is enabled, the associated pin may not be used as a general purpose I/O pin.

### 3.1 PORTA and the TRISA Registers

PORTA is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 3-2). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 3-1 shows how to initialize PORTA.

Reading the PORTA register (Register 3-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

#### REGISTER 3-1: PORTA: PORTA REGISTER

The TRISA register (Register 3-2) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

| Note: | The ANSEL register must be initialized to |

|-------|-------------------------------------------|

|       | configure an analog channel as a digital  |

|       | input. Pins configured as analog inputs   |

|       | will read '0'.                            |

| EXAMPLE 3-1:  | INITIALIZING PORTA |

|---------------|--------------------|

| BANKSEL PORTA | ;                  |

|               | THE DODER          |

| CLRF    | PORTA | ;Init PORTA            |

|---------|-------|------------------------|

| BANKSEL | ANSEL | ;                      |

| CLRF    | ANSEL | ;digital I/O           |

| BANKSEL | TRISA | ;                      |

| MOVLW   | 0Ch   | ;Set RA<3:2> as inputs |

| MOVWF   | TRISA | ;and set RA<5:4,1:0>   |

|         |       | ;as outputs            |

|         |       |                        |

| Lawawala |       |       |       |       |       |       |       |

|----------|-------|-------|-------|-------|-------|-------|-------|

|          |       |       |       |       |       |       |       |

| bit 7    |       |       |       |       |       |       | bit 0 |

| RA7      | RA6   | RA5   | RA4   | RA3   | RA2   | RA1   | RA0   |

| R/W-x    | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | · 'O'              |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

bit 7-0 RA<7:0>: PORTA I/O Pin bit

1 = Port pin is > VIH

0 = Port pin is < VIL

### REGISTER 3-2: TRISA: PORTA TRI-STATE REGISTER

| R/W-1 <sup>(1)</sup> | R/W-1 <sup>(1)</sup> | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|----------------------|----------------------|--------|--------|--------|--------|--------|--------|

| TRISA7               | TRISA6               | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 |

| bit 7                |                      |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-0 TRISA<7:0>: PORTA Tri-State Control bit

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

**Note 1:** TRISA<7:6> always reads '1' in XT, HS and LP Oscillator modes.

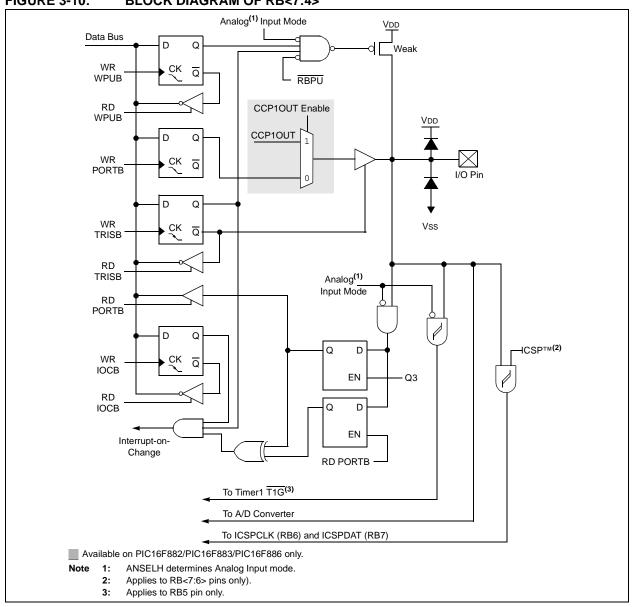

#### FIGURE 3-10: BLOCK DIAGRAM OF RB<7:4>

| Name       | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|------------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELH     | —      | —      | ANS13  | ANS12  | ANS11  | ANS10  | ANS9   | ANS8   | 49                  |

| CCP1CON    | P1M1   | P1M0   | DC1B1  | DC1B0  | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 | 122                 |

| CM2CON1    | MC1OUT | MC2OUT | C1RSEL | C2RSEL | _      | _      | T1GSS  | C2SYNC | 92                  |

| IOCB       | IOCB7  | IOCB6  | IOCB5  | IOCB4  | IOCB3  | IOCB2  | IOCB1  | IOCB0  | 50                  |

| INTCON     | GIE    | PEIE   | TOIE   | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 32                  |

| OPTION_REG | RBPU   | INTEDG | TOCS   | TOSE   | PSA    | PS2    | PS1    | PS0    | 31                  |

| PORTB      | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | 49                  |

| TRISB      | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 49                  |

| WPUB       | WPUB7  | WPUB6  | WPUB5  | WPUB4  | WPUB3  | WPUB2  | WPUB1  | WPUB0  | 50                  |

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTB.

© 2006-2015 Microchip Technology Inc.

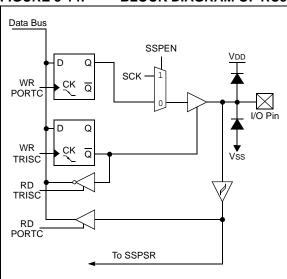

### 3.5.4 RC3/SCK/SCL

Figure 3-14 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a SPI clock

- an I<sup>2</sup>C<sup>™</sup> clock

### FIGURE 3-14: BLOCK DIAGRAM OF RC3

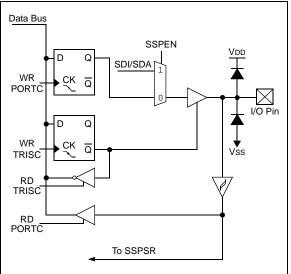

### 3.5.5 RC4/SDI/SDA

Figure 3-15 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a SPI data I/O

- an I<sup>2</sup>C data I/O

### FIGURE 3-15: BLOCK DIAGRAM OF RC4

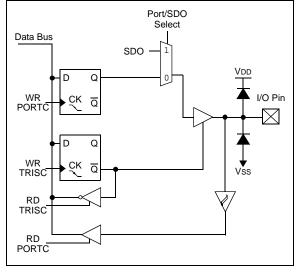

### 3.5.6 RC5/SDO

Figure 3-16 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- · a serial data output

| TABLE 6-1: | SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1 |

|------------|---------------------------------------------|

|------------|---------------------------------------------|

| Name    | Bit 7                                                                       | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-----------------------------------------------------------------------------|--------|---------|---------|---------|--------|--------|--------|---------------------|

| CM2CON1 | MC1OUT                                                                      | MC2OUT | C1RSEL  | C2RSEL  |         | —      | T1GSS  | C2SYNC | 92                  |

| INTCON  | GIE                                                                         | PEIE   | TOIE    | INTE    | RBIE    | T0IF   | INTF   | RBIF   | 32                  |

| PIE1    | —                                                                           | ADIE   | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 33                  |

| PIR1    | —                                                                           | ADIF   | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 35                  |

| TMR1H   | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register  |        |         |         |         |        |        |        | 78                  |

| TMR1L   | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |        |         |         |         |        |        |        | 78                  |

| T1CON   | T1GINV                                                                      | TMR1GE | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 81                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

| R/W-0           | U-0                                                        | R/W-0            | R/W-0           | U-0              | U-0              | U-0             | U-0   |

|-----------------|------------------------------------------------------------|------------------|-----------------|------------------|------------------|-----------------|-------|

| ADFM            |                                                            | VCFG1            | VCFG0           | —                | —                | —               | —     |

| bit 7           |                                                            |                  |                 |                  |                  |                 | bit 0 |

| r               |                                                            |                  |                 |                  |                  |                 |       |

| Legend:         |                                                            |                  |                 |                  |                  |                 |       |

| R = Readable    | bit                                                        | W = Writable     | bit             | U = Unimpler     | nented bit, read | d as '0'        |       |

| -n = Value at F | POR                                                        | '1' = Bit is set |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

| bit 7           | <b>ADFM:</b> A/D C<br>1 = Right justi<br>0 = Left justifie |                  | sult Format Sel | ect bit          |                  |                 |       |

| bit 6           | Unimplemen                                                 | ted: Read as '   | 0'              |                  |                  |                 |       |

| bit 5           | VCFG1: Volta                                               | ge Reference     | bit             |                  |                  |                 |       |

|                 | 1 = VREF- pin<br>0 = VSS                                   |                  |                 |                  |                  |                 |       |

| bit 4           | VCFG0: Volta                                               | ge Reference     | bit             |                  |                  |                 |       |

|                 | 1 = VREF+ pin<br>0 = VDD                                   | 1                |                 |                  |                  |                 |       |

| bit 3-0         | Unimplemen                                                 | ted: Read as '   | 0'              |                  |                  |                 |       |

### REGISTER 9-2: ADCON1: A/D CONTROL REGISTER 1

### 11.6.3 START-UP CONSIDERATIONS

When any PWM mode is used, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins.

Note: When the microcontroller is released from Reset, all of the I/O pins are in the highimpedance state. The external circuits must keep the power switch devices in the Off state until the microcontroller drives the I/O pins with the proper signal levels or activates the PWM output(s).

The CCP1M<1:0> bits of the CCP1CON register allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (P1A/P1C and P1B/P1D). The PWM output polarities must be selected before the PWM pin output drivers are enabled. Changing the polarity configuration while the PWM pin output drivers are enable is not recommended since it may result in damage to the application circuits.

The P1A, P1B, P1C and P1D output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pin output drivers at the same time as the Enhanced PWM modes may cause damage to the application circuit. The Enhanced PWM modes must be enabled in the proper Output mode and complete a full PWM cycle before enabling the PWM pin output drivers. The completion of a full PWM cycle is indicated by the TMR2IF bit of the PIR1 register being set as the second PWM period begins.

| R-0           | R-1                                             | U-0                                         | R/W-0           | R/W-0              | U-0             | R/W-0             | R/W-0          |  |  |  |

|---------------|-------------------------------------------------|---------------------------------------------|-----------------|--------------------|-----------------|-------------------|----------------|--|--|--|

| ABDOVF        | RCIDL                                           |                                             | SCKP            | BRG16              | _               | WUE               | ABDEN          |  |  |  |

| bit 7         |                                                 |                                             |                 | 1                  |                 |                   | bit 0          |  |  |  |

|               |                                                 |                                             |                 |                    |                 |                   |                |  |  |  |

| Legend:       |                                                 |                                             |                 |                    |                 |                   |                |  |  |  |

| R = Readable  | e bit                                           | W = Writable                                | bit             | U = Unimplem       | nented bit, rea | ad as '0'         |                |  |  |  |

| -n = Value at | POR                                             | '1' = Bit is se                             | t               | '0' = Bit is clea  | ared            | x = Bit is unki   | nown           |  |  |  |

|               |                                                 |                                             |                 |                    |                 |                   |                |  |  |  |

| bit 7         | -                                               | uto-Baud Deteo                              | ct Overflow bit | :                  |                 |                   |                |  |  |  |

|               | Asynchrono                                      |                                             |                 |                    |                 |                   |                |  |  |  |

|               |                                                 | ud timer overflo<br>ud timer did not        |                 |                    |                 |                   |                |  |  |  |

|               | <u>Synchronou</u>                               |                                             | overnow         |                    |                 |                   |                |  |  |  |

|               | Don't care                                      |                                             |                 |                    |                 |                   |                |  |  |  |

| bit 6         | RCIDL: Rec                                      | eive Idle Flag b                            | it              |                    |                 |                   |                |  |  |  |

|               | <u>Asynchrono</u>                               | <u>us mode</u> :                            |                 |                    |                 |                   |                |  |  |  |

|               | 1 = Receive                                     |                                             |                 |                    |                 |                   |                |  |  |  |

|               | 0 = Start bit<br>Synchronou                     |                                             | /ed and the re  | eceiver is receivi | ng              |                   |                |  |  |  |

|               | Don't care                                      | <u>s mode</u> .                             |                 |                    |                 |                   |                |  |  |  |

| bit 5         | Unimpleme                                       | nted: Read as                               | ʻ0'             |                    |                 |                   |                |  |  |  |

| bit 4         | SCKP: Sync                                      | SCKP: Synchronous Clock Polarity Select bit |                 |                    |                 |                   |                |  |  |  |

|               | Asynchronous mode:                              |                                             |                 |                    |                 |                   |                |  |  |  |

|               | 1 = Transmit inverted data to the RB7/TX/CK pin |                                             |                 |                    |                 |                   |                |  |  |  |

|               |                                                 | t non-inverted d                            | ata to the RB   | 7/TX/CK pin        |                 |                   |                |  |  |  |

|               | Synchronou                                      |                                             | n adap of the   | alaak              |                 |                   |                |  |  |  |

|               |                                                 | clocked on rising                           |                 |                    |                 |                   |                |  |  |  |

| bit 3         |                                                 | bit Baud Rate C                             | • •             |                    |                 |                   |                |  |  |  |

|               |                                                 | aud Rate Gene                               |                 |                    |                 |                   |                |  |  |  |

|               | 0 = 8-bit Ba                                    | ud Rate Generation                          | ator is used    |                    |                 |                   |                |  |  |  |

| bit 2         | Unimpleme                                       | nted: Read as                               | ʻ0'             |                    |                 |                   |                |  |  |  |

| bit 1         | WUE: Wake                                       | -up Enable bit                              |                 |                    |                 |                   |                |  |  |  |

|               | <u>Asynchrono</u>                               | <u>us mode</u> :                            |                 |                    |                 |                   |                |  |  |  |

|               |                                                 |                                             |                 | No character wil   | l be received l | byte RCIF will be | e set. WUE wil |  |  |  |

|               |                                                 | tically clear afte                          |                 |                    |                 |                   |                |  |  |  |

|               | 0 = Receive<br>Synchronou                       | r is operating no                           | ormally         |                    |                 |                   |                |  |  |  |

|               | Don't care                                      | <u>s mode</u> .                             |                 |                    |                 |                   |                |  |  |  |

| bit 0         |                                                 | to-Baud Detect                              | Enable bit      |                    |                 |                   |                |  |  |  |

|               | Asynchrono                                      |                                             |                 |                    |                 |                   |                |  |  |  |

|               | -                                               |                                             | e is enabled (  | clears when aut    | o-baud is con   | nplete)           |                |  |  |  |

|               |                                                 | aud Detect mod                              |                 |                    |                 | . ,               |                |  |  |  |

|               | <u>Synchronou</u>                               | <u>s mode</u> :                             |                 |                    |                 |                   |                |  |  |  |

|               | Don't care                                      |                                             |                 |                    |                 |                   |                |  |  |  |

### REGISTER 12-3: BAUDCTL: BAUD RATE CONTROL REGISTER

© 2006-2015 Microchip Technology Inc.

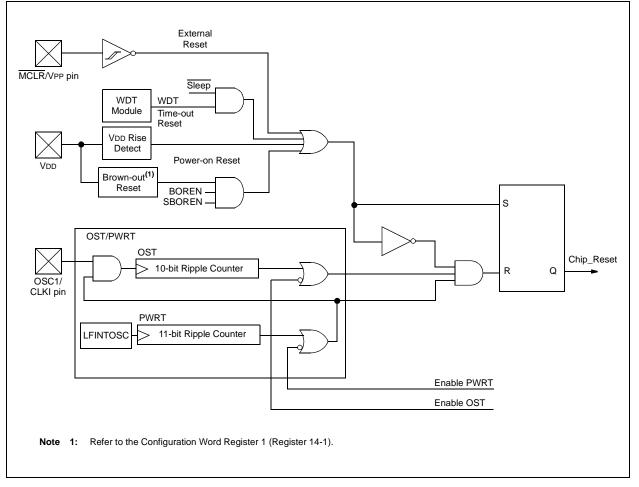

### 14.2 Reset

The PIC16F882/883/884/886/887 devices differentiate between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- c) WDT Reset during Sleep

- d) MCLR Reset during normal operation

- e) MCLR Reset during Sleep

- f) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- Power-on Reset

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

- Brown-out Reset (BOR)

They are not affected by a WDT Wake-up since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different Reset situations, as indicated in Table 14-2. These bits are used in software to determine the nature of the Reset. See Table 14-5 for a full description of Reset states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 14-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See **Section 17.0** "**Electrical Specifications**" for pulse-width specifications.

### FIGURE 14-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

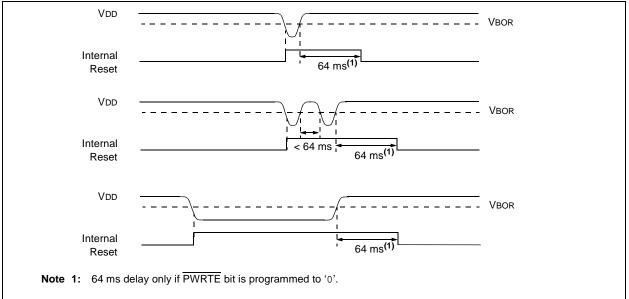

### 14.2.4 BROWN-OUT RESET (BOR)

The BOREN0 and BOREN1 bits in the Configuration Word Register 1 select one of four BOR modes. Two modes have been added to allow software or hardware control of the BOR enable. When BOREN<1:0> = 01, the SBOREN bit (PCON<4>) enables/disables the BOR allowing it to be controlled in software. By selecting BOREN<1:0>, the BOR is automatically disabled in Sleep to conserve power and enabled on wake-up. In this mode, the SBOREN bit is disabled. See Register 14-3 for the Configuration Word definition.

The BOR4V bit in the Configuration Word Register 2 selects one of two Brown-out Reset voltages. When BOR4B = 1, VBOR is set to 4V. When BOR4V = 0, VBOR is set to 2.1V.

If VDD falls below VBOR for greater than parameter (TBOR) (see **Section 17.0 "Electrical Specifications"**), the Brown-out situation will reset the device. This will occur regardless of VDD slew rate. A Reset is not insured to occur if VDD falls below VBOR for less than parameter (TBOR).

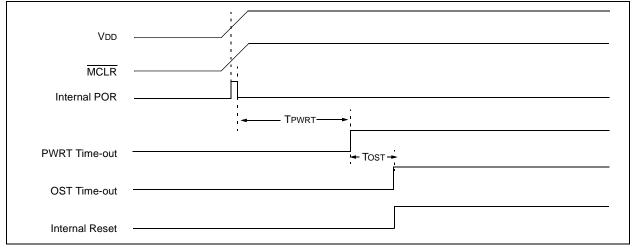

On any Reset (Power-on, Brown-out Reset, Watchdog Timer, etc.), the chip will remain in Reset until VDD rises above VBOR (see Figure 14-3). The Power-up Timer will now be invoked, if enabled and will keep the chip in Reset an additional 64 ms.

| Note: | The Power-up Timer is enabled by the |

|-------|--------------------------------------|

|       | PWRTE bit in the Configuration Word  |

|       | Register 1.                          |

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will execute a 64 ms Reset.

### FIGURE 14-3: BROWN-OUT SITUATIONS

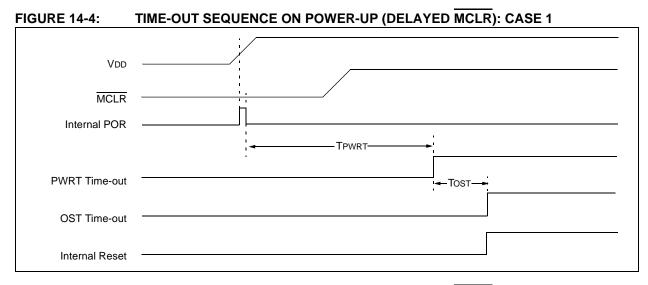

### FIGURE 14-5: TIME-OUT SEQUENCE ON POWER-UP (DELAYED MCLR): CASE 2

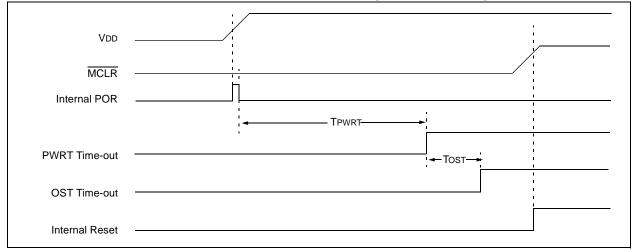

### FIGURE 14-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR WITH VDD)

## 15.0 INSTRUCTION SET SUMMARY

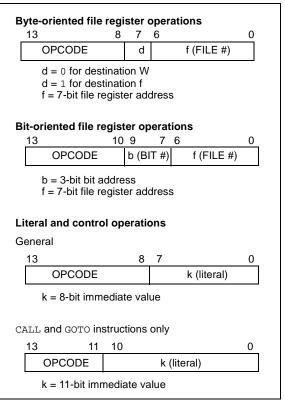

The PIC16F882/883/884/886/887 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 15-1, while the various opcode fields are summarized in Table 15-1.

Table 15-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8-bit or 11-bit constant, or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

### 15.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (RMW) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a CLRF PORTA instruction will read PORTA, clear all the data bits, then write the result back to PORTA. This example would have the unintended consequence of clearing the condition that set the RAIF flag.

### TABLE 15-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                            |

| W     | Working register (accumulator)                                                                                                                                                  |

| b     | Bit address within an 8-bit file register                                                                                                                                       |

| k     | Literal field, constant data or label                                                                                                                                           |

| x     | Don't care location (= 0 or 1).<br>The assembler will generate code with $x = 0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                |

| PC    | Program Counter                                                                                                                                                                 |

| TO    | Time-out bit                                                                                                                                                                    |

| С     | Carry bit                                                                                                                                                                       |

| DC    | Digit carry bit                                                                                                                                                                 |

| Z     | Zero bit                                                                                                                                                                        |

| PD    | Power-down bit                                                                                                                                                                  |

#### FIGURE 15-1: GENERAL FORMAT FOR INSTRUCTIONS

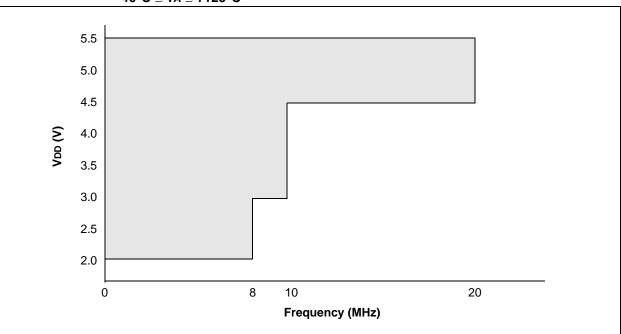

FIGURE 17-1: PIC16F882/883/884/886/887 VOLTAGE-FREQUENCY GRAPH, -40°C  $\leq$  TA  $\leq$  +125°C

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

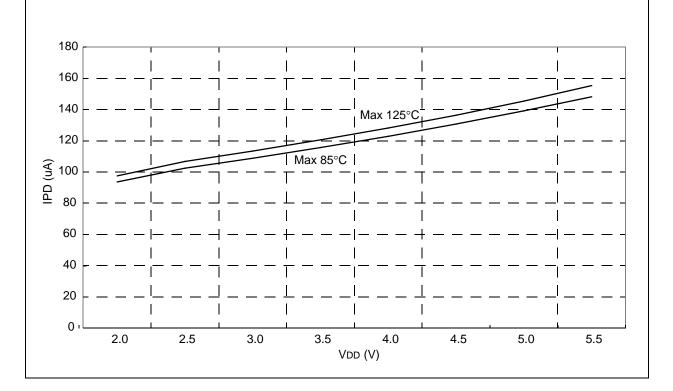

| 17.3 | DC Characteristics: | PIC16F882/883/884/886/887-I (Industrial) |

|------|---------------------|------------------------------------------|

|------|---------------------|------------------------------------------|

| DC CHARACTERISTICS |                             | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |      |      |       |            |                                                 |  |

|--------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|-------------------------------------------------|--|

| Param              | Device Characteristics      | Min                                                                                                                                | Turt |      |       | Conditions |                                                 |  |

| No.                | Device Characteristics      | Min.                                                                                                                               | Тур† | Max. | Units | Vdd        | Note                                            |  |

| D020               | Power-down Base             | —                                                                                                                                  | 0.05 | 1.2  | μA    | 2.0        | WDT, BOR, Comparators, VREF and                 |  |

|                    | Current(IPD) <sup>(2)</sup> | —                                                                                                                                  | 0.15 | 1.5  | μA    | 3.0        | T1OSC disabled                                  |  |

|                    |                             |                                                                                                                                    | 0.35 | 1.8  | μΑ    | 5.0        |                                                 |  |

|                    |                             | —                                                                                                                                  | 150  | 500  | nA    | 3.0        | $\text{-40°C} \leq \text{TA} \leq \text{+25°C}$ |  |

| D021               |                             |                                                                                                                                    | 1.0  | 2.2  | μΑ    | 2.0        | WDT Current <sup>(1)</sup>                      |  |

|                    |                             | —                                                                                                                                  | 2.0  | 4.0  | μA    | 3.0        |                                                 |  |

|                    |                             | —                                                                                                                                  | 3.0  | 7.0  | μΑ    | 5.0        |                                                 |  |

| D022               |                             | —                                                                                                                                  | 42   | 60   | μΑ    | 3.0        | BOR Current <sup>(1)</sup>                      |  |

|                    |                             | —                                                                                                                                  | 85   | 122  | μA    | 5.0        |                                                 |  |

| D023               |                             | —                                                                                                                                  | 32   | 45   | μA    | 2.0        | Comparator Current <sup>(1)</sup> , both        |  |

|                    |                             |                                                                                                                                    | 60   | 78   | μΑ    | 3.0        | comparators enabled                             |  |

|                    |                             | _                                                                                                                                  | 120  | 160  | μA    | 5.0        |                                                 |  |

| D024               |                             | —                                                                                                                                  | 30   | 36   | μA    | 2.0        | CVREF Current <sup>(1)</sup> (high range)       |  |

|                    |                             | _                                                                                                                                  | 45   | 55   | μΑ    | 3.0        |                                                 |  |

|                    |                             | —                                                                                                                                  | 75   | 95   | μA    | 5.0        |                                                 |  |

| D025*              |                             | —                                                                                                                                  | 39   | 47   | μΑ    | 2.0        | CVREF Current <sup>(1)</sup> (low range)        |  |

|                    |                             |                                                                                                                                    | 59   | 72   | μΑ    | 3.0        |                                                 |  |

|                    |                             | —                                                                                                                                  | 98   | 124  | μΑ    | 5.0        |                                                 |  |

| D026               |                             | —                                                                                                                                  | 2.0  | 5.0  | μΑ    | 2.0        | T1OSC Current <sup>(1)</sup> , 32.768 kHz       |  |

|                    |                             | _                                                                                                                                  | 2.5  | 5.5  | μΑ    | 3.0        |                                                 |  |

|                    |                             | —                                                                                                                                  | 3.0  | 7.0  | μΑ    | 5.0        |                                                 |  |

| D027               |                             | —                                                                                                                                  | 0.30 | 1.6  | μΑ    | 3.0        | A/D Current <sup>(1)</sup> , no conversion in   |  |

|                    |                             | —                                                                                                                                  | 0.36 | 1.9  | μΑ    | 5.0        | progress                                        |  |

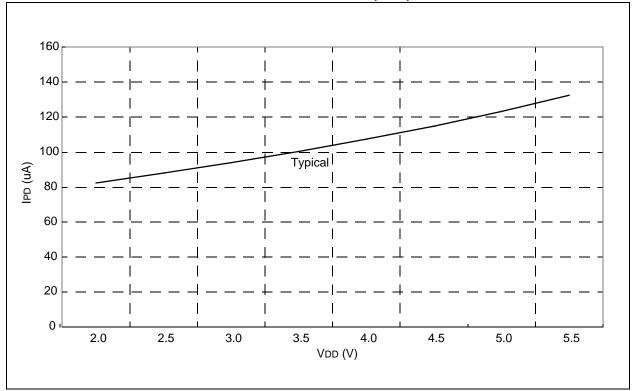

| D028               |                             | —                                                                                                                                  | 90   | 125  | μA    | 3.0        | VP6 Reference Current                           |  |

|                    |                             | —                                                                                                                                  | 125  | 162  | μA    | 5.0        |                                                 |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

### TABLE 17-7: COMPARATOR SPECIFICATIONS

|              | Standard Operating Conditions (unless otherwise stated)   Operating Temperature -40°C ≤ TA ≤ +125°C |                                           |         |      |       |           |       |               |

|--------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------|---------|------|-------|-----------|-------|---------------|

| Param<br>No. | Sym.                                                                                                | Characteristics                           |         | Min. | Тур†  | Max.      | Units | Comments      |

| CM01         | Vos                                                                                                 | Input Offset Voltage                      |         | —    | ± 5.0 | ± 10      | mV    | (Vdd - 1.5)/2 |

| CM02         | Vсм                                                                                                 | Input Common Mode Voltage                 |         | 0    |       | Vdd - 1.5 | V     |               |

| CM03*        | CMRR                                                                                                | Common Mode Rejection Ratio               |         | +55  |       | _         | dB    |               |

| CM04*        | TRT                                                                                                 | Response Time                             | Falling | _    | 150   | 600       | ns    | (Note 1)      |

|              |                                                                                                     |                                           | Rising  |      | 200   | 1000      | ns    |               |

| CM05*        | Тмс2coV                                                                                             | Comparator Mode Change to<br>Output Valid |         | —    |       | 10        | μS    |               |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Response time is measured with one comparator input at (VDD - 1.5)/2 - 100 mV to (VDD - 1.5)/2 + 20 mV.

### TABLE 17-8: COMPARATOR VOLTAGE REFERENCE (CVREF) SPECIFICATIONS

#### Standard Operating Conditions (unless otherwise stated)

Operating temperature  $-40^{\circ}C \le TA \le +125^{\circ}C$

| Param<br>No. | Sym. | Characteristics              | Min. | Тур†             | Max.           | Units      | Comments                                    |

|--------------|------|------------------------------|------|------------------|----------------|------------|---------------------------------------------|

| CV01*        | CLSB | Step Size <sup>(2)</sup>     |      | VDD/24<br>VDD/32 |                | V<br>V     | Low Range (VRR = 1)<br>High Range (VRR = 0) |

| CV02*        | CACC | Absolute Accuracy            |      |                  | ± 1/2<br>± 1/2 | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |

| CV03*        | CR   | Unit Resistor Value (R)      | —    | 2k               | _              | Ω          |                                             |

| CV04*        | Сѕт  | Settling Time <sup>(1)</sup> | _    | _                | 10             | μS         |                                             |

These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** Settling time measured while VRR = 1 and VR<3:0> transitions from '0000' to '1111'.

- 2: See Section 8.10 "Comparator Voltage Reference" for more information.

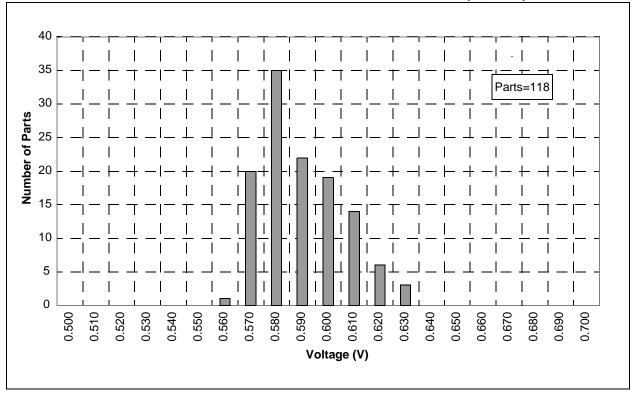

### TABLE 17-9: VOLTAGE (VR) REFERENCE SPECIFICATIONS

| VR Voltage Reference Specifications |         | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |      |       |          |  |

|-------------------------------------|---------|------------------------------------------------------|------|------|-------|----------|--|

| Param<br>No. Symbol Characteristics |         | Min.                                                 | Тур. | Max. | Units | Comments |  |

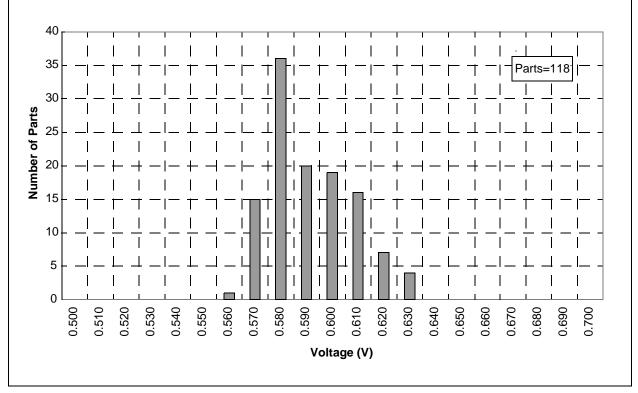

| VR01                                | VROUT   | VR voltage output                                    | 0.5  | 0.6  | 0.7   | V        |  |

| VR02*                               | TSTABLE | Settling Time                                        |      | 10   | 100*  | μS       |  |

These parameters are characterized but not tested.

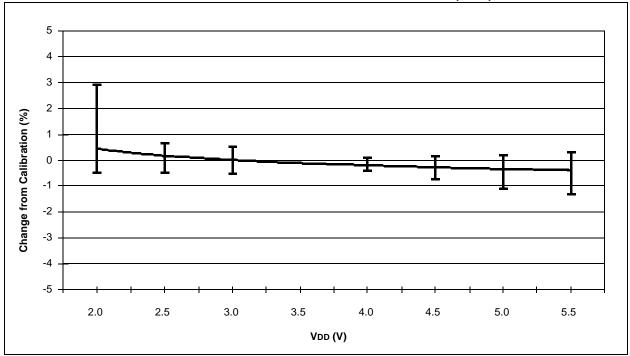

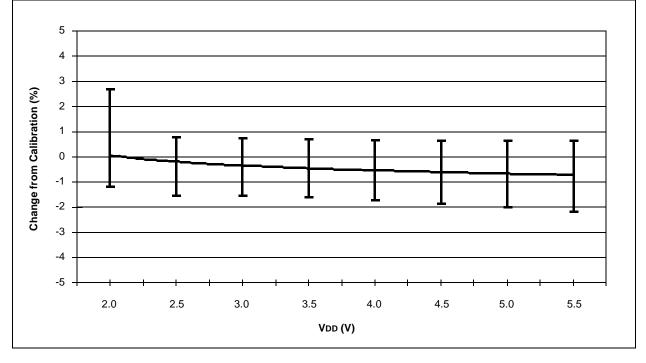

### FIGURE 18-39: TYPICAL HFINTOSC FREQUENCY CHANGE vs. VDD (25°C)

### FIGURE 18-47: TYPICAL VP6 REFERENCE VOLTAGE DISTRIBUTION (3V, 85°C)

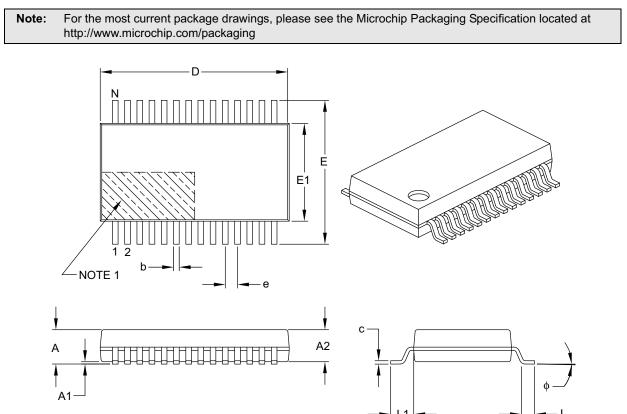

### 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

|                          | Units            | MILLIMETERS |          |       |  |  |

|--------------------------|------------------|-------------|----------|-------|--|--|

|                          | Dimension Limits | MIN         | NOM      | MAX   |  |  |

| Number of Pins           | N                |             | 28       |       |  |  |

| Pitch                    | е                |             | 0.65 BSC |       |  |  |

| Overall Height           | А                | -           | -        | 2.00  |  |  |

| Molded Package Thickness | A2               | 1.65        | 1.75     | 1.85  |  |  |

| Standoff                 | A1               | 0.05        | -        | _     |  |  |

| Overall Width            | E                | 7.40        | 7.80     | 8.20  |  |  |

| Molded Package Width     | E1               | 5.00        | 5.30     | 5.60  |  |  |

| Overall Length           | D                | 9.90        | 10.20    | 10.50 |  |  |

| Foot Length              | L                | 0.55        | 0.75     | 0.95  |  |  |

| Footprint                | Footprint L1     |             |          |       |  |  |

| Lead Thickness           | С                | 0.09        | -        | 0.25  |  |  |

| Foot Angle               | φ                | 0°          | 4°       | 8°    |  |  |

| Lead Width               | b                | 0.22        | -        | 0.38  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

## THE MICROCHIP WEB SITE

Microchip provides online support via our web site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://www.microchip.com/support