Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 24                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-QFN (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f886-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Davias    | Program<br>Memory | Data N          | Data Memory       |     | 10-bit A/D | ECCP/ | EUSART | MSSP | Commonatorio | Timers   |  |

|-----------|-------------------|-----------------|-------------------|-----|------------|-------|--------|------|--------------|----------|--|

| Device    | Flash<br>(words)  | SRAM<br>(bytes) | EEPROM<br>(bytes) | I/O | (ch)       | ССР   | EUSARI | MOOP | Comparators  | 8/16-bit |  |

| PIC16F882 | 2048              | 128             | 128               | 24  | 11         | 1/1   | 1      | 1    | 2            | 2/1      |  |

| PIC16F883 | 4096              | 256             | 256               | 24  | 11         | 1/1   | 1      | 1    | 2            | 2/1      |  |

| PIC16F884 | 4096              | 256             | 256               | 35  | 14         | 1/1   | 1      | 1    | 2            | 2/1      |  |

| PIC16F886 | 8192              | 368             | 256               | 24  | 11         | 1/1   | 1      | 1    | 2            | 2/1      |  |

| PIC16F887 | 8192              | 368             | 256               | 35  | 14         | 1/1   | 1      | 1    | 2            | 2/1      |  |

# PIC16F882/883/884/886/887 Family Types

| TABL | E 5:        | 5: 44-PIN TQFP ALLOCATION TABLE (PIC16F884/887) |             |             |          |        |         |           |         |                 |

|------|-------------|-------------------------------------------------|-------------|-------------|----------|--------|---------|-----------|---------|-----------------|

| 0/1  | 44-Pin TQFP | Analog                                          | Comparators | Timers      | ECCP     | EUSART | MSSP    | Interrupt | Pull-up | Basic           |

| RA0  | 19          | AN0/ULPWU                                       | C12IN0-     | —           | —        |        | —       | —         | _       | —               |

| RA1  | 20          | AN1                                             | C12IN1-     | —           | —        | _      | —       | —         | _       | _               |

| RA2  | 21          | AN2                                             | C2IN+       | —           | —        | _      | —       | —         | —       | VREF-/CVREF     |

| RA3  | 22          | AN3                                             | C1IN+       | —           | —        | _      | —       | —         | _       | VREF+           |

| RA4  | 23          | —                                               | C1OUT       | TOCKI       | —        |        | —       | _         |         | —               |

| RA5  | 24          | AN4                                             | C2OUT       | —           | —        |        | SS      | —         | _       | —               |

| RA6  | 31          | —                                               | —           | —           | —        |        | —       | —         |         | OSC2/CLKOUT     |

| RA7  | 30          | —                                               | —           | —           | —        |        | —       | —         | _       | OSC1/CLKIN      |

| RB0  | 8           | AN12                                            | —           | —           | —        | _      | _       | IOC/INT   | Y       | —               |

| RB1  | 9           | AN10                                            | C12IN3-     | —           | —        | -      | —       | IOC       | Y       | —               |

| RB2  | 10          | AN8                                             | —           | —           | —        |        | —       | IOC       | Y       | —               |

| RB3  | 11          | AN9                                             | C12IN2-     | —           | —        | -      | —       | IOC       | Y       | PGM             |

| RB4  | 14          | AN11                                            | —           | —           | _        | _      | _       | IOC       | Y       | —               |

| RB5  | 15          | AN13                                            | _           | T1G         | —        | _      | _       | IOC       | Y       | _               |

| RB6  | 16          | —                                               | —           | —           | _        | _      | _       | IOC       | Y       | ICSPCLK         |

| RB7  | 17          | —                                               | _           | —           | _        | _      | _       | IOC       | Y       | ICSPDAT         |

| RC0  | 32          | —                                               | _           | T1OSO/T1CKI | _        | _      | _       | _         |         | _               |

| RC1  | 35          | —                                               |             | T1OSI       | CCP2     | _      | _       | _         | _       | _               |

| RC2  | 36          |                                                 | —           | _           | CCP1/P1A | _      | _       | —         | _       | _               |

| RC3  | 37          |                                                 |             |             | _        |        | SCK/SCL | _         |         |                 |

| RC4  | 42          |                                                 | —           | _           | —        | _      | SDI/SDA | —         | _       | _               |

| RC5  | 43          |                                                 |             |             | _        |        | SDO     | _         |         |                 |

| RC6  | 44          | _                                               | _           | _           | —        | TX/CK  | _       | —         | —       | _               |

| RC7  | 1           |                                                 | _           | _           | _        | RX/DT  | _       | —         |         | _               |

| RD0  | 38          |                                                 | _           |             | _        | _      | _       | —         |         |                 |

| RD1  | 39          |                                                 | _           |             | _        |        | _       | _         |         | _               |

| RD2  | 40          |                                                 | _           |             | _        | _      | _       | —         |         |                 |

| RD3  | 41          |                                                 |             |             | _        |        | _       | _         |         |                 |

| RD4  | 2           | _                                               | _           | _           | —        | _      | _       | —         | —       | _               |

| RD5  | 3           |                                                 |             |             | P1B      |        | _       | _         |         | _               |

| RD6  | 4           |                                                 | —           | _           | P1C      | _      | _       | —         | _       | _               |

| RD7  | 5           |                                                 | _           | _           | P1D      |        | _       | —         |         | _               |

| RE0  | 25          | AN5                                             | _           | _           | _        | _      | _       | _         |         | _               |

| RE1  | 26          | AN6                                             | _           | _           | _        |        | _       | —         |         | _               |

| RE2  | 27          | AN7                                             |             | —           | —        | _      | —       |           | _       | _               |

| RE3  | 18          | _                                               | _           | _           | _        | _      | _       | _         | Y(1)    | MCLR/VPP        |

|      | 7           |                                                 |             | —           |          |        | _       |           | _       | Vdd             |

| _    | 28          | _                                               | _           | _           | _        | _      | _       | _         | _       | Vdd             |

| _    | 6           |                                                 | _           | _           | _        | _      | _       | _         |         | Vss             |

|      | 13          | _                                               | _           |             | _        | _      | _       | —         | _       | NC (no connect) |

|      | 29          | _                                               | _           |             | _        | _      | _       | _         |         | Vss             |

|      | 34          | _                                               | _           | _           | _        | _      | _       | _         | _       | NC (no connect) |

|      | 33          | _                                               | _           | _           | —        |        | _       | _         |         | NC (no connect) |

| _    | 12          | _                                               | _           | _           | _        | _      | _       | _         | _       | NC (no connect) |

| L    |             | L                                               |             |             | 1        | 1      | 1       | I         |         | , -7            |

**Note 1:** Pull-up activated only with external MCLR configuration.

| Addr   | Name    | Bit 7       | Bit 6          | Bit 5         | Bit 4                  | Bit 3         | Bit 2           | Bit 1          | Bit 0               | Value on<br>POR, BOR | Value on all other Resets |

|--------|---------|-------------|----------------|---------------|------------------------|---------------|-----------------|----------------|---------------------|----------------------|---------------------------|

| Bank 2 | 2       |             |                |               |                        |               |                 |                |                     |                      |                           |

| 100h   | INDF    | Addressing  | g this locatio | n uses conte  | ents of FSR to a       | address data  | memory (not     | t a physical r | egister)            | XXXX XXXX            | xxxx xxxx                 |

| 101h   | TMR0    | Timer0 Mo   | dule Registe   | er            |                        |               |                 |                |                     | XXXX XXXX            | uuuu uuuu                 |

| 102h   | PCL     | Program C   | ounter's (PC   | C) Least Sigr | nificant Byte          |               |                 |                |                     | 0000 0000            | 0000 0000                 |

| 103h   | STATUS  | IRP         | RP1            | RP0           | TO                     | PD            | Z               | DC             | С                   | 0001 1xxx            | 000q quuu <b>(3)</b>      |

| 104h   | FSR     | Indirect Da | ta Memory A    | Address Poir  | nter                   |               |                 |                |                     | xxxx xxxx            | uuuu uuuu                 |

| 105h   | WDTCON  | —           | —              | —             | WDTPS3                 | WDTPS2        | WDTPS1          | WDTPS0         | SWDTEN              | 0 1000               | 0 1000                    |

| 106h   | PORTB   | RB7         | RB6            | RB5           | RB4                    | RB3           | RB2             | RB1            | RB0                 | XXXX XXXX            | 0000 0000                 |

| 107h   | CM1CON0 | C10N        | C1OUT          | C1OE          | C1POL                  | _             | C1R             | C1CH1          | C1CH0               | 0000 -000            | 0000 0-00                 |

| 108h   | CM2CON0 | C2ON        | C2OUT          | C2OE          | C2POL                  | _             | C2R             | C2CH1          | C2CH0               | 0000 -000            | 0000 0-00                 |

| 109h   | CM2CON1 | MC1OUT      | MC2OUT         | C1RSEL        | C2RSEL                 | _             | _               | T1GSS          | C2SYNC              | 000010               | 0000 00                   |

| 10Ah   | PCLATH  | _           | _              | _             | Write Buff             | er for the up | per 5 bits of t | he Program     | Counter             | 0 0000               | 0 0000                    |

| 10Bh   | INTCON  | GIE         | PEIE           | TOIE          | INTE                   | RBIE          | T0IF            | INTF           | RBIF <sup>(1)</sup> | 0000 000x            | 0000 000u                 |

| 10Ch   | EEDAT   | EEDAT7      | EEDAT6         | EEDAT5        | EEDAT4                 | EEDAT3        | EEDAT2          | EEDAT1         | EEDAT0              | 0000 0000            | 0000 0000                 |

| 10Dh   | EEADR   | EEADR7      | EEADR6         | EEADR5        | EEADR4                 | EEADR3        | EEADR2          | EEADR1         | EEADR0              | 0000 0000            | 0000 0000                 |

| 10Eh   | EEDATH  | —           | —              | EEDATH5       | EEDATH4                | EEDATH3       | EEDATH2         | EEDATH1        | EEDATH0             | 00 0000              | 00 0000                   |

| 10Fh   | EEADRH  | _           | _              | _             | EEADRH4 <sup>(2)</sup> | EEADRH3       | EEADRH2         | EEADRH1        | EEADRH0             | 0000                 | 0 0000                    |

TABLE 2-3: PIC16F882/883/884/886/887 SPECIAL FUNCTION REGISTERS SUMMARY BANK 2

**Legend:** -= Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented **Note 1:** MCLR and WDT Reset does not affect the previous value data latch. The RBIF bit will be cleared upon Reset but will set again if the mismatch exists.

2: PIC16F886/PIC16F887 only.

3: See Table 14-5 for Reset value for specific condition.

| TABLE 2-4: | PIC16F882/883/884/886/887 SPECIAL FUNCTION REGISTERS SUMMARY BANK 3 |

|------------|---------------------------------------------------------------------|

|            |                                                                     |

| Addr   | Name       | Bit 7               | Bit 6                                              | Bit 5               | Bit 4         | Bit 3         | Bit 2         | Bit 1         | Bit 0               | Value on<br>POR, BOR | Value on all other Resets |

|--------|------------|---------------------|----------------------------------------------------|---------------------|---------------|---------------|---------------|---------------|---------------------|----------------------|---------------------------|

| Bank 3 | ank 3      |                     |                                                    |                     |               |               |               |               |                     |                      |                           |

| 180h   | INDF       | Addressing          | this location                                      | n uses conte        | ents of FSR   | to address of | data memory   | / (not a phys | ical register)      | xxxx xxxx            | xxxx xxxx                 |

| 181h   | OPTION_REG | RBPU                | INTEDG                                             | TOCS                | TOSE          | PSA           | PS2           | PS1           | PS0                 | 1111 1111            | 1111 1111                 |

| 182h   | PCL        | Program C           | ounter's (PC                                       | C) Least Sigr       | nificant Byte | 9             |               |               |                     | 0000 0000            | 0000 0000                 |

| 183h   | STATUS     | IRP                 | RP1                                                | RP0                 | TO            | PD            | Z             | DC            | С                   | 0001 1xxx            | 000q quuu <b>(3)</b>      |

| 184h   | FSR        | Indirect Da         | ta Memory A                                        | Address Poir        | nter          |               |               |               |                     | xxxx xxxx            | uuuu uuuu                 |

| 185h   | SRCON      | SR1                 | SR0                                                | C1SEN               | C2REN         | PULSS         | PULSR         | —             | FVREN               | 0000 00-0            | 0000 00-0                 |

| 186h   | TRISB      | TRISB7              | TRISB6                                             | TRISB5              | TRISB4        | TRISB3        | TRISB2        | TRISB1        | TRISB0              | 1111 1111            | 1111 1111                 |

| 187h   | BAUDCTL    | ABDOVF              | RCIDL                                              |                     | SCKP          | BRG16         |               | WUE           | ABDEN               | 01-0 0-00            | 01-0 0-00                 |

| 188h   | ANSEL      | ANS7 <sup>(2)</sup> | ANS6 <sup>(2)</sup>                                | ANS5 <sup>(2)</sup> | ANS4          | ANS3          | ANS2          | ANS1          | ANS0                | 1111 1111            | 1111 1111                 |

| 189h   | ANSELH     |                     | _                                                  | ANS13               | ANS12         | ANS11         | ANS10         | ANS9          | ANS8                | 11 1111              | 1111 1111                 |

| 18Ah   | PCLATH     |                     | _                                                  |                     | Write Buffe   | er for the up | per 5 bits of | the Program   | Counter             | 0 0000               | 0 0000                    |

| 18Bh   | INTCON     | GIE                 | PEIE                                               | TOIE                | INTE          | RBIE          | T0IF          | INTF          | RBIF <sup>(1)</sup> | 0000 000x            | 0000 000u                 |

| 18Ch   | EECON1     | EEPGD               | _                                                  | -                   |               | WRERR         | WREN          | WR            | RD                  | x x000               | q000                      |

| 18Dh   | EECON2     | EEPROM              | EPROM Control Register 2 (not a physical register) |                     |               |               |               |               |                     |                      |                           |

Legend:-= Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplementedNote1:MCLR and WDT Reset does not affect the previous value data latch. The RBIF bit will be cleared upon Reset but will set again if the mismatch exists.

2: PIC16F884/PIC16F887 only.

3: See Table 14-5 for Reset value for specific condition.

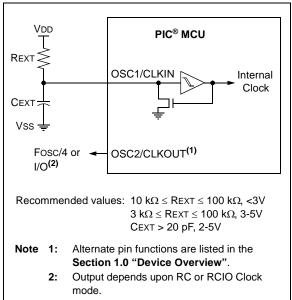

#### 4.4.4 EXTERNAL RC MODES

The external Resistor-Capacitor (RC) modes support the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required. There are two modes: RC and RCIO.

In RC mode, the RC circuit connects to OSC1. OSC2/ CLKOUT outputs the RC oscillator frequency divided by 4. This signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements. Figure 4-5 shows the external RC mode connections.

FIGURE 4-5: EXTERNAL RC MODES

In RCIO mode, the RC circuit is connected to OSC1. OSC2 becomes an additional general purpose I/O pin.

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- threshold voltage variation

- component tolerances

- packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

### 4.5 Internal Clock Modes

The oscillator module has two independent, internal oscillators that can be configured or selected as the system clock source.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory calibrated and operates at 8 MHz. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 4-2).

- 2. The **LFINTOSC** (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<2:0> of the OSCCON register.

The system clock can be selected between external or internal clock sources via the System Clock Selection (SCS) bit of the OSCCON register. See **Section 4.6** "**Clock Switching**" for more information.

#### 4.5.1 INTOSC AND INTOSCIO MODES

The INTOSC and INTOSCIO modes configure the internal oscillators as the system clock source when the device is programmed using the oscillator selection or the FOSC<2:0> bits in the Configuration Word Register 1 (CONFIG1).

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT outputs the selected internal oscillator frequency divided by 4. The CLKOUT signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements.

In **INTOSCIO** mode, OSC1/CLKIN and OSC2/CLKOUT are available for general purpose I/O.

#### 4.5.2 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a factory calibrated 8 MHz internal clock source. The frequency of the HFINTOSC can be altered via software using the OSCTUNE register (Register 4-2).

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 4-1). One of seven frequencies can be selected via software using the IRCF<2:0> bits of the OSCCON register. See **Section 4.5.4 "Frequency Select Bits (IRCF)"** for more information.

The HFINTOSC is enabled by selecting any frequency between 8 MHz and 125 kHz by setting the IRCF<2:0> bits of the OSCCON register  $\neq$  000. Then, set the System Clock Source (SCS) bit of the OSCCON register to '1' or enable Two-Speed Start-up by setting the IESO bit in the Configuration Word Register 1 (CONFIG1) to '1'.

The HF Internal Oscillator (HTS) bit of the OSCCON register indicates whether the HFINTOSC is stable or not.

### 8.8 Additional Comparator Features

There are three additional comparator features:

- Timer1 count enable (gate)

- Synchronizing output with Timer1

- Simultaneous read of comparator outputs

## 8.8.1 COMPARATOR C2 GATING TIMER1

This feature can be used to time the duration or interval of analog events. Clearing the T1GSS bit of the CM2CON1 register will enable Timer1 to increment based on the output of Comparator C2. This requires that Timer1 is on and gating is enabled. See **Section 6.0 "Timer1 Module with Gate Control"** for details.

It is recommended to synchronize the comparator with Timer1 by setting the C2SYNC bit when the comparator is used as the Timer1 gate source. This ensures Timer1 does not miss an increment if the comparator changes during an increment.

### 8.8.2 SYNCHRONIZING COMPARATOR C2 OUTPUT TO TIMER1

The Comparator C2 output can be synchronized with Timer1 by setting the C2SYNC bit of the CM2CON1 register. When enabled, the C2 output is latched on the falling edge of the Timer1 clock source. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figures 8-2 and 8-3) and the Timer1 Block Diagram (Figure 6-1) for more information.

#### 8.8.3 SIMULTANEOUS COMPARATOR OUTPUT READ

The MC1OUT and MC2OUT bits of the CM2CON1 register are mirror copies of both comparator outputs. The ability to read both outputs simultaneously from a single register eliminates the timing skew of reading separate registers.

Note 1: Obtaining the status of C1OUT or C2OUT by reading CM2CON1 does not affect the comparator interrupt mismatch registers.

### REGISTER 8-3: CM2CON1: COMPARATOR C2 CONTROL REGISTER 1

| R-0    | R-0    | R/W-0  | R/W-0  | U-0 | U-0 | R/W-1 | R/W-0  |

|--------|--------|--------|--------|-----|-----|-------|--------|

| MC1OUT | MC2OUT | C1RSEL | C2RSEL | —   |     | T1GSS | C2SYNC |

| bit 7  |        |        |        |     |     |       | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | MC10UT: Mirror Copy of C10UT bit                                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                                                                                                                                                         |

| bit 6   | MC2OUT: Mirror Copy of C2OUT bit                                                                                                                        |

| bit 5   | C1RSEL: Comparator C1 Reference Select bit                                                                                                              |

|         | 1 = CVREF routed to C1VREF input of Comparator C1                                                                                                       |

|         | <ul> <li>0 = Absolute voltage reference (0.6) routed to C1VREF input of Comparator C1 (or 1.2V precision<br/>reference on parts so equipped)</li> </ul> |

| bit 4   | C2RSEL: Comparator C2 Reference Select bit                                                                                                              |

|         | 1 = CVREF routed to C2VREF input of Comparator C2                                                                                                       |

|         | 0 = Absolute voltage reference (0.6) routed to C2VREF input of Comparator C2 (or 1.2V precision                                                         |

|         | reference on parts so equipped)                                                                                                                         |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                              |

| bit 1   | T1GSS: Timer1 Gate Source Select bit                                                                                                                    |

|         | 1 = Timer1 gate source is $\overline{T1G}$                                                                                                              |

|         | 0 = Timer1 gate source is SYNCC2OUT.                                                                                                                    |

| bit 0   | C2SYNC: Comparator C2 Output Synchronization bit                                                                                                        |

|         | 1 = Output is synchronous to falling edge of Timer1 clock                                                                                               |

|         | 0 = Output is asynchronous                                                                                                                              |

|         |                                                                                                                                                         |

# 10.1.4 READING THE FLASH PROGRAM MEMORY

To read a program memory location, the user must write the Least and Most Significant address bits to the EEADR and EEADRH registers, set the EEPGD control bit of the EECON1 register, and then set control bit RD. Once the read control bit is set, the program memory Flash controller will use the second instruction immediately following the "BSF EECON1, RD" instruction to be ignored. The data is available in the very next cycle, in the EEDAT and EEDATH registers; therefore, it can be read as two bytes in the following instructions.

# EEDAT and EEDATH registers will hold this value until another read or until it is written to by the user.

- Note 1: The two instructions following a program memory read are required to be NOPS. This prevents the user from executing a 2-cycle instruction on the next instruction after the RD bit is set.

- If the WR bit is set when EEPGD = 1, it will be immediately reset to '0' and no operation will take place.

### EXAMPLE 10-3: FLASH PROGRAM READ

|                      | BANKSEL | EEADR           | ;                                                        |

|----------------------|---------|-----------------|----------------------------------------------------------|

|                      | MOVLW   | MS_PROG_EE_ADDR | ;                                                        |

|                      | MOVWF   | EEADRH          | ;MS Byte of Program Address to read                      |

|                      | MOVLW   | LS_PROG_EE_ADDR | ;                                                        |

|                      | MOVWF   | EEADR           | ;LS Byte of Program Address to read                      |

|                      | BANKSEL | EECON1          | ;                                                        |

|                      | BSF     | EECON1, EEPGD   | ;Point to PROGRAM memory                                 |

| pa eo                | BSF     | EECON1, RD      | ;EE Read                                                 |

| Required<br>Sequence | NOP     |                 | ;First instruction after BSF EECON1,RD executes normally |

|                      | NOP     |                 | ;Any instructions here are ignored as program            |

| <b></b>              |         |                 | ;memory is read in second cycle after BSF EECON1,RD      |

| ;                    |         |                 |                                                          |

|                      | BANKSEL |                 | ;                                                        |

|                      | MOVF    | EEDAT, W        | ;W = LS Byte of Program Memory                           |

|                      | MOVWF   | LOWPMBYTE       | i                                                        |

|                      | MOVF    | EEDATH, W       | ;W = MS Byte of Program EEDAT                            |

|                      | MOVWF   | HIGHPMBYTE      | ;                                                        |

|                      | BCF     | STATUS, RP1     | ;Bank 0                                                  |

|                      |         |                 |                                                          |

## 11.5.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to multiple registers: CCPRxL register and DCxB<1:0> bits of the CCPxCON register. The CCPRxL contains the eight MSbs and the DCxB<1:0> bits of the CCPxCON register contain the two LSbs. CCPRxL and DCxB<1:0> bits of the CCPxCON register can be written to at any time. The duty cycle value is not latched into CCPRxH until after the period completes (i.e., a match between PR2 and TMR2 registers occurs). While using the PWM, the CCPRxH register is read-only.

Equation 11-2 is used to calculate the PWM pulse width.

Equation 11-3 is used to calculate the PWM duty cycle ratio.

### EQUATION 11-2: PULSE WIDTH

Pulse Width = (CCPRxL:CCPxCON<5:4>) • Tosc • (TMR2 Prescale Value)

# EQUATION 11-3: DUTY CYCLE RATIO

$Duty Cycle Ratio = \frac{(CCPRxL:CCPxCON < 5:4>)}{4(PR2 + 1)}$

The CCPRxH register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH and 2-bit latch, then the CCPx pin is cleared (see Figure 11-3).

### 11.5.4 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 11.5.5 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 4.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for additional details.

#### 11.5.6 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 11.5.7 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Disable the PWM pin (CCPx) output drivers as an input by setting the associated TRIS bit.

- 2. Set the PWM period by loading the PR2 register.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- Set the PWM duty cycle by loading the CCPRxL register and DCxB<1:0> bits of the CCPxCON register.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register.

- Set the Timer2 prescale value by loading the T2CKPS bits of the T2CON register.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output after a new PWM cycle has started:

- Wait until Timer2 overflows (TMR2IF bit of the PIR1 register is set).

- Enable the CCPx pin output driver by clearing the associated TRIS bit.

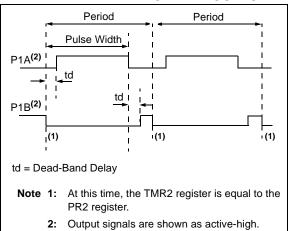

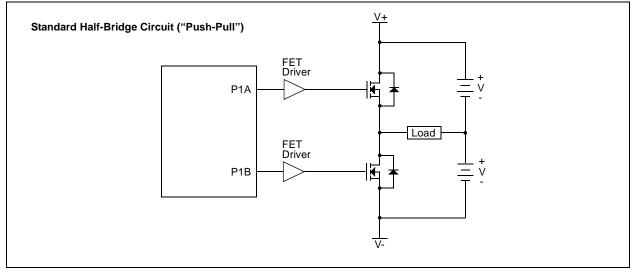

#### 11.6.6 PROGRAMMABLE DEAD-BAND DELAY MODE

In Half-Bridge applications where all power switches are modulated at the PWM frequency, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on, and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shoot-through current*) will flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In Half-Bridge mode, a digitally programmable deadband delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 11-17 for illustration. The lower seven bits of the associated PWM1CON register (Register 11-4) sets the delay period in terms of microcontroller instruction cycles (Tcy or 4 Tosc).

#### FIGURE 11-17: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

### FIGURE 11-18: EXAMPLE OF HALF-BRIDGE APPLICATIONS

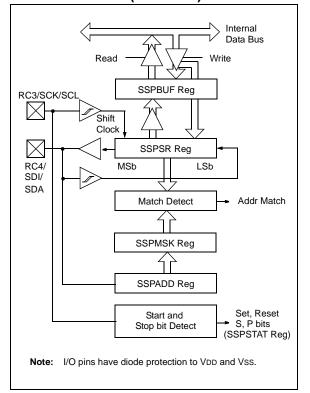

# 13.4 MSSP I<sup>2</sup>C Operation

The MSSP module in I<sup>2</sup>C mode, fully implements all master and slave functions (including general call support) and provides interrupts on Start and Stop bits in hardware, to determine a free bus (Multi-Master mode). The MSSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RC3/SCK/SCL pin, which is the clock (SCL), and the RC4/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

The MSSP module functions are enabled by setting MSSP Enable bit SSPEN of the SSPCON register.

FIGURE 13-6: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The MSSP module has these six registers for  $I^2C$  operation:

- MSSP Control Register 1 (SSPCON)

- MSSP Control Register 2 (SSPCON2)

- MSSP STATUS register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

- MSSP Address register (SSPADD)

- MSSP Mask register (SSPMSK)

The SSPCON register allows control of the  $I^2C$  operation. The SSPM<3:0> mode selection bits (SSPCON register) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Master mode, clock = OSC/4 (SSPADD +1)

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address), with Start and Stop bit interrupts enabled

- I<sup>2</sup>C firmware controlled master operation, slave is idle

Selection of any  $I^2C$  mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain, provided these pins are programmed to be inputs by setting the appropriate TRISC bits.

#### 13.4.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse and load the SSPBUF register with the received value currently in the SSPSR register.

If either or both of the following <u>conditions</u> are true, the MSSP module will not give this ACK pulse:

- a) The buffer full bit BF (SSPCON register) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON register) was set before the transfer was received.

In this event, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF of the PIR1 register is set. The BF bit is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, are shown in timing parameter #100 and parameter #101.

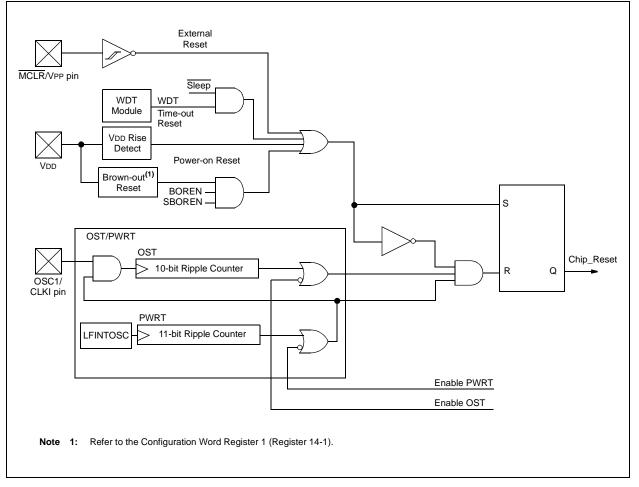

# 14.2 Reset

The PIC16F882/883/884/886/887 devices differentiate between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- c) WDT Reset during Sleep

- d) MCLR Reset during normal operation

- e) MCLR Reset during Sleep

- f) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- Power-on Reset

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

- Brown-out Reset (BOR)

They are not affected by a WDT Wake-up since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different Reset situations, as indicated in Table 14-2. These bits are used in software to determine the nature of the Reset. See Table 14-5 for a full description of Reset states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 14-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See **Section 17.0** "**Electrical Specifications**" for pulse-width specifications.

#### FIGURE 14-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| MOVF             | Move f                                                                                                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] MOVF f,d                                                                                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                          |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                                                                                                                                          |

| Description:     | The contents of register 'f' is<br>moved to a destination dependent<br>upon the status of 'd'. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register 'f'<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |

| Words:           | 1                                                                                                                                                                                                                                                                                          |

| Cycles:          | 1                                                                                                                                                                                                                                                                                          |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                                |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                                 |

| MOVWF            | Move W to f                                |

|------------------|--------------------------------------------|

| Syntax:          | [ label ] MOVWF f                          |

| Operands:        | $0 \leq f \leq 127$                        |

| Operation:       | $(W) \rightarrow (f)$                      |

| Status Affected: | None                                       |

| Description:     | Move data from W register to register 'f'. |

| Words:           | 1                                          |

| Cycles:          | 1                                          |

| Example:         | MOVW OPTION<br>F                           |

|                  | Before Instruction                         |

|                  | OPTION = 0xFF                              |

|                  | W = 0x4F                                   |

|                  | After Instruction                          |

|                  | OPTION = 0x4F                              |

|                  | W = 0x4F                                   |

|                  |                                            |

| MOVLW            | Move literal to W                                                                         |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                  |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                       |  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                       |  |  |  |  |  |  |

| Status Affected: | None                                                                                      |  |  |  |  |  |  |

| Description:     | The 8-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |  |  |  |  |  |  |

| Words:           | 1                                                                                         |  |  |  |  |  |  |

| Cycles:          | 1                                                                                         |  |  |  |  |  |  |

| Example:         | MOVLW 0x5A                                                                                |  |  |  |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                             |  |  |  |  |  |  |

| NOP              | No Operation  |  |  |  |  |

|------------------|---------------|--|--|--|--|

| Syntax:          | [label] NOP   |  |  |  |  |

| Operands:        | None          |  |  |  |  |

| Operation:       | No operation  |  |  |  |  |

| Status Affected: | None          |  |  |  |  |

| Description:     | No operation. |  |  |  |  |

| Words:           | 1             |  |  |  |  |

| Cycles:          | 1             |  |  |  |  |

| Example:         | NOP           |  |  |  |  |

# 16.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 16.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 16.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 16.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 16.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

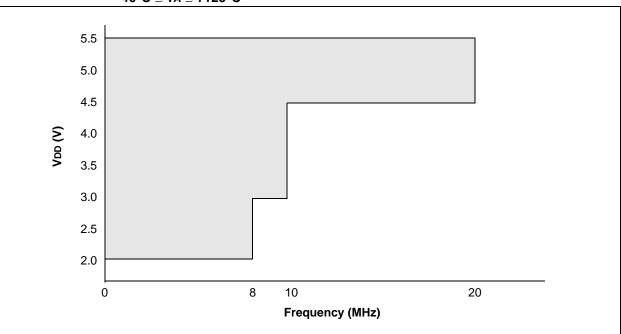

FIGURE 17-1: PIC16F882/883/884/886/887 VOLTAGE-FREQUENCY GRAPH, -40°C  $\leq$  TA  $\leq$  +125°C

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

## 17.5 DC Characteristics: PIC16F882/883/884/886/887-I (Industrial) PIC16F882/883/884/886/887-E (Extended)

| DC CHARACTERISTICS |      |                                                 |                |           | (unless otherwise stated)<br>$C \le TA \le +85^{\circ}C$ for industrial<br>$C \le TA \le +125^{\circ}C$ for extended |       |                                                                    |

|--------------------|------|-------------------------------------------------|----------------|-----------|----------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------------------------------|

| Param<br>No.       | Sym. | Characteristic                                  | Min.           | Тур†      | Max.                                                                                                                 | Units | Conditions                                                         |

|                    | VIL  | Input Low Voltage                               |                |           |                                                                                                                      |       |                                                                    |

|                    |      | I/O Port:                                       |                |           |                                                                                                                      |       |                                                                    |

| D030               |      | with TTL buffer                                 | Vss            | —         | 0.8                                                                                                                  | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                   |

| D030A              |      |                                                 | Vss            | —         | 0.15 Vdd                                                                                                             | V     | $2.0V \le VDD \le 4.5V$                                            |

| D031               |      | with Schmitt Trigger buf-<br>fer                | Vss            | _         | 0.2 Vdd                                                                                                              | V     | $2.0V \leq V\text{dd} \leq 5.5V$                                   |

| D032               |      | MCLR, OSC1 (RC mode) <sup>(1)</sup>             | Vss            | _         | 0.2 Vdd                                                                                                              | V     |                                                                    |

| D033               |      | OSC1 (XT and LP modes)                          | Vss            | —         | 0.3                                                                                                                  | V     |                                                                    |

| D033A              |      | OSC1 (HS mode)                                  | Vss            | _         | 0.3 Vdd                                                                                                              | V     |                                                                    |

|                    | Vih  | Input High Voltage                              |                |           |                                                                                                                      |       |                                                                    |

| _                  |      | I/O ports:                                      |                | —         |                                                                                                                      |       |                                                                    |

| D040               |      | with TTL buffer                                 | 2.0            | —         | Vdd                                                                                                                  | V     | $4.5V \le VDD \le 5.5V$                                            |

| D040A              |      |                                                 | 0.25 VDD + 0.8 | —         | Vdd                                                                                                                  | V     | $2.0V \le VDD \le 4.5V$                                            |

| D041               |      | with Schmitt Trigger buffer                     |                | —         | Vdd                                                                                                                  | V     | $2.0V \leq V\text{DD} \leq 5.5V$                                   |

| D042               |      | MCLR                                            | 0.8 Vdd        | —         | Vdd                                                                                                                  | V     |                                                                    |

| D043               |      | OSC1 (XT and LP modes)                          | 1.6            | —         | Vdd                                                                                                                  | V     |                                                                    |

| D043A              |      | OSC1 (HS mode)                                  | 0.7 Vdd        | —         | Vdd                                                                                                                  | V     |                                                                    |

| D043B              |      | OSC1 (RC mode)                                  | 0.9 Vdd        | —         | Vdd                                                                                                                  | V     | (Note 1)                                                           |

|                    | lı∟  | Input Leakage Current <sup>(2)</sup>            |                |           |                                                                                                                      |       |                                                                    |

| D060               |      | I/O ports                                       | —              | ± 0.1     | ± 1                                                                                                                  | μA    | $Vss \le VPIN \le VDD,$ Pin at high-impedance                      |

| D061               |      | MCLR <sup>(3)</sup>                             | —              | $\pm 0.1$ | ± 5                                                                                                                  | μΑ    | $VSS \leq VPIN \leq VDD$                                           |

| D063               |      | OSC1                                            | —              | ± 0.1     | ± 5                                                                                                                  | μA    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP oscillator configuration |

| D070*              | IPUR | PORTB Weak Pull-up Cur-<br>rent                 | 50             | 250       | 400                                                                                                                  | μΑ    | VDD = 5.0V, VPIN = VSS                                             |

|                    | Vol  | Output Low Voltage <sup>(5)</sup>               |                |           |                                                                                                                      |       |                                                                    |

| D080               |      | I/O ports                                       | _              | -         | 0.6                                                                                                                  | V     | IOL = 8.5 mA, VDD = 4.5V<br>(Ind.)                                 |

| D090               | Vон  | Output High Voltage <sup>(5)</sup><br>I/O ports | Vdd - 0.7      | _         | _                                                                                                                    | V     | Іон = -3.0 mA, Vdd = 4.5V<br>(Ind.)                                |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

**3:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: See Section 10.3.1 "Using the Data EEPROM" for additional information.

5: Including OSC2 in CLKOUT mode.

## 17.5 DC Characteristics: PIC16F882/883/884/886/887-I (Industrial) PIC16F882/883/884/886/887-E (Extended) (Continued)

| DC CHARACTERISTICS |       | Standard Operating Co<br>Operating temperature                      |      | nditions (unless otherwise stated)<br>-40°C ≤ TA ≤ +85°C for industrial<br>-40°C ≤ TA ≤ +125°C for extended |      |       |                                                                                                     |

|--------------------|-------|---------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------|------|-------|-----------------------------------------------------------------------------------------------------|

| Param<br>No.       | Sym.  | Characteristic                                                      | Min. | Тур†                                                                                                        | Max. | Units | Conditions                                                                                          |

| D100               | IULP  | Ultra Low-Power Wake-Up<br>Current                                  | _    | 200                                                                                                         | _    | nA    | See Application Note AN879,<br>"Using the Microchip Ultra<br>Low-Power Wake-up Module"<br>(DS00879) |

|                    |       | Capacitive Loading Specs<br>on Output Pins                          |      |                                                                                                             |      |       |                                                                                                     |

| D101*              | COSC2 | OSC2 pin                                                            | _    | -                                                                                                           | 15   | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1                              |

| D101A<br>*         | Сю    | All I/O pins                                                        | _    | —                                                                                                           | 50   | pF    |                                                                                                     |

|                    |       | Data EEPROM Memory                                                  |      |                                                                                                             |      |       |                                                                                                     |

| D120               | ED    | Byte Endurance                                                      | 100K | 1M                                                                                                          | —    | E/W   | $-40^{\circ}C \le TA \le +85^{\circ}C$                                                              |

| D120A              | ED    | Byte Endurance                                                      | 10K  | 100K                                                                                                        | _    | E/W   | $+85^{\circ}C \leq TA \leq +125^{\circ}C$                                                           |

| D121               | Vdrw  | VDD for Read/Write                                                  | Vmin | -                                                                                                           | 5.5  | V     | Using EECON1 to read/write<br>VMIN = Minimum operating<br>voltage                                   |

| D122               | TDEW  | Erase/Write Cycle Time                                              | _    | 5                                                                                                           | 6    | ms    |                                                                                                     |

| D123               | Tretd | Characteristic Retention                                            | 40   | —                                                                                                           | —    | Year  | Provided no other specifications are violated                                                       |

| D124               | Tref  | Number of Total Erase/Write<br>Cycles before Refresh <sup>(4)</sup> | 1M   | 10M                                                                                                         | —    | E/W   | $-40^{\circ}C \le TA \le +85^{\circ}C$                                                              |

|                    |       | Program Flash Memory                                                |      |                                                                                                             |      |       |                                                                                                     |

| D130               | Eр    | Cell Endurance                                                      | 10K  | 100K                                                                                                        | —    | E/W   | $-40^{\circ}C \le TA \le +85^{\circ}C$                                                              |

| D130A              | ED    | Cell Endurance                                                      | 1K   | 10K                                                                                                         | —    | E/W   | $+85^{\circ}C \leq TA \leq +125^{\circ}C$                                                           |

| D131               | Vpr   | VDD for Read                                                        | Vmin | —                                                                                                           | 5.5  | V     | VMIN = Minimum operating voltage                                                                    |

| D132               | VPEW  | VDD for Row Erase/Write                                             | VMIN |                                                                                                             | 5.5  | V     |                                                                                                     |

|                    |       | VDD for Bulk Erase Opera-<br>tions                                  | 4.5  | -                                                                                                           | 5.5  | V     |                                                                                                     |

| D133               | TPEW  | Erase/Write cycle time                                              | —    | 2                                                                                                           | 2.5  | ms    |                                                                                                     |

| D134               | Tretd | Characteristic Retention                                            | 40   | -                                                                                                           | —    | Year  | Provided no other specifications are violated                                                       |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

**3:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: See Section 10.3.1 "Using the Data EEPROM" for additional information.

5: Including OSC2 in CLKOUT mode.

#### TABLE 17-10: PIC16F882/883/884/886/887 A/D CONVERTER (ADC) CHARACTERISTICS

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                                      |            |      |          |       |                                                                     |

|----------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------|------------|------|----------|-------|---------------------------------------------------------------------|

| Param<br>No.                                                                                                         | Sym. | Characteristic                                       | Min.       | Тур† | Max.     | Units | Conditions                                                          |

| AD01                                                                                                                 | NR   | Resolution                                           | —          | _    | 10 bits  | bit   |                                                                     |

| AD02                                                                                                                 | EIL  | Integral Error                                       |            | —    | ±1       | LSb   | VREF = 5.12V                                                        |

| AD03                                                                                                                 | Edl  | Differential Error                                   |            | _    | ±1       | LSb   | No missing codes to 10 bits<br>VREF = 5.12V                         |

| AD04                                                                                                                 | EOFF | Offset Error                                         | 0          | +1.5 | +3.0     | LSb   | VREF = 5.12V                                                        |

| AD07                                                                                                                 | Egn  | Gain Error                                           | _          | _    | ±1       | LSb   | VREF = 5.12V                                                        |

| AD06<br>AD06A                                                                                                        | Vref | Reference Voltage <sup>(3)</sup>                     | 2.2<br>2.7 |      | —<br>Vdd | V     | Absolute minimum to ensure 1 LSb<br>accuracy                        |

| AD07                                                                                                                 | VAIN | Full-Scale Range                                     | Vss        | _    | Vref     | V     |                                                                     |

| AD08                                                                                                                 | ZAIN | Recommended<br>Impedance of Analog<br>Voltage Source | _          | _    | 10       | kΩ    |                                                                     |

| AD09*                                                                                                                | IREF | VREF Input Current <sup>(3)</sup>                    | 10         | _    | 1000     | μA    | During VAIN acquisition.<br>Based on differential of VHOLD to VAIN. |

|                                                                                                                      |      |                                                      | _          | _    | 50       | μA    | During A/D conversion cycle.                                        |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Total Absolute Error includes integral, differential, offset and gain errors.

2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

3: ADC VREF is from external VREF or VDD pin, whichever is selected as reference input.

4: When ADC is off, it will not consume any current other than leakage current. The power-down current specification includes any such leakage from the ADC module.

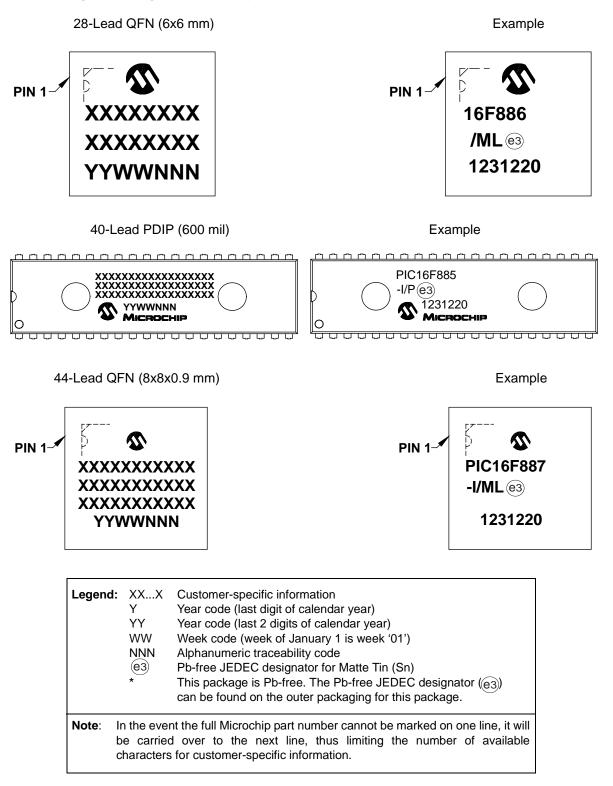

# **19.1** Package Marking Information (Continued)