#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 24                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 28-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f886-i-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IADL | LE Z: ZO-FIN QFN ALLOCATION TABLE (FICTOF002/003/000) |           |             |             |          |        |         |           |         |             |

|------|-------------------------------------------------------|-----------|-------------|-------------|----------|--------|---------|-----------|---------|-------------|

| 0/1  | 28-Pin QFN                                            | Analog    | Comparators | Timers      | ECCP     | EUSART | MSSP    | Interrupt | Pull-up | Basic       |

| RA0  | 27                                                    | AN0/ULPWU | C12IN0-     | —           |          |        | _       | —         | _       | —           |

| RA1  | 28                                                    | AN1       | C12IN1-     | —           | —        | _      | —       | _         | _       | _           |

| RA2  | 1                                                     | AN2       | C2IN+       | _           | _        | _      |         | _         |         | VREF-/CVREF |

| RA3  | 2                                                     | AN3       | C1IN+       | —           | _        |        | _       | _         | _       | VREF+       |

| RA4  | 3                                                     | —         | C1OUT       | TOCKI       | _        | _      |         | _         |         | _           |

| RA5  | 4                                                     | AN4       | C2OUT       | _           |          | _      | SS      | _         |         | _           |

| RA6  | 7                                                     | —         | _           | _           |          |        | _       | _         | _       | OSC2/CLKOUT |

| RA7  | 6                                                     | —         | _           | —           | —        | _      | —       | —         | _       | OSC1/CLKIN  |

| RB0  | 18                                                    | AN12      | _           | —           | _        | _      | _       | IOC/INT   | Y       | _           |

| RB1  | 19                                                    | AN10      | C12IN3-     | —           | P1C      | -      | _       | IOC       | Y       | —           |

| RB2  | 20                                                    | AN8       | _           | —           | P1B      | _      | —       | IOC       | Y       | —           |

| RB3  | 21                                                    | AN9       | C12IN2-     | —           | —        | _      | —       | IOC       | Y       | PGM         |

| RB4  | 22                                                    | AN11      | —           | —           | P1D      |        | _       | IOC       | Y       | —           |

| RB5  | 23                                                    | AN13      |             | T1G         | _        |        | _       | IOC       | Y       | —           |

| RB6  | 24                                                    | —         | _           | —           | _        | -      | _       | IOC       | Y       | ICSPCLK     |

| RB7  | 25                                                    | —         | —           | —           | —        |        | —       | IOC       | Y       | ICSPDAT     |

| RC0  | 8                                                     | —         | —           | T1OSO/T1CKI | _        |        | _       | —         |         | —           |

| RC1  | 9                                                     | —         |             | T1OSI       | CCP2     |        | _       | —         | —       | —           |

| RC2  | 10                                                    | —         |             | —           | CCP1/P1A |        |         | —         |         | —           |

| RC3  | 11                                                    | —         | —           | —           | —        |        | SCK/SCL | —         | —       | —           |

| RC4  | 12                                                    | —         | —           | _           | _        |        | SDI/SDA | _         |         | —           |

| RC5  | 13                                                    | —         | —           | —           | —        |        | SDO     | —         | _       | —           |

| RC6  | 14                                                    | —         | —           | _           | _        | TX/CK  | _       | _         |         | —           |

| RC7  | 15                                                    | —         | —           | —           | —        | RX/DT  | —       | —         | _       | —           |

| RE3  | 26                                                    | —         | _           | _           | —        | _      | —       | —         | Y(1)    | MCLR/VPP    |

| —    | 17                                                    | —         | _           | _           | _        |        | _       | _         | _       | Vdd         |

|      | 5                                                     |           | —           |             | —        | _      | —       | —         | —       | Vss         |

| —    | 16                                                    | —         |             |             | —        |        | —       | —         | _       | Vss         |

#### TABLE 2: 28-PIN QFN ALLOCATION TABLE (PIC16F882/883/886)

**Note 1:** Pull-up activated only with external MCLR configuration.

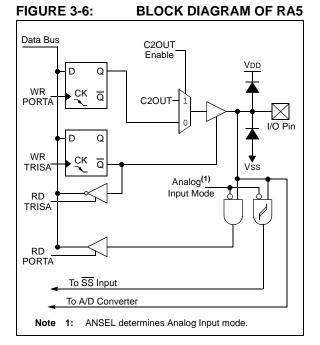

#### 3.2.3.6 RA5/AN4/SS/C2OUT

Figure 3-6 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- · a slave select input

- a digital output from Comparator C2

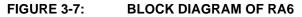

#### 3.2.3.7 RA6/OSC2/CLKOUT

Figure 3-7 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a crystal/resonator connection

- a clock output

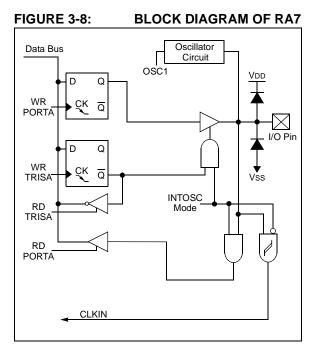

#### 3.2.3.8 RA7/OSC1/CLKIN

Figure 3-8 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a crystal/resonator connection

- · a clock input

#### TABLE 3-1: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name       | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|------------|--------|--------|--------|--------|--------|--------|---------|--------|---------------------|

| ADCON0     | ADCS1  | ADCS0  | CHS3   | CHS2   | CHS1   | CHS0   | GO/DONE | ADON   | 104                 |

| ANSEL      | ANS7   | ANS6   | ANS5   | ANS4   | ANS3   | ANS2   | ANS1    | ANS0   | 41                  |

| CM1CON0    | C10N   | C10UT  | C10E   | C1POL  |        | C1R    | C1CH1   | C1CH0  | 89                  |

| CM2CON0    | C2ON   | C2OUT  | C2OE   | C2POL  |        | C2R    | C2CH1   | C2CH0  | 90                  |

| CM2CON1    | MC1OUT | MC2OUT | C1RSEL | C2RSEL |        | _      | T1GSS   | C2SYNC | 92                  |

| PCON       | _      | _      | ULPWUE | SBOREN |        | _      | POR     | BOR    | 37                  |

| OPTION_REG | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1     | PS0    | 31                  |

| PORTA      | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1     | RA0    | 40                  |

| SSPCON     | WCOL   | SSPOV  | SSPEN  | CKP    | SSPM3  | SSPM2  | SSPM1   | SSPM0  | 177                 |

| TRISA      | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1  | TRISA0 | 40                  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

### 3.7 PORTE and TRISE Registers

PORTE<sup>(1)</sup> is a 4-bit wide, bidirectional port. The corresponding data direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). The exception is RE3, which is input only and its TRIS bit will always read as '1'. Example 3-6 shows how to initialize PORTE.

Reading the PORTE register (Register 3-13) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch. RE3 reads '0' when MCLRE = 1.

| Note 1: | RE<2:0>   | pins    | are  | available | on |

|---------|-----------|---------|------|-----------|----|

|         | PIC16F884 | 4/887 o | nly. |           |    |

#### REGISTER 3-13: PORTE: PORTE REGISTER

The TRISE register (Register 3-14) controls the PORTE pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISE register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

| Note: | The ANSEL register must be initialized to |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|

|       | configure an analog channel as a digital  |  |  |  |  |

|       | input. Pins configured as analog inputs   |  |  |  |  |

|       | will read '0'.                            |  |  |  |  |

#### EXAMPLE 3-6: INITIALIZING PORTE

| BANKSEL | PORTE       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTE       | ;Init PORTE            |

| BANKSEL | ANSEL       | ;                      |

| CLRF    | ANSEL       | ;digital I/O           |

| BCF     | STATUS, RP1 | ;Bank 1                |

| BANKSEL | TRISE       | ;                      |

| MOVLW   | B`00001100′ | ;Set RE<3:2> as inputs |

| MOVWF   | TRISE       | ;and set RE<1:0>       |

|         |             | ;as outputs            |

|         |             |                        |

| U-0   | U-0 | U-0 | U-0 | R-x | R/W-x                                 | R/W-x | R/W-x |

|-------|-----|-----|-----|-----|---------------------------------------|-------|-------|

| _     | _   | _   |     | RE3 | RE2                                   | RE1   | RE0   |

| bit 7 | •   |     |     |     | · · · · · · · · · · · · · · · · · · · |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 RD<3:0>: PORTE General Purpose I/O Pin bit

1 = Port pin is > VIH

0 = Port pin is < VIL

#### REGISTER 3-14: TRISE: PORTE TRI-STATE REGISTER

| U-0   | U-0 | U-0 | U-0 | R-1 <sup>(1)</sup> | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|-----|--------------------|--------|--------|--------|

| —     | _   | _   | -   | TRISE3             | TRISE2 | TRISE1 | TRISE0 |

| bit 7 |     |     |     |                    |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 **TRISE<3:0>:** PORTE Tri-State Control bit 1 = PORTE pin configured as an input (tri-stated) 0 = PORTE pin configured as an output

Note 1: TRISE<3> always reads '1'.

| Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register on<br>Page |

|-------|-------|-------|-------|-------|--------|--------|--------|--------|---------------------|

| ANSEL | ANS7  | ANS6  | ANS5  | ANS4  | ANS3   | ANS2   | ANS1   | ANS0   | 41                  |

| PORTE | —     | _     | _     | _     | RE3    | RE2    | RE1    | RE0    | 60                  |

| TRISE | _     |       |       |       | TRISE3 | TRISE2 | TRISE1 | TRISE0 | 60                  |

#### TABLE 3-5: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTE

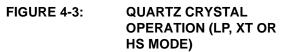

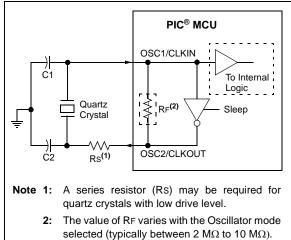

#### 4.4.3 LP, XT, HS MODES

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 4-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 4-3 and Figure 4-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- 2: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

CERAMIC RESONATOR OPERATION (XT OR HS MODE)

### 6.7 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- Timer1 interrupt enable bit of the PIE1 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TTMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

#### 6.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- · PEIE bit of the INTCON register must be set

The device will wake-up on an overflow and execute the next instruction. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine (0004h).

#### 6.9 ECCP Capture/Compare Time Base

The ECCP module uses the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPRxH:CCPRxL register pair on a configured event.

In Compare mode, an event is triggered when the value CCPRxH:CCPRxL register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Special Event Trigger.

See Section 11.0 "Capture/Compare/PWM Modules (CCP1 and CCP2)" for more information.

### 6.10 ECCP Special Event Trigger

If an ECCP is configured to trigger a special event, the trigger will clear the TMR1H:TMR1L register pair. This special event does not cause a Timer1 interrupt. The ECCP module may still be configured to generate a ECCP interrupt.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

Timer1 should be synchronized to the Fosc to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Special Event Trigger from the ECCP, the write will take precedence.

For more information, see Section 11.0 "Capture/ Compare/PWM Modules (CCP1 and CCP2)".

#### 6.11 Comparator Synchronization

The same clock used to increment Timer1 can also be used to synchronize the comparator output. This feature is enabled in the Comparator module.

When using the comparator for Timer1 gate, the comparator output should be synchronized to Timer1. This ensures Timer1 does not miss an increment if the comparator changes.

For more information, see **Section 8.0 "Comparator Module**".

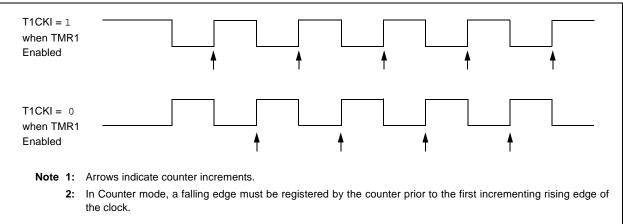

#### FIGURE 6-2: TIMER1 INCREMENTING EDGE

### 8.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. The comparators are very useful mixed signal building blocks because they provide analog functionality independent of the program execution. The analog comparator module includes the following features:

- Independent comparator control

- Programmable input selection

- · Comparator output is available internally/externally

- Programmable output polarity

- Interrupt-on-change

- Wake-up from Sleep

- PWM shutdown

- Timer1 gate (count enable)

- Output synchronization to Timer1 clock input

- SR Latch

- Programmable and Fixed Voltage Reference

Note: Only Comparator C2 can be linked to Timer1.

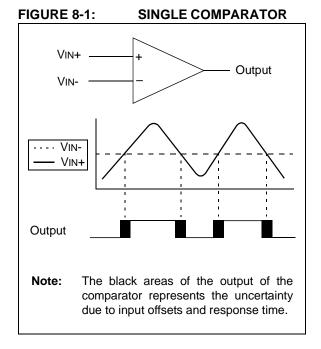

#### 8.1 Comparator Overview

A single comparator is shown in Figure 8-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

An example of the complete 8-word write sequence is shown in Example 10-4. The initial address is loaded into the EEADRH and EEADR register pair; the eight words of data are loaded using indirect addressing.

#### EXAMPLE 10-4: WRITING TO FLASH PROGRAM MEMORY

```

*****

; This write routine assumes the following:

A valid starting address (the least significant bits = '000')

;

is loaded in ADDRH:ADDRL

;

;

ADDRH, ADDRL and DATADDR are all located in data memory

;

BANKSEL EEADRH

MOVF

ADDRH,W

; Load initial address

MOVWF

EEADRH

MOVF

ADDRL,W

MOVWF

EEADR

DATAADDR,W ; Load initial data address

MOVF

MOVWF FSR

LOOP

MOVF

INDF,W

; Load first data byte into lower

;

MOVWF EEDATA

; Next byte

INCE

FSR,F

; Load second data byte into upper

MOVF

INDF,W

MOVWF

EEDATH

INCF

FSR,F

BANKSEL EECON1

EECON1, EEPGD ; Point to program memory

BSF

EECON1,WREN ; Enable writes

BSF

BCF

INTCON,GIE ; Disable interrupts (if using)

BTFSC INTCON, GIE ; See AN576

GOTO

$-2

Required Sequence

;

MOVLW

55h

; Start of required write sequence:

EECON2

MOVWF

; Write 55h

0AAh

MOVLW

;

MOVWF EECON2

; Write OAAh

BSF

EECON1,WR ; Set WR bit to begin write

NOP

; Required to transfer data to the buffer

NOP

; registers

BCF

EECON1,WREN ; Disable writes

BSF

INTCON,GIE ; Enable interrupts (comment out if not using interrupts)

BANKSEL EEADR

EEADR, W

MOVF

; Increment address

INCF

EEADR, F

; Indicates when sixteen words have been programmed

ANDLW

0x0F

SUBLW

; 0x0F = 16 words

0x0F

; 0x0B = 12 words (PIC16F884/883/882 only)

; 0x07 = 8 words

0x03 = 4 \text{ words}(\text{PIC16F884}/883/882 \text{ only})

;

BTFSS

STATUS,Z

; Exit on a match,

GOTO

LOOP

; Continue if more data needs to be written

```

### 11.2 Capture/Compare/PWM (CCP2)

The Capture/Compare/PWM module is a peripheral which allows the user to time and control different events. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate a Pulse-Width Modulated signal of varying frequency and duty cycle.

The timer resources used by the module are shown in Table 11-2.

Additional information on CCP modules is available in the Application Note AN594, *"Using the CCP Modules"* (DS00594).

#### TABLE 11-2: CCP MODE – TIMER RESOURCES REQUIRED

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

#### REGISTER 11-2: CCP2CON: CCP2 CONTROL REGISTER

| _                                                                 |                                                                                                          | R/W-0            | R/W-0        | R/W-0                                    | R/W-0          | R/W-0          | R/W-0  |  |  |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------|--------------|------------------------------------------|----------------|----------------|--------|--|--|

|                                                                   | _                                                                                                        | DC2B1            | DC2B0        | CCP2M3                                   | CCP2M2         | CCP2M1         | CCP2M0 |  |  |

| bit 7                                                             |                                                                                                          |                  |              |                                          |                |                | bit 0  |  |  |

|                                                                   |                                                                                                          |                  |              |                                          |                |                |        |  |  |

| Legend:                                                           |                                                                                                          |                  |              |                                          |                |                |        |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0 |                                                                                                          |                  |              |                                          | d as '0'       |                |        |  |  |

| -n = Value at POR                                                 |                                                                                                          | '1' = Bit is set |              | 0' = Bit is cleared $x = Bit is unknown$ |                |                | nown   |  |  |

| bit 7-6                                                           | Unimplomon                                                                                               | ted: Read as '   | 0'           |                                          |                |                |        |  |  |

| bit 5-4                                                           | •                                                                                                        |                  |              | ificant hita                             |                |                |        |  |  |

| DIL 3-4                                                           | DC2B<1:0>: PWM Duty Cycle Least Significant bits                                                         |                  |              |                                          |                |                |        |  |  |

|                                                                   | <u>Capture mode:</u><br>Unused.                                                                          |                  |              |                                          |                |                |        |  |  |

|                                                                   | Compare mode:                                                                                            |                  |              |                                          |                |                |        |  |  |

|                                                                   | Unused.                                                                                                  |                  |              |                                          |                |                |        |  |  |

|                                                                   | PWM mode:                                                                                                |                  |              |                                          |                |                |        |  |  |

|                                                                   | These bits are                                                                                           | e the two LSbs   | of the PWM c | luty cycle. The                          | eight MSbs are | e found in CCP | R2L.   |  |  |

| bit 3-0                                                           | CCP2M<3:0>: CCP2 Mode Select bits                                                                        |                  |              |                                          |                |                |        |  |  |

|                                                                   | 0000 = Capture/Compare/PWM off (resets CCP2 module)                                                      |                  |              |                                          |                |                |        |  |  |

|                                                                   | 0001 = Unused (reserved)                                                                                 |                  |              |                                          |                |                |        |  |  |

|                                                                   | 0010 = Unused (reserved)                                                                                 |                  |              |                                          |                |                |        |  |  |

|                                                                   | 0011 = Unused (reserved)<br>0100 = Capture mode, every falling edge                                      |                  |              |                                          |                |                |        |  |  |

|                                                                   | 0101 = Capture mode, every rising edge                                                                   |                  |              |                                          |                |                |        |  |  |

|                                                                   | 0110 = Capture mode, every 4th rising edge                                                               |                  |              |                                          |                |                |        |  |  |

|                                                                   | 0111 = Capture mode, every 16th rising edge                                                              |                  |              |                                          |                |                |        |  |  |

|                                                                   | 1000 = Compare mode, set output on match (CCP2IF bit is set)                                             |                  |              |                                          |                |                |        |  |  |

|                                                                   | 1001 = Compare mode, clear output on match (CCP2IF bit is set)                                           |                  |              |                                          |                |                |        |  |  |

|                                                                   | 1010 = Compare mode, generate software interrupt on match (CCP2IF bit is set, CCP2 pin<br>is unaffected) |                  |              |                                          |                |                |        |  |  |

|                                                                   | 1011 = Compare mode, trigger special event (CCP2IF bit is set, TMR1 is reset and A/D                     |                  |              |                                          |                |                |        |  |  |

|                                                                   | conversion is started if the ADC module is enabled. CCP2 pin is unaffected.)                             |                  |              |                                          |                |                |        |  |  |

|                                                                   | 11xx = PWM mode.                                                                                         |                  |              |                                          |                |                |        |  |  |

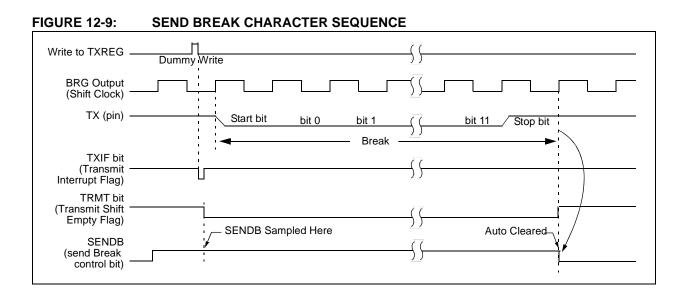

### 12.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- Address detection in 9-bit mode

- Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- 13-bit Break character transmit

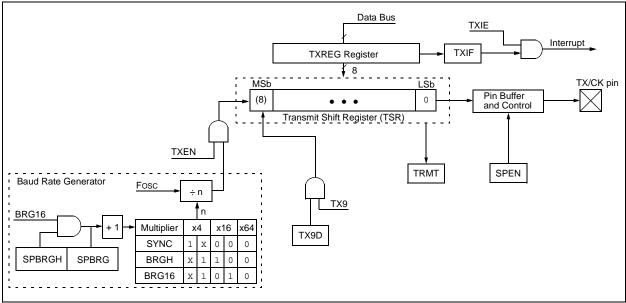

Block diagrams of the EUSART transmitter and receiver are shown in Figure 12-1 and Figure 12-2.

#### FIGURE 12-1: EUSART TRANSMIT BLOCK DIAGRAM

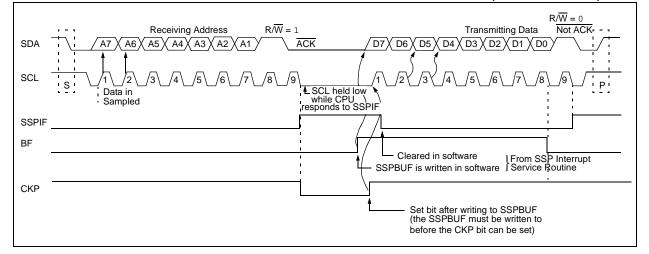

| FIGURE 13-7: | I <sup>2</sup> C <sup>™</sup> SLAVE MODE           | WAVEFORMS FOR                                  |                                        | ON (7-BIT ADD                                                                                     | RESS) |

|--------------|----------------------------------------------------|------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------|-------|

|              | eiving Address RW = 0<br><u>5</u> XA4XA3XA2XA1<br> | Cleared in software<br>SSPBUF register is read | B9t_1_2_<br>   <br>   <br>   <br> <br> | Receiving Data<br>D5XD4XD3XD2XD1<br>/3_/4_/5_/6\_/7<br>BUF register is still ful<br>ACK is not se |       |

|              |                                                    |                                                |                                        |                                                                                                   |       |

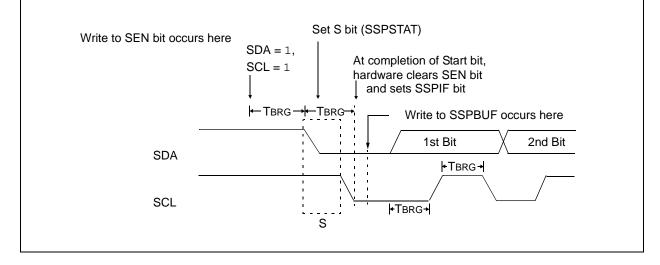

#### 13.4.6 I<sup>2</sup>C<sup>™</sup> MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Condition Enable bit SEN of the SSPCON2 register. If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low, while SCL is high, is the Start condition, and causes the S bit of the SSPSTAT register to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit of the SSPCON2 register will be automatically cleared by hardware, the Baud Rate Generator is suspended leaving the SDA line held low and the Start condition is complete.

**Note:** If, at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF, is set, the Start condition is aborted, and the I<sup>2</sup>C module is reset into its Idle state.

#### 13.4.6.1 WCOL Status Flag

If the user writes the SSPBUF when a Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur).

Note: Because queuing of events is not allowed, writing to the lower five bits of SSPCON2 is disabled until the Start condition is complete.

#### FIGURE 13-13: FIRST START BIT TIMING

| Register | Address | Power-on<br>Reset | MCLR Reset<br>WDT Reset (Continued)<br>Brown-out Reset <sup>(1)</sup> | Wake-up from Sleep through<br>Interrupt<br>Wake-up from Sleep through<br>WDT Time-out (Continued) |

|----------|---------|-------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| CM2CON1  | 109h    | 0000 00           | 0000 00                                                               | uuuu uu                                                                                           |

| EEDAT    | 10Ch    | 0000 0000         | 0000 0000                                                             | uuuu uuuu                                                                                         |

| EEADR    | 10Dh    | 0000 0000         | 0000 0000                                                             | uuuu uuuu                                                                                         |

| EEDATH   | 10Eh    | 00 0000           | 00 0000                                                               | uu uuuu                                                                                           |

| EEADRH   | 10Fh    | 0 0000            | 0 0000                                                                | u uuuu                                                                                            |

| SRCON    | 185h    | 0000 00-0         | 0000 00-0                                                             | uuuu uu-u                                                                                         |

| BAUDCTL  | 187h    | 01-0 0-00         | 01-0 0-00                                                             | uu-u u-uu                                                                                         |

| ANSEL    | 188h    | 1111 1111         | 1111 1111                                                             | uuuu uuuu                                                                                         |

| ANSELH   | 189h    | 1111 1111         | 1111 1111                                                             | uuuu uuuu                                                                                         |

| EECON1   | 18Ch    | x000              | q000                                                                  | uuuu                                                                                              |

| EECON2   | 18Dh    |                   |                                                                       |                                                                                                   |

#### TABLE 14-4: INITIALIZATION CONDITION FOR REGISTER (CONTINUED)

$\label{eq:logend: u = unchanged, x = unknown, - = unimplemented bit, reads as `0', q = value depends on condition.$

- Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

- 2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

- **3:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- 4: See Table 14-5 for Reset value for specific condition.

- **5:** If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

- 6: Accessible only when SSPCON register bits SSPM<3:0> = 1001.

#### TABLE 14-5: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | Status<br>Register | PCON<br>Register |  |

|------------------------------------|-----------------------|--------------------|------------------|--|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 010x             |  |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | 0uuu             |  |

| MCLR Reset during Sleep            | 000h                  | 0001 Ouuu          | 0uuu             |  |

| WDT Reset                          | 000h                  | 0000 uuuu          | 0uuu             |  |

| WDT Wake-up                        | PC + 1                | uuu0 Ouuu          | uuuu             |  |

| Brown-out Reset                    | 000h                  | 0001 luuu          | 01u0             |  |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uuuu             |  |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Interrupt Enable bit, GIE, is set, the PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

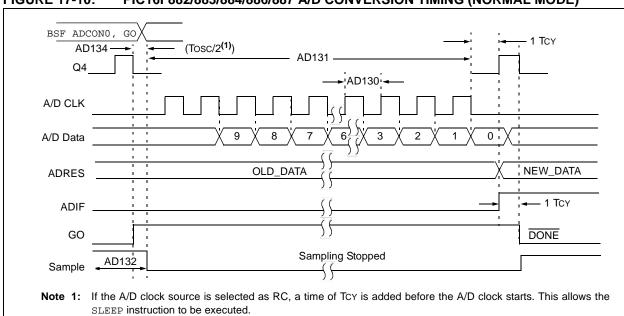

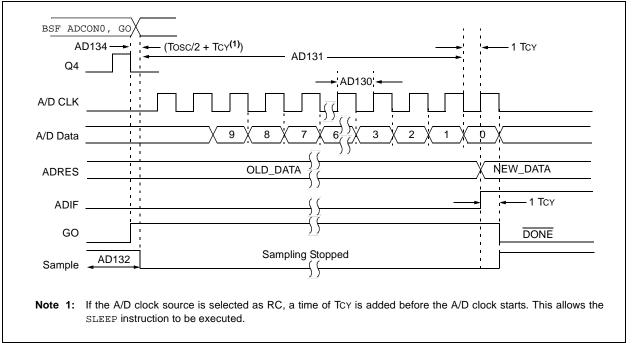

#### FIGURE 17-10: PIC16F882/883/884/886/887 A/D CONVERSION TIMING (NORMAL MODE)

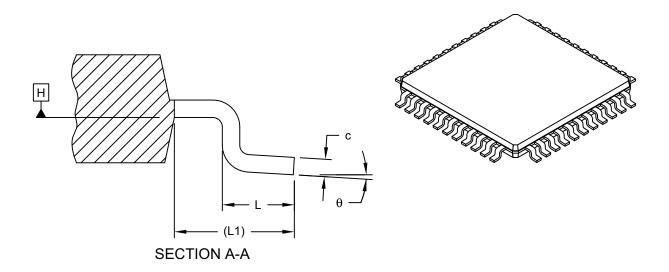

#### 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |      |      |  |

|--------------------------|-------------|-----------|------|------|--|

| Dimension                | MIN         | NOM       | MAX  |      |  |

| Number of Leads          | N           | 44        |      |      |  |

| Lead Pitch               | е           | 0.80 BSC  |      |      |  |

| Overall Height           | Α           | -         | -    | 1.20 |  |

| Standoff                 | A1          | 0.05      | -    | 0.15 |  |

| Molded Package Thickness | A2          | 0.95      | 1.00 | 1.05 |  |

| Overall Width            | E           | 12.00 BSC |      |      |  |

| Molded Package Width     | E1          | 10.00 BSC |      |      |  |

| Overall Length           | D           | 12.00 BSC |      |      |  |

| Molded Package Length    | D1          | 10.00 BSC |      |      |  |

| Lead Width               | b           | 0.30      | 0.37 | 0.45 |  |

| Lead Thickness           | С           | 0.09      | -    | 0.20 |  |

| Lead Length              | L           | 0.45      | 0.60 | 0.75 |  |

| Footprint                | L1          | 1.00 REF  |      |      |  |

| Foot Angle               | θ           | 0°        | 3.5° | 7°   |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Exact shape of each corner is optional.

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076C Sheet 2 of 2

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, flexPWR, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC<sup>32</sup> logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

The Embedded Control Solutions Company and mTouch are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, ECAN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, KleerNet, KleerNet logo, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, RightTouch logo, REAL ICE, SQI, Serial Quad I/O, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2006-2015, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-63277-237-4

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.