Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 368 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f886t-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.5 PIE2 Register

The PIE2 register contains the interrupt enable bits, as shown in Register 2-5.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

# **REGISTER DEFINITIONS: PIE2**

## REGISTER 2-5: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | U-0 | R/W-0  |

|-------|-------|-------|-------|-------|---------|-----|--------|

| OSFIE | C2IE  | C1IE  | EEIE  | BCLIE | ULPWUIE |     | CCP2IE |

| bit 7 |       |       |       |       |         |     | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | OSFIE: Oscillator Fail Interrupt Enable bit                                                                               |

|-------|---------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Enables oscillator fail interrupt</li><li>0 = Disables oscillator fail interrupt</li></ul>                    |

| bit 6 | C2IE: Comparator C2 Interrupt Enable bit                                                                                  |

|       | <ul><li>1 = Enables Comparator C2 interrupt</li><li>0 = Disables Comparator C2 interrupt</li></ul>                        |

| bit 5 | C1IE: Comparator C1 Interrupt Enable bit                                                                                  |

|       | <ul><li>1 = Enables Comparator C1 interrupt</li><li>0 = Disables Comparator C1 interrupt</li></ul>                        |

| bit 4 | EEIE: EEPROM Write Operation Interrupt Enable bit                                                                         |

|       | <ul> <li>1 = Enables EEPROM write operation interrupt</li> <li>0 = Disables EEPROM write operation interrupt</li> </ul>   |

| bit 3 | BCLIE: Bus Collision Interrupt Enable bit                                                                                 |

|       | <ul><li>1 = Enables Bus Collision interrupt</li><li>0 = Disables Bus Collision interrupt</li></ul>                        |

| bit 2 | ULPWUIE: Ultra Low-Power Wake-up Interrupt Enable bit                                                                     |

|       | <ul> <li>1 = Enables Ultra Low-Power Wake-up interrupt</li> <li>0 = Disables Ultra Low-Power Wake-up interrupt</li> </ul> |

| bit 1 | Unimplemented: Read as '0'                                                                                                |

| bit 0 | CCP2IE: CCP2 Interrupt Enable bit                                                                                         |

|       | <ul><li>1 = Enables CCP2 interrupt</li><li>0 = Disables CCP2 interrupt</li></ul>                                          |

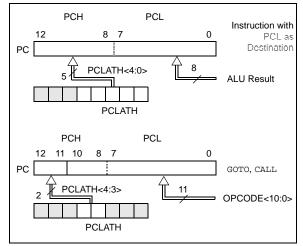

## 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-7 shows the two situations for the loading of the PC. The upper example in Figure 2-7 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 2-7 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 2-7: LOADING OF PC IN DIFFERENT SITUATIONS

## 2.3.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<12:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper five bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 13 bits of the program counter will change to the values contained in the PCLATH register.

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). Care should be exercised when jumping into a look-up table or program branch table (computed GOTO) by modifying the PCL register. Assuming that PCLATH is set to the table start address, if the table length is greater than 255 instructions or if the lower eight bits of the memory address rolls over from 0xFF to 0x00 in the middle of the table, then PCLATH must be incremented for each address rollover that occurs between the table beginning and the target location within the table.

For more information refer to Application Note AN556, "*Implementing a Table Read*" (DS00556).

## 2.3.2 STACK

The PIC16F882/883/884/886/887 devices have an 8-level x 13-bit wide hardware stack (see Figures 2-2 and 2-3). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

2: There are no instructions minemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

## 2.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR and the IRP bit of the STATUS register, as shown in Figure 2-8.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 2-1.

| EXAMPLE 2-1: | INDIRECT ADDRESSING |

|--------------|---------------------|

|--------------|---------------------|

|          | MOVLW | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ;to RAM              |

| NEXT     | CLRF  | INDF  | ;clear INDF register |

|          | INCF  | FSR   | ;inc pointer         |

|          | BTFSS | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;no clear next       |

| CONTINUE |       |       | ;yes continue        |

|          |       |       |                      |

## 4.2 Oscillator Control

The Oscillator Control (OSCCON) register (Figure 4-1) controls the system clock and frequency selection options. The OSCCON register contains the following bits:

- Frequency selection bits (IRCF)

- Frequency Status bits (HTS, LTS)

- System clock control bits (OSTS, SCS)

# **REGISTER DEFINITIONS: OSCILLATOR CONTROL**

## REGISTER 4-1: OSCCON: OSCILLATOR CONTROL REGISTER

| _           | IDOED                                                                                                                                                                                          |                   |                | R-1                 | R-0             | R-0            | R/W-0        |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|---------------------|-----------------|----------------|--------------|

|             | IRCF2                                                                                                                                                                                          | IRCF1             | IRCF0          | OSTS <sup>(1)</sup> | HTS             | LTS            | SCS          |

| oit 7       |                                                                                                                                                                                                | ·                 |                |                     |                 |                | bit C        |

|             |                                                                                                                                                                                                |                   |                |                     |                 |                |              |

| _egend:     |                                                                                                                                                                                                |                   |                |                     |                 |                |              |

| R = Readab  | ole bit                                                                                                                                                                                        | W = Writable      | bit            | U = Unimplem        | nented bit, rea | id as '0'      |              |

| n = Value a | at POR                                                                                                                                                                                         | '1' = Bit is set  |                | '0' = Bit is clea   | ared            | x = Bit is unk | nown         |

|             |                                                                                                                                                                                                |                   |                |                     |                 |                |              |

| oit 7       | Unimpleme                                                                                                                                                                                      | nted: Read as '   | 0'             |                     |                 |                |              |

| oit 6-4     |                                                                                                                                                                                                | Internal Oscillat | or Frequency   | Select bits         |                 |                |              |

|             | 111 = 8 MHz                                                                                                                                                                                    |                   |                |                     |                 |                |              |

|             | 110 = 4 MHz<br>101 = 2 MHz                                                                                                                                                                     | · /               |                |                     |                 |                |              |

|             | 101 = 2  MHz<br>100 = 1  MHz                                                                                                                                                                   |                   |                |                     |                 |                |              |

|             | 011 = 500  k                                                                                                                                                                                   | _                 |                |                     |                 |                |              |

|             | 010 = 250 k                                                                                                                                                                                    |                   |                |                     |                 |                |              |

|             | 001 <b>= 125</b> kHz                                                                                                                                                                           |                   |                |                     |                 |                |              |

|             |                                                                                                                                                                                                | z (LFINTOSC)      |                |                     |                 |                |              |

| oit 3       |                                                                                                                                                                                                | lator Start-up Ti |                |                     |                 |                |              |

|             | <ul> <li>1 = Device is running from the clock defined by FOSC&lt;2:0&gt; of the CONFIG1 register</li> <li>0 = Device is running from the internal oscillator (HFINTOSC or LFINTOSC)</li> </ul> |                   |                |                     |                 |                |              |

|             |                                                                                                                                                                                                | -                 |                | -                   |                 | OSC)           |              |

| oit 2       |                                                                                                                                                                                                |                   | (High Frequer  | ncy – 8 MHz to 1    | 25 kHz)         |                |              |

|             | 1 = HFINTC                                                                                                                                                                                     | SC is stable      |                |                     |                 |                |              |

|             |                                                                                                                                                                                                |                   |                | 04 (4) (-)          |                 |                |              |

| bit 1       | LTS: LFINTOSC Stable bit (Low Frequency – 31 kHz)<br>1 = LFINTOSC is stable                                                                                                                    |                   |                |                     |                 |                |              |

|             |                                                                                                                                                                                                | SC is stable      |                |                     |                 |                |              |

| oit O       |                                                                                                                                                                                                | n Clock Select b  |                |                     |                 |                |              |

|             | -                                                                                                                                                                                              | oscillator is use |                | clock               |                 |                |              |

|             |                                                                                                                                                                                                |                   | •              | of the CONFIG1      | 1 register      |                |              |

| Note 1: E   | Bit resets to '0' w                                                                                                                                                                            | ith Two-Speed 9   | Start-up and L | P XT or HS cold     | acted as the C  | Scillator modo | or Fail-Safa |

|             | node is enabled.                                                                                                                                                                               | •                 | Start-up and L |                     |                 |                | UI Fall-Sale |

## 8.10 Comparator Voltage Reference

The comparator voltage reference module provides an internally generated voltage reference for the comparators. The following features are available:

- Independent from Comparator operation

- Two 16-level voltage ranges

- Output clamped to Vss

- Ratiometric with VDD

- Fixed Reference (0.6V)

The VRCON register (Register 8-5) controls the voltage reference module shown in Figure 8-8.

The voltage source is selectable through both ends of the 16 connection resistor ladder network. Bit VRSS of the VRCON register selects either the internal or external voltage source.

The PIC16F882/883/884/886/887 allows the CVREF signal to be output to the RA2 pin of PORTA under certain configurations only. For more details, see Figure 8-9.

#### 8.10.1 INDEPENDENT OPERATION

The comparator voltage reference is independent of the comparator configuration. Setting the VREN bit of the VRCON register will enable the voltage reference.

#### 8.10.2 OUTPUT VOLTAGE SELECTION

The CVREF voltage reference has two ranges with 16 voltage levels in each range. Range selection is controlled by the VRR bit of the VRCON register. The 16 levels are set with the VR<3:0> bits of the VRCON register.

The CVREF output voltage is determined by the following equations:

## EQUATION 8-1: CVREF OUTPUT VOLTAGE

VRR = 1 (low range): CVREF = (VR<3:0>/24) × VLADDER VRR = 0 (high range): CVREF = (VLADDER/4) + (VR<3:0> × VLADDER/32) VLADDER = VDD or ([VREF+] - [VREF-]) or VREF+

The full range of VSS to VDD cannot be realized due to the construction of the module. See Figure 8-8.

### 8.10.3 OUTPUT CLAMPED TO Vss

The CVREF output voltage can be set to Vss with no power consumption by clearing the FVREN bit of the VRCON register.

This allows the comparator to detect a zero-crossing while not consuming additional CVREF module current.

Note: Depending on the application, additional components may be required for a zero cross circuit. Reference TB3013, *"Using the ESD Parasitic Diodes on Mixed Signal Microcontrollers"* (DS93013), for more information.

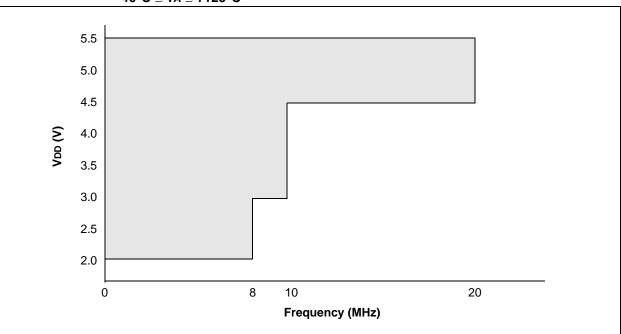

#### 8.10.4 OUTPUT RATIOMETRIC TO VDD

The comparator voltage reference is VDD derived and therefore, the CVREF output changes with fluctuations in VDD. The tested absolute accuracy of the Comparator Voltage Reference can be found in **Section 17.0 "Electrical Specifications"**.

#### 8.10.5 FIXED VOLTAGE REFERENCE

The Fixed Voltage Reference is independent of VDD, with a nominal output voltage of 0.6V. This reference can be enabled by setting the FVREN bit of the SRCON register to '1'. This reference is always enabled when the HFINTOSC oscillator is active.

#### 8.10.6 FIXED VOLTAGE REFERENCE STABILIZATION PERIOD

When the Fixed Voltage Reference module is enabled, it will require some time for the reference and its amplifier circuits to stabilize. The user program must include a small delay routine to allow the module to settle. See **Section 17.0 "Electrical Specifications"** for the minimum delay requirement.

#### 8.10.7 VOLTAGE REFERENCE SELECTION

Multiplexers on the output of the voltage reference module enable selection of either the CVREF or Fixed Voltage Reference for use by the comparators.

Setting the C1RSEL bit of the CM2CON1 register enables current to flow in the CVREF voltage divider and selects the CVREF voltage for use by C1. Clearing the C1RSEL bit selects the fixed voltage for use by C1.

Setting the C2RSEL bit of the CM2CON1 register enables current to flow in the CVREF voltage divider and selects the CVREF voltage for use by C2. Clearing the C2RSEL bit selects the fixed voltage for use by C2.

When both the C1RSEL and C2RSEL bits are cleared, current flow in the CVREF voltage divider is disabled minimizing the power drain of the voltage reference peripheral.

| IADLE | 0-2.  |                        |                        |                      |                      |      | _    | -    |      |

|-------|-------|------------------------|------------------------|----------------------|----------------------|------|------|------|------|

| RA3   | RA2   | Comp.<br>Reference (+) | Comp.<br>Reference (-) | ADC<br>Reference (+) | ADC<br>Reference (-) | CFG1 | CFG0 | VRSS | VROE |

| I/O   | I/O   | AVdd                   | AVss                   | AVdd                 | AVss                 | 0    | 0    | 0    | 0    |

| I/O   | CVREF | AVdd                   | AVss                   | AVdd                 | AVss                 | 0    | 0    | 0    | 1    |

| VREF+ | VREF- | Vref+                  | VREF-                  | AVdd                 | AVss                 | 0    | 0    | 1    | 0    |

| VREF+ | CVREF | Vref+                  | AVss                   | AVdd                 | AVss                 | 0    | 0    | 1    | 1    |

| VREF+ | I/O   | AVdd                   | AVss                   | Vref+                | AVss                 | 0    | 1    | 0    | 0    |

| VREF+ | CVREF | AVdd                   | AVss                   | Vref+                | AVss                 | 0    | 1    | 0    | 1    |

| VREF+ | VREF- | Vref+                  | VREF-                  | Vref+                | AVss                 | 0    | 1    | 1    | 0    |

| VREF+ | CVREF | Vref+                  | AVss                   | Vref+                | AVss                 | 0    | 1    | 1    | 1    |

| I/O   | Vref- | AVdd                   | AVss                   | AVDD                 | Vref-                | 1    | 0    | 0    | 0    |

| I/O   | VREF- | AVdd                   | AVss                   | AVdd                 | Vref-                | 1    | 0    | 0    | 1    |

| VREF+ | Vref- | Vref+                  | VREF-                  | AVDD                 | Vref-                | 1    | 0    | 1    | 0    |

| VREF+ | VREF- | Vref+                  | VREF-                  | AVdd                 | VREF-                | 1    | 0    | 1    | 1    |

| VREF+ | VREF- | AVdd                   | AVss                   | Vref+                | Vref-                | 1    | 1    | 0    | 0    |

| VREF+ | VREF- | AVdd                   | AVss                   | Vref+                | VREF-                | 1    | 1    | 0    | 1    |

| VREF+ | VREF- | Vref+                  | VREF-                  | Vref+                | VREF-                | 1    | 1    | 1    | 0    |

| VREF+ | VREF- | VREF+                  | Vref-                  | Vref+                | VREF-                | 1    | 1    | 1    | 1    |

## TABLE 8-2: COMPARATOR AND ADC VOLTAGE REFERENCE PRIORITY

#### TABLE 9-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES (VDD $\geq$ 3.0V)

| ADC Clock        | Period (TAD) | Device Frequency (Fosc) |                         |                         |                               |  |  |

|------------------|--------------|-------------------------|-------------------------|-------------------------|-------------------------------|--|--|

| ADC Clock Source | ADCS<1:0>    | 20 MHz                  | 8 MHz                   | 4 MHz                   | 1 MHz                         |  |  |

| Fosc/2           | 00           | 100 ns <sup>(2)</sup>   | 250 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>   | 2.0 μs                        |  |  |

| Fosc/8           | 01           | 400 ns <sup>(2)</sup>   | 1.0 μs <b>(2)</b>       | 2.0 μs                  | 8.0 μs <b>(3)</b>             |  |  |

| Fosc/32          | 10           | 1.6 μs                  | 4.0 μs                  | 8.0 μs <sup>(3)</sup>   | 32.0 μs <b><sup>(3)</sup></b> |  |  |

| FRC              | 11           | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup>       |  |  |

Legend: Shaded cells are outside of recommended range.

**Note 1:** The FRC source has a typical TAD time of 4  $\mu$ s for VDD > 3.0V.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: When the device frequency is greater than 1 MHz, the FRC clock source is only recommended if the conversion will be performed during Sleep.

#### FIGURE 9-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

| TCY to TAD TAD1               | TAD2      | TAD3    | TAD4   | TAD5   | TAD6   | TAD7          | TAD8                  | TAD9         | TAD10 | TAD11 |                                  |

|-------------------------------|-----------|---------|--------|--------|--------|---------------|-----------------------|--------------|-------|-------|----------------------------------|

| $\uparrow \uparrow  \uparrow$ | b9        | b8      | b7     | b6     | b5     | b4            | b3                    | b2           | b1    | b0    |                                  |

| Conver                        | sion St   | arts    |        |        |        |               |                       |              |       |       |                                  |

| Holding Capa                  | acitor is | s Disco | nnecte | d from | Analog | g Input       | (typica               | lly 100      | ns)   |       |                                  |

| <br>Set GO/DONE               | bit       |         |        |        |        | GO bi<br>ADIF | it is cle<br>bit is s | ared,<br>et, |       | •     | l<br>are loaded,<br>analog input |

#### 9.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADC interrupt enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

**Note:** The ADIF bit is set at the completion of every conversion, regardless of whether or not the ADC interrupt is enabled.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the global interrupt must be disabled. If the global interrupt is enabled, execution will switch to the Interrupt Service Routine.

Please see **Section 14.3 "Interrupts"** for more information.

## REGISTER 11-3: ECCPAS: ENHANCED CAPTURE/COMPARE/PWM AUTO-SHUTDOWN CONTROL REGISTER

| R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                                                                         | R/W-0            | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|------------------|------------------|-----------------|--------|--|

| ECCPASE       |                                                                                                                                                                                                                                                                                                                                                               | ECCPAS1          | ECCPAS0         | PSSAC1           | PSSAC0           | PSSBD1          | PSSBD0 |  |

| bit 7         |                                                                                                                                                                                                                                                                                                                                                               |                  |                 | bit 0            |                  |                 |        |  |

|               |                                                                                                                                                                                                                                                                                                                                                               |                  |                 |                  |                  |                 |        |  |

| Legend:       |                                                                                                                                                                                                                                                                                                                                                               |                  |                 |                  |                  |                 |        |  |

| R = Readabl   | e bit                                                                                                                                                                                                                                                                                                                                                         | W = Writable     | bit             | U = Unimpler     | mented bit, read | d as '0'        |        |  |

| -n = Value at | POR                                                                                                                                                                                                                                                                                                                                                           | '1' = Bit is set |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |  |

| bit 7         | <b>ECCPASE:</b> ECCP Auto-Shutdown Event Status bit<br>1 = A shutdown event has occurred; ECCP outputs are in shutdown state<br>0 = ECCP outputs are operating                                                                                                                                                                                                |                  |                 |                  |                  |                 |        |  |

| bit 6-4       | ECCPAS<2:0                                                                                                                                                                                                                                                                                                                                                    | >: ECCP Auto     | -shutdown Sou   | arce Select bits | 6                |                 |        |  |

|               | 000 = Auto-Shutdown is disabled<br>001 = Comparator C1 output high<br>010 = Comparator C2 output high <sup>(1)</sup><br>011 = Either Comparators output is high<br>100 = VIL on INT pin<br>101 = VIL on INT pin or Comparator C1 output high<br>110 = VIL on INT pin or Comparator C2 output high<br>111 =VIL on INT pin or either Comparators output is high |                  |                 |                  |                  |                 |        |  |

| bit 3-2       | PSSACn: Pins P1A and P1C Shutdown State Control bits<br>00 = Drive pins P1A and P1C to '0'<br>01 = Drive pins P1A and P1C to '1'<br>1x = Pins P1A and P1C tri-state                                                                                                                                                                                           |                  |                 |                  |                  |                 |        |  |

| bit 1-0       | <b>PSSBDn:</b> Pins P1B and P1D Shutdown State Control bits<br>00 = Drive pins P1B and P1D to '0'<br>01 = Drive pins P1B and P1D to '1'<br>1x = Pins P1B and P1D tri-state                                                                                                                                                                                    |                  |                 |                  |                  |                 |        |  |

| Note 1: If    | C2SYNC is enal                                                                                                                                                                                                                                                                                                                                                | bled, the shutd  | own will be del | ayed by Timer    | 1.               |                 |        |  |

| Note 1: | The auto-shutdown condition is a level-    |

|---------|--------------------------------------------|

|         | based signal, not an edge-based signal.    |

|         | As long as the level is present, the auto- |

|         | shutdown will persist.                     |

- 2: Writing to the ECCPASE bit is disabled while an auto-shutdown condition persists.

- **3:** Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart) the PWM signal will always restart at the beginning of the next PWM period.

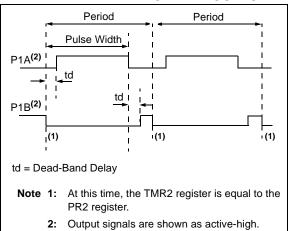

### 11.6.6 PROGRAMMABLE DEAD-BAND DELAY MODE

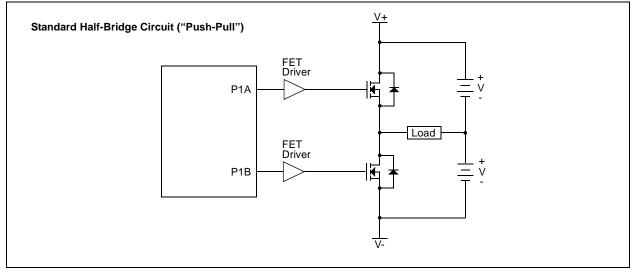

In Half-Bridge applications where all power switches are modulated at the PWM frequency, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on, and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shoot-through current*) will flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In Half-Bridge mode, a digitally programmable deadband delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 11-17 for illustration. The lower seven bits of the associated PWM1CON register (Register 11-4) sets the delay period in terms of microcontroller instruction cycles (Tcy or 4 Tosc).

#### FIGURE 11-17: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

## FIGURE 11-18: EXAMPLE OF HALF-BRIDGE APPLICATIONS

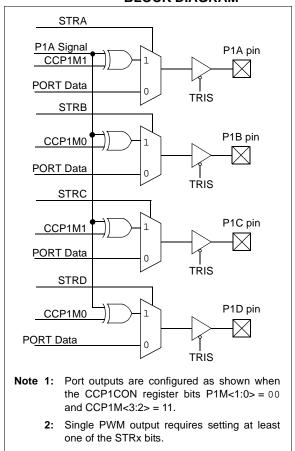

## FIGURE 11-19: SIMPLIFIED STEERING BLOCK DIAGRAM

## 12.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTA register which resets the EUSART. Clearing the CREN bit of the RCSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive  |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|

|       | FIFO have framing errors, repeated reads  |  |  |  |  |  |  |  |  |

|       | of the RCREG will not clear the FERR bit. |  |  |  |  |  |  |  |  |

#### 12.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated If a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCSTA register or by resetting the EUSART by clearing the SPEN bit of the RCSTA register.

#### 12.1.2.6 Receiving 9-Bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

### 12.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

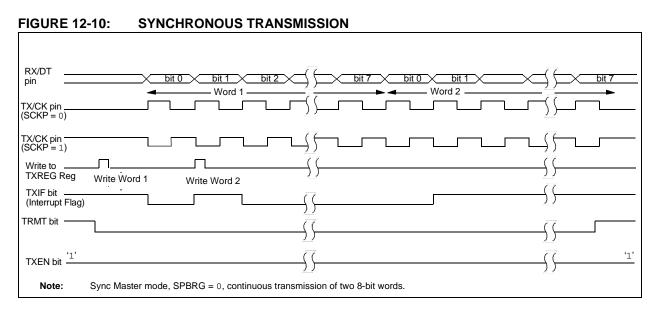

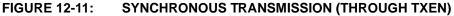

#### TABLE 12-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name    | Bit 7                               | Bit 6        | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |  |

|---------|-------------------------------------|--------------|---------|--------|--------|--------|--------|--------|---------------------|--|

| BAUDCTL | ABDOVF                              | RCIDL        | _       | SCKP   | BRG16  | _      | WUE    | ABDEN  | 159                 |  |

| INTCON  | GIE                                 | PEIE         | T0IE    | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 32                  |  |

| PIE1    | —                                   | ADIE         | RCIE    | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 33                  |  |

| PIR1    | —                                   | ADIF         | RCIF    | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 35                  |  |

| RCREG   | EUSART Rece                         | eive Data Re | egister |        |        |        |        |        | 155                 |  |

| RCSTA   | SPEN                                | RX9          | SREN    | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 158                 |  |

| SPBRG   | BRG7                                | BRG6         | BRG5    | BRG4   | BRG3   | BRG2   | BRG1   | BRG0   | 160                 |  |

| SPBRGH  | BRG15                               | BRG14        | BRG13   | BRG12  | BRG11  | BRG10  | BRG9   | BRG8   | 160                 |  |

| TRISC   | TRISC7                              | TRISC6       | TRISC5  | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 54                  |  |

| TXREG   | TXREG EUSART Transmit Data Register |              |         |        |        |        |        |        |                     |  |

| TXSTA   | CSRC                                | TX9          | TXEN    | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 157                 |  |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Transmission.

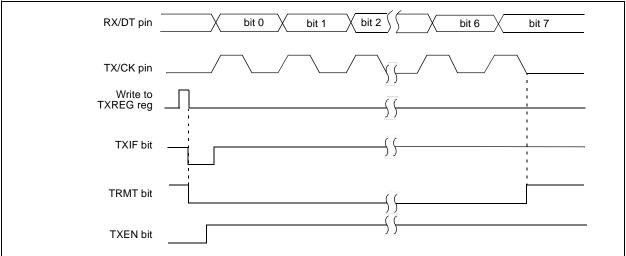

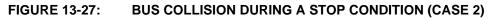

#### 13.4.16.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- After the SDA pin has been de-asserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is de-asserted, SCL is sampled low before SDA goes high.

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPADD<6:0> and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 13-26). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 13-27).

## FIGURE 13-26: BUS COLLISION DURING A STOP CONDITION (CASE 1)

| MOVF             | Move f                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] MOVF f,d                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Description:     | The contents of register 'f' is<br>moved to a destination dependent<br>upon the status of 'd'. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register 'f'<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| MOVWF            | Move W to f                                |  |  |  |  |  |  |

|------------------|--------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] MOVWF f                          |  |  |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                        |  |  |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                      |  |  |  |  |  |  |

| Status Affected: | None                                       |  |  |  |  |  |  |

| Description:     | Move data from W register to register 'f'. |  |  |  |  |  |  |

| Words:           | 1                                          |  |  |  |  |  |  |

| Cycles:          | 1                                          |  |  |  |  |  |  |

| Example:         | MOVW OPTION<br>F                           |  |  |  |  |  |  |

|                  | Before Instruction                         |  |  |  |  |  |  |

|                  | OPTION = 0xFF                              |  |  |  |  |  |  |

|                  | W = 0x4F                                   |  |  |  |  |  |  |

|                  | After Instruction                          |  |  |  |  |  |  |

|                  | OPTION = 0x4F                              |  |  |  |  |  |  |

|                  | W = 0x4F                                   |  |  |  |  |  |  |

|                  |                                            |  |  |  |  |  |  |

| MOVLW            | Move literal to W                                                                         |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                  |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                       |  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                       |  |  |  |  |  |  |

| Status Affected: | None                                                                                      |  |  |  |  |  |  |

| Description:     | The 8-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |  |  |  |  |  |  |

| Words:           | 1                                                                                         |  |  |  |  |  |  |

| Cycles:          | 1                                                                                         |  |  |  |  |  |  |

| Example:         | MOVLW 0x5A                                                                                |  |  |  |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                             |  |  |  |  |  |  |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

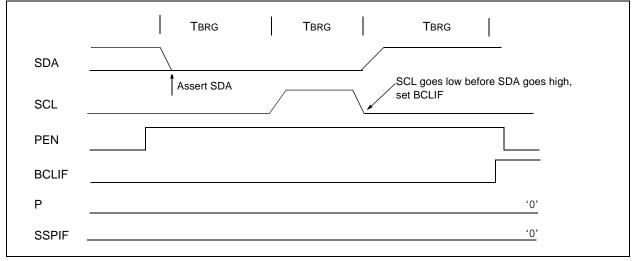

FIGURE 17-1: PIC16F882/883/884/886/887 VOLTAGE-FREQUENCY GRAPH, -40°C  $\leq$  TA  $\leq$  +125°C

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

# TABLE 17-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET PARAMETERS

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |       |                                                                |          |          |          |          |                                            |  |  |

|----------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------|----------|----------|----------|----------|--------------------------------------------|--|--|

| Param<br>No.                                                                                                         | Sym.  | Characteristic                                                 | Min.     | Тур†     | Max.     | Units    | Conditions                                 |  |  |

| 30                                                                                                                   | ТмсL  | MCLR Pulse Width (low)                                         | 2<br>5   |          |          | μs<br>μs | VDD = 5V, -40°C to +85°C<br>VDD = 5V       |  |  |

| 31                                                                                                                   | Twdt  | Watchdog Timer Time-out<br>Period (No Prescaler)               | 10<br>10 | 16<br>16 | 29<br>31 | ms<br>ms | VDD = 5V, -40°C to +85°C<br>VDD = 5V       |  |  |

| 32                                                                                                                   | Tost  | Oscillation Start-up Timer<br>Period <sup>(1, 2)</sup>         | -        | 1024     | —        | Tosc     | (Note 3)                                   |  |  |

| 33*                                                                                                                  | TPWRT | Power-up Timer Period                                          | 40       | 65       | 140      | ms       |                                            |  |  |

| 34*                                                                                                                  | Tioz  | I/O High-impedance from<br>MCLR Low or Watchdog<br>Timer Reset | —        | —        | 2.0      | μS       |                                            |  |  |

| 35                                                                                                                   | VBOR  | Brown-out Reset Voltage                                        | 2.0      |          | 2.2      | V        | BOR4V bit = 0 (Note 4)                     |  |  |

|                                                                                                                      |       |                                                                | 3.6      | 4.0      | 4.4      | V        | BOR4V bit = 1, -40°C to +85°C<br>(Note 4)  |  |  |

|                                                                                                                      |       |                                                                | 3.6      | 4.0      | 4.5      | V        | BOR4V bit = 1, -40°C to +125°C<br>(Note 4) |  |  |

| 36*                                                                                                                  | VHYST | Brown-out Reset Hysteresis                                     | —        | 50       | _        | mV       |                                            |  |  |

| 37*                                                                                                                  | TBOR  | Brown-out Reset Minimum<br>Detection Period                    | 100      | —        | —        | μs       | $VDD \leq VBOR$                            |  |  |

<sup>t</sup> These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- 2: By design.

- 3: Period of the slower clock.

4: To ensure these voltage tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

| Param.<br>No. | Symbol  | Characte              | eristic      | Min.       | Max. | Units | Conditions                                  |

|---------------|---------|-----------------------|--------------|------------|------|-------|---------------------------------------------|

| 100*          | Тнідн   | Clock high time       | 100 kHz mode | 4.0        |      | μS    | Device must operate at a minimum of 1.5 MHz |

|               |         |                       | 400 kHz mode | 0.6        | _    | μS    | Device must operate at a minimum of 10 MHz  |

|               |         |                       | SSP Module   | 1.5TCY     | _    |       |                                             |

| 101*          | TLOW    | Clock low time        | 100 kHz mode | 4.7        | _    | μS    | Device must operate at a minimum of 1.5 MHz |

|               |         |                       | 400 kHz mode | 1.3        | _    | μS    | Device must operate at a minimum of 10 MHz  |

|               |         |                       | SSP Module   | 1.5TCY     | _    |       |                                             |

| 102*          | TR      | SDA and SCL rise      | 100 kHz mode | —          | 1000 | ns    |                                             |

|               |         | time                  | 400 kHz mode | 20 + 0.1Св | 300  | ns    | CB is specified to be from 10-400 pF        |

| 103*          | TF      | SDA and SCL fall      | 100 kHz mode | —          | 300  | ns    |                                             |

|               |         | time                  | 400 kHz mode | 20 + 0.1Св | 300  | ns    | CB is specified to be from 10-400 pF        |

| 90*           | TSU:STA | Start condition       | 100 kHz mode | 4.7        | _    | μS    | Only relevant for                           |

|               |         | setup time            | 400 kHz mode | 0.6        | _    | μS    | Repeated Start condition                    |

| 91*           | THD:STA | Start condition hold  | 100 kHz mode | 4.0        | _    | μS    | After this period the first                 |

|               |         | time                  | 400 kHz mode | 0.6        | —    | μS    | clock pulse is generated                    |

| 106*          | THD:DAT | Data input hold time  | 100 kHz mode | 0          | —    | ns    |                                             |

|               |         |                       | 400 kHz mode | 0          | 0.9  | μS    |                                             |

| 107*          | TSU:DAT | Data input setup      | 100 kHz mode | 250        |      | ns    | (Note 2)                                    |

|               |         | time                  | 400 kHz mode | 100        | _    | ns    |                                             |

| 92*           | Tsu:sto | Stop condition        | 100 kHz mode | 4.7        |      | μS    | -                                           |

|               |         | setup time            | 400 kHz mode | 0.6        | —    | μS    |                                             |

| 109*          | ΤΑΑ     | Output valid from     | 100 kHz mode | —          | 3500 | ns    | (Note 1)                                    |

|               |         | clock                 | 400 kHz mode | —          | —    | ns    |                                             |

| 110*          | TBUF    | Bus free time         | 100 kHz mode | 4.7        |      | μS    | Time the bus must be free                   |

|               |         |                       | 400 kHz mode | 1.3        |      | μS    | before a new transmission<br>can start      |

|               | Св      | Bus capacitive loadir | ng           | —          | 400  | pF    |                                             |

# TABLE 17-16: I<sup>2</sup>C<sup>™</sup> BUS DATA REQUIREMENTS

These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

**2:** A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement TsU:DAT  $\ge$  250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

\*

### TABLE 17-22: DATA EEPROM MEMORY ENDURANCE SPECIFICATIONS FOR PIC16F886/7-H (High Temp.)

| Param<br>No. | Sym. | Characteristic | Min. | Тур. | Max. | Units | Conditions                                     |

|--------------|------|----------------|------|------|------|-------|------------------------------------------------|

| D120A        | ED   | Byte Endurance | 5K   | 50K  |      | E/W   | $126^\circ C \le T \texttt{A} \le 150^\circ C$ |

#### TABLE 17-23: OSCILLATOR PARAMETERS FOR PIC16F886/7-H (High Temp.)

| Param<br>No. | Sym.   | Characteristic                                 | Frequency<br>Tolerance | Min. | Тур. | Max. | Units | Conditions                                          |

|--------------|--------|------------------------------------------------|------------------------|------|------|------|-------|-----------------------------------------------------|

| OS08         | INTosc | Int. Calibrated INTOSC<br>Freq. <sup>(1)</sup> | ±7.5%                  | 7.4  | 8.0  | 8.6  |       | $2.1V \le VDD \le 5.5V$<br>-40°C $\le TA \le 150°C$ |

**Note 1:** To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1 µF and 0.01 µF values in parallel are recommended.

#### TABLE 17-24: WATCHDOG TIMER SPECIFICATIONS FOR PIC16F886/7-H (High Temp.)

| Param<br>No. | Sym. | Characteristic                                   | Min. | Тур. | Max. | Units | Conditions        |

|--------------|------|--------------------------------------------------|------|------|------|-------|-------------------|

| 31           | Twdt | Watchdog Timer Time-out Period<br>(No Prescaler) | 10   | 20   | 70   | ms    | 150°C Temperature |

#### TABLE 17-25: COMPARATOR SPECIFICATIONS FOR PIC16F886/7-H (High Temp.)

| Param<br>No. | Sym. | Characteristic       | Min. | Тур. | Max. | Units | Conditions    |

|--------------|------|----------------------|------|------|------|-------|---------------|

| CM01         | Vos  | Input Offset Voltage |      | ±5   | ±20  | mV    | (Vdd - 1.5)/2 |

#### TABLE 17-26: ADC SPECIFICATIONS FOR PIC16F886/7-H (High Temp.)

| Param<br>No. | Sym. | Characteristic | Min. | Тур. | Max. | Units | Conditions  |

|--------------|------|----------------|------|------|------|-------|-------------|

| AD02         | Eı∟  | Integral Error |      | _    | ±1.5 | LSb   | VDD = 5.12V |

| AD07         | Egn  | Gain Error     |      | —    | ±1.5 | LSb   | VDD = 5.12V |

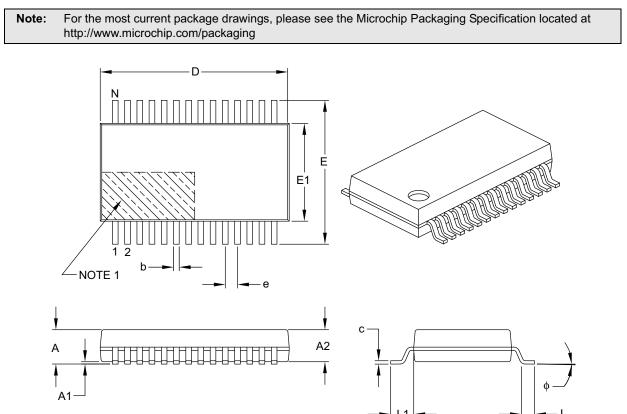

## 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

|                          | Units            |          | MILLIMETERS |       |  |  |

|--------------------------|------------------|----------|-------------|-------|--|--|

|                          | Dimension Limits | MIN      | NOM         | MAX   |  |  |

| Number of Pins           | N                | 28       |             |       |  |  |

| Pitch                    | е                | 0.65 BSC |             |       |  |  |

| Overall Height           | А                | -        | -           | 2.00  |  |  |

| Molded Package Thickness | A2               | 1.65     | 1.75        | 1.85  |  |  |

| Standoff                 | A1               | 0.05     | -           | _     |  |  |

| Overall Width            | E                | 7.40     | 7.80        | 8.20  |  |  |

| Molded Package Width     | E1               | 5.00     | 5.30        | 5.60  |  |  |

| Overall Length           | D                | 9.90     | 10.20       | 10.50 |  |  |

| Foot Length              | L                | 0.55     | 0.75        | 0.95  |  |  |

| Footprint                | L1               | 1.25 REF |             |       |  |  |

| Lead Thickness           | С                | 0.09     | -           | 0.25  |  |  |

| Foot Angle               |                  | 0°       | 4°          | 8°    |  |  |

| Lead Width               | b                | 0.22     | -           | 0.38  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

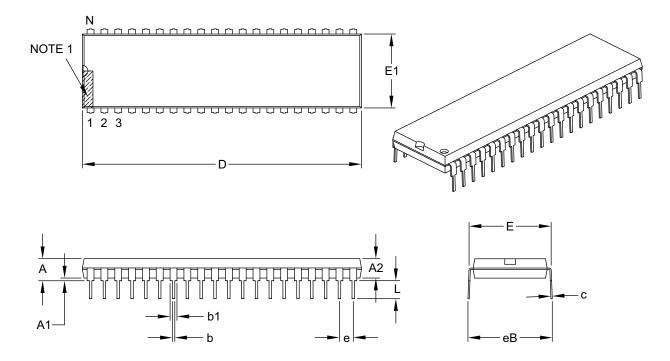

## 40-Lead Plastic Dual In-Line (P) – 600 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |          |     | INCHES |  |  |

|----------------------------|------------------|----------|-----|--------|--|--|

|                            | Dimension Limits | MIN      | NOM | MAX    |  |  |

| Number of Pins             | N                |          |     |        |  |  |

| Pitch                      | е                | .100 BSC |     |        |  |  |

| Top to Seating Plane       | A                | -        | -   | .250   |  |  |

| Molded Package Thickness   | A2               | .125     | -   | .195   |  |  |

| Base to Seating Plane      | A1               | .015     | -   | _      |  |  |

| Shoulder to Shoulder Width | E                | .590     | -   | .625   |  |  |

| Molded Package Width       | E1               | .485     | -   | .580   |  |  |

| Overall Length             | D                | 1.980    | -   | 2.095  |  |  |

| Tip to Seating Plane       | L                | .115     | -   | .200   |  |  |

| Lead Thickness             | С                | .008     | -   | .015   |  |  |

| Upper Lead Width           | b1               | .030     | -   | .070   |  |  |

| Lower Lead Width           |                  | .014     | -   | .023   |  |  |

| Overall Row Spacing §      | eB               | _        | -   | .700   |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-016B