Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 201010                     |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 14x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 44-QFN (8x8)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f887-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

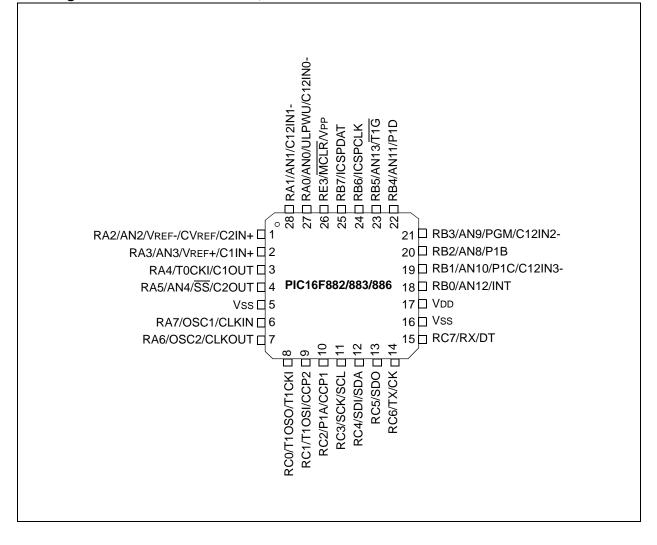

### Pin Diagrams – PIC16F882/883/886, 28-Pin QFN

| TABL | E 3:        | 3: 40-PIN PDIP ALLOCATION TABLE (PIC16F884/887) |             |             |          |        |         |           |         |             |

|------|-------------|-------------------------------------------------|-------------|-------------|----------|--------|---------|-----------|---------|-------------|

| 0/1  | 40-Pin PDIP | Analog                                          | Comparators | Timers      | ECCP     | EUSART | MSSP    | Interrupt | Pull-up | Basic       |

| RA0  | 2           | AN0/ULPWU                                       | C12IN0-     | —           | —        | _      | —       | —         | —       | —           |

| RA1  | 3           | AN1                                             | C12IN1-     | —           | _        |        |         | —         |         | —           |

| RA2  | 4           | AN2                                             | C2IN+       | —           | _        | _      |         | _         |         | VREF-/CVREF |

| RA3  | 5           | AN3                                             | C1IN+       | —           | _        | _      | _       | —         | _       | VREF+       |

| RA4  | 6           | _                                               | C1OUT       | T0CKI       | _        | _      |         | _         |         | —           |

| RA5  | 7           | AN4                                             | C2OUT       | —           | _        | _      | SS      | —         | _       | —           |

| RA6  | 14          | _                                               | _           | —           | _        | _      | _       | _         | _       | OSC2/CLKOUT |

| RA7  | 13          | _                                               |             | —           | _        | _      |         | _         | _       | OSC1/CLKIN  |

| RB0  | 33          | AN12                                            | _           | —           | _        | _      | _       | IOC/INT   | Y       | —           |

| RB1  | 34          | AN10                                            | C12IN3-     | —           | _        | _      | _       | IOC       | Y       | —           |

| RB2  | 35          | AN8                                             | _           | —           | _        | _      | _       | IOC       | Y       | —           |

| RB3  | 36          | AN9                                             | C12IN2-     | —           | _        | _      | _       | IOC       | Y       | PGM         |

| RB4  | 37          | AN11                                            | _           | —           | _        | _      |         | IOC       | Y       | —           |

| RB5  | 38          | AN13                                            |             | T1G         | _        | _      |         | IOC       | Y       | —           |

| RB6  | 39          | _                                               | _           | —           | _        | _      | _       | IOC       | Y       | ICSPCLK     |

| RB7  | 40          | —                                               | _           | —           | _        | _      | _       | IOC       | Y       | ICSPDAT     |

| RC0  | 15          | _                                               | _           | T1OSO/T1CKI | _        | _      |         | _         |         | —           |

| RC1  | 16          | —                                               | _           | T1OSI       | CCP2     | _      | _       | —         | _       | —           |

| RC2  | 17          | _                                               | _           | —           | CCP1/P1A | _      | _       | _         | _       | —           |

| RC3  | 18          | —                                               | —           | —           | _        | _      | SCK/SCL | —         | _       | —           |

| RC4  | 23          | _                                               | _           | —           | —        | _      | SDI/SDA | —         | —       | —           |

| RC5  | 24          | _                                               |             | —           | —        | _      | SDO     | —         | —       | _           |

| RC6  | 25          | —                                               | _           | —           | —        | TX/CK  | _       | —         | —       | —           |

| RC7  | 26          | —                                               |             | —           | —        | RX/DT  | _       | —         | _       | —           |

| RD0  | 19          | —                                               |             | —           | —        |        | —       | —         |         | —           |

| RD1  | 20          | —                                               |             | —           | —        |        | _       | —         | _       | —           |

| RD2  | 21          | —                                               | _           | _           | —        | _      | —       | —         | _       | —           |

| RD3  | 22          | —                                               | _           |             | —        | _      | _       | —         | _       | —           |

| RD4  | 27          | —                                               | _           | _           | —        | _      | —       | —         | _       | —           |

| RD5  | 28          | —                                               | _           |             | P1B      | _      | _       | —         | _       | —           |

| RD6  | 29          | —                                               | _           | _           | P1C      | _      | _       | —         | —       | —           |

| RD7  | 30          | —                                               | _           |             | P1D      | _      | —       | —         | _       | —           |

| RE0  | 8           | AN5                                             | _           | _           | —        |        | —       | _         | —       | _           |

| RE1  | 9           | AN6                                             | _           | _           |          |        |         | —         | —       | _           |

| RE2  | 10          | AN7                                             | -           | _           | —        | _      | —       | —         | _       | _           |

| RE3  | 1           | —                                               | _           | —           | —        | _      |         | —         | Y(1)    | MCLR/VPP    |

|      | 11          | _                                               | _           | _           |          | _      | _       | _         |         | Vdd         |

| _    | 32          | —                                               | _           |             |          | _      | _       | —         | _       | Vdd         |

|      | 12          | _                                               | _           | _           | —        |        | —       | _         | _       | Vss         |

| _    | 31          | —                                               | _           |             | —        | _      | —       | —         | _       | Vss         |

# TABLE 3: 40-PIN PDIP ALLOCATION TABLE (PIC16F884/887)

**Note 1:** Pull-up activated only with external MCLR configuration.

| Name                                                            | Function                    | Input<br>Type      | Output<br>Type | Description                                                                                       |

|-----------------------------------------------------------------|-----------------------------|--------------------|----------------|---------------------------------------------------------------------------------------------------|

| RA0/AN0/ULPWU/C12IN0-                                           | RA0                         | TTL                | CMOS           | General purpose I/O.                                                                              |

|                                                                 | AN0                         | AN                 | _              | A/D Channel 0 input.                                                                              |

|                                                                 | ULPWU                       | AN                 | —              | Ultra Low-Power Wake-up input.                                                                    |

|                                                                 | C12IN0-                     | AN                 | _              | Comparator C1 or C2 negative input.                                                               |

| RA1/AN1/C12IN1-                                                 | RA1                         | TTL                | CMOS           | General purpose I/O.                                                                              |

|                                                                 | AN1                         | AN                 | _              | A/D Channel 1 input.                                                                              |

|                                                                 | C12IN1-                     | AN                 | —              | Comparator C1 or C2 negative input.                                                               |

| RA2/AN2/Vref-/CVref/C2IN+                                       | RA2                         | TTL                | CMOS           | General purpose I/O.                                                                              |

|                                                                 | AN2                         | AN                 | _              | A/D Channel 2.                                                                                    |

|                                                                 | VREF-                       | AN                 | _              | A/D Negative Voltage Reference input.                                                             |

|                                                                 | CVREF                       | _                  | AN             | Comparator Voltage Reference output.                                                              |

|                                                                 | C2IN+                       | AN                 | _              | Comparator C2 positive input.                                                                     |

| RA3/AN3/Vref+/C1IN+                                             | RA3                         | TTL                | _              | General purpose I/O.                                                                              |

|                                                                 | AN3                         | AN                 | _              | A/D Channel 3.                                                                                    |

|                                                                 | VREF+                       | AN                 | —              | Programming voltage.                                                                              |

|                                                                 | C1IN+                       | AN                 | _              | Comparator C1 positive input.                                                                     |

| RA4/T0CKI/C1OUT                                                 | RA4                         | TTL                | CMOS           | General purpose I/O.                                                                              |

|                                                                 | T0CKI                       | ST                 | _              | Timer0 clock input.                                                                               |

|                                                                 | C10UT                       | _                  | CMOS           | Comparator C1 output.                                                                             |

| RA5/AN4/SS/C2OUT                                                | RA5                         | TTL                | CMOS           | General purpose I/O.                                                                              |

|                                                                 | AN4                         | AN                 | _              | A/D Channel 4.                                                                                    |

|                                                                 | SS                          | ST                 | _              | Slave Select input.                                                                               |

|                                                                 | C2OUT                       | _                  | CMOS           | Comparator C2 output.                                                                             |

| RA6/OSC2/CLKOUT                                                 | RA6                         | TTL                | CMOS           | General purpose I/O.                                                                              |

|                                                                 | OSC2                        | _                  | XTAL           | Master Clear with internal pull-up.                                                               |

|                                                                 | CLKOUT                      | —                  | CMOS           | Fosc/4 output.                                                                                    |

| RA7/OSC1/CLKIN                                                  | RA7                         | TTL                | CMOS           | General purpose I/O.                                                                              |

|                                                                 | OSC1                        | XTAL               | —              | Crystal/Resonator.                                                                                |

|                                                                 | CLKIN                       | ST                 | —              | External clock input/RC oscillator connection.                                                    |

| RB0/AN12/INT                                                    | RB0                         | TTL                | CMOS           | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |

|                                                                 | AN12                        | AN                 | _              | A/D Channel 12.                                                                                   |

|                                                                 | INT                         | ST                 | —              | External interrupt.                                                                               |

| RB1/AN10/P1C/C12IN3-                                            | RB1                         | TTL                | CMOS           | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |

|                                                                 | AN10                        | AN                 | _              | A/D Channel 10.                                                                                   |

|                                                                 | P1C                         | —                  | CMOS           | PWM output.                                                                                       |

|                                                                 | C12IN3-                     | AN                 | _              | Comparator C1 or C2 negative input.                                                               |

| RB2/AN8/P1B                                                     | RB2                         | TTL                | CMOS           | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |

|                                                                 | AN8                         | AN                 | _              | A/D Channel 8.                                                                                    |

|                                                                 | P1B                         | _                  | CMOS           | PWM output.                                                                                       |

| Legend: AN = Analog inpu<br>TTL = TTL compa<br>HV = High Voltag | It or output<br>tible input | CMOS<br>ST<br>XTAL | = CMO          | S compatible input or output OD = Open-Drain<br>itt Trigger input with CMOS levels                |

| TABLE 1-1: | PIC16F882/883/886 PINOUT DESCRIPTION  |

|------------|---------------------------------------|

| IADLE I-I. | FIG 10F002/003/000 FINUUT DESCRIFTION |

### FIGURE 2-4: PIC16F882 SPECIAL FUNCTION REGISTERS

|                                 | File    |                                 | File       |                     | File         |                       | File         |

|---------------------------------|---------|---------------------------------|------------|---------------------|--------------|-----------------------|--------------|

|                                 | Address |                                 | Address    |                     | Address      |                       | Addre        |

| ndirect addr. (1)               | 00h     | Indirect addr. (1)              | 80h        | Indirect addr. (1)  | 100h         | Indirect addr. (1)    | 180          |

| TMR0                            | 01h     | OPTION_REG                      | 81h        | TMR0                | 101h         | OPTION_REG            | 181          |

| PCL                             | 02h     | PCL                             | 82h        | PCL                 | 102h         | PCL                   | 182          |

| STATUS                          | 03h     | STATUS                          | 83h        | STATUS              | 103h         | STATUS                | 183ł         |

| FSR                             | 04h     | FSR                             | 84h        | FSR                 | 104h         | FSR                   | 184ł         |

| PORTA                           | 05h     | TRISA                           | 85h        | WDTCON              | 105h         | SRCON                 | 185ł         |

| PORTB                           | 06h     | TRISB                           | 86h        | PORTB               | 106h         | TRISB                 | 186ł         |

| PORTC                           | 07h     | TRISC                           | 87h        | CM1CON0             | 107h         | BAUDCTL               | 187h         |

|                                 | 08h     |                                 | 88h        | CM2CON0             | 108h         | ANSEL                 | 188h         |

| PORTE                           | 09h     | TRISE                           | 89h        | CM2CON1             | 109h         | ANSELH                | 189ł         |

| PCLATH                          | 0Ah     | PCLATH                          | 8Ah        | PCLATH              | 10Ah         | PCLATH                | 18Ał         |

| INTCON                          | 0Bh     | INTCON                          | 8Bh        | INTCON              | 10Bh         | INTCON                | 18Bł         |

| PIR1                            | 0Ch     | PIE1                            | 8Ch        | EEDAT               | 10Ch         | EECON1                | 18CI         |

| PIR2                            | 0Dh     | PIE2                            | 8Dh        | EEADR               | 10Dh         | EECON2 <sup>(1)</sup> | 18DI         |

| TMR1L                           | 0Eh     | PCON                            | 8Eh        | EEDATH              | 10Eh         | Reserved              | 18Eł         |

| TMR1H                           | 0Fh     | OSCCON                          | 8Fh        | EEADRH              | 10Fh         | Reserved              | 18Fł         |

| T1CON                           | 10h     | OSCTUNE                         | 90h        |                     | 110h         |                       | 190ł         |

| TMR2                            | 11h     | SSPCON2                         | 91h        |                     | 111h         |                       | 191h         |

| T2CON                           | 12h     | PR2                             | 92h        |                     | 112h         |                       | 192ł         |

| SSPBUF                          | 13h     | SSPADD                          | 93h        |                     | 113h         |                       | 193ł         |

| SSPCON                          | 14h     | SSPSTAT                         | 94h        |                     | 114h         |                       | 194ł         |

| CCPR1L                          | 15h     | WPUB                            | 95h        |                     | 115h         |                       | 195ł         |

| CCPR1H                          | 16h     | IOCB                            | 96h        |                     | 116h         |                       | 196ł         |

| CCP1CON                         | 17h     | VRCON                           | 97h        |                     | 117h         |                       | 197h         |

| RCSTA                           | 18h     | TXSTA                           | 98h        |                     | 118h         |                       | 198ł         |

| TXREG                           | 19h     | SPBRG                           | 99h        |                     | 119h         |                       | 199ł         |

| RCREG                           | 1Ah     | SPBRGH                          | 9Ah        |                     | 11Ah         |                       | 19Ał         |

| CCPR2L                          | 1Bh     | PWM1CON                         | 9Bh        |                     | 11Bh         |                       | 19Bł         |

| CCPR2H                          | 1Ch     | ECCPAS                          | 9Ch        |                     | 11Ch         |                       | 19CI         |

| CCP2CON                         | 1Dh     | PSTRCON                         | 9Dh        |                     | 11Dh         |                       | 19DI         |

| ADRESH                          | 1Eh     | ADRESL                          | 9Eh        |                     | 11Eh         |                       | 19Eł         |

| ADCON0                          | 1Fh     | ADCON1                          | 9Fh        |                     | 11Fh         |                       | 19Fł         |

|                                 | 20h     | General<br>Purpose<br>Registers | A0h        |                     | 120h         |                       | 1A0ł         |

| General<br>Purpose<br>Registers |         | 32 Bytes                        | BFh<br>C0h |                     |              |                       |              |

| 96 Bytes                        |         |                                 | EFh        |                     | 16Fh         |                       | 1EFI         |

|                                 | 7Fh     | accesses<br>70h-7Fh             | F0h<br>FFh | accesses<br>70h-7Fh | 170h<br>17Fh | accesses<br>70h-7Fh   | 1F0i<br>1FFi |

| Bank 0                          |         | Bank 1                          |            | Bank 2              |              | Bank 3                |              |

**Note 1:** Not a physical register.

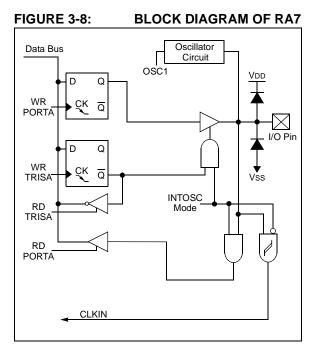

### 3.2.3.8 RA7/OSC1/CLKIN

Figure 3-8 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- a crystal/resonator connection

- · a clock input

### TABLE 3-1: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name       | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|------------|--------|--------|--------|--------|--------|--------|---------|--------|---------------------|

| ADCON0     | ADCS1  | ADCS0  | CHS3   | CHS2   | CHS1   | CHS0   | GO/DONE | ADON   | 104                 |

| ANSEL      | ANS7   | ANS6   | ANS5   | ANS4   | ANS3   | ANS2   | ANS1    | ANS0   | 41                  |

| CM1CON0    | C10N   | C10UT  | C10E   | C1POL  |        | C1R    | C1CH1   | C1CH0  | 89                  |

| CM2CON0    | C2ON   | C2OUT  | C2OE   | C2POL  |        | C2R    | C2CH1   | C2CH0  | 90                  |

| CM2CON1    | MC1OUT | MC2OUT | C1RSEL | C2RSEL |        | _      | T1GSS   | C2SYNC | 92                  |

| PCON       | _      | _      | ULPWUE | SBOREN |        | _      | POR     | BOR    | 37                  |

| OPTION_REG | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1     | PS0    | 31                  |

| PORTA      | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1     | RA0    | 40                  |

| SSPCON     | WCOL   | SSPOV  | SSPEN  | CKP    | SSPM3  | SSPM2  | SSPM1   | SSPM0  | 177                 |

| TRISA      | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1  | TRISA0 | 40                  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

| R/W-1   | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|---------|-------|-------|-------|-------|-------|-------|-------|

| WPUB7   | WPUB6 | WPUB5 | WPUB4 | WPUB3 | WPUB2 | WPUB1 | WPUB0 |

| bit 7   |       |       |       |       |       |       | bit 0 |

|         |       |       |       |       |       |       |       |

| Legend: |       |       |       |       |       |       |       |

### REGISTER 3-7: WPUB: WEAK PULL-UP PORTB REGISTER

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 7-0 WPUB<7:0>: Weak Pull-up Register bit

- 1 = Pull-up enabled

- 0 = Pull-up disabled

Note 1: Global RBPU bit of the OPTION register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

### REGISTER 3-8: IOCB: INTERRUPT-ON-CHANGE PORTB REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IOCB7 | IOCB6 | IOCB5 | IOCB4 | IOCB3 | IOCB2 | IOCB1 | IOCB0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 IOCB<7:0>: Interrupt-on-Change PORTB Control bit

1 = Interrupt-on-change enabled

0 = Interrupt-on-change disabled

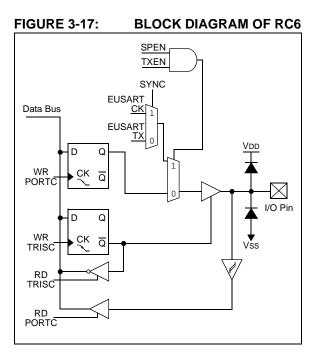

### 3.5.7 RC6/TX/CK

Figure 3-17 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an asynchronous serial output

- a synchronous clock I/O

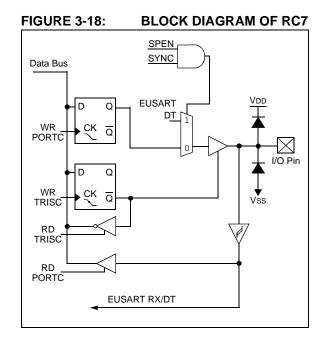

### 3.5.8 RC7/RX/DT

Figure 3-18 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- an asynchronous serial input

- a synchronous serial data I/O

#### TABLE 3-3: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name    | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|--------|--------|---------|---------|---------|--------|--------|--------|---------------------|

| CCP1CON | P1M1   | P1M0   | DC1B1   | DC1B0   | CCP1M3  | CCP1M2 | CCP1M1 | CCP1M0 | 122                 |

| CCP2CON |        |        | DC2B1   | DC2B0   | CCP2M3  | CCP2M2 | CCP2M1 | CCP2M0 | 123                 |

| PORTC   | RC7    | RC6    | RC5     | RC4     | RC3     | RC2    | RC1    | RC0    | 54                  |

| PSTRCON | _      |        |         | STRSYNC | STRD    | STRC   | STRB   | STRA   | 144                 |

| RCSTA   | SPEN   | RX9    | SREN    | CREN    | ADDEN   | FERR   | OERR   | RX9D   | 158                 |

| SSPCON  | WCOL   | SSPOV  | SSPEN   | CKP     | SSPM3   | SSPM2  | SSPM1  | SSPM0  | 177                 |

| T1CON   | T1GINV | TMR1GE | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 81                  |

| TRISC   | TRISC7 | TRISC6 | TRISC5  | TRISC4  | TRISC3  | TRISC2 | TRISC1 | TRISC0 | 54                  |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

### 8.2 Comparator Control

Each comparator has a separate control and Configuration register: CM1CON0 for Comparator C1 and CM2CON0 for Comparator C2. In addition, Comparator C2 has a second control register, CM2CON1, for controlling the interaction with Timer1 and simultaneous reading of both comparator outputs.

The CM1CON0 and CM2CON0 registers (see Registers 8-1 and 8-2, respectively) contain the control and Status bits for the following:

- Enable

- Input selection

- Reference selection

- Output selection

- Output polarity

### 8.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

### 8.2.2 COMPARATOR INPUT SELECTION

The CxCH<1:0> bits of the CMxCON0 register direct one of four analog input pins to the comparator inverting input.

| Note: | To use C <u>x</u> IN+ and C <u>x</u> IN- pins as analog |

|-------|---------------------------------------------------------|

|       | inputs, the appropriate bits must be set in             |

|       | the ANSEL and ANSELH registers and                      |

|       | the corresponding TRIS bits must also be                |

|       | set to disable the output drivers.                      |

# 8.2.3 COMPARATOR REFERENCE SELECTION

Setting the CxR bit of the CMxCON0 register directs an internal voltage reference or an analog input pin to the non-inverting input of the comparator. See **Section 8.10 "Comparator Voltage Reference"** for more information on the internal voltage reference module.

### 8.2.4 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CM2CON1 register. In order to make the output available for an external connection, the following conditions must be true:

- CxOE bit of the CMxCON0 register must be set

- · Corresponding TRIS bit must be cleared

- CxON bit of the CMxCON0 register must be set

**Note 1:** The CxOE bit overrides the PORT data latch. Setting the CxON has no impact on the port override.

2: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

### 8.2.5 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 8-1 shows the output state versus input conditions, including polarity control.

#### TABLE 8-1: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition   | CxPOL | CxOUT |

|-------------------|-------|-------|

| CxVIN - > CxVIN + | 0     | 0     |

| CxVIN- < CxVIN+   | 0     | 1     |

| CxVIN - > CxVIN + | 1     | 1     |

| CxVIN- < CxVIN+   | 1     | 0     |

### 8.3 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference specifications in **Section 17.0 "Electrical Specifications"** for more details.

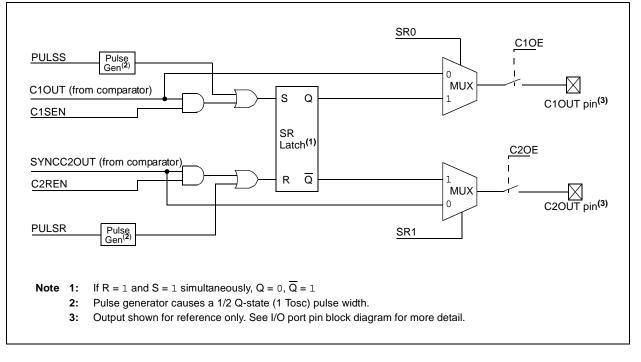

### 8.9 Comparator SR Latch

The SR latch module provides additional control of the comparator outputs. The module consists of a single SR latch and output multiplexers. The SR latch can be set, reset or toggled by the comparator outputs. The SR latch may also be set or reset, independent of comparator output, by control bits in the SRCON control register. The SR latch output multiplexers select whether the latch outputs or the comparator outputs are directed to the I/O port logic for eventual output to a pin.

### 8.9.1 LATCH OPERATION

The latch is a Set-Reset latch that does not depend on a clock source. Each of the Set and Reset inputs are active-high. Each latch input is connected to a comparator output and a software controlled pulse generator. The latch can be set by C1OUT or the PULSS bit of the SRCON register. The latch can be reset by C2OUT or the PULSR bit of the SRCON register. The latch is reset-dominant, therefore, if both Set and Reset inputs are high the latch will go to the Reset state. Both the PULSS and PULSR bits are self resetting which means that a single write to either of the bits is all that is necessary to complete a latch set or Reset operation.

### 8.9.2 LATCH OUTPUT

The SR<1:0> bits of the SRCON register control the latch output multiplexers and determine four possible output configurations. In these four configurations, the CxOUT I/O port logic is connected to:

- C1OUT and C2OUT

- C1OUT and SR latch  $\overline{Q}$

- C2OUT and SR latch Q

- SR latch Q and Q

After any Reset, the default output configuration is the unlatched C1OUT and C2OUT mode. This maintains compatibility with devices that do not have the SR latch feature.

The applicable TRIS bits of the corresponding ports must be cleared to enable the port pin output drivers. Additionally, the CxOE comparator output enable bits of the CMxCON0 registers must be set in order to make the comparator or latch outputs available on the output pins. The latch configuration enable states are completely independent of the enable states for the comparators.

### FIGURE 8-7: SR LATCH SIMPLIFIED BLOCK DIAGRAM

| IADEE J-2. |           |               | 700001    |        |        |        |         |        |                     |

|------------|-----------|---------------|-----------|--------|--------|--------|---------|--------|---------------------|

| Name       | Bit 7     | Bit 6         | Bit 5     | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

| ADCON0     | ADCS1     | ADCS0         | CHS3      | CHS2   | CHS1   | CHS0   | GO/DONE | ADON   | 104                 |

| ADCON1     | ADFM      |               | VCFG1     | VCFG0  | _      | _      | _       |        | 105                 |

| ANSEL      | ANS7      | ANS6          | ANS5      | ANS4   | ANS3   | ANS2   | ANS1    | ANS0   | 41                  |

| ANSELH     | —         | —             | ANS13     | ANS12  | ANS11  | ANS10  | ANS9    | ANS8   | 49                  |

| ADRESH     | A/D Resul | lt Register I | High Byte |        |        |        |         |        | 106                 |

| ADRESL     | A/D Resul | lt Register I | Low Byte  |        |        |        |         |        | 106                 |

| INTCON     | GIE       | PEIE          | TOIE      | INTE   | RBIE   | T0IF   | INTF    | RBIF   | 32                  |

| PIE1       | —         | ADIE          | RCIE      | TXIE   | SSPIE  | CCP1IE | TMR2IE  | TMR1IE | 33                  |

| PIR1       |           | ADIF          | RCIF      | TXIF   | SSPIF  | CCP1IF | TMR2IF  | TMR1IF | 35                  |

| PORTA      | RA7       | RA6           | RA5       | RA4    | RA3    | RA2    | RA1     | RA0    | 40                  |

| PORTB      | RB7       | RB6           | RB5       | RB4    | RB3    | RB2    | RB1     | RB0    | 49                  |

| PORTE      | —         | —             | —         | —      | RE3    | RE2    | RE1     | RE0    | 60                  |

| TRISA      | TRISA7    | TRISA6        | TRISA5    | TRISA4 | TRISA3 | TRISA2 | TRISA1  | TRISA0 | 40                  |

| TRISB      | TRISB7    | TRISB6        | TRISB5    | TRISB4 | TRISB3 | TRISB2 | TRISB1  | TRISB0 | 49                  |

| TRISE      |           |               |           |        | TRISE3 | TRISE2 | TRISE1  | TRISE0 | 60                  |

TABLE 9-2: SUMMARY OF ASSOCIATED ADC REGISTERS

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for ADC module.

### 11.5.3 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 11-4.

### EQUATION 11-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

### TABLE 11-3:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

### TABLE 11-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

| R/W-0         | R/W-0                                                                                 | R/W-0                                            | R/W-0          | R/W-0            | R-0                                  | R-0             | R-x   |  |  |  |

|---------------|---------------------------------------------------------------------------------------|--------------------------------------------------|----------------|------------------|--------------------------------------|-----------------|-------|--|--|--|

| SPEN          | RX9                                                                                   | SREN                                             | CREN           | ADDEN            | FERR                                 | OERR            | RX9D  |  |  |  |

| bit 7         |                                                                                       |                                                  |                |                  |                                      | •               | bit 0 |  |  |  |

|               |                                                                                       |                                                  |                |                  |                                      |                 |       |  |  |  |

| Legend:       |                                                                                       |                                                  |                |                  |                                      |                 |       |  |  |  |

| R = Readable  |                                                                                       | W = Writable                                     |                | -                | nented bit, read                     |                 |       |  |  |  |

| -n = Value at | POR                                                                                   | '1' = Bit is set                                 |                | '0' = Bit is cle | ared                                 | x = Bit is unkr | nown  |  |  |  |

| bit 7         | SPEN: Serial                                                                          | Port Enable bit                                  | t              |                  |                                      |                 |       |  |  |  |

|               | •                                                                                     | rt enabled (con<br>rt disabled (hel              | -              | T and TX/CK p    | ins as serial por                    | rt pins)        |       |  |  |  |

| bit 6         | <b>RX9:</b> 9-bit Re                                                                  | ceive Enable b                                   | it             |                  |                                      |                 |       |  |  |  |

|               |                                                                                       | -bit reception<br>3-bit reception                |                |                  |                                      |                 |       |  |  |  |

| bit 5         | SREN: Single                                                                          | e Receive Enab                                   | le bit         |                  |                                      |                 |       |  |  |  |

|               |                                                                                       | Asynchronous mode:                               |                |                  |                                      |                 |       |  |  |  |

|               |                                                                                       | Don't care                                       |                |                  |                                      |                 |       |  |  |  |

|               | -                                                                                     | Synchronous mode – Master:                       |                |                  |                                      |                 |       |  |  |  |

|               | <ul> <li>1 = Enables single receive</li> <li>0 = Disables single receive</li> </ul>   |                                                  |                |                  |                                      |                 |       |  |  |  |

|               |                                                                                       | This bit is cleared after reception is complete. |                |                  |                                      |                 |       |  |  |  |

|               | -                                                                                     | Synchronous mode – Slave                         |                |                  |                                      |                 |       |  |  |  |

|               | Don't care                                                                            |                                                  |                |                  |                                      |                 |       |  |  |  |

| bit 4         | CREN: Conti                                                                           | CREN: Continuous Receive Enable bit              |                |                  |                                      |                 |       |  |  |  |

|               | Asynchronous mode:                                                                    |                                                  |                |                  |                                      |                 |       |  |  |  |

|               |                                                                                       | 1 = Enables receiver                             |                |                  |                                      |                 |       |  |  |  |

|               | 0 = Disables receiver<br><u>Synchronous mode</u> :                                    |                                                  |                |                  |                                      |                 |       |  |  |  |

|               | 1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN) |                                                  |                |                  |                                      |                 |       |  |  |  |

|               | <ul> <li>0 = Disables continuous receive</li> </ul>                                   |                                                  |                |                  |                                      |                 |       |  |  |  |

| bit 3         | ADDEN: Add                                                                            | ress Detect En                                   | able bit       |                  |                                      |                 |       |  |  |  |

|               | Asynchronou                                                                           | Asynchronous mode 9-bit (RX9 = 1):               |                |                  |                                      |                 |       |  |  |  |

|               | 0 = Disables                                                                          |                                                  | ion, all bytes |                  | d the receive bu<br>nd ninth bit can |                 |       |  |  |  |

|               | Don't care                                                                            |                                                  |                |                  |                                      |                 |       |  |  |  |

| bit 2         | FERR: Frami                                                                           | -                                                |                |                  |                                      |                 |       |  |  |  |

|               | 1 = Framing<br>0 = No frami                                                           |                                                  | pdated by rea  | ading RCREG I    | register and rec                     | eive next valid | byte) |  |  |  |

| bit 1         | OERR: Overr                                                                           |                                                  |                |                  |                                      |                 |       |  |  |  |

|               | 1 = Overrun<br>0 = No overr                                                           | error (can be cl<br>un error                     | eared by clea  | aring bit CREN   | )                                    |                 |       |  |  |  |

| bit 0         | RX9D: Ninth                                                                           | bit of Received                                  | Data           |                  |                                      |                 |       |  |  |  |

|               | This can be a                                                                         | ddress/data bit                                  | or a parity bi | t and must be o  | calculated by us                     | er firmware.    |       |  |  |  |

# REGISTER 12-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER<sup>(1)</sup>

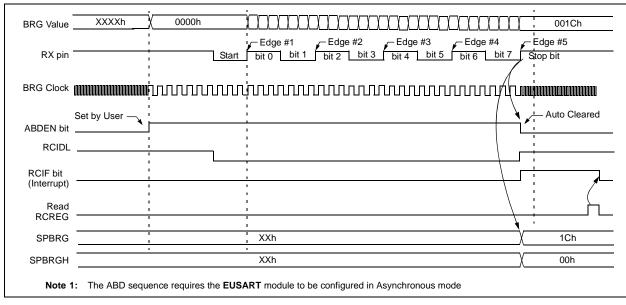

### 12.3.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCTL register starts the auto-baud calibration sequence (Figure 12-6). While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRG begins counting up using the BRG counter clock as shown in Table 12-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGH, SPBRG register pair, the ABDEN bit is automatically cleared and the RCIF interrupt flag is set. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded. When calibrating for modes that do not use the SPBRGH register the user can verify that the SPBRG register did not overflow by checking for 00h in the SPBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 12-6. During ABD, both the SPBRGH and SPBRG registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGH and SPBRG registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte <u>following</u> the Break character (see Section 12.3.2 "Auto-Wake-up on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- **3:** During the auto-baud process, the autobaud counter starts counting at 1. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPBRGH:SPBRG register pair.

#### TABLE 12-6: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

**Note:** During the ABD sequence, SPBRG and SPBRGH registers are both used as a 16-bit counter, independent of BRG16 setting.

#### FIGURE 12-6: AUTOMATIC BAUD RATE CALIBRATION

# 13.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

### 13.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit<sup>™</sup> (I<sup>2</sup>C<sup>™</sup>)

- Full Master mode

- Slave mode (with general address call).

The  $I^2C$  interface supports the following modes in hardware:

- Master mode

- Multi-Master mode

- Slave mode.

### 13.2 Control Registers

The MSSP module has three associated registers. These include a STATUS register and two control registers.

Register 13-1 shows the MSSP STATUS register (SSPSTAT), Register 13-2 shows the MSSP Control Register 1 (SSPCON), and Register 13-3 shows the MSSP Control Register 2 (SSPCON2).

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. The buffer full bit BF of the SSPSTAT register indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP Interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 13-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable, and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP STATUS register (SSPSTAT register) indicates the various status conditions.

### 13.3.2 ENABLING SPI I/O

To enable the serial port, SSP Enable bit SSPEN of the SSPCON register must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCON registers, and then set the <u>SSPEN</u> bit. This configures the SDI, SDO, SCK and <u>SS</u> pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> bit cleared

- SCK (Master mode) must have TRISC<3> bit cleared

- SCK (Slave mode) must have TRISC<3> bit set

- SS must have TRISA<5> bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

### EXAMPLE 13-1: LOADING THE SSPBUF (SSPSR) REGISTER

| LOOP | GOTO  | SSPSTAT, BF<br>LOOP<br>SSPBUF, W | ;Has data been received (transmit complete)?<br>;No<br>;WREG reg = contents of SSPBUF |

|------|-------|----------------------------------|---------------------------------------------------------------------------------------|

|      | MOVWF | RXDATA                           | ;Save in user RAM, if data is meaningful                                              |

|      |       | TXDATA, W<br>SSPBUF              | ;W reg = contents of TXDATA<br>;New data to xmit                                      |

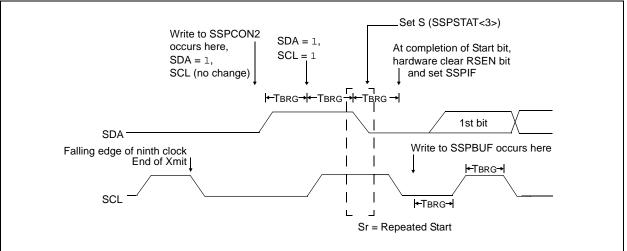

### 13.4.7 I<sup>2</sup>C<sup>™</sup> MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2 register) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be de-asserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG, while SCL is high. Following this, the RSEN bit (SSPCON2 register) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit (SSPSTAT register) will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data "1".

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode), or eight bits of data (7-bit mode).

### 13.4.7.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur).

Note: Because queuing of events is not allowed, writing of the lower five bits of SSPCON2 is disabled until the Repeated Start condition is complete.

# FIGURE 13-14: REPEAT START CONDITION WAVEFORM

| RLF              | Rotate Left f through Carry                                                                                                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RLF f,d                                                                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                          |

| Operation:       | See description below                                                                                                                                                                                                |

| Status Affected: | С                                                                                                                                                                                                                    |

| Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is stored<br>back in register 'f'. |

| Words:           | 1                                                                                                                                                                                                                    |

| Cycles:          | 1                                                                                                                                                                                                                    |

| Example:         | RLF REG1,0                                                                                                                                                                                                           |

|                  | Before Instruction<br>REG1 = 1110 0110<br>C = 0                                                                                                                                                                      |

|                  | After Instruction                                                                                                                                                                                                    |

|                  | REG1 = 1110 0110<br>W = 1100 1100                                                                                                                                                                                    |

|                  | C = 1                                                                                                                                                                                                                |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                          |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                       |

| Operation:       | See description below                                                                                                                                                                                                 |

| Status Affected: | С                                                                                                                                                                                                                     |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is placed<br>back in register 'f'. |

|                  | C Register f                                                                                                                                                                                                          |

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                      |

| Operands:        | None                                                                                                                                                                                                                               |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow \text{WDT,} \\ 0 \rightarrow \text{WDT prescaler,} \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \text{PD} \end{array}$                                                         |

| Status Affected: | TO, PD                                                                                                                                                                                                                             |

| Description:     | The power-down Status bit, $\overline{PD}$<br>is cleared. Time-out Status bit,<br>$\overline{TO}$ is set. Watchdog Timer and<br>its prescaler are cleared.<br>The processor is put into Sleep<br>mode with the oscillator stopped. |

| SUBLW            | Subtract W from literal                                                                                                  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                 |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                        |  |  |  |  |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                 |  |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the 8-bit literal 'k'. The result is placed in the W register. |  |  |  |  |

|                  | C = 0 $W > k$                                                                                                            |  |  |  |  |

| <b>C</b> = 0 | W > k                     |

|--------------|---------------------------|

| <b>C</b> = 1 | $W \leq k$                |

| DC = 0       | W<3:0> > k<3:0>           |

| DC = 1       | $W < 3:0 > \le k < 3:0 >$ |

| SUBWF            | Subtract W from f                                                                                                                                                                           |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                                  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                           |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                       |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                    |  |  |  |

| Description:     | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is<br>'0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |

| <b>C</b> = 0 | W > f                     |

|--------------|---------------------------|

| <b>C</b> = 1 | $W \leq f$                |

| DC = 0       | W<3:0> > f<3:0>           |

| DC = 1       | $W < 3:0 > \le f < 3:0 >$ |

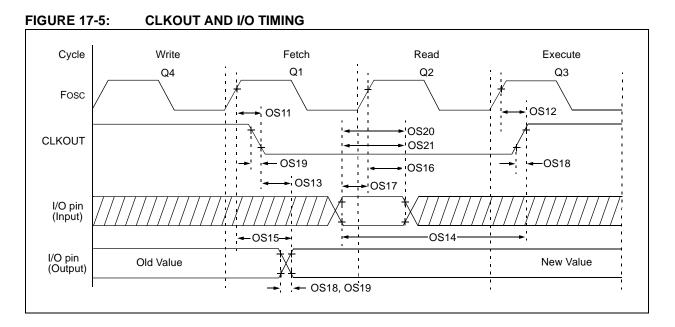

### TABLE 17-3: CLKOUT AND I/O TIMING PARAMETERS

| Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature -40°C $\leq$ TA $\leq$ +125°C |          |                                                             |               |          |          |       |                          |

|----------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------|---------------|----------|----------|-------|--------------------------|

| Param<br>No.                                                                                                   | Sym.     | Characteristic                                              | Min.          | Тур†     | Max.     | Units | Conditions               |

| OS11                                                                                                           | TosH2ckL | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                             | —             | —        | 70       | ns    | VDD = 5.0V               |

| OS12                                                                                                           | TosH2ckH | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                             |               | _        | 72       | ns    | VDD = 5.0V               |

| OS13                                                                                                           | TckL2IoV | CLKOUT↓ to Port out valid <sup>(1)</sup>                    | _             | _        | 20       | ns    |                          |

| OS14                                                                                                           | ТюV2скН  | Port input valid before CLKOUT <sup>(1)</sup>               | Tosc + 200 ns | _        |          | ns    |                          |

| OS15*                                                                                                          | TosH2IoV | Fosc↑ (Q1 cycle) to Port out valid                          | —             | 50       | 70       | ns    | VDD = 5.0V               |

| OS16                                                                                                           | TosH2iol | Fosc↑ (Q2 cycle) to Port input invalid (I/O in hold time)   | 50            | —        | _        | ns    | VDD = 5.0V               |

| OS17                                                                                                           | TioV2osH | Port input valid to Fosc↑ (Q2 cycle)<br>(I/O in setup time) | 20            |          | _        | ns    |                          |

| OS18                                                                                                           | TIOR     | Port output rise time <sup>(2)</sup>                        |               | 15<br>40 | 72<br>32 | ns    | VDD = 2.0V<br>VDD = 5.0V |

| OS19                                                                                                           | TIOF     | Port output fall time <sup>(2)</sup>                        |               | 28<br>15 | 55<br>30 | ns    | VDD = 2.0V<br>VDD = 5.0V |

| OS20*                                                                                                          | TINP     | INT pin input high or low time                              | 25            | —        | _        | ns    |                          |

| OS21*                                                                                                          | Trap     | PORTA interrupt-on-change new<br>input level time           | Тсү           | —        |          | ns    |                          |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated.

Note 1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

2: Includes OSC2 in CLKOUT mode.

### TABLE 17-11: PIC16F882/883/884/886/887 A/D CONVERSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                                                       |      |              |      |       |                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------|------|--------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                                                                                                         | Sym. | Characteristic                                                        | Min. | Тур†         | Max. | Units | Conditions                                                                                                                                                |

| AD130*                                                                                                               | TAD  | A/D Clock Period                                                      | 1.6  | —            | 9.0  | μS    | Tosc-based, VREF $\geq$ 3.0V                                                                                                                              |

|                                                                                                                      |      |                                                                       | 3.0  | —            | 9.0  | μS    | Tosc-based, VREF full range                                                                                                                               |

|                                                                                                                      |      | A/D Internal RC<br>Oscillator Period                                  | 3.0  | 6.0          | 9.0  | μS    | ADCS<1:0> = 11 (ADRC mode)<br>At VDD = 2.5V                                                                                                               |