Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 14x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-TQFP                                                                  |

| Supplier Device Package    | 44-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f887-i-pt |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 MEMORY ORGANIZATION

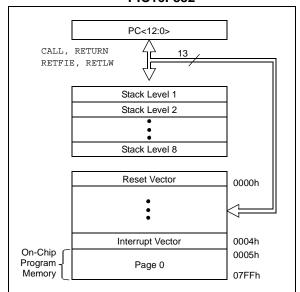

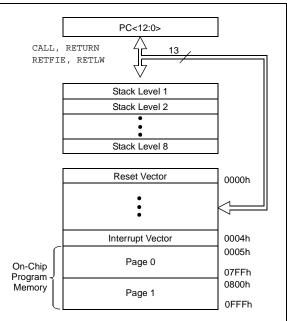

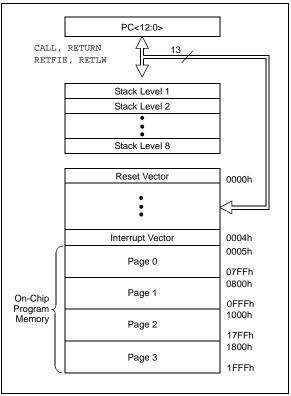

# 2.1 Program Memory Organization

The PIC16F882/883/884/886/887 devices have a 13-bit program counter capable of addressing a  $2K \times 14$  (0000h-07FFh) for the PIC16F882,  $4K \times 14$  (0000h-0FFFh) for the PIC16F883/PIC16F884, and  $8K \times 14$  (0000h-1FFFh) for the PIC16F886/PIC16F887 program memory space. Accessing a location above these boundaries will cause a wrap-around within the first  $8K \times 14$  space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figures 2-2 and 2-3).

#### FIGURE 2-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16F882

### FIGURE 2-2:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16F883/PIC16F884

# FIGURE 2-3:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16F886/PIC16F887

### FIGURE 2-4: PIC16F882 SPECIAL FUNCTION REGISTERS

|                                 | File    |                                 | File       |                     | File         |                       | File         |

|---------------------------------|---------|---------------------------------|------------|---------------------|--------------|-----------------------|--------------|

|                                 | Address |                                 | Address    |                     | Address      |                       | Addre        |

| ndirect addr. (1)               | 00h     | Indirect addr. (1)              | 80h        | Indirect addr. (1)  | 100h         | Indirect addr. (1)    | 180          |

| TMR0                            | 01h     | OPTION_REG                      | 81h        | TMR0                | 101h         | OPTION_REG            | 181          |

| PCL                             | 02h     | PCL                             | 82h        | PCL                 | 102h         | PCL                   | 182          |

| STATUS                          | 03h     | STATUS                          | 83h        | STATUS              | 103h         | STATUS                | 183ł         |

| FSR                             | 04h     | FSR                             | 84h        | FSR                 | 104h         | FSR                   | 184ł         |

| PORTA                           | 05h     | TRISA                           | 85h        | WDTCON              | 105h         | SRCON                 | 185ł         |

| PORTB                           | 06h     | TRISB                           | 86h        | PORTB               | 106h         | TRISB                 | 186ł         |

| PORTC                           | 07h     | TRISC                           | 87h        | CM1CON0             | 107h         | BAUDCTL               | 187h         |

|                                 | 08h     |                                 | 88h        | CM2CON0             | 108h         | ANSEL                 | 188h         |

| PORTE                           | 09h     | TRISE                           | 89h        | CM2CON1             | 109h         | ANSELH                | 189ł         |

| PCLATH                          | 0Ah     | PCLATH                          | 8Ah        | PCLATH              | 10Ah         | PCLATH                | 18Ał         |

| INTCON                          | 0Bh     | INTCON                          | 8Bh        | INTCON              | 10Bh         | INTCON                | 18Bł         |

| PIR1                            | 0Ch     | PIE1                            | 8Ch        | EEDAT               | 10Ch         | EECON1                | 18CI         |

| PIR2                            | 0Dh     | PIE2                            | 8Dh        | EEADR               | 10Dh         | EECON2 <sup>(1)</sup> | 18DI         |

| TMR1L                           | 0Eh     | PCON                            | 8Eh        | EEDATH              | 10Eh         | Reserved              | 18Eł         |

| TMR1H                           | 0Fh     | OSCCON                          | 8Fh        | EEADRH              | 10Fh         | Reserved              | 18Fł         |

| T1CON                           | 10h     | OSCTUNE                         | 90h        |                     | 110h         |                       | 190ł         |

| TMR2                            | 11h     | SSPCON2                         | 91h        |                     | 111h         |                       | 191h         |

| T2CON                           | 12h     | PR2                             | 92h        |                     | 112h         |                       | 192ł         |

| SSPBUF                          | 13h     | SSPADD                          | 93h        |                     | 113h         |                       | 193ł         |

| SSPCON                          | 14h     | SSPSTAT                         | 94h        |                     | 114h         |                       | 194ł         |

| CCPR1L                          | 15h     | WPUB                            | 95h        |                     | 115h         |                       | 195ł         |

| CCPR1H                          | 16h     | IOCB                            | 96h        |                     | 116h         |                       | 196ł         |

| CCP1CON                         | 17h     | VRCON                           | 97h        |                     | 117h         |                       | 197h         |

| RCSTA                           | 18h     | TXSTA                           | 98h        |                     | 118h         |                       | 198ł         |

| TXREG                           | 19h     | SPBRG                           | 99h        |                     | 119h         |                       | 199ł         |

| RCREG                           | 1Ah     | SPBRGH                          | 9Ah        |                     | 11Ah         |                       | 19Ał         |

| CCPR2L                          | 1Bh     | PWM1CON                         | 9Bh        |                     | 11Bh         |                       | 19Bł         |

| CCPR2H                          | 1Ch     | ECCPAS                          | 9Ch        |                     | 11Ch         |                       | 19CI         |

| CCP2CON                         | 1Dh     | PSTRCON                         | 9Dh        |                     | 11Dh         |                       | 19DI         |

| ADRESH                          | 1Eh     | ADRESL                          | 9Eh        |                     | 11Eh         |                       | 19Eł         |

| ADCON0                          | 1Fh     | ADCON1                          | 9Fh        |                     | 11Fh         |                       | 19Fł         |

|                                 | 20h     | General<br>Purpose<br>Registers | A0h        |                     | 120h         |                       | 1A0ł         |

| General<br>Purpose<br>Registers |         | 32 Bytes                        | BFh<br>C0h |                     |              |                       |              |

| 96 Bytes                        |         |                                 | EFh        |                     | 16Fh         |                       | 1EFI         |

|                                 | 7Fh     | accesses<br>70h-7Fh             | F0h<br>FFh | accesses<br>70h-7Fh | 170h<br>17Fh | accesses<br>70h-7Fh   | 1F0i<br>1FFi |

| Bank 0                          |         | Bank 1                          |            | Bank 2              |              | Bank 3                |              |

**Note 1:** Not a physical register.

#### 2.2.2.8 PCON Register

The Power Control (PCON) register (see Register 2-8) contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON register also controls the <u>Ultra Low-Power</u> Wake-up and software enable of the BOR.

# **REGISTER DEFINITIONS: PCON**

#### REGISTER 2-8: PCON: POWER CONTROL REGISTER

| U-0   | U-0 | R/W-0  | R/W-1                 | U-0 | U-0 | R/W-0 | R/W-x |

|-------|-----|--------|-----------------------|-----|-----|-------|-------|

| —     | —   | ULPWUE | SBOREN <sup>(1)</sup> | _   | —   | POR   | BOR   |

| bit 7 |     |        |                       |     |     |       | bit 0 |

| Legend:    |           |                                            |                                  |                       |  |  |  |  |  |

|------------|-----------|--------------------------------------------|----------------------------------|-----------------------|--|--|--|--|--|

| R = Reada  | ble bit   | W = Writable bit                           | U = Unimplemented bit,           | read as '0'           |  |  |  |  |  |

| -n = Value | at POR    | '1' = Bit is set                           | '0' = Bit is cleared             | x = Bit is unknown    |  |  |  |  |  |

|            |           |                                            |                                  |                       |  |  |  |  |  |

| bit 7-6    | Unimple   | mented: Read as '0'                        |                                  |                       |  |  |  |  |  |

| bit 5      | ULPWU     | E: Ultra Low-Power Wake-up                 | Enable bit                       |                       |  |  |  |  |  |

|            | 1 = Ultra | 1 = Ultra Low-Power Wake-up enabled        |                                  |                       |  |  |  |  |  |

|            | 0 = Ultra | Low-Power Wake-up disable                  | ed                               |                       |  |  |  |  |  |

| bit 4      | SBORE     | I: Software BOR Enable bit <sup>(1</sup> ) | )                                |                       |  |  |  |  |  |

|            | 1 = BOR   | 1 = BOR enabled                            |                                  |                       |  |  |  |  |  |

|            | 0 = BOR   | 0 = BOR disabled                           |                                  |                       |  |  |  |  |  |

| bit 3-2    | Unimple   | mented: Read as '0'                        |                                  |                       |  |  |  |  |  |

| bit 1      | POR: Po   | wer-on Reset Status bit                    |                                  |                       |  |  |  |  |  |

|            | 1 = No P  | 1 = No Power-on Reset occurred             |                                  |                       |  |  |  |  |  |

|            | 0 = A Po  | wer-on Reset occurred (must                | t be set in software after a Po  | wer-on Reset occurs)  |  |  |  |  |  |

| bit 0      | BOR: Br   | BOR: Brown-out Reset Status bit            |                                  |                       |  |  |  |  |  |

|            | 1 = No B  | rown-out Reset occurred                    |                                  |                       |  |  |  |  |  |

|            | 0 = A Bro | own-out Reset occurred (mus                | st be set in software after a Br | own-out Reset occurs) |  |  |  |  |  |

**Note 1:** BOREN<1:0> = 01 in the Configuration Word Register 1 for this bit to control the  $\overline{BOR}$ .

# 3.5 PORTC and TRISC Registers

PORTC is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISC (Register 3-10). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 3-4 shows how to initialize PORTC.

Reading the PORTC register (Register 3-9) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

The TRISC register (Register 3-10) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### EXAMPLE 3-4: INITIALIZING PORTC

| BANKSEL | PORTC       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTC       | ;Init PORTC            |

| BANKSEL | TRISC       | ;                      |

| MOVLW   | B`00001100′ | ;Set RC<3:2> as inputs |

| MOVWF   | TRISC       | ;and set RC<7:4,1:0>   |

|         |             | ;as outputs            |

|         |             |                        |

### REGISTER 3-9: PORTC: PORTC REGISTER

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RC7   | RC6   | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:                                                              |                  |                      |                    |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 7-0

RC<7:0>: PORTC General Purpose I/O Pin bit

1 = Port pin is > VIH 0 = Port pin is < VIL

REGISTER 3-10: TRISC: PORTC TRI-STATE REGISTER

| R/W-1       | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1 <sup>(1)</sup> | R/W-1 <sup>(1)</sup> |  |

|-------------|--------|--------|--------|--------|--------|----------------------|----------------------|--|

| TRISC7      | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1               | TRISC0               |  |

| bit 7 bit 0 |        |        |        |        |        |                      |                      |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 7-0 TRISC<7:0>: PORTC Tri-State Control bit

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

**Note 1:** TRISC<1:0> always reads '1' in LP Oscillator mode.

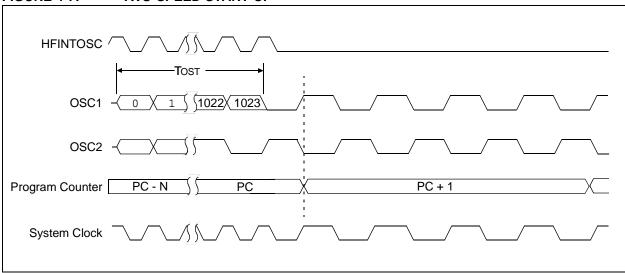

#### 4.7.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- Instructions begin execution by the internal oscillator at the frequency set in the IRCF<2:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

### 4.7.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCCON register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word Register 1 (CONFIG1), or the internal oscillator.

### FIGURE 4-7: TWO-SPEED START-UP

# 9.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- · Port configuration

- · Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- Interrupt control

- Results formatting

#### 9.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. See the corresponding Port section for more information.

| Note:                                    | Analog voltages on any pin that is defined |  |  |

|------------------------------------------|--------------------------------------------|--|--|

| as a digital input may cause the input t |                                            |  |  |

|                                          | fer to conduct excess current.             |  |  |

#### 9.1.2 CHANNEL SELECTION

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 9.2 "ADC Operation"** for more information.

### 9.1.3 ADC VOLTAGE REFERENCE

The VCFG bits of the ADCON1 register provide independent control of the positive and negative voltage references. The positive voltage reference can be either VDD or an external voltage source. Likewise, the negative voltage reference can be either VSS or an external voltage source.

#### 9.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON0 register. There are four possible clock options:

- Fosc/2

- Fosc/8

- Fosc/32

- FRC (dedicated internal oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11 TAD periods as shown in Figure 9-2.

For correct conversion, the appropriate TAD specification must be met. See A/D conversion requirements in **Section 17.0 "Electrical Specifications"** for more information. Table 9-1 gives examples of appropriate ADC clock selections.

**Note:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

#### **REGISTER 9-3:** ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

| R/W-x    | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|----------|--------|--------|--------|--------|--------|--------|--------|

| ADRES9   | ADRES8 | ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 |

| bit 7    |        |        |        |        |        |        | bit 0  |

|          |        |        |        |        |        |        |        |

| l egend: |        |        |        |        |        |        |        |

| Legena.           |                                                     |                      |                    |

|-------------------|-----------------------------------------------------|----------------------|--------------------|

| R = Readable bit  | V = Writable bit U = Unimplemented bit, read as '0' |                      |                    |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |

bit 7-0 ADRES<9:2>: ADC Result Register bits

Upper eight bits of 10-bit conversion result

'1' = Bit is set

#### **REGISTER 9-4:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x                                                                | R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|----------------------------------------------------------------------|--------|-------|-------|-------|-------|-------|-------|

| ADRES1                                                               | ADRES0 | —     | —     | —     | —     | —     | —     |

| bit 7                                                                |        |       |       |       |       |       | bit 0 |

|                                                                      |        |       |       |       |       |       |       |

| Legend:                                                              |        |       |       |       |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |        |       |       |       |       |       |       |

'0' = Bit is cleared

| bit 7-6 | ADRES<1:0>: ADC Result Register bits       |

|---------|--------------------------------------------|

|         | Lower two bits of 10-bit conversion result |

| bit 5-0 | Reserved: Do not use.                      |

#### REGISTER 9-5: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

| R/W-x  | R/W-x  |

|-------|-------|-------|-------|-------|-------|--------|--------|

| —     | —     | —     | —     | —     | —     | ADRES9 | ADRES8 |

| bit 7 |       |       |       |       |       |        | bit 0  |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | s 'O'              |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

bit 7-2 Reserved: Do not use.

-n = Value at POR

bit 1-0 ADRES<9:8>: ADC Result Register bits Upper two bits of 10-bit conversion result

### REGISTER 9-6: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 | ADRES1 | ADRES0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | s 'O'              |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

bit 7-0 ADRES<7:0>: ADC Result Register bits Lower eight bits of 10-bit conversion result x = Bit is unknown

#### 10.1.2 READING THE DATA EEPROM MEMORY

To read a data memory location, the user must write the address to the EEADR register, clear the EEPGD control bit of the EECON1 register, and then set control bit RD. The data is available at the very next cycle, in the EEDAT register; therefore, it can be read in the next instruction. EEDAT will hold this value until another read or until it is written to by the user (during a write operation).

| EXAMPLE 10-1:   | DATA EEPROM READ |

|-----------------|------------------|

| EXAIVIPLE IV-I. |                  |

| BANKSEL | EEADR         | i                     |

|---------|---------------|-----------------------|

| MOVLW   | DATA_EE_ADDR  | ;                     |

| MOVWF   | EEADR         | ;Data Memory          |

|         |               | ;Address to read      |

| BANKSEL | EECON1        | ;                     |

| BCF     | EECON1, EEPGD | ;Point to DATA memory |

| BSF     | EECON1, RD    | ;EE Read              |

| BANKSEL | EEDAT         | ;                     |

| MOVF    | EEDAT, W      | ;W = EEDAT            |

| BCF     | STATUS, RP1   | ;Bank 0               |

|         |               |                       |

# 10.1.3 WRITING TO THE DATA EEPROM MEMORY

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDAT register. Then the user must follow a specific sequence to initiate the write for each byte.

The write will not initiate if the above sequence is not followed exactly (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. Interrupts should be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

|    |          | BANKSEL<br>MOVLW | EEADR<br>DATA_EE_ADDR | ;<br>;                                       |  |  |  |

|----|----------|------------------|-----------------------|----------------------------------------------|--|--|--|

|    |          | MOVWF            | EEADR                 | ;Data Memory Address to write                |  |  |  |

|    |          | MOVLW            | DATA_EE_DATA          | ;                                            |  |  |  |

|    |          | MOVWF            | EEDAT                 | ;Data Memory Value to write                  |  |  |  |

|    |          | BANKSEL          |                       | ;                                            |  |  |  |

|    |          | BCF              | EECON1, EEPGD         | -                                            |  |  |  |

|    |          | BSF              | EECON1, WREN          | ;Enable writes                               |  |  |  |

|    |          | BCF              | INTCON, GIE           | ;Disable INTs.                               |  |  |  |

|    |          | BTFSC            | INTCON, GIE           | ;SEE AN576                                   |  |  |  |

|    |          | GOTO             | \$-2                  |                                              |  |  |  |

| ΙΓ |          | MOVLW            | 55h                   | ;                                            |  |  |  |

| 7  | Sequence | MOVWF            | EECON2                | ;Write 55h                                   |  |  |  |

|    | neu      | MOVLW            | AAh                   | ;                                            |  |  |  |

|    | Sed Re   | MOVWF            | EECON2                | ;Write AAh                                   |  |  |  |

|    | - 0)     | BSF              | EECON1, WR            | ;Set WR bit to begin write                   |  |  |  |

|    |          | BSF              | INTCON, GIE           | ;Enable INTs.                                |  |  |  |

|    |          | SLEEP            |                       | ;Wait for interrupt to signal write complete |  |  |  |

|    |          | BCF              | EECON1, WREN          | ;Disable writes                              |  |  |  |

|    |          | BCF              | STATUS, RPO           | ;Bank 0                                      |  |  |  |

|    |          | BCF              | STATUS, RP1           |                                              |  |  |  |

|    |          |                  |                       |                                              |  |  |  |

#### EXAMPLE 10-2: DATA EEPROM WRITE

### 11.6.7.1 Steering Synchronization

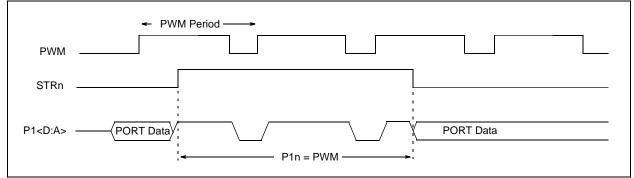

The STRSYNC bit of the PSTRCON register gives the user two selections of when the steering event will happen. When the STRSYNC bit is '0', the steering event will happen at the end of the instruction that writes to the PSTRCON register. In this case, the output signal at the P1<D:A> pins may be an incomplete PWM waveform. This operation is useful when the user firmware needs to immediately remove a PWM signal from the pin.

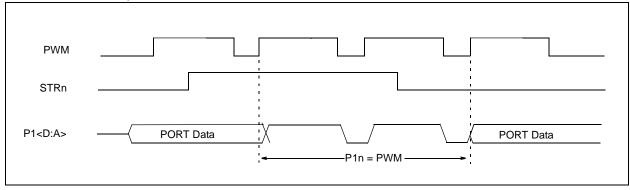

When the STRSYNC bit is '1', the effective steering update will happen at the beginning of the next PWM period. In this case, steering on/off the PWM output will always produce a complete PWM waveform. Figures 11-20 and 11-21 illustrate the timing diagrams of the PWM steering depending on the STRSYNC setting.

### FIGURE 11-20: EXAMPLE OF STEERING EVENT AT END OF INSTRUCTION (STRSYNC = 0)

#### FIGURE 11-21: EXAMPLE OF STEERING EVENT AT BEGINNING OF INSTRUCTION (STRSYNC = 1)

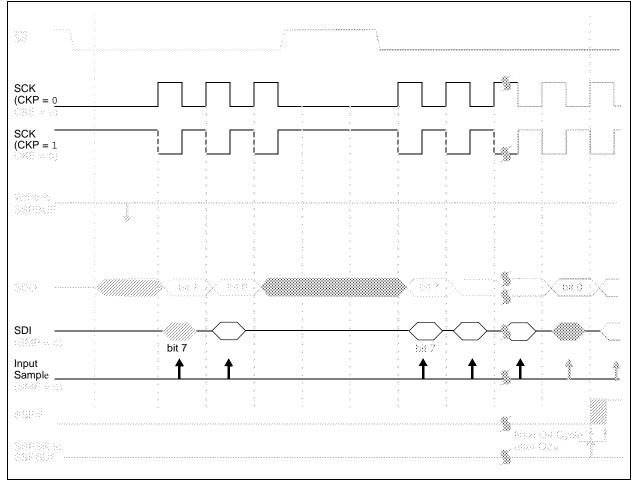

### 13.3.4 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit of the PIR1 register is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times, as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from Sleep.

#### 13.3.5 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = 04h). The pin must not be driven low for the  $\overline{SS}$  pin to function as an input. The Data Latch must be high. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high,

the SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. External pull-up/pull-down resistors may be desirable, depending on the application.

| <b>Note 1:</b> When the SPI is in Slave mode with $\overline{SS}$ |

|-------------------------------------------------------------------|

| pin control enabled (SSPCON<3:0> =                                |

| 0100), the SPI module will reset if the $\overline{SS}$           |

| pin is set to VDD.                                                |

2: If the SPI is used in Slave mode with CKE set (SSPSTAT register), then the SS pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level, or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver, the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function), since it cannot create a bus conflict.

### FIGURE 13-3: SLAVE SYNCHRONIZATION WAVEFORM

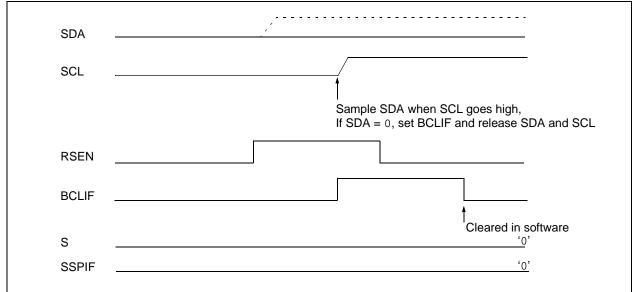

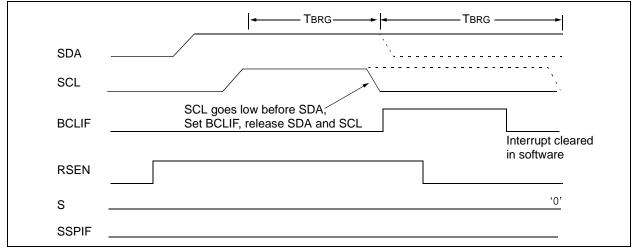

# 13.4.16.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user de-asserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then de-asserted, and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e, another master is attempting to transmit a data '0', see Figure 13-24). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from highto-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (Figure 13-25).

If at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

FIGURE 13-24: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

#### FIGURE 13-25: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

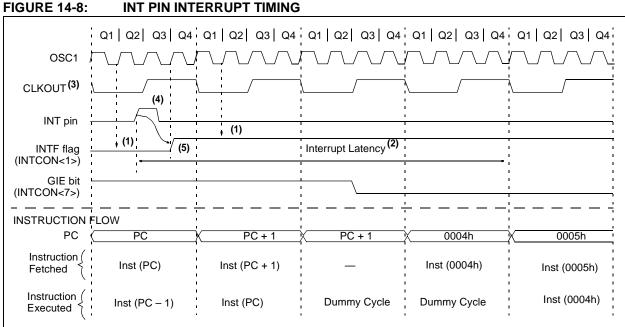

Note 1: INTF flag is sampled here (every Q1).

- **2:** Asynchronous interrupt latency = 3-4 TCY. Synchronous latency = 3 TCY, where TCY = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: CLKOUT is available only in INTOSC and RC Oscillator modes.

- 4: For minimum width of INT pulse, refer to AC specifications in Section 17.0 "Electrical Specifications".

- 5: INTF is enabled to be set any time during the Q4-Q1 cycles.

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1  | Bit 0  | Register on<br>Page |

|--------|-------|-------|-------|-------|-------|---------|--------|--------|---------------------|

| INTCON | GIE   | PEIE  | T0IE  | INTE  | RBIE  | T0IF    | INTF   | RBIF   | 32                  |

| PIE1   | —     | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE  | TMR2IE | TMR1IE | 33                  |

| PIE2   | OSFIE | C2IE  | C1IE  | EEIE  | BCLIE | ULPWUIE | —      | CCP2IE | 34                  |

| PIR1   | —     | ADIF  | RCIF  | TXIF  | SSPIF | CCP1IF  | TMR2IF | TMR1IF | 35                  |

| PIR2   | OSFIF | C2IF  | C1IF  | EEIF  | BCLIF | ULPWUIF |        | CCP2IF | 36                  |

TABLE 14-6:

SUMMARY OF INTERRUPT REGISTERS

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by the interrupt module.

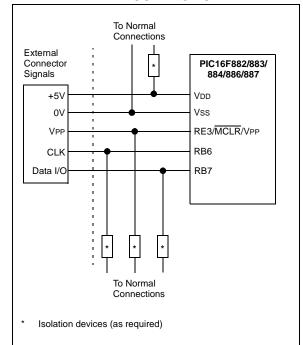

#### FIGURE 14-11:

TYPICAL IN-CIRCUIT SERIAL PROGRAMMING™ CONNECTION

# 14.10 Low-Voltage (Single-Supply) ICSP Programming

The LVP bit of the Configuration Word enables low-voltage ICSP programming. This mode allows the microcontroller to be programmed via ICSP using a VDD source in the operating voltage range. This only means that VPP does not have to be brought to VIHH but can instead be left at the normal operating voltage. In this mode, the RB3/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. During programming, VDD is applied to the MCLR pin. To enter Programming mode, VDD must be applied to the RB3/PGM provided the LVP bit is set. The LVP bit defaults to on ('1') from the factory.

- Note 1: The High-Voltage Programming mode is always available, regardless of the state of the LVP bit, by applying V<sub>IHH</sub> to the MCLR pin.

- 2: While in Low-Voltage ICSP mode, the RB3 pin can no longer be used as a general purpose I/O pin.

- 3: When using Low-Voltage ICSP Programming (LVP) and the pull-ups on PORTB are enabled, bit 3 in the TRISB register must be cleared to disable the pull-up on RB3 and ensure the proper operation of the device.

- 4: RB3 should not be allowed to float if LVP is enabled. An external pull-down device should be used to default the device to normal operating mode. If RB3 floats high, the PIC16F882/883/884/886/887 devices will enter Programming mode.

- LVP mode is enabled by default on all devices shipped from Microchip. It can be disabled by clearing the LVP bit in the CONFIG register.

If Low-Voltage Programming mode is not used, the LVP bit can be programmed to a '0' and RB3/PGM becomes a digital I/O pin. However, the LVP bit may only be programmed when programming is entered with VIHH on MCLR. The LVP bit can only be charged when using high voltage on MCLR.

It should be noted, that once the LVP bit is programmed to '0', only the High-Voltage Programming mode is available and only High-Voltage Programming mode can be used to program the device.

When using low-voltage ICSP, the part must be supplied at 4.5V to 5.5V if a bulk erase will be executed. This includes reprogramming of the code-protect bits from an on state to an off state. For all other cases of low-voltage ICSP, the part may be programmed at the normal operating voltage. This means calibration values, unique user IDs or user code can be reprogrammed or added.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                          |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                               |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                     |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', then a NOP is<br>executed instead, making it a<br>2-cycle instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                       |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                    |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                       |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                            |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                       |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The 11-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>2-cycle instruction. |  |  |  |  |

| INCF             | Increment f                                                                                                                                                                |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] INCF f,d                                                                                                                                                           |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                |  |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                        |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                          |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |  |  |  |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a 2-cycle<br>instruction. |  |  |  |  |  |

| IORLW            | Inclusive OR literal with W                                                                                  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                     |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                          |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                 |  |  |  |  |  |

| Status Affected: | Z                                                                                                            |  |  |  |  |  |

| Description:     | The contents of the W register are OR'ed with the 8-bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                    |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |  |

| MOVF             | Move f                                                                                                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] MOVF f,d                                                                                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                          |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                                                                                                                                          |

| Description:     | The contents of register 'f' is<br>moved to a destination dependent<br>upon the status of 'd'. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register 'f'<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |

| Words:           | 1                                                                                                                                                                                                                                                                                          |

| Cycles:          | 1                                                                                                                                                                                                                                                                                          |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                                |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                                 |

| MOVWF            | Move W to f                                |

|------------------|--------------------------------------------|

| Syntax:          | [ label ] MOVWF f                          |

| Operands:        | $0 \leq f \leq 127$                        |

| Operation:       | $(W) \rightarrow (f)$                      |

| Status Affected: | None                                       |

| Description:     | Move data from W register to register 'f'. |

| Words:           | 1                                          |

| Cycles:          | 1                                          |

| Example:         | MOVW OPTION<br>F                           |

|                  | Before Instruction                         |

|                  | OPTION = 0xFF                              |

|                  | W = 0x4F                                   |

|                  | After Instruction                          |

|                  | OPTION = 0x4F                              |

|                  | W = 0x4F                                   |

|                  |                                            |

| MOVLW            | Move literal to W                                                                         |

|------------------|-------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                  |

| Operands:        | $0 \leq k \leq 255$                                                                       |

| Operation:       | $k \rightarrow (W)$                                                                       |

| Status Affected: | None                                                                                      |

| Description:     | The 8-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |

| Words:           | 1                                                                                         |

| Cycles:          | 1                                                                                         |

| Example:         | MOVLW 0x5A                                                                                |

|                  | After Instruction<br>W = 0x5A                                                             |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

# 16.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 16.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 16.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 16.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 16.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

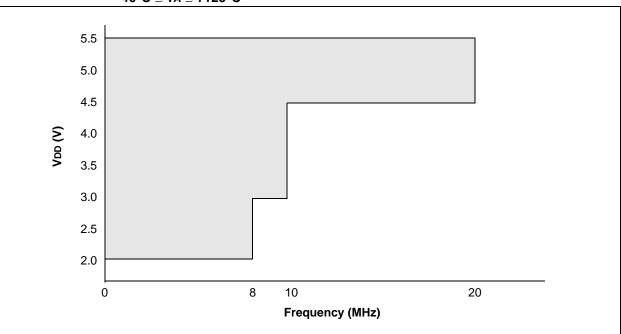

FIGURE 17-1: PIC16F882/883/884/886/887 VOLTAGE-FREQUENCY GRAPH, -40°C  $\leq$  TA  $\leq$  +125°C

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

### 17.1 DC Characteristics: PIC16F882/883/884/886/887-I (Industrial) PIC16F882/883/884/886/887-E (Extended)

| DC CHARACTERISTICS |      |                                                                  | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |     |     | $0^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                                        |

|--------------------|------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------------------------------------------------|--------------------------------------------------------|

| Param<br>No.       | Sym. | Characteristic                                                   | Min. Typ† Max. Units Conditions                                                                                                                                                                                                                                 |     |     |                                                     |                                                        |

|                    | Vdd  | Supply Voltage                                                   | 2.0                                                                                                                                                                                                                                                             | —   | 5.5 | V                                                   | Fosc < = 8 MHz: HFINTOSC, EC                           |

| D001               |      |                                                                  | 2.0                                                                                                                                                                                                                                                             | —   | 5.5 | V                                                   | Fosc < = 4 MHz                                         |

| D001C              |      |                                                                  | 3.0                                                                                                                                                                                                                                                             | —   | 5.5 | V                                                   | Fosc < = 10 MHz                                        |

| D001D              |      |                                                                  | 4.5                                                                                                                                                                                                                                                             | —   | 5.5 | V                                                   | Fosc < = 20 MHz                                        |

| D002*              | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | 1.5                                                                                                                                                                                                                                                             | —   | —   | V                                                   | Device in Sleep mode                                   |

| D003               | VPOR | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | —                                                                                                                                                                                                                                                               | Vss | —   | V                                                   | See Section 14.2.1 "Power-on Reset (POR)" for details. |

| D004*              | Svdd | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05                                                                                                                                                                                                                                                            |     | _   | V/ms                                                | See Section 14.2.1 "Power-on Reset (POR)" for details. |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

# TABLE 17-18:ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES (VDD $\geq$ 3.0V,<br/>VREF $\geq$ 2.5V)

| ADC Clock Period (TAD) |           | Device Frequency (Fosc) |               |               |               |

|------------------------|-----------|-------------------------|---------------|---------------|---------------|

| ADC Clock Source       | ADCS<2:0> | 20 MHz                  | 8 MHz         | 4 MHz         | 1 MHz         |

| Fosc/2                 | 000       | 100 ns                  | 250 ns        | 500 ns        | 2.0 μs        |

| Fosc/8                 | 001       | 400 ns                  | 1.0 μs        | 2.0 μs        | 8.0 μs        |

| Fosc/32                | 010       | 1.6 μs                  | 4.0 μs        | 8.0 μs        | 32.0 μs       |

| Frc                    | x11       | <b>2-6</b> μs           | <b>2-6</b> μs | <b>2-6</b> μs | <b>2-6</b> μs |

Legend: Shaded cells should not be used for conversions at temperatures above +125°C.

Note 1: TAD must be between 1.6  $\mu$ s and 6.0  $\mu$ s.

# 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |          |          |      |

|-------------------------|-------------|----------|----------|------|

| Dimension               | Limits      | MIN      | NOM      | MAX  |

| Number of Pins          | N           |          | 44       |      |

| Pitch                   | е           |          | 0.65 BSC |      |

| Overall Height          | A           | 0.80     | 0.90     | 1.00 |

| Standoff                | A1          | 0.00     | 0.02     | 0.05 |

| Terminal Thickness      | A3          | 0.20 REF |          |      |

| Overall Width           | E           | 8.00 BSC |          |      |

| Exposed Pad Width       | E2          | 6.25     | 6.45     | 6.60 |

| Overall Length          | D           | 8.00 BSC |          |      |

| Exposed Pad Length      | D2          | 6.25     | 6.45     | 6.60 |

| Terminal Width          | b           | 0.20     | 0.30     | 0.35 |

| Terminal Length         | L           | 0.30     | 0.40     | 0.50 |

| Terminal-to-Exposed-Pad | K           | 0.20     | -        | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension. usually without tolerance. for information purposes only.

Microchip Technology Drawing C04-103C Sheet 2 of 2