#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFL

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | SH2A-FPU                                                                         |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SCI, SPI, USB                                |

| Peripherals                | DMA, PWM, WDT                                                                    |

| Number of I/O              | 112                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x12b                                                                        |

| Oscillator Type            | External                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 176-LQFP                                                                         |

| Supplier Device Package    | 176-LFQFP (20x20)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f72145bdfa-v1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

When exception handling starts, the CPU operates as follows:

## (1) Exception Handling Triggered by Reset

The initial values of the program counter (PC) and stack pointer (SP) are fetched from the exception handling vector table (PC and SP are respectively the H'00000000 and H'00000004 addresses for power-on resets and the H'00000008 and H'0000000C addresses for manual resets). See section 5.1.3, Exception Handling Vector Table, for more information. The vector base register (VBR) is then initialized to H'00000000, the interrupt mask level bits (I3 to I0) of the status register (SR) are initialized to H'F (B'1111), and the BO and CS bits are initialized. The BN bit in IBNR of the interrupt controller (INTC) is also initialized to 0. The program begins running from the PC address fetched from the exception handling vector table.

# (2) Exception Handling Triggered by Address Errors, Register Bank Errors, Interrupts, and Instructions

SR and PC are saved to the stack indicated by R15. In the case of interrupt exception handling other than NMI or UBC with usage of the register banks enabled, general registers R0 to R14, control register GBR, system registers MACH, MACL, and PR, and the vector table address offset of the interrupt exception handling to be executed are saved to the register banks. In the case of exception handling due to an address error, register bank error, NMI interrupt, UBC interrupt, or instruction, saving to a register bank is not performed. When saving is performed to all register banks, automatic saving to the stack is performed instead of register bank saving. In this case, an interrupt controller setting must have been made so that register bank overflow exceptions are not accepted (the BOVE bit in IBNR of the INTC is 0). If a setting to accept register bank overflow exception will be generated. In the case of interrupt exception handling, the interrupt priority level is written to the I3 to I0 bits in SR. In the case of exception handling due to an address error or instruction, the I3 to I0 bits are not affected. The start address is then fetched from the exception handling vector table and the program begins running from that address.

| Object to be<br>Accessed |                                                 | On-Chip<br>RAM* <sup>1</sup>               | Flash Memory<br>(ROM)               | On-Chip I/O             | Registers* <sup>4</sup> | External Device <sup>∗⁵</sup> |                    |                   |                    |

|--------------------------|-------------------------------------------------|--------------------------------------------|-------------------------------------|-------------------------|-------------------------|-------------------------------|--------------------|-------------------|--------------------|

| Bus wid                  | lth                                             | 32 bits                                    | 32 bits                             | 8 bits* <sup>4</sup>    | 16 bits                 | 32 bits                       | 8 bits             | 16 bits           | 32 bits            |

| Access                   | cycles                                          | 1Βφ to<br>4Βφ* <sup>1</sup> *²             | $3B\phi$ to $4I\phi + 3B\phi^{*^2}$ | 2Pø                     | 2Pø                     | 2Pø                           | 2Bø                | 2Вф               | 2Bø                |

| Exe-<br>cution           | Vector read<br>S <sub>i</sub>                   | 1Βφ to<br>4Βφ* <sup>1</sup> * <sup>2</sup> | $3B\phi$ to $4I\phi + 3B\phi^{*^2}$ | _                       | _                       | _                             | 9Bø                | 5Bø               | ЗВф                |

| status                   | Transfer<br>information<br>read S <sub>J</sub>  | 1Βφ to<br>4Βφ* <sup>1</sup>                |                                     | —                       | —                       | —                             | 9Вф                | 5Bø               | 3Вф                |

|                          | Transfer<br>information<br>write S <sub>k</sub> | 1Βφ to<br>3Βφ*¹                            | _                                   | _                       | _                       | _                             | 2B\$*              | 2B∳* <sup>6</sup> | 2B\$*6             |

|                          | Byte data<br>read S <sub>L</sub>                | 1Bǫ to<br>4Bǫ*¹                            | _                                   | $1B\phi + 2P\phi^{*^3}$ | $1B\phi + 2P\phi^{*^3}$ | _                             | ЗВф                | ЗВф               | 3Вф                |

|                          | Word data<br>read S <sub>L</sub>                | 1Bǫ to<br>4Bǫ*¹                            | _                                   | $1B\phi + 2P\phi^{*^3}$ | $1B\phi + 2P\phi^{*^3}$ | _                             | 5Bø                | ЗВф               | 3Вф                |

|                          | Longword data read $S_{L}$                      | 1Βφ to<br>4Βφ* <sup>1</sup>                | _                                   | $1B\phi + 4P\phi^{*^3}$ | $1B\phi + 2P\phi^{*^3}$ | $1B\phi + 4P\phi^{*^3}$       | 9Вф                | 5Bø               | ЗВф                |

|                          | Byte data<br>write S <sub>м</sub>               | 1B∳ to<br>3B∳*¹                            | _                                   | $1B\phi + 2P\phi^{*^3}$ | $1B\phi + 2P\phi^{*^3}$ | _                             | 2B\$*6             | 2B\$*6            | 2B\$*6             |

|                          | Word data<br>write S <sub>м</sub>               | 1Βφ to<br>3Βφ*¹                            | _                                   | $1B\phi + 2P\phi^{*^3}$ | $1B\phi + 2P\phi^{*^3}$ | _                             | 2B\$*6             | 2B\$*6            | 2B\$*6             |

|                          | Longword data write $S_{_{\rm M}}$              | 1B∳ to<br>3B∲*¹                            | _                                   | $1B\phi + 4P\phi^{*^3}$ | $1B\phi + 2P\phi^{*^3}$ | $1B\phi + 4P\phi^{*^3}$       | 2B\$* <sup>6</sup> | 2B\$*6            | 2B\$* <sup>6</sup> |

|                          | Internal operation $S_{N}$                      |                                            |                                     |                         | 1                       |                               |                    |                   |                    |

## Table 8.10 Number of Cycles Required for Each Execution State

Notes: 1. Values for on-chip RAM. Number of cycles varies depending on the ratio of  $l\phi:B\phi$ .

|                               | Read     | Write             |

|-------------------------------|----------|-------------------|

| $I\varphi{:}B\varphi=1{:}1$   | 3Bø, 4Bø | 2Bø, 3Bø          |

| $I\phi:B\phi = 1:1/2$         | 2B¢, 3B¢ | 2Bø               |

| $I\varphi:B\varphi = 1:1/4$   | 2Bø      | 1B <b>φ</b> , 2Bφ |

| $I\varphi{:}B\varphi=1{:}1/8$ | 1Вф      | 1Bø               |

- 6. SRAM interface with byte selection

- Can connect directly to a SRAM with byte selection.

- 7. Burst ROM interface (clock synchronous)

- Can connect directly to a ROM of the clock-synchronous type.

- 8. Bus arbitration

- Shares all of the resources with other CPU and outputs the bus enable after receiving the bus request from external devices.

- 9. Refresh function

- Supports the auto-refresh and self-refresh functions.

- Specifies the refresh interval using the refresh counter and clock selection.

- Can execute concentrated refresh by specifying the refresh counts (1, 2, 4, 6, or 8).

- 10. Usage as interval timer for refresh counter

- Generates an interrupt request at compare match.

Figure 9.1 shows a block diagram of the BSC.

| No. | Condition                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Range   | Note                                                                                                                                                                                                                                                                      |

|-----|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (1) | DMAIW[2:0] in<br>CMNCR             | These bits specify the number of<br>idle cycles for DMA single address<br>transfer. This condition is effective<br>only for single address transfer and<br>generates idle cycles after the<br>access is completed.                                                                                                                                                                                                                                                                                                                                                                   | 0 to 12 | When 0 is specified for the<br>number of idle cycles, the<br>DACK signal may be asserted<br>continuously. This causes a<br>discrepancy between the<br>number of cycles detected by<br>the device with DACK and the<br>DMAC transfer count,<br>resulting in a malfunction. |

| (2) | IW***[2:0] in<br>CSnBCR            | These bits specify the number of<br>idle cycles for access other than<br>single address transfer. The<br>number of idle cycles can be<br>specified independently for each<br>combination of the previous and<br>next cycles. For example, in the<br>case where reading CS1 space<br>followed by reading other CS<br>space, the bits IWRRD[2:0] in<br>CS1BCR should be set to B'100 to<br>specify six or more idle cycles. This<br>condition is effective only for access<br>cycles other than single address<br>transfer and generates idle cycles<br>after the access is completed. | 0 to 12 | Do not set 0 for the number of<br>idle cycles between memory<br>types which are not allowed<br>to be accessed successively.                                                                                                                                               |

| (3) | SDRAM-related<br>bits in<br>CSnWCR | These bits specify precharge<br>completion and startup wait cycles<br>and idle cycles between commands<br>for SDRAM access. This condition<br>is effective only for SDRAM access<br>and generates idle cycles after the<br>access is completed                                                                                                                                                                                                                                                                                                                                       | 0 to 3  | Specify these bits in<br>accordance with the<br>specification of the target<br>SDRAM.                                                                                                                                                                                     |

| (4) | WM in<br>CSnWCR                    | This bit enables or disables external $\overline{\text{WAIT}}$ pin input for the memory types other than SDRAM. When this bit is cleared to 0 (external $\overline{\text{WAIT}}$ enabled), one idle cycle is inserted to check the external $\overline{\text{WAIT}}$ pin input after the access is completed. When this bit is set to 1 (disabled), no idle cycle is generated.                                                                                                                                                                                                      | 0 or 1  |                                                                                                                                                                                                                                                                           |

## Table 9.21 Conditions for Determining Number of Idle Cycles

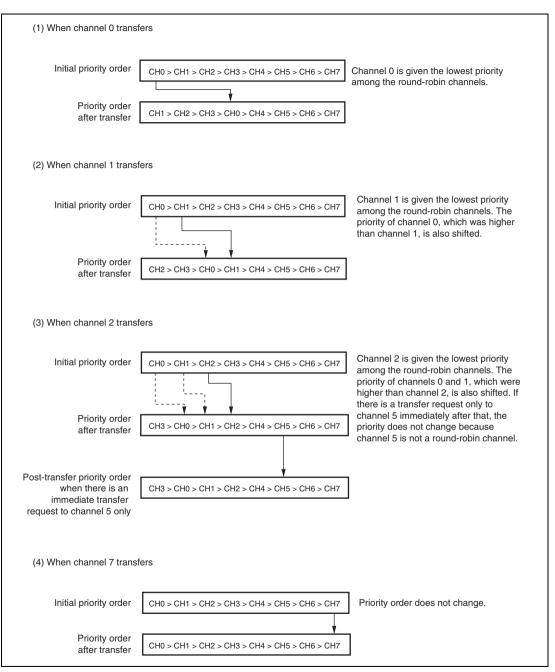

## Figure 10.3 Round-Robin Mode

| Bit 3<br>MD3 | Bit 2<br>MD2 | Bit 1<br>MD1 | Bit 0<br>MD0 | Description                                                     |

|--------------|--------------|--------------|--------------|-----------------------------------------------------------------|

| 0            | 0            | 0            | 0            | Normal operation                                                |

|              |              |              | 1            | Setting prohibited                                              |

|              |              | 1            | 0            | PWM mode 1                                                      |

|              |              |              | 1            | PWM mode 2*1                                                    |

|              | 1            | 0            | 0            | Phase counting mode 1* <sup>2</sup>                             |

|              |              |              | 1            | Phase counting mode 2* <sup>2</sup>                             |

|              |              | 1            | 0            | Phase counting mode 3* <sup>2</sup>                             |

|              |              |              | 1            | Phase counting mode 4* <sup>2</sup>                             |

| 1            | 0            | 0            | 0            | Reset synchronous PWM mode* <sup>3</sup>                        |

|              |              |              | 1            | Setting prohibited                                              |

|              |              | 1            | Х            | Setting prohibited                                              |

|              | 1            | 0            | 0            | Setting prohibited                                              |

|              |              |              | 1            | Complementary PWM mode 1 (transmit at crest)*3                  |

|              |              | 1            | 0            | Complementary PWM mode 2 (transmit at trough)*3                 |

|              |              |              | 1            | Complementary PWM mode 2 (transmit at crest and trough)* $^{3}$ |

#### Table 11.11 Setting of Operation Mode by Bits MD0 to MD3

## [Legend]

X: Don't care

Notes: 1. PWM mode 2 cannot be set for channels 3 and 4.

- 2. Phase counting mode cannot be set for channels 0, 3, and 4.

- 3. Reset synchronous PWM mode, complementary PWM mode can only be set for channel 3. When channel 3 is set to reset synchronous PWM mode or complementary PWM mode, the channel 4 settings become ineffective and automatically conform to the channel 3 settings. However, do not set channel 4 to reset synchronous PWM mode or complementary PWM mode. Reset synchronous PWM mode and complementary PWM mode cannot be set for channels 0, 1, and 2.

|     |          | Initial |        |                                                                   |

|-----|----------|---------|--------|-------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W    | Description                                                       |

| 1   | SCH3S    | 0       | R/(W)* | Synchronous Start                                                 |

|     |          |         |        | Controls synchronous start of TCNT_3S in the MTU2S.               |

|     |          |         |        | 0: Does not specify synchronous start for TCNT_3S in the MTU2S    |

|     |          |         |        | 1: Specifies synchronous start for TCNT_3S in the<br>MTU2S        |

|     |          |         |        | [Clearing condition]                                              |

|     |          |         |        | • When 1 is set to the CST3 bit of TSTRS in MTU2S                 |

|     |          |         |        | while SCH3S = 1                                                   |

| 0   | SCH4S    | 0       | R/(W)* | Synchronous Start                                                 |

|     |          |         |        | Controls synchronous start of TCNT_4S in the MTU2S.               |

|     |          |         |        | 0: Does not specify synchronous start for TCNT_4S in the MTU2S    |

|     |          |         |        | 1: Specifies synchronous start for TCNT_4S in the<br>MTU2S        |

|     |          |         |        | [Clearing condition]                                              |

|     |          |         |        | • When 1 is set to the CST4 bit of TSTRS in MTU2S while SCH4S = 1 |

Note: Only 1 can be written to set the register.

| Bit | Bit Name | Initial<br>Value | R/W   | Description                                                        |

|-----|----------|------------------|-------|--------------------------------------------------------------------|

|     |          |                  |       | · · · · · · · · · · · · · · · · · · ·                              |

| 0   | WRE      | 0                | R/(W) | Initial Output Suppression Enable                                  |

|     |          |                  |       | Selects the waveform output when synchronous                       |

|     |          |                  |       | counter clearing occurs in complementary PWM mode.                 |

|     |          |                  |       | The initial output is suppressed only when synchronous             |

|     |          |                  |       | clearing occurs within the Tb interval at the trough in            |

|     |          |                  |       | complementary PWM mode. When synchronous                           |

|     |          |                  |       | clearing occurs outside this interval, the initial value           |

|     |          |                  |       | specified in TOCR is output regardless of the WRE bit              |

|     |          |                  |       | setting. The initial value is also output when                     |

|     |          |                  |       | synchronous clearing occurs in the Tb interval at the              |

|     |          |                  |       | trough immediately after TCNT_3 and TCNT_4 start                   |

|     |          |                  |       | operation.                                                         |

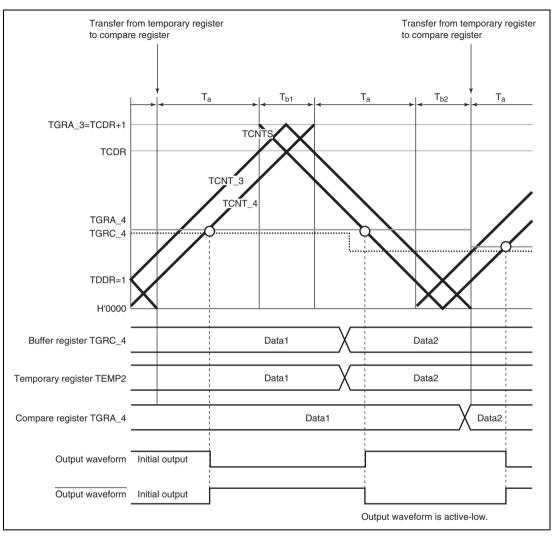

|     |          |                  |       | For the Tb interval at the trough in complementary                 |

|     |          |                  |       | PWM mode, see figure 11.40.                                        |

|     |          |                  |       | 0: Outputs the initial value specified in TOCR                     |

|     |          |                  |       | 1: Suppresses initial output                                       |

|     |          |                  |       | [Setting condition]                                                |

|     |          |                  |       | <ul> <li>When 1 is written to WRE after reading WRE = 0</li> </ul> |

Note: \* Do not set to 1 when complementary PWM mode is not selected.

## **11.3.33** Bus Master Interface

The timer counters (TCNT), general registers (TGR), timer subcounter (TCNTS), timer cycle buffer register (TCBR), timer dead time data register (TDDR), timer cycle data register (TCDR), timer A/D converter start request control register (TADCR), timer A/D converter start request cycle set registers (TADCOR), and timer A/D converter start request cycle set buffer registers (TADCOBR) are 16-bit registers. A 16-bit data bus to the bus master enables 16-bit read/writes. 8-bit read/write is not possible. Always access in 16-bit units.

All registers other than the above registers are 8-bit registers. These are connected to the CPU by a 16-bit data bus, so 16-bit read/writes and 8-bit read/writes are both possible.

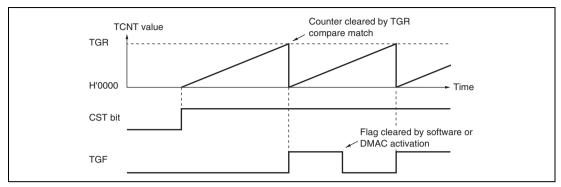

Figure 11.6 illustrates periodic counter operation.

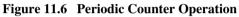

## (2) Waveform Output by Compare Match

The MTU2 can perform 0, 1, or toggle output from the corresponding output pin using compare match.

## (a) Example of Setting Procedure for Waveform Output by Compare Match

Figure 11.7 shows an example of the setting procedure for waveform output by compare match.

Figure 11.7 Example of Setting Procedure for Waveform Output by Compare Match

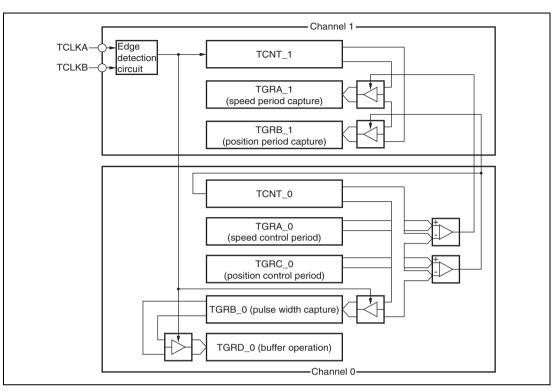

Figure 11.34 Phase Counting Mode Application Example

Figure 11.41 Example of Operation without Dead Time

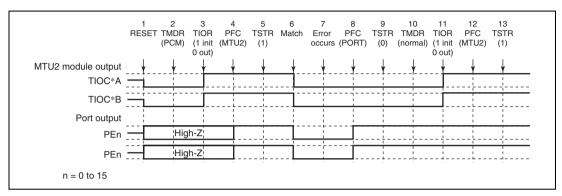

## (17) Operation when Error Occurs during Phase Counting Mode Operation, and Operation is Restarted in Normal Mode

Figure 11.155 shows an explanatory diagram of the case where an error occurs in phase counting mode and operation is restarted in normal mode after re-setting.

## Figure 11.155 Error Occurrence in Phase Counting Mode, Recovery in Normal Mode

- 1. After a reset, MTU2 output is low and ports are in the high-impedance state.

- 2. Set phase counting mode.

- 3. Initialize the pins with TIOR. (The example shows initial high output, with low output on compare-match occurrence.)

- 4. Set MTU2 output with the PFC.

- 5. The count operation is started by TSTR.

- 6. Output goes low on compare-match occurrence.

- 7. An error occurs.

- 8. Set port output with the PFC and output the inverse of the active level.

- 9. The count operation is stopped by TSTR.

- 10. Set in normal mode.

- 11. Initialize the pins with TIOR.

- 12. Set MTU2 output with the PFC.

- 13. Operation is restarted by TSTR.

## 17.3.6 Serial Control Register (SCSCR)

SCSCR operates the SCIF transmitter/receiver, enables/disables interrupt requests, and selects the transmit/receive clock source. The CPU can always read and write to SCSCR. SCSCR is initialized to H'0000 by a power-on reset.

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7   | 6   | 5   | 4   | 3    | 2 | 1   | 0     |

|----------------|----|----|----|----|----|----|---|---|-----|-----|-----|-----|------|---|-----|-------|

|                | -  | -  | -  | -  | -  | -  | - | - | TIE | RIE | TE  | RE  | REIE | - | CKE | [1:0] |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0   | 0   | 0   | 0   | 0    | 0 | 0   | 0     |

| R/W:           | R  | R  | R  | R  | R  | R  | R | R | R/W | R/W | R/W | R/W | R/W  | R | R/W | R/W   |

| Bit     | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|----------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 8 | _        | All 0            | R   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                                                                                                                                                                                                                                                                                                  |

| 7       | TIE      | 0                | R/W | Transmit Interrupt Enable                                                                                                                                                                                                                                                                                                                                                                                                             |

|         |          |                  |     | Enables or disables the transmit-FIFO-data-empty<br>interrupt (TXI) requested when the serial transmit data<br>is transferred from the transmit FIFO data register<br>(SCFTDR) to the transmit shift register (SCTSR), when<br>the quantity of data in the transmit FIFO register<br>becomes less than the specified number of<br>transmission triggers, and when the TDFE flag in the<br>serial status register (SCFSR) is set to 1. |

|         |          |                  |     | 0: Transmit-FIFO-data-empty interrupt request (TXI) is<br>disabled                                                                                                                                                                                                                                                                                                                                                                    |

|         |          |                  |     | 1: Transmit-FIFO-data-empty interrupt request (TXI) is<br>enabled*                                                                                                                                                                                                                                                                                                                                                                    |

|         |          |                  |     | Note: * The TXI interrupt request can be cleared by<br>writing a greater quantity of transmit data than<br>the specified transmission trigger number to<br>SCFTDR and by clearing TDFE to 0 after<br>reading 1 from TDFE, or can be cleared by<br>clearing TIE to 0.                                                                                                                                                                  |

## 17.4 Operation

#### 17.4.1 Overview

For serial communication, the SCIF has an asynchronous mode in which characters are synchronized individually, and a clocked synchronous mode in which communication is synchronized with clock pulses.

The SCIF has a 16-stage FIFO buffer for both transmission and receptions, reducing the overhead of the CPU, and enabling continuous high-speed communication.

The transmission format is selected in the serial mode register (SCSMR), as shown in table 17.14. The SCIF clock source is selected by the combination of the CKE1 and CKE0 bits in the serial control register (SCSCR), as shown in table 17.15.

## (1) Asynchronous Mode

- Data length is selectable: 7 or 8 bits

- Parity bit is selectable. So is the stop bit length (1 or 2 bits). The combination of the preceding selections constitutes the communication format and character length.

- In receiving, it is possible to detect framing errors, parity errors, receive FIFO data full, overrun errors, receive data ready, and breaks.

- The number of stored data bytes is indicated for both the transmit and receive FIFO registers.

- An internal or external clock can be selected as the SCIF clock source.

- When an internal clock is selected, the SCIF operates using the clock of on-chip baud rate generator.

- When an external clock is selected, the external clock input must have a frequency 16 times the bit rate. (The on-chip baud rate generator is not used.)

## (2) Clocked Synchronous Mode

- The transmission/reception format has a fixed 8-bit data length.

- In receiving, it is possible to detect overrun errors (ORER).

- An internal or external clock can be selected as the SCIF clock source.

- When an internal clock is selected, the SCIF operates using the clock of the on-chip baud rate generator, and outputs this clock to external devices as the synchronous clock.

- When an external clock is selected, the SCIF operates on the input synchronous clock not using the on-chip baud rate generator.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                         |

|--------|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5      | MST      | 0                | R/W | Master/Slave Select                                                                                                                                                                                                                                                                                                                                 |

| 4      | TRS      | 0                | R/W | Transmit/Receive Select                                                                                                                                                                                                                                                                                                                             |

|        |          |                  |     | In master mode with the I <sup>2</sup> C bus format, when<br>arbitration is lost, MST and TRS are both reset by<br>hardware, causing a transition to slave receive mode.<br>Modification of the TRS bit should be made between<br>transfer frames.                                                                                                  |

|        |          |                  |     | When seven bits after the start condition is issued in<br>slave receive mode match the slave address set to<br>SAR and the 8th bit is set to 1, TRS is automatically<br>set to 1. If an overrun error occurs in master receive<br>mode with the clocked synchronous serial format, MST<br>is cleared and the mode changes to slave receive<br>mode. |

|        |          |                  |     | Operating modes are described below according to MST and TRS combination. When clocked synchronous serial format is selected and MST = 1, clock is output.                                                                                                                                                                                          |

|        |          |                  |     | 00: Slave receive mode                                                                                                                                                                                                                                                                                                                              |

|        |          |                  |     | 01: Slave transmit mode                                                                                                                                                                                                                                                                                                                             |

|        |          |                  |     | 10: Master receive mode                                                                                                                                                                                                                                                                                                                             |

|        |          |                  |     | 11: Master transmit mode                                                                                                                                                                                                                                                                                                                            |

| 3 to 0 | CKS[3:0] | 0000             | R/W | Transfer Clock Select                                                                                                                                                                                                                                                                                                                               |

|        |          |                  |     | These bits should be set according to the necessary transfer rate (table 19.3) in master mode.                                                                                                                                                                                                                                                      |

## • Port A Control Register L3 (PACRL3)

| Bit:           | 15 | 14  | 13     | 12  | 11 | 10  | 9      | 8   | 7 | 6   | 5       | 4   | 3 | 2   | 1       | 0   |

|----------------|----|-----|--------|-----|----|-----|--------|-----|---|-----|---------|-----|---|-----|---------|-----|

|                |    | PA  | 11MD[2 | :0] | -  | PA  | 10MD[2 | :0] | - | P   | A9MD[2: | 0]  | - | P   | A8MD[2: | 0]  |

| Initial value: | 0  | 0   | 0      | 0   | 0  | 0   | 0      | 0   | 0 | 0   | 0       | 0   | 0 | 0   | 0       | 0   |

| R/W:           | R  | R/W | R/W    | R/W | R  | R/W | R/W    | R/W | R | R/W | R/W     | R/W | R | R/W | R/W     | R/W |

| Bit      | Bit Name    | Initial<br>Value | R/W | Description                                                            |

|----------|-------------|------------------|-----|------------------------------------------------------------------------|

| 15       |             | 0                | R   | Reserved                                                               |

|          |             |                  |     | This bit is always read as 0. The write value should always be 0.      |

| 14 to 12 | PA11MD[2:0] | 000*             | R/W | PA11 Mode                                                              |

|          |             |                  |     | Select the function of the<br>PA11/CS1/IRQ1/TIC5V/CRx0/RXD0/TX_EN pin. |

|          |             |                  |     | 000: PA11 I/O (port)                                                   |

|          |             |                  |     | 001: CS1 output (BSC)                                                  |

|          |             |                  |     | 010: Setting prohibited                                                |

|          |             |                  |     | 011: IRQ1 input (INTC)                                                 |

|          |             |                  |     | 100: TIC5V input (MTU2)                                                |

|          |             |                  |     | 101: CRx0 input (RCAN-ET)                                              |

|          |             |                  |     | 110: RXD0 input (SCI)                                                  |

|          |             |                  |     | 111: TX_EN input (Ether)                                               |

| 11       | _           | 0                | R   | Reserved                                                               |

|          |             |                  |     | This bit is always read as 0. The write value should always be 0.      |

| 10 to 8  | PA10MD[2:0] | 000*             | R/W | PA10 Mode                                                              |

|          |             |                  |     | Select the function of the PA10/CS2/IRQ2/TIC5W/CTx0/TXD0/MII_TXD0 pin. |

|          |             |                  |     | 000: PA10 I/O (port)                                                   |

|          |             |                  |     | 001: CS2 output (BSC)                                                  |

|          |             |                  |     | 010: Setting prohibited                                                |

|          |             |                  |     | 011: IRQ2 input (INTC)                                                 |

|          |             |                  |     | 100: TIC5W input (MTU2)                                                |

|          |             |                  |     | 101: CTx0 output (RCAN-ET)                                             |

|          |             |                  |     | 110: TXD0 output (SCI)                                                 |

|          |             |                  |     | 111: MII_TXD0 output (Ether)                                           |

## 25.3.18 Multicast Address Frame Receive Counter Register (MAFCR)

MAFCR is a 32-bit counter that indicates the number of received frames that specify a multicast address. When the value of this register reaches H'FFFFFFF, the counter stops incrementing. The counter value is cleared to 0 by writing any value to this register.

| Bit:                   | 31               | 30       | 29       | 28          | 27       | 26                            | 25             | 24       | 23       | 22       | 21       | 20       | 19       | 18       | 17       | 16       |

|------------------------|------------------|----------|----------|-------------|----------|-------------------------------|----------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

|                        |                  |          |          |             |          |                               |                | MAFC     | [31:16]  |          |          |          |          |          |          |          |

| Initial value:<br>R/W: | 0<br>R/W         | 0<br>R/W | 0<br>R/W | 0<br>R/W    | 0<br>R/W | 0<br>R/W                      | 0<br>R/W       | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W |

| Bit:                   | 15               | 14       | 13       | 12          | 11       | 10                            | 9              | 8        | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|                        |                  |          |          |             |          |                               |                | MAFC     | 2[15:0]  |          |          |          |          |          |          |          |

| Initial value:<br>R/W: | 0<br>R/W         | 0<br>R/W | 0<br>R/W | 0<br>R/W    | 0<br>R/W | 0<br>R/W                      | 0<br>R/W       | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W |

| Bit                    | Bit N            | lame     |          | tial<br>lue | R/W      | 1                             | Desci          | riptio   | n        |          |          |          |          |          |          |          |

| 31 to 0                | MAFC[31:0] All 0 |          |          | R/W         | /        | Multicast Address Frame Count |                |          |          |          |          |          |          |          |          |          |

|                        |                  |          |          |             |          |                               | These<br>frame |          |          | te the   | num      | ber of   | multi    | cast a   | addres   | ss       |

## 25.3.23 Random Number Generation Counter Upper Limit Register (RDMLR)

RDMLR is used to set the upper limit for the counter used in the random number generation block.

| Bit:                   | 31       | 30       | 29       | 28             | 27       | 26       | 25             | 24       | 23       | 22       | 21       | 20       | 19       | 18       | 17       | 16       |

|------------------------|----------|----------|----------|----------------|----------|----------|----------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

|                        | -        | -        | -        | -              | -        | -        | -              | -        | -        | -        | -        | -        |          | RMD[     | 19:16]   |          |

| Initial value:<br>R/W: | 0<br>R   | 0<br>R   | 0<br>R   | 0<br>R         | 0<br>R   | 0<br>R   | 0<br>R         | 0<br>R   | 0<br>R   | 0<br>R   | 0<br>R   | 0<br>R   | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W |

| Bit:                   | 15       | 14       | 13       | 12             | 11       | 10       | 9              | 8        | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|                        |          |          |          |                |          |          |                | RMD      | [15:0]   |          |          |          |          |          |          |          |

| Initial value:<br>R/W: | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W       | 0<br>R/W | 0<br>R/W | 0<br>R/W       | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W |

| Bit                    | Bit N    | lame     |          | Initia<br>Valu |          | k/W      | Desc           | riptio   | n        |          |          |          |          |          |          |          |

| 31 to 20               | _        |          |          | All 0          | F        | 1        | Rese           | ved      |          |          |          |          |          |          |          |          |

|                        |          |          |          |                |          |          | These<br>alway |          |          | ways     | read     | as 0.    | The w    | vrite v  | alue s   | should   |

| 19 to 0                | RMD      | 0[19:0]  | ]        | All 0          | F        | R/W      | Uppe<br>Gene   |          |          |          | er Use   | ed in F  | Rando    | om Nu    | Imber    |          |

|                        |          |          |          |                |          |          | H'000          | 00: U    | sed ir   | n norn   | nal op   | eratic   | n        |          |          |          |

|                        |          |          |          |                |          |          | H'000          | 01to I   | H'FFF    | FE: L    | Jpper    | limit f  | or the   | coun     | iter     |          |

Note: The setting of this register affects the operation of the random number generation block in the feLic. Pay attention when setting a value other than H'00000.

## • Programming/erasing unit

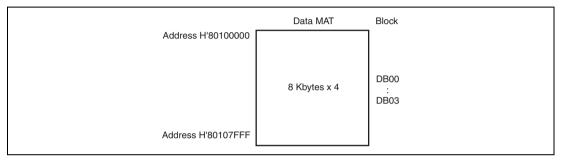

The data MAT is programmed in 8-byte or 128-byte units and erased in block units (8 Kbytes) in user mode, user program mode, and user boot mode. In boot mode, the data MAT is programmed in 256-Kbyte units and erased in block units (8 Kbytes). The product information MAT is read-only memory and cannot be programmed or erased.

Figure 28.3 shows the block configuration of the data MAT of this LSI. The data MAT is divided into four 8-Kbyte blocks (DB00 to DB03).

Figure 28.3 Block Configuration of Data MAT

• Blank check function

If data is read from erased FLD by the CPU, undefined values are read. Using blank check command of the FCU allows checking of whether the FLD is erased (in a blank state). Either an 8 Kbytes (1 erasure block) or 8 bytes of area can be checked by a single execution of the blank check command.

Blank checking proceeds for areas where erasure has been completed normally to confirm that the data have actually been erased. When erasure or programming in progress is stopped (e.g. by input of the reset signal or shutting down the power), blank checking cannot be used to check whether the data have actually been erased or written.

• Four types of on-board programming modes

- Boot mode

The data MAT can be programmed using the SCI. The bit rate for SCI communications between the host and the LSI can be automatically adjusted.

- User mode/user program mode

The data MAT can be programmed with a desired interface. The user mode includes the MCU extended mode and MCU single-chip mode (modes 2 and 3) in which the on-chip ROM is enabled.

| Item                                                                                                                        | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27.10.10 Items<br>Prohibited during<br>Programming and<br>Erasure<br>27.10.11 Abnormal<br>Ending of Programming             | 1575 | <ul> <li>Added</li> <li>Cutting off the power supply</li> <li>Transitions to software standby mode</li> <li>Read access to the flash memory by the CPU, DMAC or DTC</li> <li>Writing a new value to the FRQCR register</li> <li>Setting the PCKAR register for a different frequency from that of Pφ.</li> </ul>                                                         |

| or Erasure                                                                                                                  |      |                                                                                                                                                                                                                                                                                                                                                                          |

| <ul><li>28.1 Features</li><li>Blank check function</li></ul>                                                                | 1580 | Added<br>Blank checking proceeds for areas where erasure has been<br>completed normally to confirm that the data have actually been<br>erased. When erasure or programming in progress is stopped (e.g.<br>by input of the reset signal or shutting down the power), blank<br>checking cannot be used to check whether the data have actually<br>been erased or written. |

| 28.8.9 Items Prohibited<br>during Programming<br>and Erasure                                                                | 1619 | <ul> <li>Added</li> <li>Cutting off the power supply</li> <li>Transitions to software standby mode</li> <li>Read access to the flash memory by the CPU, DMAC or DTC</li> <li>Writing a new value to the FRQCR register</li> <li>Setting the PCKAR register for a different frequency from that of Pφ.</li> </ul>                                                         |

| 28.8.10 Abnormal<br>Ending of Programming<br>or Erasure<br>28.8.11 Handling when<br>Erasure or<br>Programming is<br>Stopped | 1619 | Subsection added                                                                                                                                                                                                                                                                                                                                                         |

| Table 30.4 Register<br>States in Software<br>Standby Mode                                                                   | 1641 | Amended     Initialized     Registers Whose       Module Name     Registers     Content is Retained       Compare match timer (CMT)     All registers                                                                                                                                                                                                                    |