Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFL

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | SH2A-FPU                                                                         |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 100MHz                                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SCI, SPI, USB                                |

| Peripherals                | DMA, PWM, WDT                                                                    |

| Number of I/O              | 112                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | <u>.</u>                                                                         |

| RAM Size                   | 64К х 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x12b                                                                        |

| Oscillator Type            | External                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

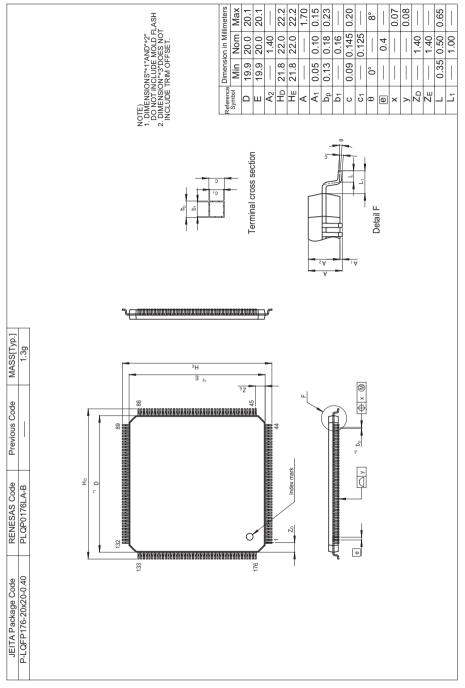

| Package / Case             | 176-LQFP                                                                         |

| Supplier Device Package    | 176-LFQFP (20x20)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f72145hdfa-v1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Items               | Specification                                                                                       |

|---------------------|-----------------------------------------------------------------------------------------------------|

| FPU                 | On-chip floating-point coprocessor                                                                  |

| (SH7216 Group only) | Supports single-precision (32 bits) and double-precision (64 bits)                                  |

|                     | Supports IEEE 754-compliant data types and exceptions                                               |

|                     | Rounding mode: Round to Nearest and Round to Zero                                                   |

|                     | Handling of denormalize numbers: Truncation to Zero                                                 |

|                     | Floating-point registers                                                                            |

|                     | Sixteen 32-bit floating-point registers (single-precision x 16 words or double-precision x 8 words) |

|                     | Two 32-bit floating-point system registers                                                          |

|                     | Supports FMAC (multiply and accumulate) instruction                                                 |

|                     | Supports FDIV (division) and FSQRT (square root) instructions                                       |

|                     | <ul> <li>Supports FLDI0/FLDI1 (load constant 0/1) instructions</li> </ul>                           |

|                     | Instruction execution times                                                                         |

|                     | Latency (FMAC/FADD/FSUB/FMUL): 3 cycles (single-precision), 8 cycles (double-precision)             |

|                     | Pitch (FMAC/FADD/FSUB/FMUL): 1 cycle (single-precision), 6 cycles (double-precision)                |

|                     | Note: FMAC is supported for single-precision only.                                                  |

|                     | Five-stage pipeline                                                                                 |

| Operating modes     | Operating modes                                                                                     |

|                     | Extended ROM enabled mode                                                                           |

|                     | Single-chip mode                                                                                    |

|                     | Processing states                                                                                   |

|                     | Program execution state                                                                             |

|                     | Exception handling state                                                                            |

|                     | Bus mastership release state                                                                        |

|                     | Power-down modes                                                                                    |

|                     | Sleep mode                                                                                          |

|                     | Software standby mode                                                                               |

|                     | Module standby mode                                                                                 |

|          |                |                  |                                                                                   |                          |   | Co   | ompatib | oility                 |

|----------|----------------|------------------|-----------------------------------------------------------------------------------|--------------------------|---|------|---------|------------------------|

| Instruct | tion           | Instruction Code | Operation                                                                         | Execu-<br>tion<br>Cycles |   | SH2E | SH4     | SH-2A/<br>SH2A-<br>FPU |

| BT/S     | label          | 10001101ddddddd  | Delayed branch When T = 1, disp $\times$ 2 + PC $\rightarrow$ PC, When T = 0, nop | 2/1*                     | _ | Yes  | Yes     |                        |

| BRA      | label          | 1010ddddddddddd  | Delayed branch, disp $\times$ 2 + PC $\rightarrow$ PC                             | 2                        | _ | Yes  | Yes     |                        |

| BRAF     | Rm             | 0000mmmm00100011 | Delayed branch,<br>Rm + PC $\rightarrow$ PC                                       | 2                        | _ | Yes  | Yes     |                        |

| BSR      | label          | 1011ddddddddddd  | Delayed branch, PC $\rightarrow$<br>PR, disp $\times$ 2 + PC $\rightarrow$ PC     | 2                        | _ | Yes  | Yes     |                        |

| BSRF     | Rm             | 0000mmmm00000011 | Delayed branch, PC $\rightarrow$ PR, Rm + PC $\rightarrow$ PC                     | 2                        | _ | Yes  | Yes     |                        |

| JMP      | @Rm            | 0100mmmm00101011 | Delayed branch, Rm $\rightarrow$ PC                                               | 2                        | _ | Yes  | Yes     |                        |

| JSR      | @Rm            | 0100mmmm00001011 | Delayed branch, PC $\rightarrow$ PR, Rm $\rightarrow$ PC                          | 2                        | _ | Yes  | Yes     |                        |

| JSR/N    | @Rm            | 0100mmmm01001011 | $\text{PC-2} \rightarrow \text{PR},  \text{Rm} \rightarrow \text{PC}$             | 3                        | _ |      |         | Yes                    |

| JSR/N    | @@(disp8, TBR) | 10000011ddddddd  | $PC-2 \rightarrow PR$ ,<br>(disp × 4 + TBR) $\rightarrow PC$                      | 5                        | _ |      |         | Yes                    |

| RTS      |                | 000000000001011  | Delayed branch, PR $\rightarrow$ PC                                               | 2                        | _ | Yes  | Yes     |                        |

| RTS/N    |                | 000000001101011  | $PR \to PC$                                                                       | 3                        |   |      |         | Yes                    |

| RTV/N    | Rm             | 0000mmmm01111011 | $\text{Rm} \rightarrow \text{R0, PR} \rightarrow \text{PC}$                       | 3                        | _ |      |         | Yes                    |

Note: \* One cycle when the program does not branch.

|                  |      |      | 1st Tran | sfer  |                                   |      |      |       |                                         |                                   |                                                        |

|------------------|------|------|----------|-------|-----------------------------------|------|------|-------|-----------------------------------------|-----------------------------------|--------------------------------------------------------|

| Transfer<br>Mode | CHNE | CHNS | RCHNE    | DISEL | Transfer<br>Counter* <sup>1</sup> | CHNE | CHNS | RCHNE | DISEL                                   | Transfer<br>Counter* <sup>1</sup> | DTC Transfer                                           |

| Block            | 0    | _    |          | 0     | Not 0                             |      |      |       | -                                       | _                                 | Ends at 1st<br>transfer                                |

|                  | 0    | 0_0  |          | —     |                                   | _    | _    | _     | Ends at 1st                             |                                   |                                                        |

|                  | 0    | _    | _        | 1     | _                                 |      |      | _     |                                         |                                   | transfer<br>Interrupt request<br>to CPU                |

|                  | 1    | 0    | _        | _     | _                                 | 0    | _    | _     | 0                                       | Not 0                             | Ends at 2nd<br>transfer                                |

|                  |      |      |          |       | 0 —<br>0 —                        | 0    | _    | _     | 0                                       | 0                                 | Ends at 2nd                                            |

|                  |      |      |          |       |                                   | _    | 1    | _     | transfer<br>Interrupt request<br>to CPU |                                   |                                                        |

|                  | 1    | 1    | _        | 0     |                                   | _    |      | _     | _                                       |                                   | Ends at 1st<br>transfer                                |

|                  | 1    | 1    | _        | 1     | Not 0                             | _    | _    | _     | _                                       |                                   | Ends at 1st<br>transfer<br>Interrupt request<br>to CPU |

|                  | 1    | 1    | _        | 1     | 0                                 | 0    | _    | _     | 0                                       | Not 0                             | Ends at 2nd<br>transfer                                |

|                  |      |      |          |       |                                   | 0    | _    | _     | 0                                       | 0                                 | Ends at 2nd                                            |

|                  |      |      |          |       |                                   | 0    | _    | _     | 1                                       |                                   | transfer<br>Interrupt request<br>to CPU                |

Notes: 1. CRA in normal mode transfer, CRAL in repeat transfer mode, or CRB in block transfer mode

2. When the contents of the CRAH is written to the CRAL

| Bit | Bit Name | Initial<br>Value | R/W   | Description                                                                                                                                                                                                                                                                                                                                                           |

|-----|----------|------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

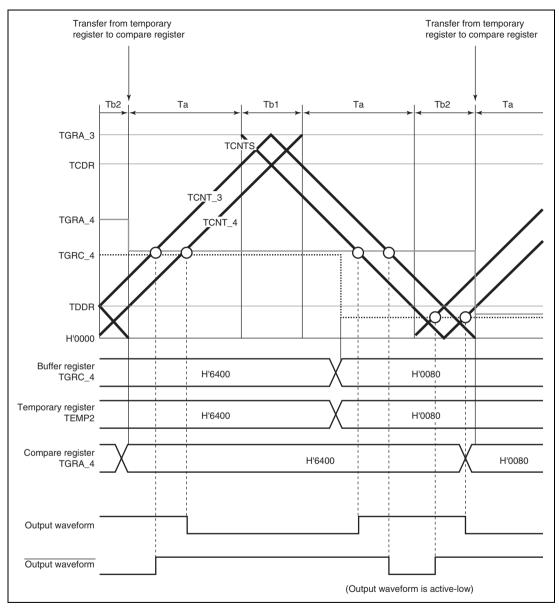

| 1   | SCC      | 0                | R/(W) | Synchronous Clearing Control                                                                                                                                                                                                                                                                                                                                          |

|     |          |                  |       | Specifies whether to clear TCNT_3 and TCNT_4 in the MTU2S when synchronous counter clearing between the MTU2 and MTU2S occurs in complementary PWM mode.                                                                                                                                                                                                              |

|     |          |                  |       | When using this control, place the MTU2S in<br>complementary PWM mode.                                                                                                                                                                                                                                                                                                |

|     |          |                  |       | When modifying the SCC bit while the counters are operating, do not modify the CCE or WRE bits.                                                                                                                                                                                                                                                                       |

|     |          |                  |       | Counter clearing synchronized with the MTU2 is<br>disabled by the SCC bit setting only when synchronous<br>clearing occurs outside the Tb interval at the trough.<br>When synchronous clearing occurs in the Tb interval at<br>the trough including the period immediately after<br>TCNT_3 and TCNT_4 start operation, TCNT_3 and<br>TCNT_4 in the MTU2S are cleared. |

|     |          |                  |       | For the Tb interval at the trough in complementary PWM mode, see figure 11.40.                                                                                                                                                                                                                                                                                        |

|     |          |                  |       | In the MTU2, this bit is reserved. It is always read as 0 and the write value should always be 0.                                                                                                                                                                                                                                                                     |

|     |          |                  |       | 0: Enables clearing of TCNT_3 and TCNT_4 in the<br>MTU2S by MTU2-MTU2S synchronous clearing<br>operation                                                                                                                                                                                                                                                              |

|     |          |                  |       | 1: Disables clearing of TCNT_3 and TCNT_4 in the<br>MTU2S by MTU2-MTU2S synchronous clearing<br>operation                                                                                                                                                                                                                                                             |

|     |          |                  |       | [Setting condition]                                                                                                                                                                                                                                                                                                                                                   |

|     |          |                  |       | • When 1 is written to SCC after reading SCC = 0                                                                                                                                                                                                                                                                                                                      |

Figure 11.40 Example of Complementary PWM Mode Operation

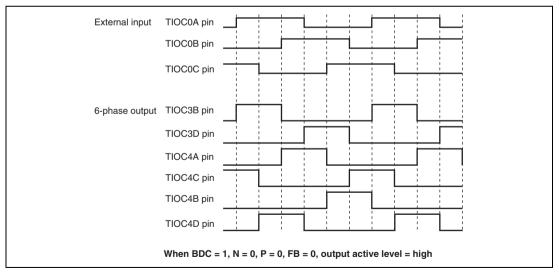

#### (q) Example of AC Synchronous Motor (Brushless DC Motor) Drive Waveform Output

In complementary PWM mode, a brushless DC motor can easily be controlled using the timer gate control register (TGCR). Figures 11.69 to 11.72 show examples of brushless DC motor drive waveforms created using TGCR.

When output phase switching for a 3-phase brushless DC motor is performed by means of external signals detected with a Hall element, etc., clear the FB bit in TGCR to 0. In this case, the external signals indicating the polarity position are input to channel 0 timer input pins TIOC0A, TIOC0B, and TIOC0C (set with PFC). When an edge is detected at pin TIOC0A, TIOC0B, or TIOC0C, the output on/off state is switched automatically.

When the FB bit is 1, the output on/off state is switched when the UF, VF, or WF bit in TGCR is cleared to 0 or set to 1.

The drive waveforms are output from the complementary PWM mode 6-phase output pins. With this 6-phase output, in the case of on output, it is possible to use complementary PWM mode output and perform chopping output by setting the N bit or P bit to 1. When the N bit or P bit is 0, level output is selected.

The 6-phase output active level (on output level) can be set with the OLSN and OLSP bits in the timer output control register (TOCR) regardless of the setting of the N and P bits.

Figure 11.69 Example of Output Phase Switching by External Input (1)

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                             |

|-----|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | SPOM     | 0                | R/W | RSPI Output Pin Mode                                                                                                                                                                                                                                                    |

|     |          |                  |     | Sets the RSPI output pins to CMOS output/open drain output.                                                                                                                                                                                                             |

|     |          |                  |     | 0: CMOS output                                                                                                                                                                                                                                                          |

|     |          |                  |     | 1: Open-drain output                                                                                                                                                                                                                                                    |

| 1   | _        | 0                | R   | Reserved                                                                                                                                                                                                                                                                |

|     |          |                  |     | The write value should always be 0. Otherwise, operation cannot be guaranteed.                                                                                                                                                                                          |

| 0   | SPLP     | 0                | R/W | RSPI Loopback                                                                                                                                                                                                                                                           |

|     |          |                  |     | When the SPLP bit is set to 1, the RSPI shuts off the<br>path between the MISO pin and the shift register,<br>and between the MOSI pin and the shift register, and<br>connects (reverses) the input path and the output<br>path for the shift register (loopback mode). |

|     |          |                  |     | 0: Normal mode                                                                                                                                                                                                                                                          |

|     |          |                  |     | 1: Loopback mode                                                                                                                                                                                                                                                        |

### 18.3.4 RSPI Status Register (SPSR)

SPSR indicates the operating status of the RSPI. SPSR can be read by the CPU. Writing 1 to the SPRF, SPTEF, MODF, and OVRF bits cannot be performed by the CPU. These bits can be cleared to 0 after they are read as 1.

| Bit:           | 7      | 6 | 5      | 4 | 3 | 2      | 1     | 0      |

|----------------|--------|---|--------|---|---|--------|-------|--------|

|                | SPRF   | - | SPTEF  | - | - | MODF   | MIDLE | OVRF   |

| Initial value: | 0      | 0 | 1      | 0 | 0 | 0      | 0     | 0      |

| R/W:           | R/(W)* | R | R/(W)* | R | R | R/(W)* | R     | R/(W)* |

Note: \* Only 0 can be written to this bit after reading it as 1 to clear the flag.

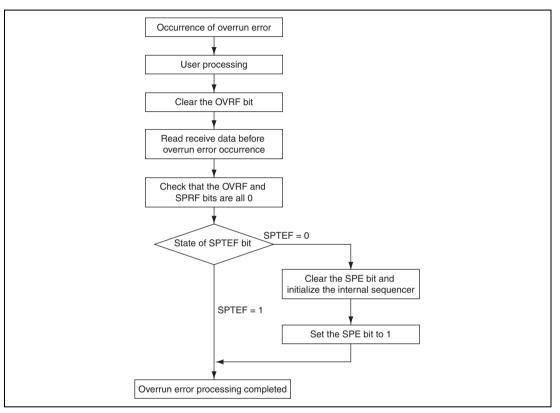

### 18.4.11 Error Processing

Figures 18.30 and 18.31 show error processing. The RSPI can recover from an error which may occur in master or slave mode, using the following error processing.

Figure 18.30 Error Processing (Overrun Error)

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                        |

|-----|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | SDAO     | 1                | R/W | SDA Output Value Control                                                                                                                                                                                                                           |

|     |          |                  |     | This bit is used with SDAOP when modifying output level of SDA. This bit should not be manipulated during transfer.                                                                                                                                |

|     |          |                  |     | 0: When reading, SDA pin outputs low.                                                                                                                                                                                                              |

|     |          |                  |     | When writing, SDA pin is changed to output low.                                                                                                                                                                                                    |

|     |          |                  |     | 1: When reading, SDA pin outputs high.                                                                                                                                                                                                             |

|     |          |                  |     | When writing, SDA pin is changed to output Hi-Z (outputs high by external pull-up resistance).                                                                                                                                                     |

| 4   | SDAOP    | 1                | R/W | SDAO Write Protect                                                                                                                                                                                                                                 |

|     |          |                  |     | Controls change of output level of the SDA pin by<br>modifying the SDAO bit. To change the output level,<br>clear SDAO and SDAOP to 0 or set SDAO to 1 and<br>clear SDAOP to 0. This bit is always read as 1.                                      |

| 3   | SCLO     | 1                | R   | SCL Output Level                                                                                                                                                                                                                                   |

|     |          |                  |     | Monitors SCL output level. When SCLO is 1, SCL pin outputs high. When SCLO is 0, SCL pin outputs low.                                                                                                                                              |

| 2   | _        | 1                | R   | Reserved                                                                                                                                                                                                                                           |

|     |          |                  |     | This bit is always read as 1. The write value should always be 1.                                                                                                                                                                                  |

| 1   | IICRST   | 0                | R/W | IIC Control Part Reset                                                                                                                                                                                                                             |

|     |          |                  |     | Resets the control part except for I <sup>2</sup> C registers. If this bit<br>is set to 1 when hang-up occurs because of<br>communication failure during I <sup>2</sup> C bus operation, some<br>IIC3 registers and the control part can be reset. |

| 0   | _        | 1                | R   | Reserved                                                                                                                                                                                                                                           |

|     |          |                  |     | This bit is always read as 1. The write value should always be 1.                                                                                                                                                                                  |

|            | _          |             |              | Pin nar                  | ne               |                           |

|------------|------------|-------------|--------------|--------------------------|------------------|---------------------------|

|            | -          |             | Initial      | function                 |                  |                           |

| Pin number | Pin number | On-chip ROM | unabled mode | On-chip ROM enabled mode | Single-chip mode |                           |

| BGA        | LQFP       | MCU mode 0  | MCU mode 1   | MCU mode 2               | MCU mode 3       | Settable function in PFC  |

| F13        | 123        |             | Ν            | IMI                      |                  | _                         |

| C13        | 134        |             | FWE/ASEBF    | KAK/ASEBRK               |                  | —                         |

| B13        | 135        |             | ASI          | EMDO                     |                  | —                         |

| D13        | 127        |             | Т            | CK                       |                  | _                         |

| D14        | 128        |             | т            | MS                       |                  | _                         |

| D15        | 125        |             | ٦            | ſDI                      |                  | _                         |

| C15        | 126        |             | т            | DO                       |                  | _                         |

| C12        | 129        |             | TI           | RST                      |                  | _                         |

| B8         | 157        |             | F            | 2A0                      |                  | PA0/CS0*1/IRQ4/CRx0/RXD0/ |

|            |            |             |              |                          |                  | RX_CLK                    |

| C7         | 158        |             | F            | PA1                      |                  | PA1/CS1*1/IRQ5/CTx0/TXD0/ |

|            |            |             |              |                          |                  | MII_RXD0                  |

| A7         | 159        |             | F            | PA2                      |                  | PA2/CS2*1/TCLKD/SSL0/     |

|            |            |             |              |                          |                  | SCK0/MII_RXD1             |

| B7         | 160        |             | F            | PA3                      |                  | PA3/CS3*1/TCLKC/MISO/     |

|            |            |             |              |                          |                  | RXD1/MII_RXD2             |

| D6         | 161        |             | F            | PA4                      |                  | PA4/CS4*1/TCLKB/MOSI/     |

|            |            |             |              |                          |                  | TXD1/MII_RXD3             |

| C6         | 162        |             | F            | PA5                      |                  | PA5/CS5*1/TCLKA/RSPCK/    |

|            |            |             |              |                          |                  | SCK1/RX_ER                |

| K14        | 103        |             | F            | PA6                      |                  | PA6/CS6*1/IRQ6/TCLKA/     |

|            |            |             |              |                          |                  | RSPCK/SCK1/TX_ER          |

| K13        | 102        |             | F            | PA7                      |                  | PA7/CS5*1/IRQ5/TCLKB/     |

|            |            |             |              |                          |                  | MOSI/TXD1/MII_TXD3        |

| K12        | 101        |             | F            | PA8                      |                  | PA8/CS4*1/IRQ4/TCLKC/     |

|            |            |             |              |                          |                  | MISO/RXD1/MII_TXD2        |

| L15        | 100        |             | F            | PA9                      |                  | PA9/CS3*1/IRQ3/TCLKD/     |

|            |            |             |              |                          |                  | SSL0/SCK0/MII_TXD1        |

## 22.1.9 Port C Pull-Up MOS Control Register L (PCPCRL)

PCPCRL controls on/off of the input pull-up MOS of port C in bits.

### • Port C Pull-Up MOS Control Register L (PCPCRL)

| Bit: 15          | 14          | 13          | 12          | 11          | 10          | 9          | 8          | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

|------------------|-------------|-------------|-------------|-------------|-------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|

| PC15<br>PCR      | PC14<br>PCR | PC13<br>PCR | PC12<br>PCR | PC11<br>PCR | PC10<br>PCR | PC9<br>PCR | PC8<br>PCR | PC7<br>PCR | PC6<br>PCR | PC5<br>PCR | PC4<br>PCR | PC3<br>PCR | PC2<br>PCR | PC1<br>PCR | PC0<br>PCR |

| Initial value: 0 | 0           | 0           | 0           | 0           | 0           | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          |

| R/W: R/W         | R/W         | R/W         | R/W         | R/W         | R/W         | R/W        | R/W        | R/W        | R/W        | R/W        | R/W        | R/W        | R/W        | R/W        | R/W        |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                       |

|-----|----------|------------------|-----|---------------------------------------------------|

| 15  | PC15PCR  | 0                | R/W | The corresponding input pull-up MOS turns on when |

| 14  | PC14PCR  | 0                | R/W | one of these bits is set to 1.                    |

| 13  | PC13PCR  | 0                | R/W | _                                                 |

| 12  | PC12PCR  | 0                | R/W | —                                                 |

| 11  | PC11PCR  | 0                | R/W | _                                                 |

| 10  | PC10PCR  | 0                | R/W | _                                                 |

| 9   | PC9PCR   | 0                | R/W | —                                                 |

| 8   | PC8PCR   | 0                | R/W | _                                                 |

| 7   | PC7PCR   | 0                | R/W | —                                                 |

| 6   | PC6PCR   | 0                | R/W | —                                                 |

| 5   | PC5PCR   | 0                | R/W | _                                                 |

| 4   | PC4PCR   | 0                | R/W | _                                                 |

| 3   | PC3PCR   | 0                | R/W | _                                                 |

| 2   | PC2PCR   | 0                | R/W | —                                                 |

| 1   | PC1PCR   | 0                | R/W | _                                                 |

| 0   | PC0PCR   | 0                | R/W |                                                   |

# • Port D Pull-Up MOS Control Register L (PDPCRL)

| Bit: 15          | 14          | 13          | 12          | 11          | 10          | 9          | 8          | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

|------------------|-------------|-------------|-------------|-------------|-------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|

| PD15<br>PCR      | PD14<br>PCR | PD13<br>PCR | PD12<br>PCR | PD11<br>PCR | PD10<br>PCR | PD9<br>PCR | PD8<br>PCR | PD7<br>PCR | PD6<br>PCR | PD5<br>PCR | PD4<br>PCR | PD3<br>PCR | PD2<br>PCR | PD1<br>PCR | PD0<br>PCR |

| Initial value: 0 | 0           | 0           | 0           | 0           | 0           | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          |

| R/W: R/W         | R/W         | R/W         | R/W         | R/W         | R/W         | R/W        | R/W        | R/W        | R/W        | R/W        | R/W        | R/W        | R/W        | R/W        | R/W        |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                  |

|-----|----------|------------------|-----|----------------------------------------------|

| 15  | PD15PCR  | 0                | R/W | The corresponding input pull-up MOS turns on |

| 14  | PD14PCR  | 0                | R/W | when one of these bits is set to 1.          |

| 13  | PD13PCR  | 0                | R/W | _                                            |

| 12  | PD12PCR  | 0                | R/W | _                                            |

| 11  | PD11PCR  | 0                | R/W | _                                            |

| 10  | PD10PCR  | 0                | R/W | _                                            |

| 9   | PD9PCR   | 0                | R/W | _                                            |

| 8   | PD8PCR   | 0                | R/W | _                                            |

| 7   | PD7PCR   | 0                | R/W | _                                            |

| 6   | PD6PCR   | 0                | R/W | _                                            |

| 5   | PD5PCR   | 0                | R/W | _                                            |

| 4   | PD4PCR   | 0                | R/W | _                                            |

| 3   | PD3PCR   | 0                | R/W | _                                            |

| 2   | PD2PCR   | 0                | R/W | _                                            |

| 1   | PD1PCR   | 0                | R/W | _                                            |

| 0   | PD0PCR   | 0                | R/W | _                                            |

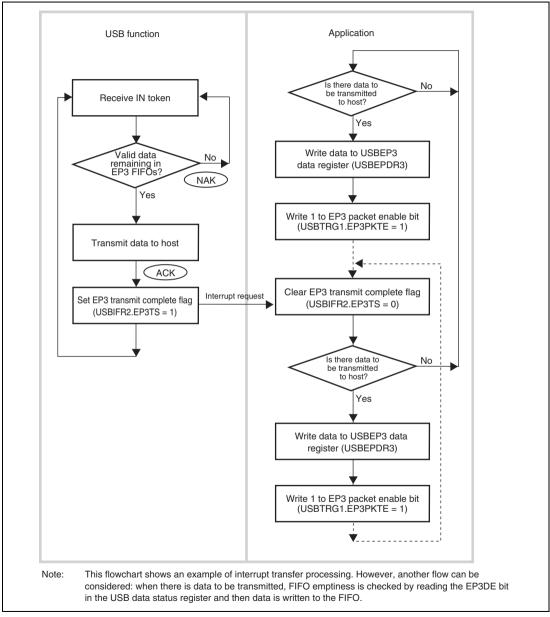

## 24.5.7 EP3/EP6/EP9 Interrupt-IN Transfer

## Figure 24.13 EP3 Interrupt-IN Transfer Operation

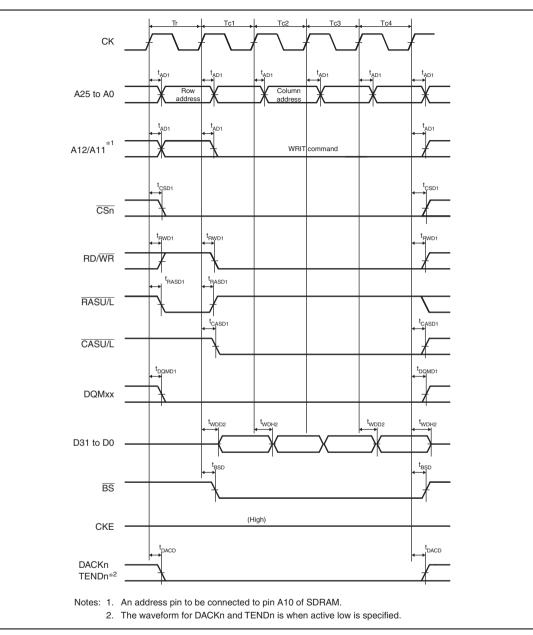

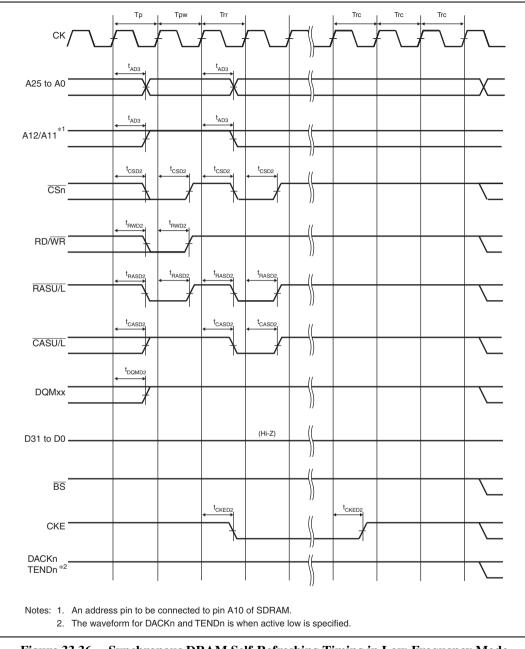

Figure 33.29 Synchronous DRAM Burst Write Bus Cycle (Four Write Cycles) (Bank Active Mode: ACT + WRITE Commands, WTRCD = 0 Cycle, TRWL = 0 Cycle)

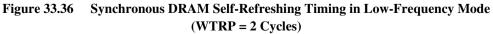

### 33.3.9 Watchdog Timer Timing

### Table 33.13 Watchdog Timer Timing

Conditions:  $V_{cc}Q = PLLV_{cc} = DrV_{cc} = 3.0 \text{ to } 3.6 \text{ V}, AV_{cc} = AVREF = 4.5 \text{ to } 5.5 \text{ V},$   $V_{ss} = PLLV_{ss} = DrV_{ss} = AVREFVSS = AV_{ss} = 0 \text{ V},$  $Ta = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C} \text{ (Industrial specifications)}$

| Item              | Symbol            | Min. | Max. | Unit | Figure       |

|-------------------|-------------------|------|------|------|--------------|

| WDTOVF delay time | t <sub>wovd</sub> |      | 50   | ns   | Figure 33.44 |

Figure 33.44 Watchdog Timer Timing

# **33.7 FLD Characteristics**

### Table 33.26 FLD (Flash Memory for Data Storage) Characteristics

Conditions:  $V_{cc}Q = PLLV_{cc} = DrV_{cc} = 3.0 \text{ to } 3.6 \text{ V}, AV_{cc} = AVREF = 4.5 \text{ to } 5.5 \text{ V},$  $V_{ss} = PLLV_{ss} = DrV_{ss} = AVREFVSS = AV_{ss} = 0 \text{ V},$

Operating temperature range during programming/erasing:

$Ta = -40^{\circ}C$  to  $+85^{\circ}C$  (Industrial specifications)

| Item                                                                         |              | Symbol              | Min. | Тур. | Max.  | Unit  | Test<br>Conditions       | Figure  |

|------------------------------------------------------------------------------|--------------|---------------------|------|------|-------|-------|--------------------------|---------|

| Programming                                                                  | 8 bytes      | t <sub>P8</sub>     | _    | 0.4  | 2     | ms    | $P\phi = 50 \text{ MHz}$ |         |

| time                                                                         | 128 bytes    | t <sub>P128</sub>   | _    | 1    | 5     | ms    | _                        |         |

| Erasure time                                                                 | 8 Kbytes     | t <sub>esk</sub>    |      | 300  | 900   | ms    | $P\phi = 50 \text{ MHz}$ |         |

| Blank check                                                                  | 8 bytes      | t <sub>BC8</sub>    | _    | _    | 30    | μs    | $P\phi = 50 \text{ MHz}$ |         |

| time                                                                         | 8 Kbytes     | t <sub>всак</sub>   |      | _    | 2.5   | ms    | -                        |         |

| Rewrite/erase                                                                | $N_{_{PEC}}$ | 30000* <sup>2</sup> | _    |      | Times |       |                          |         |

| Suspend delay time during writing                                            |              |                     |      | _    | 225   | μs    | $P\phi = 20 \text{ MHz}$ | Figure  |

|                                                                              |              |                     |      | _    | 175   | μs    | $P\phi = 40 \text{ MHz}$ | - 33.71 |

|                                                                              |              |                     |      | _    | 155   | μs    | $P\phi = 50 \text{ MHz}$ | _       |

| First suspend delay time<br>during erasing (in<br>suspension priority mode)  |              | t <sub>sesd1</sub>  | _    | _    | 220   | μs    | $P\phi = 20 \text{ MHz}$ | _       |

|                                                                              |              |                     |      | _    | 130   | μs    | $P\phi = 40 \text{ MHz}$ |         |

|                                                                              |              |                     |      | _    | 120   | μs    | $P\phi = 50 \text{ MHz}$ | _       |

| Second suspend delay<br>time during erasing (in<br>suspension priority mode) |              | t <sub>sesd2</sub>  |      |      | 1.7   | ms    | Ρφ = 50 MHz              | -       |

| Suspend delay time during erasing in erasure priority mode                   |              | t <sub>seed</sub>   | _    |      | 1.7   | ms    | -                        |         |

| Resume command interval time                                                 |              | t <sub>resi</sub>   | 1.7  | —    | —     | ms    | -                        |         |

| Data hold time*3                                                             |              | t <sub>DDRP</sub>   | 10   | _    |       | Years | -                        |         |

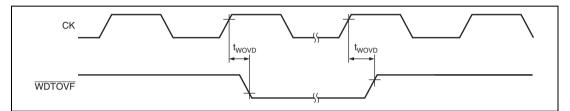

# 33.8 Usage Notes

# 33.8.1 Notes on Connecting Capacitors

This LSI includes an internal step-down circuit to automatically reduce the internal power supply voltage to an appropriate level. Between this internal stepped-down power supply ( $V_{cL}$  pin) and the  $V_{ss}$  pin, a capacitor for stabilizing the internal voltage needs to be connected. Connection of the external capacitor is shown in figure 33.72. The external capacitor should be located near the pin. Do not apply any power supply voltage to the  $V_{cL}$  pin.

A multilayer ceramic capacitor should be inserted for each pair of power supply pins as a bypass capacitor. The bypass capacitor must be inserted as close to the power supply pins of the LSI as possible. Connect the bypass capacitor and the capacitor for stabilizing the internal voltage with the capacitance from 0.02 to 0.33  $\mu$ F, after being evaluated in the system. For details on capacitors related to crystal oscillation, see section 4.9, Notes on Board Design.

Figure 33.72 Connection of Capacitors