#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | SH2A-FPU                                                                         |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SCI, SPI, USB                                |

| Peripherals                | DMA, PWM, WDT                                                                    |

| Number of I/O              | 112                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | ·                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x12b                                                                        |

| Oscillator Type            | External                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 176-LFBGA                                                                        |

| Supplier Device Package    | 176-LFBGA (13x13)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f72165adbg-u1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### (2) Global Base Register (GBR)

GBR is referenced as the base address in a GBR-referencing MOV instruction.

#### (3) Vector Base Register (VBR)

VBR is referenced as the branch destination base address when an exception or an interrupt occurs.

#### (4) Jump Table Base Register (TBR)

TBR is referenced as the start address of a function table located in memory in a JSR/N@@(disp8,TBR) table-referencing subroutine call instruction.

#### 2.2.3 System Registers

The system registers consist of four 32-bit registers: the high and low multiply and accumulate registers (MACH and MACL), the procedure register (PR), and the program counter (PC). MACH and MACL store the results of multiply or multiply and accumulate operations. PR stores the return address from a subroutine procedure. PC indicates the program address being executed and controls the flow of the processing.

| MACH | Multiply and accumulate register high (MACH) and multiply<br>and accumulate register low (MACL):<br>Store the results of multiply or multiply and accumulate operations. |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Procedure register (PR):<br>Stores the return address from a subroutine procedure.                                                                                       |

|      | Program counter (PC):<br>Indicates the four bytes ahead of the current instruction.                                                                                      |

#### Figure 2.4 System Registers

# (1) Multiply and Accumulate Register High (MACH) and Multiply and Accumulate Register Low (MACL)

MACH and MACL are used as the addition value in a MAC instruction, and store the result of a MAC or MUL instruction.

#### (8) AD Clock Frequency Control Register (ACLKCR)

The AD clock frequency control register (ACLKCR) has control bits assigned for the following functions: the frequency division ratio of the AD clock ( $A\phi$ ).

#### (9) Standby Control Register

The standby control register has bits for controlling the power-down modes and for selecting the USB clock. See section 30, Power-Down Modes, for more information.

#### (10) Oscillation Stop Detection Control Register (OSCCR)

The oscillation stop detection control register (OSCCR) has an oscillation stop detection flag and a bit for selecting flag status output through an external pin.

#### (11) USB-only oscillator

The oscillator for USB clock only that is connected to the resonator of 48 MHz.

# 4.9 Notes on Board Design

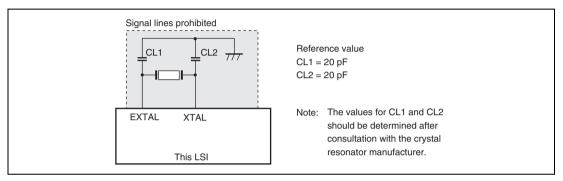

### 4.9.1 Note on Using an External Crystal Resonator

Place the crystal resonator and capacitors CL1 and CL2 as close to the XTAL and EXTAL pins as possible. In addition, to minimize induction and thus obtain oscillation at the correct frequency, the capacitors to be attached to the resonator must be grounded to the same ground. Do not bring wiring patterns close to these components.

Figure 4.9 Note on Using a Crystal Resonator

### 7.6 Usage Notes

- The CPU can read from or write to the UBC registers via the I bus. Accordingly, during the period from executing an instruction to rewrite the UBC register till the new value is actually rewritten, the desired break may not occur. In order to know the timing when the UBC register is changed, read from the last written register. Instructions after then are valid for the newly written register value.

- 2. The UBC cannot monitor access to the C bus and I bus cycles in the same channel.

- 3. When a user break and another exception occur at the same instruction, which has higher priority is determined according to the priority levels defined in table 5.1 in section 5, Exception Handling. If an exception with a higher priority occurs, the user break does not occur.

- 4. Note the following when a break occurs in a delay slot. If a pre-execution break is set at a delay slot instruction, the break is not generated until immediately before execution of the branch destination.

- 5. User breaks are disabled during UBC module standby mode. Do not read from or write to the UBC registers during UBC module standby mode; the values are not guaranteed.

- 6. Do not set an address within an interrupt exception handling routine whose interrupt priority level is at least 15 (including user break interrupts) as a break address.

- 7. Do not set break after instruction execution for the SLEEP instruction or for the delayed branch instruction where the SLEEP instruction is placed at its delay slot.

- 8. When setting a break for a 32-bit instruction, set the address where the upper 16 bits are placed. If the address of the lower 16 bits is set and a break before instruction execution is set as a break condition, the break is handled as a break after instruction execution.

- 9. Do not set a pre-execution break for an instruction that immediately follows a DIVU or DIVS instruction. If such a break is set and an interrupt or other exception occurs during execution of the DIVU or DIVS instruction, the pre-execution break will still occur even though execution of the DIVU or DIVS instruction is suspended.

- 10. Do not set a pre- and post-execution break for the same address at the same time. For example, if a pre-execution break for channel 0 and a post -execution break for channel 1 are set for the same address at the same time, the condition match flags on channel 1 after instruction execution will be set even though a pre-execution break has occurred on channel 0.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                          |

|-----|----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10  | DTSA     | 0                | R/W | DTC Short Address Mode                                                                                                                                                                               |

|     |          |                  |     | Selects the short address mode in which only three longwords are required for DTC transfer information read.                                                                                         |

|     |          |                  |     | 0: Four longwords are read as the transfer information.<br>The transfer information is arranged as shown in the<br>figure for normal mode in figure 8.2.                                             |

|     |          |                  |     | 1: Three longwords are read as the transfer information.<br>The transfer information is arranged as shown in the<br>figure for short address mode in figure 8.2.                                     |

|     |          |                  |     | Note: The short address mode can be used only for<br>transfer between an on-chip peripheral module<br>and the on-chip RAM because the upper eight<br>bits of SAR and DAR are assumed as all 1s.      |

| 9   | _        | 0                | R   | Reserved                                                                                                                                                                                             |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0.                                                                                                                                    |

| 8   | DTPR     | 0                | R/W | DTC Activation Priority                                                                                                                                                                              |

|     |          |                  |     | Selects whether to start transfer from the first DTC activation request or according to the DTC activation priority when multiple DTC activation requests are generated before the DTC is activated. |

|     |          |                  |     | For details, see section 8.5.10, DTC Activation Priority Order.                                                                                                                                      |

|     |          |                  |     | <ol> <li>Starts transfer from the DTC activation request<br/>generated first.</li> </ol>                                                                                                             |

|     |          |                  |     | <ol> <li>Starts transfer according to the DTC activation<br/>priority.</li> </ol>                                                                                                                    |

|     |          |                  |     | Notes: When this bit is set to 1, the following restrictions apply.                                                                                                                                  |

|     |          |                  |     | <ol> <li>The vector information must be stored in the<br/>on-chip ROM or on-chip RAM.</li> </ol>                                                                                                     |

|     |          |                  |     | <ol><li>The transfer information must be stored in the on-chip RAM.</li></ol>                                                                                                                        |

|     |          |                  |     | <ol> <li>The function for skipping the transfer<br/>information read step is always disabled.</li> </ol>                                                                                             |

|     |          |                  |     | <ol> <li>Set this bit to 1 while DTLOCK = 0. The<br/>DTLOCK bit should not be set to 1.</li> </ol>                                                                                                   |

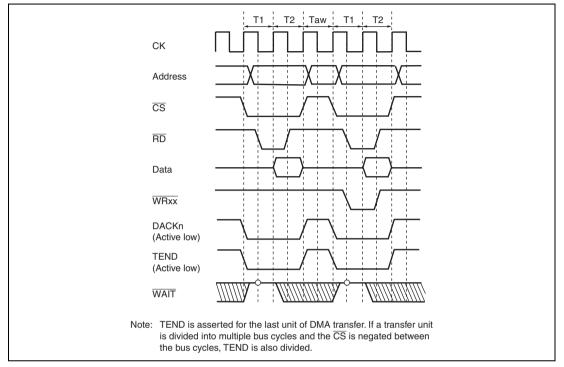

Use a setting that does not divide DACK or specify a transfer size smaller than the external device bus width if DACK is divided. Figure 10.18 shows this example.

### Figure 10.18 BSC Normal Memory Access (No Wait, Idle Cycle 1, Longword Access to 16-Bit Device)

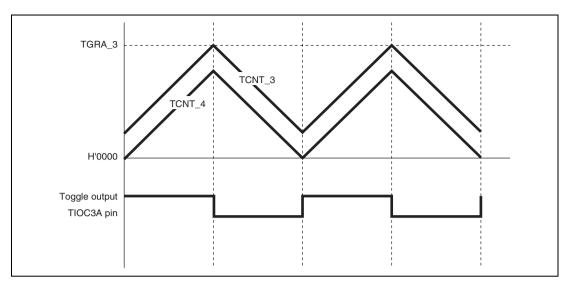

Figure 11.54 Example of Toggle Output Waveform Synchronized with PWM Output

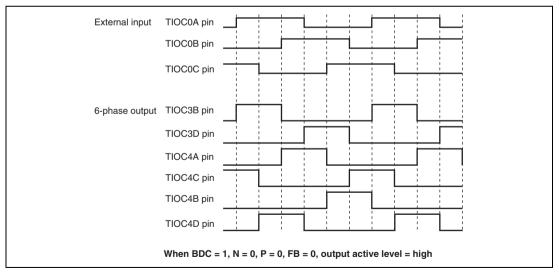

#### (q) Example of AC Synchronous Motor (Brushless DC Motor) Drive Waveform Output

In complementary PWM mode, a brushless DC motor can easily be controlled using the timer gate control register (TGCR). Figures 11.69 to 11.72 show examples of brushless DC motor drive waveforms created using TGCR.

When output phase switching for a 3-phase brushless DC motor is performed by means of external signals detected with a Hall element, etc., clear the FB bit in TGCR to 0. In this case, the external signals indicating the polarity position are input to channel 0 timer input pins TIOC0A, TIOC0B, and TIOC0C (set with PFC). When an edge is detected at pin TIOC0A, TIOC0B, or TIOC0C, the output on/off state is switched automatically.

When the FB bit is 1, the output on/off state is switched when the UF, VF, or WF bit in TGCR is cleared to 0 or set to 1.

The drive waveforms are output from the complementary PWM mode 6-phase output pins. With this 6-phase output, in the case of on output, it is possible to use complementary PWM mode output and perform chopping output by setting the N bit or P bit to 1. When the N bit or P bit is 0, level output is selected.

The 6-phase output active level (on output level) can be set with the OLSN and OLSP bits in the timer output control register (TOCR) regardless of the setting of the N and P bits.

Figure 11.69 Example of Output Phase Switching by External Input (1)

# 14.3 Operation

#### 14.3.1 Interval Count Operation

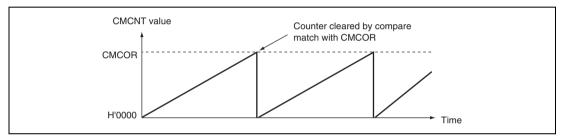

When an internal clock is selected with the CKS[1:0] bits in CMCSR and the STR bit in CMSTR is set to 1, CMCNT starts incrementing using the selected clock. When the values in CMCNT and CMCOR match, CMCNT is cleared to H'0000 and the CMF flag in CMCSR is set to 1. When the CMIE bit in CMCSR is set to 1 at this time, a compare match interrupt (CMI) is requested. CMCNT then starts counting up again from H'0000.

Figure 14.2 shows the operation of the compare match counter.

Figure 14.2 Counter Operation

### 14.3.2 CMCNT Count Timing

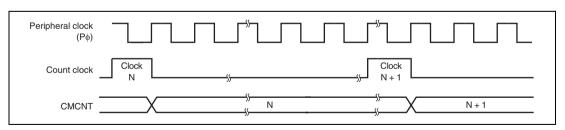

One of four clocks ( $P\phi/8$ ,  $P\phi/32$ ,  $P\phi/128$ , and  $P\phi/512$ ) obtained by dividing the peripheral clock ( $P\phi$ ) can be selected with the CKS[1:0] bits in CMCSR. Figure 14.3 shows the timing.

Figure 14.3 Count Timing

## **17.2** Input/Output Pins

Table 17.1 shows the pin configuration of the SCIF.

#### Table 17.1Pin Configuration

| Channel | Pin Name           | Symbol | I/O    | Function             |

|---------|--------------------|--------|--------|----------------------|

| 3       | Serial clock pins  | SCK3   | I/O    | Clock I/O            |

|         | Receive data pins  | RXD3   | Input  | Receive data input   |

|         | Transmit data pins | TXD3   | Output | Transmit data output |

### **17.3** Register Descriptions

The SCIF has the following registers.

#### Table 17.2 Register Configuration

| Channel | Register Name                   | Abbreviation | R/W                 | Initial Value | Address    | Access<br>Size |

|---------|---------------------------------|--------------|---------------------|---------------|------------|----------------|

| 3       | Serial mode register_3          | SCSMR_3      | R/W                 | H'0000        | H'FFFE9800 | 16             |

|         | Bit rate register_3             | SCBRR_3      | R/W                 | H'FF          | H'FFFE9804 | 8              |

|         | Serial control register_3       | SCSCR_3      | R/W                 | H'0000        | H'FFFE9808 | 16             |

|         | Transmit FIFO data register_3   | SCFTDR_3     | W                   | Undefined     | H'FFFE980C | 8              |

|         | Serial status register_3        | SCFSR_3      | R/(W)*1             | H'0060        | H'FFFE9810 | 16             |

|         | Receive FIFO data register_3    | SCFRDR_3     | R                   | Undefined     | H'FFFE9814 | 8              |

|         | FIFO control register_3         | SCFCR_3      | R/W                 | H'0000        | H'FFFE9818 | 16             |

|         | FIFO data count register_3      | SCFDR_3      | R                   | H'0000        | H'FFFE981C | 16             |

|         | Serial port register_3          | SCSPTR_3     | R/W                 | H'005x        | H'FFFE9820 | 16             |

|         | Line status register_3          | SCLSR_3      | R/(W)* <sup>2</sup> | H'0000        | H'FFFE9824 | 16             |

|         | Serial extended mode register_3 | SCSEMR_3     | R/W                 | H'00          | H'FFFE9900 | 8              |

Notes: 1. Only 0 can be written to clear the flag. Bits 15 to 8, 3, and 2 are read-only bits that cannot be modified.

2. Only 0 can be written to clear the flag. Bits 15 to 1 are read-only bits that cannot be modified.

| Bit | Bit Name   | Initial<br>Value | R/W  | Description                                                                                                       |

|-----|------------|------------------|------|-------------------------------------------------------------------------------------------------------------------|

| DIL | Dit Maille | value            | N/ W | Description                                                                                                       |

| 2   | PER        | 0                | R    | Parity Error Indication                                                                                           |

|     |            |                  |      | Indicates a parity error in the data read from the next receive FIFO data register (SCFRDR) in asynchronous mode. |

|     |            |                  |      | 0: No receive parity error occurred in the next data<br>read from SCFRDR                                          |

|     |            |                  |      | [Clearing conditions]                                                                                             |

|     |            |                  |      | <ul> <li>PER is cleared to 0 when the chip undergoes a<br/>power-on reset</li> </ul>                              |

|     |            |                  |      | • PER is cleared to 0 when no parity error is present in the next data read from SCFRDR                           |

|     |            |                  |      | 1: A receive parity error occurred in the next data read<br>from SCFRDR                                           |

|     |            |                  |      | [Setting condition]                                                                                               |

|     |            |                  |      | <ul> <li>PER is set to 1 when a parity error is present in<br/>the next data read from SCFRDR</li> </ul>          |

|     |            |                  |      | the next data read from SCFRDR                                                                                    |

**Important:** Please note that, when this function is used, the RTR bit will never be set despite receiving a Remote Frame. When a Remote Frame is received, the CPU will be notified by the corresponding RFPR set, however, as RCAN-ET needs to transmit the current message as a Data Frame, the RTR bit remains unchanged.

**Important:** Please note that in case of overrun condition (UMSR flag set when the Mailbox has its NMC = 0) the message received is discarded. In case a remote frame is causing overrun into a Mailbox configured with ATX = 1, the transmission of the corresponding data frame may be triggered only if the related RFPR flag is cleared by the CPU when the UMSR flag is set. In such case RFPR flag would get set again.

| ΑΤΧ | Description                                                   |

|-----|---------------------------------------------------------------|

| 0   | Automatic Transmission of Data Frame disabled (Initial value) |

| 1   | Automatic Transmission of Data Frame enabled                  |

**DART (Disable Automatic Re-Transmission):** When this bit is set, it disables the automatic retransmission of a message in the event of an error on the CAN bus or an arbitration lost on the CAN bus. In effect, when this function is used, the corresponding TXCR bit is automatically set at the start of transmission. When this bit is set to '0', RCAN-ET tries to transmit the message as many times as required until it is successfully transmitted or it is cancelled by the TXCR.

| DART | Description                             |

|------|-----------------------------------------|

| 0    | Re-transmission enabled (Initial value) |

| 1    | Re-Transmission disabled                |

**MBC[2:0]** (Mailbox Configuration): These bits configure the nature of each Mailbox as follows. When MBC=111 (Bin), the Mailbox is inactive, i.e., it does not receive or transmit a message regardless of TXPR or other settings. The MBC='110', '101' and '100' settings are prohibited. When the MBC is set to any other value, the LAFM field becomes available. Please don't set TXPR when MBC is set as reception. There is no hardware protection, and TXPR remains set. MBC[1] of Mailbox-0 is fixed to "1" by hardware. This is to ensure that MB0 cannot be configured to transmit Messages.

SH7214 Group, SH7216 Group

| Bit      | Bit Name | Initial<br>Value | R/W | Description                                             |

|----------|----------|------------------|-----|---------------------------------------------------------|

| 24       | RFCOFIP  | 0                | R/W | Receive Frame Counter Overflow Interrupt Enable         |

|          |          |                  |     | 0: Receive frame counter overflow interrupt is disabled |

|          |          |                  |     | 1: Receive frame counter overflow interrupt is enabled  |

| 23       | ADEIP    | 0                | R/W | Address Error Interrupt Enable                          |

|          |          |                  |     | 0: Address error interrupt is disabled                  |

|          |          |                  |     | 1: Address error interrupt is enabled                   |

| 22       | ECIIP    | 0                | R/W | EtherC Status Register Source Interrupt Enable          |

|          |          |                  |     | 0: EtherC status interrupt is disabled                  |

|          |          |                  |     | 1: EtherC status interrupt is enabled                   |

| 21       | TCIP     | 0                | R/W | Frame Transmission Complete Interrupt Enable            |

|          |          |                  |     | 0: Frame transmission complete interrupt is disabled    |

|          |          |                  |     | 1: Frame transmission complete interrupt is enabled     |

| 20       | TDEIP    | 0                | R/W | Transmit Descriptor Empty Interrupt Enable              |

|          |          |                  |     | 0: Transmit descriptor empty interrupt is disabled      |

|          |          |                  |     | 1: Transmit descriptor empty interrupt is enabled       |

| 19       | TFUFIP   | 0                | R/W | Transmit FIFO Underflow Interrupt Enable                |

|          |          |                  |     | 0: Underflow interrupt is disabled                      |

|          |          |                  |     | 1: Underflow interrupt is enabled                       |

| 18       | FRIP     | 0                | R/W | Frame Reception Interrupt Enable                        |

|          |          |                  |     | 0: Frame reception interrupt is disabled                |

|          |          |                  |     | 1: Frame reception interrupt is enabled                 |

| 17       | RDEIP    | 0                | R/W | Receive Descriptor Empty Interrupt Enable               |

|          |          |                  |     | 0: Receive descriptor empty interrupt is disabled       |

|          |          |                  |     | 1: Receive descriptor empty interrupt is enabled        |

| 16       | RFOFIP   | 0                | R/W | Receive FIFO Overflow Interrupt Enable                  |

|          |          |                  |     | 0: Overflow interrupt is disabled                       |

|          |          |                  |     | 1: Overflow interrupt is enabled                        |

| 15 to 12 | —        | All 0            | R   | Reserved                                                |

|          |          |                  |     | The write value should always be 0.                     |

| 11       | CNDIP    | 0                | R/W | Carrier Not Detect Interrupt Enable                     |

|          |          |                  |     | 0: Carrier not detect interrupt is disabled             |

|          |          |                  |     | 1: Carrier not detect interrupt is enabled              |

| Bit | Bit Name | Initial<br>Value | R/W    | Description                                                                     |  |  |  |

|-----|----------|------------------|--------|---------------------------------------------------------------------------------|--|--|--|

| 1   | EDH      | 0                | R/(W)* | NMI Interrupt Detect                                                            |  |  |  |

|     |          |                  |        | 0: No NMI interrupt has been detected                                           |  |  |  |

|     |          |                  |        | 1: An NMI interrupt has been detected                                           |  |  |  |

|     |          |                  |        | The E-DMAC stops operating when an NMI interrupt is detected while NMIE = $0$ . |  |  |  |

|     |          |                  |        | Note: Only writing 0 after reading 1 is enabled.                                |  |  |  |

| 0   | NMIE     | 0                | R/W    | NMI Interrupt Control                                                           |  |  |  |

|     |          |                  |        | 0: The E-DMAC stops operating when an NMI interrupt<br>is detected              |  |  |  |

|     |          |                  |        | 1: The E-DMAC continues to operate even when an<br>NMI interrupt is detected    |  |  |  |

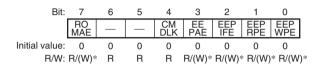

#### 28.3.2 Flash Access Status Register (FASTAT)

FASTAT indicates the access error status for the ROM and FLD. In on-chip ROM disabled mode, FASTAT is read as H'00 and writing to it is ignored. If any bit in FASTAT is set to 1, the FCU enters command-locked state (see section 28.7.3, Error Protection). To cancel command-locked state, set FASTAT to H'10, and then issue a status-clear command to the FCU. FASTAT is initialized by a power-on reset.

Note: \* Only 0 can be written to clear the flag after 1 is read.

| Bit  | Bit Name | Initial<br>Value | R/W    | Description                                                                                  |

|------|----------|------------------|--------|----------------------------------------------------------------------------------------------|

| 7    | ROMAE    | 0                | R/(W)* | ROM Access Error                                                                             |

|      |          |                  |        | Refer to section 27, Flash Memory (ROM).                                                     |

| 6, 5 | _        | All 0            | R      | Reserved                                                                                     |

|      |          |                  |        | The write value should always be 0; otherwise normal operation cannot be guaranteed.         |

| 4    | CMDLK    | 0                | R      | FCU Command Lock                                                                             |

|      |          |                  |        | Indicates whether the FCU is in command-locked state (see section 28.7.3, Error Protection). |

|      |          |                  |        | 0: The FCU is not in command-locked state                                                    |

|      |          |                  |        | 1: The FCU is in command-locked state                                                        |

|      |          |                  |        | [Setting condition]                                                                          |

|      |          |                  |        | • The FCU detects an error and enters command-<br>locked state.                              |

|      |          |                  |        | [Clearing condition]                                                                         |

|      |          |                  |        | The FCU completes the status-clear command processing.                                       |

| Module<br>Name | Register Name                           | Abbreviation | Number<br>of Bits | Address    | Access<br>Size |

|----------------|-----------------------------------------|--------------|-------------------|------------|----------------|

| MTU2S          | Timer start register_5S                 | TSTR_5S      | 8                 | H'FFFE48B4 | 8              |

|                | Timer counter U_5S                      | TCNTU_5S     | 16                | H'FFFE4880 | 16, 32         |

|                | Timer counter V_5S                      | TCNTV_5S     | 16                | H'FFFE4890 | 16, 32         |

|                | Timer counter W_5S                      | TCNTW_5S     | 16                | H'FFFE48A0 | 16, 32         |

|                | Timer general register U_5S             | TGRU_5S      | 16                | H'FFFE4882 | 16             |

|                | Timer general register V_5S             | TGRV_5S      | 16                | H'FFFE4892 | 16             |

|                | Timer general register W_5S             | TGRW_5S      | 16                | H'FFFE48A2 | 16             |

|                | Timer compare match clear register S    | TCNTCMPCLRS  | 8                 | H'FFFE48B6 | 8              |

|                | Timer start register S                  | TSTRS        | 8                 | H'FFFE4A80 | 8, 16          |

|                | Timer synchronous register S            | TSYRS        | 8                 | H'FFFE4A81 | 8              |

|                | Timer read/write enable register S      | TRWERS       | 8                 | H'FFFE4A84 | 8              |

|                | Timer output master enable register S   | TOERS        | 8                 | H'FFFE4A0A | 8              |

|                | Timer output control register 1S        | TOCR1S       | 8                 | H'FFFE4A0E | 8, 16          |

|                | Timer output control register 2S        | TOCR2S       | 8                 | H'FFFE4A0F | 8              |

|                | Timer gate control register S           | TGCRS        | 8                 | H'FFFE4A0D | 8              |

|                | Timer cycle data register S             | TCDRS        | 16                | H'FFFE4A14 | 16, 32         |

|                | Timer dead time data register S         | TDDRS        | 16                | H'FFFE4A16 | 16             |

|                | Timer subcounter S                      | TCNTSS       | 16                | H'FFFE4A20 | 16, 32         |

|                | Timer cycle buffer register S           | TCBRS        | 16                | H'FFFE4A22 | 16             |

|                | Timer interrupt skipping set register S | TITCRS       | 8                 | H'FFFE4A30 | 8, 16          |

|                | Timer interrupt skipping counter S      | TITCNTS      | 8                 | H'FFFE4A31 | 8              |

|                | Timer buffer transfer set register S    | TBTERS       | 8                 | H'FFFE4A32 | 8              |

|                | Timer dead time enable register S       | TDERS        | 8                 | H'FFFE4A34 | 8              |

|                | Timer synchronous clear register S      | TSYCRS       | 8                 | H'FFFE4A50 | 8              |

|                | Timer waveform control register S       | TWCRS        | 8                 | H'FFFE4A60 | 8              |

|                | Timer output level buffer register S    | TOLBRS       | 8                 | H'FFFE4A36 | 8              |

| POE2           | Input level control/status register 1   | ICSR1        | 16                | H'FFFE5000 | 16             |

|                | Output level control/status register 1  | OCSR1        | 16                | H'FFFE5002 | 16             |

|                | Input level control/status register 2   | ICSR2        | 16                | H'FFFE5004 | 16             |

|                | Output level control/status register 2  | OCSR2        | 16                | H'FFFE5006 | 16             |

|                | Input level control/status register 3   | ICSR3        | 16                | H'FFFE5008 | 16             |

|                | Software port output enable register    | SPOER        | 8                 | H'FFFE500A | 8              |

| Module<br>Name | Register<br>Abbreviation | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|----------------|--------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| MTU2           | TGRB_1                   |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                | TICCR                    | _                 | _                 | —                 | _                 | I2BE              | I2AE              | I1BE             | I1AE             |

|                | TCR_2                    | _                 | CCLI              | R[1:0]            | CKE               | G[1:0]            |                   | TPSC[2:0]        |                  |

|                | TMDR_2                   | —                 | _                 | —                 | —                 |                   | MD[3              | 3:0]             |                  |

|                | TIOR_2                   |                   | IOE               | 8[3:0]            |                   |                   | IOA[S             | 3:0]             |                  |

|                | TIER_2                   | TTGE              | _                 | TCIEU             | TCIEV             | —                 | —                 | TGIEB            | TGIEA            |

|                | TSR_2                    | TCFD              | _                 | TCFU              | TCFV              | —                 | —                 | TGFB             | TGFA             |

|                | TCNT_2                   |                   |                   |                   |                   |                   |                   |                  |                  |

|                | TGRA_2                   |                   |                   |                   |                   |                   |                   |                  |                  |

|                | TGRB_2                   |                   |                   |                   |                   |                   |                   |                  |                  |

|                | TCR_3                    |                   | CCLR[2:0]         |                   | СКЕ               | G[1:0]            |                   | TPSC[2:0]        |                  |

|                | TMDR_3                   | _                 | _                 | BFB               | BFA               |                   | MD[3              | 3:0]             |                  |

|                | TIORH_3                  |                   | IOE               | [3:0]             |                   |                   | IOA[3:0]          |                  |                  |

|                | TIORL_3                  |                   | IOD[3:0]          |                   |                   | IOC[3:0]          |                   |                  |                  |

|                | TIER_3                   | TTGE              | _                 | _                 | TCIEV             | TGIED             | TGIEC             | TGIEB            | TGIEA            |

|                | TSR_3                    | TCFD              | _                 | _                 | TCFV              | TGFD              | TGFC              | TGFB             | TGFA             |

|                | TCNT_3                   |                   |                   |                   |                   |                   |                   |                  |                  |

|                | TGRA_3                   |                   |                   |                   |                   |                   |                   |                  |                  |

|                | TGRB_3                   |                   |                   |                   |                   |                   |                   |                  |                  |

|                | TGRC_3                   |                   |                   |                   |                   |                   |                   |                  |                  |

|                | TGRD_3                   |                   |                   |                   |                   |                   |                   |                  |                  |

|                | TBTM_3                   | _                 | _                 | _                 | _                 | _                 | _                 | TTSB             | TTSA             |

|                | TCR_4                    |                   | CCLR[2:0]         |                   | CKE               | G[1:0]            |                   | TPSC[2:0]        |                  |

|                | TMDR_4                   | —                 | _                 | BFB               | BFA               |                   | MD[3              | 3:0]             |                  |

|                | TIORH_4                  | IOB[3:0]          |                   |                   |                   | IOA[3:0]          |                   |                  |                  |

|                | TIORL_4                  |                   | IOD               | [3:0]             |                   |                   | IOC[3             | 3:0]             |                  |

| Module<br>Name | Register  | Power-on<br>Reset | Manual<br>Reset | Software<br>Standby | Module<br>Standby | Sleep    |

|----------------|-----------|-------------------|-----------------|---------------------|-------------------|----------|

| DMAC           | DAR_6     | Initialized       | Retained        | Retained            | Retained          | Retained |

|                | DMATCR_6  | Initialized       | Retained        | Retained            | Retained          | Retained |

|                | CHCR_6    | Initialized       | Retained        | Retained            | Retained          | Retained |

|                | RSAR_6    | Initialized       | Retained        | Retained            | Retained          | Retained |

|                | RDAR_6    | Initialized       | Retained        | Retained            | Retained          | Retained |

|                | RDMATCR_6 | Initialized       | Retained        | Retained            | Retained          | Retained |

|                | SAR_7     | Initialized       | Retained        | Retained            | Retained          | Retained |

|                | DAR_7     | Initialized       | Retained        | Retained            | Retained          | Retained |

|                | DMATCR_7  | Initialized       | Retained        | Retained            | Retained          | Retained |

|                | CHCR_7    | Initialized       | Retained        | Retained            | Retained          | Retained |

|                | RSAR_7    | Initialized       | Retained        | Retained            | Retained          | Retained |

|                | RDAR_7    | Initialized       | Retained        | Retained            | Retained          | Retained |

|                | RDMATCR_7 | Initialized       | Retained        | Retained            | Retained          | Retained |

|                | DMAOR     | Initialized       | Retained        | Retained            | Retained          | Retained |

|                | DMARS0    | Initialized       | Retained        | Retained            | Retained          | Retained |

|                | DMARS1    | Initialized       | Retained        | Retained            | Retained          | Retained |

|                | DMARS2    | Initialized       | Retained        | Retained            | Retained          | Retained |

|                | DMARS3    | Initialized       | Retained        | Retained            | Retained          | Retained |

| MTU2           | TCR_0     | Initialized       | Retained        | Retained            | Initialized       | Retained |

|                | TMDR_0    | Initialized       | Retained        | Retained            | Initialized       | Retained |

|                | TIORH_0   | Initialized       | Retained        | Retained            | Initialized       | Retained |

|                | TIORL_0   | Initialized       | Retained        | Retained            | Initialized       | Retained |

|                | TIER_0    | Initialized       | Retained        | Retained            | Initialized       | Retained |

|                | TSR_0     | Initialized       | Retained        | Retained            | Initialized       | Retained |

|                | TCNT_0    | Initialized       | Retained        | Retained            | Initialized       | Retained |

|                | TGRA_0    | Initialized       | Retained        | Retained            | Initialized       | Retained |

|                | TGRB_0    | Initialized       | Retained        | Retained            | Initialized       | Retained |

|                | TGRC_0    | Initialized       | Retained        | Retained            | Initialized       | Retained |

|                | TGRD_0    | Initialized       | Retained        | Retained            | Initialized       | Retained |

# F

| -                                     |         |

|---------------------------------------|---------|

| FCU command list                      | 1534    |

| FCU command usage154                  | 1, 1609 |

| Fixed mode                            | 431     |

| FLD                                   | 1577    |

| Floating-point operation instructions | 68      |

| Floating-point registers              |         |

| Floating-point system registers       | 29      |

| Flow Control                          | 1408    |

| FPU-related CPU instructions          | 70      |

| Full-scale error                      | 1056    |

|                                       |         |

# G

| General illegal instructions | . 123 |

|------------------------------|-------|

| General registers            | 24    |

| Global base register (GBR)   | 27    |

# H

| Halt mode                | . 1109 |

|--------------------------|--------|

| Hardware protection 1566 | , 1614 |

| H-UDI interrupt          | 143    |

| H-UDI related pin timing | . 1834 |

# I

| I/O port timing            | 1829 |

|----------------------------|------|

| I/O ports                  | 1225 |

| I2C bus format             | 1004 |

| I2C bus interface 3 (IIC3) | 985  |

| ID Reorder                 | 1076 |

| IIC3 module timing         | 1826 |

| Immediate data             |      |

| Immediate data accessing   |      |

| Immediate data format                      | 34   |

|--------------------------------------------|------|

| Initial values of control registers        | 32   |

| Initial values of floating-point registers | 32   |

| Initial values of floating-point system    |      |

| registers                                  | 32   |

| Initial values of general registers        | 32   |

| Initial values of system registers         | 32   |

| Initializing RSPI                          | 960  |

| Input sampling and A/D                     |      |

| conversion time                            | 1050 |

| Instruction features                       | 35   |

| Instruction format                         | 44   |

| Instruction set                            | 48   |

| Integer division instructions              | 123  |

| Interrupt controller (INTC)                | 129  |

| Interrupt exception handling               | 120  |

| Interrupt exception handling               |      |

| vectors and priorities                     | 147  |

| Interrupt priority level                   | 119  |

| Interrupt response time                    | 159  |

| IRQ interrupts                             | 144  |

|                                            |      |

### J

| Jump table | base register | (TBR) | 27 |

|------------|---------------|-------|----|

|------------|---------------|-------|----|

### L

| Load-store architecture                  |  |

|------------------------------------------|--|

| Local acceptance filter mask (LAFM) 1074 |  |

| Location of transfer information and DTC |  |

| vector table                             |  |

| Logic operation instructions             |  |

| SCFRDR                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| SCFSR                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3                                                                                                |

| SCFTDR                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                                                                                                |

| SCLSR                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3                                                                                                |

| SCRDR (SCI)                                                                                                                                                                                                                                                                                                                                                                                                                            | 7                                                                                                |

| SCRSR (SCI)                                                                                                                                                                                                                                                                                                                                                                                                                            | 7                                                                                                |

| SCRSR (SCIF)                                                                                                                                                                                                                                                                                                                                                                                                                           | 4                                                                                                |

| SCSCR (SCI)                                                                                                                                                                                                                                                                                                                                                                                                                            | 2                                                                                                |

| SCSCR (SCIF)                                                                                                                                                                                                                                                                                                                                                                                                                           | 9                                                                                                |

| SCSDCR                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3                                                                                                |

| SCSEMR                                                                                                                                                                                                                                                                                                                                                                                                                                 | )                                                                                                |

| SCSMR (SCI)                                                                                                                                                                                                                                                                                                                                                                                                                            | 3                                                                                                |

| SCSMR (SCIF)                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                  |

| SCSPTR (SCI)                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                                                                |

| SCSPTR (SCIF)                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                  |

| SCSSR                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                  |

| SCTDR (SCI)                                                                                                                                                                                                                                                                                                                                                                                                                            | 3                                                                                                |

| SCTSR (SCI)                                                                                                                                                                                                                                                                                                                                                                                                                            | 3                                                                                                |

| SCTSR (SCIF)                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                  |

| SDCR                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                        | /                                                                                                |

| SDID                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5                                                                                                |

| SDID                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5<br>5                                                                                           |

| SDID                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5<br>5<br>8                                                                                      |

| SDID                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5<br>5<br>8<br>3                                                                                 |

| SDID                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6<br>6<br>8<br>3<br>6                                                                            |

| SDID                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6<br>6<br>8<br>3<br>6<br>3                                                                       |

| SDID                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5<br>5<br>3<br>5<br>3<br>9                                                                       |

| SDID                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6<br>6<br>8<br>6<br>7<br>8<br>6<br>7<br>8<br>7<br>8<br>7<br>8                                    |

| SDID.       1666         SDIR.       1666         SPBR       918         SPCKD       923         SPCMD       926         SPCR       903         SPDCR       919         SPDR       919         SPDR       913                                                                                                                                                                                                                          | 6<br>6<br>8<br>3<br>6<br>3<br>9<br>3<br>5                                                        |

| SDID.       1666         SDIR.       1666         SPBR       918         SPCKD       923         SPCMD       926         SPCR       903         SPDCR       919         SPDR       913         SPND       925                                                                                                                                                                                                                          | 6<br>6<br>8<br>3<br>6<br>3<br>9<br>3<br>5<br>2                                                   |

| SDID.       1666         SDIR.       1666         SPBR       918         SPCKD       923         SPCMD       926         SPCR       903         SPDCR       919         SPDR       913         SPND       925         SPOER       722                                                                                                                                                                                                  | 6<br>6<br>8<br>3<br>6<br>3<br>9<br>3<br>5<br>2<br>7                                              |

| SDID.       1666         SDIR.       1666         SPBR.       918         SPCKD.       923         SPCMD.       926         SPCR.       903         SPDCR.       919         SPDR.       913         SPND.       925         SPOER.       722         SPPCR.       907                                                                                                                                                                 | 6<br>6<br>8<br>3<br>6<br>3<br>9<br>3<br>5<br>2<br>7<br>5                                         |

| SDID.       1666         SDIR.       1666         SPBR       918         SPCKD       923         SPCMD       926         SPCR       903         SPDCR       919         SPDR       913         SPND       925         SPOER       722         SPPCR       907         SPSCR       915                                                                                                                                                  | 6683639352758                                                                                    |

| SDID.       1666         SDIR.       1666         SPBR       918         SPCKD       923         SPCMD       926         SPCR       903         SPDCR       919         SPDR       913         SPND       925         SPOER       722         SPPCR       907         SPSCR       915         SPSR       908                                                                                                                           | 6<br>6<br>7<br>7<br>7<br>8<br>6<br>7<br>7<br>8<br>6                                              |

| SDID.       1666         SDIR.       1666         SPBR       918         SPCKD       923         SPCKD       926         SPCR       903         SPDCR       919         SPDR       913         SPND       925         SPOER       722         SPPCR       907         SPSCR       915         SPSR       908         SPSSR       916                                                                                                   | 5 5 8 3 5 3 9 3 5 2 7 5 8 5 4                                                                    |

| SDID.       1666         SDIR.       1666         SPBR.       918         SPCKD.       923         SPCKD.       923         SPCKD.       923         SPCRD.       926         SPDR       903         SPDCR       919         SPDR       913         SPND.       925         SPOER.       722         SPPCR       907         SPSCR       915         SPSR       908         SPSSR       916         SSLND       924                    | 5583539352758545                                                                                 |

| SDID.       1666         SDIR.       1666         SPBR       918         SPCKD       923         SPCKD       923         SPCKD       926         SPCR       903         SPDCR       919         SPDR       913         SPND       925         SPOER       722         SPPCR       907         SPSCR       915         SPSR       908         SPSSR       916         SSLND       924         SSLP       906                            | 55835393527585452                                                                                |

| SDID.       1666         SDIR.       1666         SPBR       918         SPCKD       923         SPCKD       926         SPCR       903         SPDCR       919         SPDR       913         SPND       925         SPOER       722         SPPCR       907         SPSCR       915         SPSR       906         SSLND       924         SSLP       906         STBCR       1632                                                   | 5 5 8 3 5 3 9 3 5 2 7 5 8 5 4 5 2 3                                                              |

| SDID.       1666         SDIR.       1666         SPBR       918         SPCKD       923         SPCKD       926         SPCR       903         SPDCR       919         SPDR       913         SPND       925         SPOER       722         SPPCR       907         SPSCR       915         SPSR       906         SPSSR       916         SSLND       924         SSLP       906         STBCR       1632         STBCR2       1633 | 6<br>6<br>8<br>8<br>3<br>6<br>3<br>9<br>3<br>5<br>2<br>7<br>5<br>8<br>6<br>4<br>6<br>2<br>3<br>4 |

| STBCR5     | 1637 |

|------------|------|

| STBCR6     | 1638 |

| SYSCR1     | 1624 |

| SYSCR2     | 1626 |

| TADCOBRA_4 | 509  |

| TADCOBRB_4 |      |

| TADCORA_4  |      |

| TADCORB_4  | 509  |

| TADCR      | 506  |

| TBRAR      | 1441 |

| TBTER      | 534  |

| ТВТМ       | 501  |

| TCBR       | 531  |

| TCDR       | 530  |

| TCNT       |      |

| TCNTCMPCLR | 488  |

| TCNTS      | 529  |

| TCR        | 462  |

| TCSYSTR    | 515  |

| TDDR       | 530  |

| TDER       | 536  |

| TDFAR      |      |

| TDLAR      |      |

| TEC        |      |

| TFTR       |      |

| TFUCR      |      |

| TGCR       |      |

| TGR        |      |

| TICCR      |      |

| TIER       |      |

| TIOR       |      |

| TITCNT     |      |

| TITCR      |      |

| TLFRCR     |      |

| TMDR       |      |

| TOCR1      |      |

| TOCR2      |      |

| TOER       |      |

| TOLBR      |      |

| TPAUSECR   | 1394 |