#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFL

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | SH2A-FPU                                                                         |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SCI, SPI, USB                                |

| Peripherals                | DMA, PWM, WDT                                                                    |

| Number of I/O              | 112                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | ·                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x12b                                                                        |

| Oscillator Type            | External                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 176-LQFP                                                                         |

| Supplier Device Package    | 176-LFQFP (20x20)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f72165adfa-v1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|         | 18.4.8                 | Initializing RSPI                                              |      |

|---------|------------------------|----------------------------------------------------------------|------|

|         | 18.4.9                 | SPI Operation                                                  |      |

|         | 18.4.10                | Clock Synchronous Operation                                    |      |

|         | 18.4.11                | Error Processing                                               |      |

|         | 18.4.12                | Loopback Mode                                                  |      |

|         | 18.4.13                | Interrupt Request                                              |      |

| 18.5    | Usage No               | otes                                                           |      |

|         | 18.5.1                 | DTC Block Transfer                                             |      |

|         | 18.5.2                 | DMAC Burst Transfer                                            |      |

|         | 18.5.3                 | Reading Receive Data                                           |      |

|         | 18.5.4                 | DTC/DMAC and Mode Fault Error                                  |      |

|         | 18.5.5                 | Usage of the RSPI Output Pins as Open Drain Outputs            |      |

| Section | on 19 I <sup>2</sup> C | C Bus Interface 3 (IIC3)                                       |      |

| 19.1    |                        | ·····                                                          |      |

| 19.2    | Input/Ou               | tput Pins                                                      |      |

| 19.3    | Register               | Descriptions                                                   |      |

|         | 19.3.1                 | I <sup>2</sup> C Bus Control Register 1 (ICCR1)                |      |

|         | 19.3.2                 | I <sup>2</sup> C Bus Control Register 2 (ICCR2)                |      |

|         | 19.3.3                 | I <sup>2</sup> C Bus Mode Register (ICMR)                      |      |

|         | 19.3.4                 | I <sup>2</sup> C Bus Interrupt Enable Register (ICIER)         |      |

|         | 19.3.5                 | I <sup>2</sup> C Bus Status Register (ICSR)                    |      |

|         | 19.3.6                 | Slave Address Register (SAR)                                   | 1001 |

|         | 19.3.7                 | I <sup>2</sup> C Bus Transmit Data Register (ICDRT)            |      |

|         | 19.3.8                 | I <sup>2</sup> C Bus Receive Data Register (ICDRR)             | 1002 |

|         | 19.3.9                 | I <sup>2</sup> C Bus Shift Register (ICDRS)                    | 1002 |

|         | 19.3.10                | NF2CYC Register (NF2CYC)                                       | 1003 |

| 19.4    | Operation              | n                                                              | 1004 |

|         | 19.4.1                 | I <sup>2</sup> C Bus Format                                    | 1004 |

|         | 19.4.2                 | Master Transmit Operation                                      | 1005 |

|         | 19.4.3                 | Master Receive Operation                                       | 1007 |

|         | 19.4.4                 | Slave Transmit Operation                                       | 1009 |

|         | 19.4.5                 | Slave Receive Operation                                        | 1012 |

|         | 19.4.6                 | Clocked Synchronous Serial Format                              | 1014 |

|         | 19.4.7                 | Noise Filter                                                   | 1017 |

|         | 19.4.8                 | Using the IICRST Bit to Reset I <sup>2</sup> C Bus Interface 3 | 1018 |

|         | 19.4.9                 | Example of Use                                                 | 1019 |

| 19.5    | Interrupt              | Requests                                                       | 1023 |

| 19.6    | Data Tra               | nsfer Using DTC                                                | 1024 |

| 19.7    | Bit Syncl              | hronous Circuit                                                | 1025 |

| 19.8    | Usage No               | otes                                                           | 1027 |

|         | 19.8.1                 | Setting for Multi-Master Operation                             | 1027 |

# 2.5.8 Floating-Point Operation Instructions

# Table 2.18 Floating-Point Operation Instructions

|             |             |                  |                                           |                          |                           | Co   | ompatib | oility                 |

|-------------|-------------|------------------|-------------------------------------------|--------------------------|---------------------------|------|---------|------------------------|

| Instruction |             | Instruction Code | Operation                                 | Execu-<br>tion<br>Cycles | T Bit                     | SH2E | SH4     | SH-2A/<br>SH2A-<br>FPU |

| FABS        | FRn         | 1111nnnn01011101 | $ FRn  \to FRn$                           | 1                        | _                         | Yes  | Yes     |                        |

| FABS        | DRn         | 1111nnn001011101 | $ DRn \toDRn$                             | 1                        | _                         |      | Yes     |                        |

| FADD        | FRm, FRn    | 1111nnnnmmm0000  | $FRn + FRm \to FRn$                       | 1                        | _                         | Yes  | Yes     |                        |

| FADD        | DRm, DRn    | 1111nnn0mmm00000 | $DRn + DRm \to DRn$                       | 6                        | _                         |      | Yes     |                        |

| FCMP/EQ     | FRm, FRn    | 1111nnnmmm0100   | (FRn = FRm)? 1:0 $\rightarrow$ T          | 1                        | Compa-<br>rison<br>result | Yes  | Yes     |                        |

| FCMP/EQ     | DRm, DRn    | 1111nnn0mmm00100 | (DRn = DRm)? 1:0 $\rightarrow$ T          | 2                        | Compa-<br>rison<br>result |      | Yes     |                        |

| FCMP/GT     | FRm, FRn    | 1111nnnmmmm0101  | (FRn > FRm)? 1:0 $\rightarrow$ T          | 1                        | Compa<br>-rison<br>result | Yes  | Yes     |                        |

| FCMP/GT     | DRm, DRn    | 1111nnn0mmm00101 | (DRn > DRm)? 1:0 $\rightarrow$ T          | 2                        | Compa-<br>rison<br>result |      | Yes     |                        |

| FCNVDS      | DRm, FPUL   | 1111mmm010111101 | (float) DRm $\rightarrow$ FPUL            | 2                        | _                         |      | Yes     |                        |

| FCNVSD      | FPUL, DRn   | 1111nnn010101101 | (double) FPUL $\rightarrow$ DRn           | 2                        | _                         |      | Yes     |                        |

| FDIV        | FRm, FRn    | 1111nnnnmmm0011  | $\text{FRn/FRm} \rightarrow \text{FRn}$   | 10                       | _                         | Yes  | Yes     |                        |

| FDIV        | DRm, DRn    | 1111nnn0mmm00011 | $\text{DRn/DRm} \rightarrow \text{DRn}$   | 23                       | _                         |      | Yes     |                        |

| FLDI0       | FRn         | 1111nnnn10001101 | $0 \times 00000000 \rightarrow FRn$       | 1                        | _                         | Yes  | Yes     |                        |

| FLDI1       | FRn         | 1111nnnn10011101 | $0\times 3F800000 \rightarrow FRn$        | 1                        | _                         | Yes  | Yes     |                        |

| FLDS        | FRm, FPUL   | 1111mmmm00011101 | $\text{FRm} \rightarrow \text{FPUL}$      | 1                        | _                         | Yes  | Yes     |                        |

| FLOAT       | FPUL,FRn    | 1111nnnn00101101 | (float)FPUL $\rightarrow$ FRn             | 1                        | _                         | Yes  | Yes     |                        |

| FLOAT       | FPUL,DRn    | 1111nnn000101101 | (double)FPUL $\rightarrow$ DRn            | 2                        | _                         |      | Yes     |                        |

| FMAC        | FR0,FRm,FRn | 1111nnnnmmm1110  | $FR0 \times FRm + FRn \rightarrow$<br>FRn | 1                        | _                         | Yes  | Yes     |                        |

| FMOV        | FRm, FRn    | 1111nnnnmmm1100  | $FRm\toFRn$                               | 1                        | _                         | Yes  | Yes     |                        |

| FMOV        | DRm, DRn    | 1111nnn0mmm01100 | $\text{DRm} \rightarrow \text{DRn}$       | 2                        | _                         |      | Yes     |                        |

# 6.4.6 On-Chip Peripheral Module Interrupts

On-chip peripheral module interrupts are generated by the following on-chip peripheral modules:

- A/D converter (ADC)

- Controller area network (RCAN-ET)

- Direct memory access controller (DMAC)

- Compare match timer (CMT)

- Bus state controller (BSC)

- Watchdog timer (WDT)

- Ethernet Controller (EtherC, E-DMAC)

- USB function module (USB)

- Multi-function timer pulse unit 2 (MTU2)

- Multi-function timer pulse unit 2S (MTU2S)

- Port output enable 2 (POE2)

- I<sup>2</sup>C bus interface 3 (IIC3)

- Renesas serial peripheral interface (RSPI)

- Serial communication interface (SCI)

- Serial communication interface with FIFO (SCIF)

As every source is assigned a different interrupt vector, the source does not need to be identified in the exception service routine. A priority level in a range from 0 to 15 can be set for each module by interrupt priority registers 05 to 19 (IPR05 to IPR19). The on-chip peripheral module interrupt exception handling sets the I3 to I0 bits in SR to the priority level of the accepted on-chip peripheral module interrupt.

# 8.2.1 DTC Mode Register A (MRA)

MRA selects DTC operating mode. MRA cannot be accessed directly by the CPU.

| Bit:           | 7  | 6     | 5   | 4    | 3  | 2     | 1 | 0 |

|----------------|----|-------|-----|------|----|-------|---|---|

|                | MD | [1:0] | Sz[ | 1:0] | SM | [1:0] | - | - |

| Initial value: | *  | *     | *   | *    | *  | *     | * | * |

| R/W:           | -  | -     | -   | -    | -  | -     | - | - |

| *: Unde        |    |       |     |      |    |       |   |   |

|      |          | Initial   |     |                                                  |

|------|----------|-----------|-----|--------------------------------------------------|

| Bit  | Bit Name | Value     | R/W | Description                                      |

| 7, 6 | MD[1:0]  | Undefined | _   | DTC Mode 1 and 0                                 |

|      |          |           |     | Specify DTC transfer mode.                       |

|      |          |           |     | 00: Normal mode                                  |

|      |          |           |     | 01: Repeat mode                                  |

|      |          |           |     | 10: Block transfer mode                          |

|      |          |           |     | 11: Setting prohibited                           |

| 5, 4 | Sz[1:0]  | Undefined |     | DTC Data Transfer Size 1 and 0                   |

|      |          |           |     | Specify the size of data to be transferred.      |

|      |          |           |     | 00: Byte-size transfer                           |

|      |          |           |     | 01: Word-size transfer                           |

|      |          |           |     | 10: Longword-size transfer                       |

|      |          |           |     | 11: Setting prohibited                           |

| 3, 2 | SM[1:0]  | Undefined | _   | Source Address Mode 1 and 0                      |

|      |          |           |     | Specify an SAR operation after a data transfer.  |

|      |          |           |     | 0x: SAR is fixed                                 |

|      |          |           |     | (SAR write-back is skipped)                      |

|      |          |           |     | 10: SAR is incremented after a transfer          |

|      |          |           |     | (by 1 when Sz1 and Sz0 = B'00; by 2 when Sz1 and |

|      |          |           |     | Sz0 = B'01; by 4 when $Sz1$ and $Sz0 = B'10$ )   |

|      |          |           |     | 11: SAR is decremented after a transfer          |

|      |          |           |     | (by 1 when Sz1 and Sz0 = B'00; by 2 when Sz1 and |

|      |          |           |     | Sz0 = B'01; by 4 when Sz1 and Sz0 = B'10)        |

|       |             | Initial       |            |                                                                                                                                                                                                                                                                                                                                    |

|-------|-------------|---------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Bit Name    | Value         | R/W        | Description                                                                                                                                                                                                                                                                                                                        |

| 0     | ERR         | 0             | R/(W)*     | Transfer Stop Flag                                                                                                                                                                                                                                                                                                                 |

|       |             |               |            | Indicates that a DTC address error or NMI interrupt has occurred.                                                                                                                                                                                                                                                                  |

|       |             |               |            | If a DTC address error or NMI interrupt occurs while the<br>DTC is active, a DTC address error handling or NMI<br>interrupt handling processing is executed after the DTC<br>has released the bus mastership. The DTC halts after a<br>data transfer or a transfer information writing state<br>depending on the NMI input timing. |

|       |             |               |            | Note that a writing state is not exact, when the DTC halts<br>after a data transfer. When the data is transferred, set a<br>transfer information once again (except that a read skip is<br>performed).                                                                                                                             |

|       |             |               |            | 0: No interrupt has occurred                                                                                                                                                                                                                                                                                                       |

|       |             |               |            | 1: An interrupt has occurred                                                                                                                                                                                                                                                                                                       |

|       |             |               |            | [Clearing condition]                                                                                                                                                                                                                                                                                                               |

|       |             |               |            | When writing 0 after reading 1                                                                                                                                                                                                                                                                                                     |

| Note: | * Writing 0 | to this bit a | after reac | ling it as 1 clears the flag and is the only allowed way.                                                                                                                                                                                                                                                                          |

# 8.2.9 DTC Vector Base Register (DTCVBR)

DTCVBR is a 32-bit register that specifies the base address for vector table address calculation.

| Bit: 31                      | 30       | 29       | 28       | 27       | 26       | 25       | 24       | 23       | 22       | 21       | 20       | 19       | 18       | 17       | 16       |

|------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

|                              |          |          |          |          |          |          |          |          |          |          |          |          |          |          |          |

| Initial value: 0<br>R/W: R/W | 0<br>R/W |

| Bit: 15                      | 14       | 13       | 12       | 11       | 10       | 9        | 8        | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|                              |          |          |          | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        |

| Initial value: 0             | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |

| R/W: R/W                     | R/W      | R/W      | R/W      | R        | R        | R        | R        | R        | R        | R        | R        | R        | R        | R        | R        |

| Bit      | Bit Name | Initial<br>Value | R/W | Description                                               |

|----------|----------|------------------|-----|-----------------------------------------------------------|

| 31 to 12 |          |                  |     | Bits 11 to 0 are always read as 0. The write value should |

| 11 to 0  | —        | All 0            | R   | always be 0.                                              |

# 9.4.3 CSn Space Wait Control Register (CSnWCR) (n = 0 to 7)

CSnWCR specifies various wait cycles for memory access. The bit configuration of this register varies as shown below according to the memory type (TYPE2 to TYPE0) specified by the CSn space bus control register (CSnBCR). Specify CSnWCR before accessing the target area. Specify CSnBCR first, then specify CSnWCR.

CSnWCR is initialized to H'00000500 by a power-on reset and retains the value by a manual reset and in software standby mode.

# (1) Normal Space, SRAM with Byte Selection, MPX-I/O

• CS0WCR

| Bit:                   | 31       | 30       | 29       | 28       | 27       | 26       | 25       | 24       | 23       | 22       | 21       | 20       | 19       | 18       | 17       | 16       |

|------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

|                        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | BAS      | -        | -        | -        | -        |

| Initial value:<br>R/W: | 0<br>R/W |

| Bit:                   | 15       | 14       | 13       | 12       | 11       | 10       | 9        | 8        | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|                        | -        | -        | -        | SW       | [1:0]    |          | WR[3:0]  |          |          | WM       | -        | -        | -        | -        | HW       | [1:0]    |

| Initial value:         | 0        | 0        | 0        | 0        | 0        | 1        | 0        | 1        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |

| R/W:                   | R/W      | R        | R        | R        | R        | R/W      | R/W      |

|                        |          |          |          |          |          |          |          |          |          |          |          |          |          |          |          |          |

| Bit      | Bit Name | Initial<br>Value | R/W | Description                                                          |

|----------|----------|------------------|-----|----------------------------------------------------------------------|

| 31 to 21 | *        | All 0            | R/W | Reserved                                                             |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0. |

## (9) Relationship between Refresh Requests and Bus Cycles

If a refresh request occurs during bus cycle execution, the refresh cycle must wait for the bus cycle to be completed. If a refresh request occurs while the bus is released by the bus arbitration function, the refresh will not be executed until the bus mastership is acquired. This LSI has the  $\overline{\text{REFOUT}}$  pin to request the bus while waiting for refresh execution. For  $\overline{\text{REFOUT}}$  pin function selection, see section 22, Pin Function Controller (PFC). This LSI continues to assert  $\overline{\text{REFOUT}}$  (low level) until the bus is acquired.

On receiving the asserted  $\overline{\text{REFOUT}}$  signal, the external device must negate the  $\overline{\text{BREQ}}$  signal and return the bus. If the external bus does not return the bus for a period longer than the specified refresh interval, refresh cannot be executed and the SDRAM contents may be lost.

If a new refresh request occurs while waiting for the previous refresh request, the previous refresh request is deleted. To refresh correctly, a bus cycle longer than the refresh interval or the bus mastership occupation must be prevented from occurring.

If a bus mastership is requested during self-refresh, the bus will not be released until the refresh is completed.

|     |          | Initial |     |                                                                                     |

|-----|----------|---------|-----|-------------------------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                                         |

| 0   | I1AE     | 0       | R/W | Input Capture Enable                                                                |

|     |          |         |     | Specifies whether to include the TIOC1A pin in the TGRA_2 input capture conditions. |

|     |          |         |     | 0: Does not include the TIOC1A pin in the TGRA_2<br>input capture conditions        |

|     |          |         |     | 1: Includes the TIOC1A pin in the TGRA_2 input<br>capture conditions                |

#### **11.3.9** Timer Synchronous Clear Register S (TSYCRS)

TSYCRS is an 8-bit readable/writable register that specifies conditions for clearing TCNT\_3 and TCNT\_4 in the MTU2S in synchronization with the MTU2. The MTU2S has one TSYCRS in channel 3 but the MTU2 has no TSYCRS.

| Bit:           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----------------|------|------|------|------|------|------|------|------|

|                | CE0A | CE0B | CE0C | CE0D | CE1A | CE1B | CE2A | CE2B |

| Initial value: | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W:           | R/W  |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                          |

|-----|----------|------------------|-----|--------------------------------------------------------------------------------------|

| 7   | CE0A     | 0                | R/W | Clear Enable 0A                                                                      |

|     |          |                  |     | Enables or disables counter clearing when the TGFA flag of TSR_0 in the MTU2 is set. |

|     |          |                  |     | 0: Disables counter clearing by the TGFA flag in TSR_0                               |

|     |          |                  |     | 1: Enables counter clearing by the TGFA flag in TSR_0                                |

| 6   | CE0B     | 0                | R/W | Clear Enable 0B                                                                      |

|     |          |                  |     | Enables or disables counter clearing when the TGFB flag of TSR_0 in the MTU2 is set. |

|     |          |                  |     | 0: Disables counter clearing by the TGFB flag in TSR_0                               |

|     |          |                  |     | 1: Enables counter clearing by the TGFB flag in TSR_0                                |

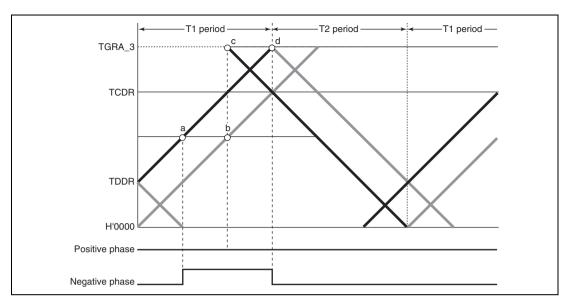

Figure 11.51 Example of Complementary PWM Mode 0% and 100% Waveform Output (3)

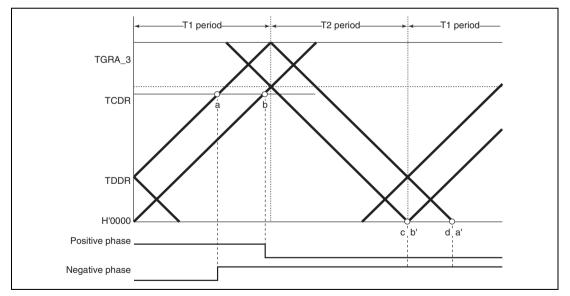

Figure 11.52 Example of Complementary PWM Mode 0% and 100% Waveform Output (4)

# 17.4.2 Operation in Asynchronous Mode

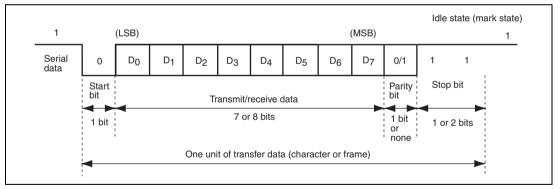

In asynchronous mode, each transmitted or received character begins with a start bit and ends with a stop bit. Serial communication is synchronized one character at a time.

The transmitting and receiving sections of the SCIF are independent, so full duplex communication is possible. The transmitter and receiver are 16-byte FIFO buffered, so data can be written and read while transmitting and receiving are in progress, enabling continuous transmitting and receiving.

Figure 17.2 shows the general format of asynchronous serial communication.

In asynchronous serial communication, the communication line is normally held in the mark (high) state. The SCIF monitors the line and starts serial communication when the line goes to the space (low) state, indicating a start bit. One serial character consists of a start bit (low), data (LSB first), parity bit (high or low), and stop bit (high), in that order.

When receiving in asynchronous mode, the SCIF synchronizes at the falling edge of the start bit. The SCIF samples each data bit on the eighth pulse of a clock with a frequency 16 times the bit rate. Receive data is latched at the center of each bit.

Figure 17.2 Example of Data Format in Asynchronous Communication (8-Bit Data with Parity and Two Stop Bits)

| Bit:           | 31    | 30    | 29    | 28    | 27    | 26    | 25    | 24    | 23    | 22    | 21    | 20    | 19    | 18    | 17    | 16    |

|----------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|                | SPD31 | SPD30 | SPD29 | SPD28 | SPD27 | SPD26 | SPD25 | SPD24 | SPD23 | SPD22 | SPD21 | SPD20 | SPD19 | SPD18 | SPD17 | SPD16 |

| Initial value: | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W:           | R/W   |

| Bit:           | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|                | SPD15 | SPD14 | SPD13 | SPD12 | SPD11 | SPD10 | SPD9  | SPD8  | SPD7  | SPD6  | SPD5  | SPD4  | SPD3  | SPD2  | SPD1  | SPD0  |

| Initial value: | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W:           | R/W   |

#### 18.3.8 RSPI Bit Rate Register (SPBR)

SPBR sets the bit rate in master mode. SPBR can be read from or written to by the CPU. If the contents of SPBR are changed by the CPU while the MSTR and SPE bits in the RSPI control register (SPCR) are 1 with the RSPI function in master mode enabled, operation cannot be guaranteed. When the RSPI is used in slave mode, the bit rate depends on the input clock regardless of the settings of SPBR and BRDV.

The bit rate is determined by combinations of SPBR settings and the bit settings in the BRDV1 and BRDV0 bits in the RSPI command registers (SPCMD0 to SPCMD7). The equation for calculating the bit rate is given below. In the equation, N denotes an SPBR setting (0, 1, 2, ..., 255), and n denotes bit settings in the bits BRDV1 and BRDV0 (0, 1, 2, 3).

Bit rate =

$$\frac{f(P\phi)}{2 \times (N+1) \times 2^n}$$

Table 18.3 shows examples of the relationship between the SPBR register and BRDV1 and BRDV0 bit settings.

| SPBR | BRDV[1:0] | Division | vision Bit Rate |             |             |             |             |  |  |  |  |  |

|------|-----------|----------|-----------------|-------------|-------------|-------------|-------------|--|--|--|--|--|

| (N)  | (n)       | Ratio    | Pφ = 16 MHz     | Pφ = 20 MHz | Pφ = 32 MHz | Pφ = 40 MHz | Pø = 50 MHz |  |  |  |  |  |

| 0    | 0         | 2        | 8.0 Mbps        | 10.0 Mbps   | _           | _           | _           |  |  |  |  |  |

| 1    | 0         | 4        | 4.0 Mbps        | 5.0 Mbps    | 8.0 Mbps    | 10.0 Mbps   | 12.5 Mbps   |  |  |  |  |  |

| 2    | 0         | 6        | 2.67 Mbps       | 3.3 Mbps    | 5.33 Mbps   | 6.67 Mbps   | 8.33 Mbps   |  |  |  |  |  |

| 3    | 0         | 8        | 2.0 Mbps        | 2.5 Mbps    | 4.0 Mbps    | 5.0 Mbps    | 6.25 Mbps   |  |  |  |  |  |

| 4    | 0         | 10       | 1.6 Mbps        | 2.0 Mbps    | 3.2 Mbps    | 4.0 Mbps    | 5.00 Mbps   |  |  |  |  |  |

| 5    | 0         | 12       | 1.33 Mbps       | 1.67 Mbps   | 2.67 Mbps   | 3.33 Mbps   | 4.17 Mbps   |  |  |  |  |  |

| 5    | 1         | 24       | 667 kbps        | 833 kbps    | 1.33 Mbps   | 1.67 Mbps   | 2.08 Mbps   |  |  |  |  |  |

Table 18.3

Relationship between SPBR and BRDV[1:0] Settings

# • Port B Control Register L2 (PBCRL2)

| Bit            | : 15 | 14  | 13      | 12  | 11 | 10  | 9       | 8   | 7 | 6   | 5       | 4   | 3 | 2   | 1       | 0   |

|----------------|------|-----|---------|-----|----|-----|---------|-----|---|-----|---------|-----|---|-----|---------|-----|

|                | -    | P   | B7MD[2: | 0]  | -  | Р   | B6MD[2: | 0]  | - | Р   | B5MD[2: | 0]  | - | P   | B4MD[2: | 0]  |

| Initial value: | 0    | 0   | 0       | 0*  | 0  | 0   | 0       | 0*  | 0 | 0   | 0       | 0*  | 0 | 0   | 0       | 0*  |

| R/W            | R    | R/W | R/W     | R/W | R  | R/W | R/W     | R/W | R | R/W | R/W     | R/W | R | R/W | R/W     | R/W |

Note: \* The initial value is 1 during the on-chip ROM disabled external extension mode.

| Bit      | Bit Name   | Initial<br>Value | R/W | Description                                                            |

|----------|------------|------------------|-----|------------------------------------------------------------------------|

| 15       | _          | 0                | R   | Reserved                                                               |

|          |            |                  |     | This bit is always read as 0. The write value should always be 0.      |

| 14 to 12 | PB7MD[2:0] | 000*             | R/W | PB7 Mode                                                               |

|          |            |                  |     | Select the function of the<br>PB7/A23/TEND0/IRQ7/TCLKC/SCK4/RD/WR pin. |

|          |            |                  |     | 000: PB7 I/O (port)                                                    |

|          |            |                  |     | 001: A23 output (BSC)                                                  |

|          |            |                  |     | 010: TEND0 output (DMAC)                                               |

|          |            |                  |     | 011: IRQ7 input (INTC)                                                 |

|          |            |                  |     | 100: TCLKC input (MTU2)                                                |

|          |            |                  |     | 101: Setting prohibited                                                |

|          |            |                  |     | 110: SCK4 I/O (SCI)                                                    |

|          |            |                  |     | 111: RD/WR output (BSC)                                                |

| 11       |            | 0                | R   | Reserved                                                               |

|          |            |                  |     | This bit is always read as 0. The write value should always be 0.      |

| 10 to 8  | PB6MD[2:0] | 000*             | R/W | PB6 Mode                                                               |

|          |            |                  |     | Select the function of the<br>PB6/A22/WAIT/IRQ6/TCLKD/TXD0 pin.        |

|          |            |                  |     | 000: PB6 I/O (port)                                                    |

|          |            |                  |     | 001: A22 output (BSC)                                                  |

|          |            |                  |     | 010: WAIT input (BSC)                                                  |

|          |            |                  |     | 011: IRQ6 input (INTC)                                                 |

|          |            |                  |     | 100: TCLKD input (MTU2)                                                |

|          |            |                  |     | 101: Setting prohibited                                                |

|          |            |                  |     | 110: TXD0 output (SCI)                                                 |

|          |            |                  |     | 111: Setting prohibited                                                |

# Section 24 USB Function Module (USB)

This LSI incorporates a USB function module (USB).

# 24.1 Features

• Automatic processing of USB protocol with on-chip protocol processor and transceiver conforming to USB2.0

Automatic processing of USB standard commands for endpoint 0 (some commands and class/vendor commands require decoding and processing by firmware)

- Transfer speed: Full-speed (12 Mbps)

- Endpoint configuration

| Endpoint Name | Abbreviation | Transfer Type | Maximum<br>Packet Size | FIFO Buffer<br>Capacity<br>(Byte) | DMA/DTC<br>Transfer |

|---------------|--------------|---------------|------------------------|-----------------------------------|---------------------|

| Endpoint 0    | EP0s         | Setup         | 8                      | 8                                 | —                   |

|               | EP0i         | Control IN    | 16                     | 16                                |                     |

|               | EP0o         | Control OUT   | 16                     | 16                                | —                   |

| Endpoint 1    | EP1          | Bulk OUT      | 64                     | 128                               | Possible            |

| Endpoint 2    | EP2          | Bulk IN       | 64                     | 128                               | Possible            |

| Endpoint 3    | EP3          | Interrupt IN  | 16                     | 16                                |                     |

| Endpoint 4    | EP4          | Bulk OUT      | 64                     | 128                               | Possible            |

| Endpoint 5    | EP5          | Bulk IN       | 64                     | 128                               | Possible            |

| Endpoint 6    | EP6          | Interrupt IN  | 16                     | 16                                |                     |

| Endpoint 7    | EP7          | Bulk OUT      | 64                     | 64                                |                     |

| Endpoint 8    | EP8          | Bulk IN       | 64                     | 64                                |                     |

| Endpoint 9    | EP9          | Interrupt IN  | 16                     | 16                                | _                   |

# 24.3.37 USB Trigger Register 1 (USBTRG1)

USBTRG1 is a write-only register that generates one-shot triggers to control the transmit/receive sequence for each endpoint. The read value of this register is undefined. Do not write a value to this register using the read value, such as a bit manipulation instruction.

| Bit:           | 7 | 6 | 5 | 4 | 3 | 2           | 1           | 0           |

|----------------|---|---|---|---|---|-------------|-------------|-------------|

|                | - | - | - | - | - | EP3<br>PKTE | EP2<br>PKTE | EP1<br>RDFN |

| Initial value: | 0 | 0 | 0 | 0 | 0 | 0           | 0           | 0           |

| R/W:           | - | - | - | - | - | W           | W           | W           |

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                             |

|--------|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 3 | _        | All 0            | —   | Reserved                                                                                                                                                                                                                                                                                |

|        |          |                  |     | The write value should always be 0.                                                                                                                                                                                                                                                     |

| 2      | EP3PKTE  | 0                | W   | EP3 Packet Enable                                                                                                                                                                                                                                                                       |

|        |          |                  |     | After one packet of data has been written to the<br>endpoint 3 transmit FIFO buffer, the transmit data is<br>fixed by writing 1 to this bit.                                                                                                                                            |

| 1      | EP2PKTE  | 0                | W   | EP2 Packet Enable                                                                                                                                                                                                                                                                       |

|        |          |                  |     | After one packet of data has been written to the<br>endpoint 2 transmit FIFO buffer, the transmit data is<br>fixed by writing 1 to this bit.                                                                                                                                            |

| 0      | EP1RDFN  | 0                | W   | EP1 Read Complete                                                                                                                                                                                                                                                                       |

|        |          |                  |     | Write 1 to this bit after one packet of data has been<br>read from the endpoint 1 receive FIFO buffer. The<br>endpoint 1 receive FIFO buffer has a dual-FIFO<br>configuration. Writing 1 to this bit initializes the FIFO<br>that was read, enabling the next packet to be<br>received. |

# 26.2.16 Receive Descriptor Fetch Address Register (RDFAR)

RDFAR stores the descriptor start address required when the E-DMAC fetches descriptor information from the receive descriptor. Which receive descriptor information is used for processing by the E-DMAC can be recognized by monitoring the addresses indicated by this register. The address that the E-DMAC is actually accessing during the descriptor fetch processing is not always equal to the value read from this register.

| Bit:                   | 31     | 30     | 29     | 28     | 27     | 26     | 25     | 24     | 23     | 22     | 21     | 20     | 19     | 18     | 17     | 16     |

|------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

|                        |        |        |        |        |        |        |        | RDFA[  | 31:16] |        |        |        |        |        |        |        |

| Initial value:<br>R/W: | 0<br>R |

| Bit:                   | 15     | 14     | 13     | 12     | 11     | 10     | 9      | 8      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|                        |        |        |        |        |        |        |        | RDFA[  | 15:0]  |        |        |        |        |        |        |        |

| Initial value:<br>R/W: | 0<br>R |

| Bit     | Bit Name   | Initial<br>Value | R/W | Description                                         |

|---------|------------|------------------|-----|-----------------------------------------------------|

| 31 to 0 | RDFA[31:0] | All 0            | R   | Receive Descriptor Fetch Address                    |

|         |            |                  |     | These bits can only be read. Writing is prohibited. |

# 30.5 Usage Notes

# 30.5.1 Current Consumption during Oscillation Settling Time

While waiting for clock oscillation to settle, the current consumption is increased.

#### **30.5.2** Notes on Writing to Registers

When writing to a register related to power-down modes by the CPU, after the CPU executes the write instruction, it then executes the subsequent instruction without waiting for the actual writing process to the register to finish.

To update the change made by writing to a register while executing the subsequent instruction, perform a dummy read to the same register between the instruction to write to the register and the subsequent instruction.

#### 30.5.3 Notes on Canceling Software Standby Mode with an IRQx Interrupt Request

When canceling software standby mode using an IRQx interrupt request, change the IRQ sense select setting of ICRx in a state in which no IRQx interrupt requests are generated and clear the IRQxF flag in IRQRRx to 0 by the automatic clearing function of the IRQx interrupt processing.

If the IRQxF flag in the IRQ interrupt request register x (IRQRRx) is 1, changing the setting of the IRQ sense select bits in the interrupt control register x (ICRx) or clearing the IRQxF flag in IRQRRx to 0 will clear the relevant IRQx interrupt request but will not clear the software standby cancellation request.

| Module<br>Name | Register Name                           | Abbreviation | Number<br>of Bits | Address    | Access<br>Size |

|----------------|-----------------------------------------|--------------|-------------------|------------|----------------|

| MTU2S          | Timer start register_5S                 | TSTR_5S      | 8                 | H'FFFE48B4 | 8              |

|                | Timer counter U_5S                      | TCNTU_5S     | 16                | H'FFFE4880 | 16, 32         |

|                | Timer counter V_5S                      | TCNTV_5S     | 16                | H'FFFE4890 | 16, 32         |

|                | Timer counter W_5S                      | TCNTW_5S     | 16                | H'FFFE48A0 | 16, 32         |

|                | Timer general register U_5S             | TGRU_5S      | 16                | H'FFFE4882 | 16             |

|                | Timer general register V_5S             | TGRV_5S      | 16                | H'FFFE4892 | 16             |

|                | Timer general register W_5S             | TGRW_5S      | 16                | H'FFFE48A2 | 16             |

|                | Timer compare match clear register S    | TCNTCMPCLRS  | 8                 | H'FFFE48B6 | 8              |

|                | Timer start register S                  | TSTRS        | 8                 | H'FFFE4A80 | 8, 16          |

|                | Timer synchronous register S            | TSYRS        | 8                 | H'FFFE4A81 | 8              |

|                | Timer read/write enable register S      | TRWERS       | 8                 | H'FFFE4A84 | 8              |

|                | Timer output master enable register S   | TOERS        | 8                 | H'FFFE4A0A | 8              |

|                | Timer output control register 1S        | TOCR1S       | 8                 | H'FFFE4A0E | 8, 16          |

|                | Timer output control register 2S        | TOCR2S       | 8                 | H'FFFE4A0F | 8              |

|                | Timer gate control register S           | TGCRS        | 8                 | H'FFFE4A0D | 8              |

|                | Timer cycle data register S             | TCDRS        | 16                | H'FFFE4A14 | 16, 32         |

|                | Timer dead time data register S         | TDDRS        | 16                | H'FFFE4A16 | 16             |

|                | Timer subcounter S                      | TCNTSS       | 16                | H'FFFE4A20 | 16, 32         |

|                | Timer cycle buffer register S           | TCBRS        | 16                | H'FFFE4A22 | 16             |

|                | Timer interrupt skipping set register S | TITCRS       | 8                 | H'FFFE4A30 | 8, 16          |

|                | Timer interrupt skipping counter S      | TITCNTS      | 8                 | H'FFFE4A31 | 8              |

|                | Timer buffer transfer set register S    | TBTERS       | 8                 | H'FFFE4A32 | 8              |

|                | Timer dead time enable register S       | TDERS        | 8                 | H'FFFE4A34 | 8              |

|                | Timer synchronous clear register S      | TSYCRS       | 8                 | H'FFFE4A50 | 8              |

|                | Timer waveform control register S       | TWCRS        | 8                 | H'FFFE4A60 | 8              |

|                | Timer output level buffer register S    | TOLBRS       | 8                 | H'FFFE4A36 | 8              |

| POE2           | Input level control/status register 1   | ICSR1        | 16                | H'FFFE5000 | 16             |

|                | Output level control/status register 1  | OCSR1        | 16                | H'FFFE5002 | 16             |

|                | Input level control/status register 2   | ICSR2        | 16                | H'FFFE5004 | 16             |

|                | Output level control/status register 2  | OCSR2        | 16                | H'FFFE5006 | 16             |

|                | Input level control/status register 3   | ICSR3        | 16                | H'FFFE5008 | 16             |

|                | Software port output enable register    | SPOER        | 8                 | H'FFFE500A | 8              |

# 33.3.5 DMAC Module Timing

# Table 33.9 DMAC Module Timing

Conditions:  $V_{cc}Q = PLLV_{cc} = DrV_{cc} = 3.0 \text{ to } 3.6 \text{ V}, AV_{cc} = AVREF = 4.5 \text{ to } 5.5 \text{ V},$   $V_{ss} = PLLV_{ss} = DrV_{ss} = AVREFVSS = AV_{ss} = 0 \text{ V},$  $Ta = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C} \text{ (Industrial specifications)}$

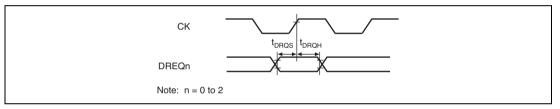

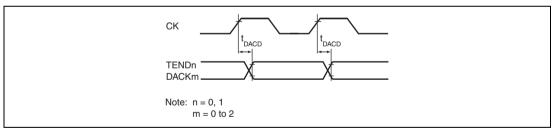

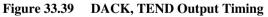

| Item                  | Symbol              | Min. | Max. | Unit | Figure       |

|-----------------------|---------------------|------|------|------|--------------|

| DREQ setup time       | t <sub>DRQS</sub>   | 20   | _    | ns   | Figure 33.38 |

| DREQ hold time        | t <sub>drqh</sub>   | 20   |      | _    |              |

| DACK, TEND delay time | $\mathbf{t}_{DACD}$ |      | 20   | _    | Figure 33.39 |

# 33.3.14 IIC3 Module Timing

# Table 33.18 I<sup>2</sup>C Bus Interface 3 Timing

Conditions:  $V_{cc}Q = PLLV_{cc} = DrV_{cc} = 3.0 \text{ to } 3.6 \text{ V}, AV_{cc} = AVREF = 4.5 \text{ to } 5.5 \text{ V},$   $V_{ss} = PLLV_{ss} = DrV_{ss} = AVREFVSS = AV_{ss} = 0 \text{ V},$  $Ta = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C} \text{ (Industrial specifications)}$

|                                                       |                   |                 | Specifications                          |      |                        |                                  |              |

|-------------------------------------------------------|-------------------|-----------------|-----------------------------------------|------|------------------------|----------------------------------|--------------|

| Item                                                  | Symbol            | Test Conditions | Min.                                    | Тур. | Max.                   | Unit                             | Figure       |

| SCL input cycle time                                  | t <sub>sc∟</sub>  |                 | $12 t_{pcyc}^{*1} + 600$                | _    | _                      | ns                               | Figure 33.55 |

| SCL input high pulse width                            | t <sub>sclH</sub> |                 | $3 t_{pcyc}^{*1} + 300$                 | _    | _                      | ns                               | _            |

| SCL input low pulse width                             | t <sub>scll</sub> |                 | $5 t_{pcyc}^{*1} + 300$                 | —    | _                      | ns                               | _            |

| SCL, SDA input rise time                              | t <sub>sr</sub>   |                 | _                                       | —    | 300                    | ns                               | _            |

| SCL, SDA input fall time                              | t <sub>sf</sub>   |                 | _                                       | _    | 300                    | ns                               | _            |

| SCL, SDA input spike pulse removal time* <sup>2</sup> | t <sub>sP</sub>   |                 | _                                       | —    | 1 t <sub>pcyc</sub> *1 | ns                               | _            |

| SDA input bus free time                               | t <sub>BUF</sub>  |                 | 5                                       | —    | _                      | t <sub>pcyc</sub> *1             | _            |

| Start condition input hold time                       | t <sub>stah</sub> |                 | 3                                       | —    | _                      | t <sub>pcyc</sub> *1             | _            |

| Retransmit start condition input setup time           | t <sub>stas</sub> |                 | 3                                       | —    | _                      | t <sub>pcyc</sub> *1             | _            |

| Stop condition input setup time                       | t <sub>stos</sub> |                 | 3                                       | —    | _                      | t <sub>pcyc</sub> * <sup>1</sup> | -            |

| Data input setup time                                 | t <sub>sdas</sub> |                 | 1 t <sub>pcyc</sub> * <sup>1</sup> + 20 | —    | _                      | ns                               | _            |

| Data input hold time                                  | t <sub>sdah</sub> |                 | 0                                       | _    | _                      | ns                               | _            |

| SCL, SDA capacitive load                              | Cb                |                 | 0                                       | _    | 400                    | pF                               | _            |

| SCL, SDA output fall time*3                           | t <sub>sf</sub>   |                 | 20 + 0.1 Cb                             | _    | 250                    | ns                               |              |

Notes: 1.  $t_{pcyc}$  indicates peripheral clock (P $\phi$ ) cycle.

2. Depends on the value of NF2CYC.

3. Indicates the I/O buffer characteristic.