#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | SH2A-FPU                                                                         |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SCI, SPI, USB                                |

| Peripherals                | DMA, PWM, WDT                                                                    |

| Number of I/O              | 112                                                                              |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | ·                                                                                |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x12b                                                                        |

| Oscillator Type            | External                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 176-LFBGA                                                                        |

| Supplier Device Package    | 176-LFBGA (13x13)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f72167bdbg-u1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|       | 16.3.3    | Transmit Shift Register (SCTSR)                                  | 768     |

|-------|-----------|------------------------------------------------------------------|---------|

|       | 16.3.4    | Transmit Data Register (SCTDR)                                   | 768     |

|       | 16.3.5    | Serial Mode Register (SCSMR)                                     |         |

|       | 16.3.6    | Serial Control Register (SCSCR)                                  | 772     |

|       | 16.3.7    | Serial Status Register (SCSSR)                                   | 775     |

|       | 16.3.8    | Serial Port Register (SCSPTR)                                    | 781     |

|       | 16.3.9    | Serial Direction Control Register (SCSDCR)                       |         |

|       | 16.3.10   | Bit Rate Register (SCBRR)                                        | 784     |

| 16.4  | Operation | n                                                                | 796     |

|       | 16.4.1    | Overview                                                         | 796     |

|       | 16.4.2    | Operation in Asynchronous Mode                                   | 798     |

|       | 16.4.3    | Clock Synchronous Mode                                           |         |

|       | 16.4.4    | Multiprocessor Communication Function                            | 818     |

|       | 16.4.5    | Multiprocessor Serial Data Transmission                          | 820     |

|       | 16.4.6    | Multiprocessor Serial Data Reception                             | 821     |

| 16.5  | SCI Inter | rrupt Sources and DTC                                            | 824     |

| 16.6  | Serial Po | ort Register (SCSPTR) and SCI Pins                               | 825     |

| 16.7  | Usage N   | otes                                                             | 827     |

|       | 16.7.1    | SCTDR Writing and TDRE Flag                                      | 827     |

|       | 16.7.2    | Multiple Receive Error Occurrence                                | 827     |

|       | 16.7.3    | Break Detection and Processing                                   | 828     |

|       | 16.7.4    | Sending a Break Signal                                           | 828     |

|       | 16.7.5    | Receive Data Sampling Timing and Receive Margin (Asynchronous Mo | de) 828 |

|       | 16.7.6    | Note on Using DTC                                                | 830     |

|       | 16.7.7    | Note on Using External Clock in Clock Synchronous Mode           | 830     |

|       | 16.7.8    | Module Standby Mode Setting                                      | 830     |

| Saati | on 17 So  | rial Communication Interface with FIFO (SCIF)                    | 921     |

|       |           | rial Communication Interface with FIFO (SCIF)                    |         |

| 17.1  |           | tput Pins                                                        |         |

| 17.2  | -         | 1                                                                |         |

| 17.3  | -         | Descriptions                                                     |         |

|       | 17.3.1    | Receive Shift Register (SCRSR)                                   |         |

|       | 17.3.2    | Receive FIFO Data Register (SCFRDR)                              |         |

|       | 17.3.3    | Transmit Shift Register (SCTSR)                                  |         |

|       | 17.3.4    | Transmit FIFO Data Register (SCFTDR)                             |         |

|       | 17.3.5    | Serial Mode Register (SCSMR)                                     |         |

|       | 17.3.6    | Serial Control Register (SCSCR)                                  |         |

|       | 17.3.7    | Serial Status Register (SCFSR)                                   |         |

|       | 17.3.8    | Bit Rate Register (SCBRR)                                        |         |

|       | 17.3.9    | FIFO Control Register (SCFCR)                                    |         |

|       | 17.3.10   | FIFO Data Count Register (SCFDR)                                 |         |

|       | 17.3.11   | Serial Port Register (SCSPTR)                                    | 866     |

| Origin of<br>Activation<br>Source | Activation<br>Source | Vector<br>Number | DTC Vector<br>Address<br>Offset | DTCE*1   | Transfer<br>Source         | Transfer<br>Destination    | Priority |

|-----------------------------------|----------------------|------------------|---------------------------------|----------|----------------------------|----------------------------|----------|

| RSPI                              | SPRI                 | 234              | H'000007A8                      | DTCERD5  | SPDR                       | Any location* <sup>2</sup> | High     |

|                                   | SPTI                 | 235              | H'000007AC                      | DTCERD4  | Any location* <sup>2</sup> | SPDR                       |          |

| SCI4                              | RXI4                 | 237              | H'000007B4                      | DTCERD3  | SCRDR_4                    | Any location* <sup>2</sup> | -        |

|                                   | TXI4                 | 238              | H'000007B8                      | DTCERD2  | Any location* <sup>2</sup> | SCTDR_4                    | -        |

| SCI0                              | RXI0                 | 241              | H'000007C4                      | DTCERE15 | SCRDR_0                    | Any location* <sup>2</sup> | -        |

|                                   | TXI0                 | 242              | H'000007C8                      | DTCERE14 | Any location* <sup>2</sup> | SCTDR_0                    | -        |

| SCI1                              | RXI1                 | 245              | H'000007D4                      | DTCERE13 | SCRDR_1                    | Any location* <sup>2</sup> | -        |

|                                   | TXI1                 | 246              | H'000007D8                      | DTCERE12 | Any location* <sup>2</sup> | SCTDR_1                    | -        |

| SCI2                              | RXI2                 | 249              | H'000007E4                      | DTCERE11 | SCRDR_2                    | Any location* <sup>2</sup> | -        |

|                                   | TXI2                 | 250              | H'000007E8                      | DTCERE10 | Any location* <sup>2</sup> | SCTDR_2                    | -        |

| SCIF3                             | RXI3                 | 254              | H'000007F8                      | DTCERE9  | SCFRDR_3                   | Any location* <sup>2</sup> | - ↓      |

|                                   | ТХІЗ                 | 255              | H'000007FC                      | DTCERE8  | Any location* <sup>2</sup> | SCFTDR_3                   | Low      |

Notes: 1. The DTCE bits with no corresponding interrupt are reserved, and the write value should always be 0.

2. An external memory, a memory-mapped external device, an on-chip memory, or an onchip peripheral module (except for DTC, BSC, UBC, AUD, FLASH, and DMAC) can be selected as the source or destination. Note that at least either the source or destination must be an on-chip peripheral module; transfer cannot be done among an external memory, a memory-mapped external device, and an on-chip memory.

3. Read to a message control field in mailbox 0 by using a block transfer mode or etc.

| <b>D</b> :4 | Dit Norma | Initial<br>Value | DAM | Description                                                                                                                                             |

|-------------|-----------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit         | Bit Name  |                  | R/W | Description                                                                                                                                             |

| 15 to 13    | _         | All 0            | R   | Reserved                                                                                                                                                |

|             |           |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                    |

| 12, 11      | SW[1:0]   | 00               | R/W | Number of Delay Cycles from Address, $\overline{CS4}$ Assertion to $\overline{RD}$ , $\overline{WRxx}$ Assertion                                        |

|             |           |                  |     | Specify the number of delay cycles from address and $\overline{\text{CS4}}$ assertion to $\overline{\text{RD}}$ and $\overline{\text{WRxx}}$ assertion. |

|             |           |                  |     | 00: 0.5 cycles                                                                                                                                          |

|             |           |                  |     | 01: 1.5 cycles                                                                                                                                          |

|             |           |                  |     | 10: 2.5 cycles                                                                                                                                          |

|             |           |                  |     | 11: 3.5 cycles                                                                                                                                          |

| 10 to 7     | WR[3:0]   | 1010             | R/W | Number of Read Access Wait Cycles                                                                                                                       |

|             |           |                  |     | Specify the number of cycles that are necessary for read access.                                                                                        |

|             |           |                  |     | 0000: No cycle                                                                                                                                          |

|             |           |                  |     | 0001: 1 cycle                                                                                                                                           |

|             |           |                  |     | 0010: 2 cycles                                                                                                                                          |

|             |           |                  |     | 0011: 3 cycles                                                                                                                                          |

|             |           |                  |     | 0100: 4 cycles                                                                                                                                          |

|             |           |                  |     | 0101: 5 cycles                                                                                                                                          |

|             |           |                  |     | 0110: 6 cycles                                                                                                                                          |

|             |           |                  |     | 0111: 8 cycles                                                                                                                                          |

|             |           |                  |     | 1000: 10 cycles                                                                                                                                         |

|             |           |                  |     | 1001: 12 cycles                                                                                                                                         |

|             |           |                  |     | 1010: 14 cycles                                                                                                                                         |

|             |           |                  |     | 1011: 18 cycles                                                                                                                                         |

|             |           |                  |     | 1100: 24 cycles                                                                                                                                         |

|             |           |                  |     | 1101: Reserved (setting prohibited)                                                                                                                     |

|             |           |                  |     | 1110: Reserved (setting prohibited)                                                                                                                     |

|             |           |                  |     | 1111: Reserved (setting prohibited)                                                                                                                     |

### (9) Relationship between Refresh Requests and Bus Cycles

If a refresh request occurs during bus cycle execution, the refresh cycle must wait for the bus cycle to be completed. If a refresh request occurs while the bus is released by the bus arbitration function, the refresh will not be executed until the bus mastership is acquired. This LSI has the  $\overline{\text{REFOUT}}$  pin to request the bus while waiting for refresh execution. For  $\overline{\text{REFOUT}}$  pin function selection, see section 22, Pin Function Controller (PFC). This LSI continues to assert  $\overline{\text{REFOUT}}$  (low level) until the bus is acquired.

On receiving the asserted  $\overline{\text{REFOUT}}$  signal, the external device must negate the  $\overline{\text{BREQ}}$  signal and return the bus. If the external bus does not return the bus for a period longer than the specified refresh interval, refresh cannot be executed and the SDRAM contents may be lost.

If a new refresh request occurs while waiting for the previous refresh request, the previous refresh request is deleted. To refresh correctly, a bus cycle longer than the refresh interval or the bus mastership occupation must be prevented from occurring.

If a bus mastership is requested during self-refresh, the bus will not be released until the refresh is completed.

### 10.3.3 DMA Transfer Count Registers (DMATCR)

The DMA transfer count registers (DMATCR) are 32-bit readable/writable registers that specify the number of DMA transfers. The transfer count is 1 when the setting is H'00000001, 16,777,215 when H'00FFFFFF is set, and 16,777,216 (the maximum) when H'00000000 is set. During a DMA transfer, these registers indicate the remaining transfer count.

The upper eight bits of DMATCR are always read as 0, and the write value should always be 0. To transfer data in 16 bytes, one 16-byte transfer (128 bits) counts one.

DMATCR is initialized to H'00000000 by a reset and retains the value in software standby mode and module standby mode.

| Bit:           | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|                | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

| Initial value: | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W:           | R   | R   | R   | R   | R   | R   | R   | R   | R/W |

|                |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Bit:           | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|                | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

| Initial value: | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W:           | R/W |

SH7214 Group, SH7216 Group

| Item                                          | Channel 0                                                                    | Channel 1                                         | Channel 2                                      | Channel 3                                         | Channel 4                                                                                                             | Channel 5                                   |

|-----------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------|------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| Phase counting mode                           | _                                                                            | $\checkmark$                                      | $\checkmark$                                   | _                                                 | _                                                                                                                     | _                                           |

| Buffer operation                              | $\checkmark$                                                                 | _                                                 | _                                              | $\checkmark$                                      | $\checkmark$                                                                                                          | _                                           |

| Dead time<br>compensation<br>counter function | _                                                                            | _                                                 | _                                              | _                                                 | _                                                                                                                     | $\checkmark$                                |

| DMAC activation                               | TGRA_0<br>compare<br>match or<br>input capture                               | TGRA_1<br>compare<br>match or<br>input<br>capture | TGRA_2<br>compare<br>match or<br>input capture | TGRA_3<br>compare<br>match or<br>input<br>capture | TGRA_4<br>compare<br>match or<br>input capture<br>and TCNT<br>overflow or<br>underflow                                | _                                           |

| DTC activation                                | TGR<br>compare<br>match or<br>input capture                                  | TGR<br>compare<br>match or<br>input<br>capture    | TGR<br>compare<br>match or<br>input capture    | TGR<br>compare<br>match or<br>input<br>capture    | TGR<br>compare<br>match or<br>input capture<br>or TCNT<br>overflow or<br>underflow                                    | TGR<br>compare<br>match or<br>input capture |

| A/D converter start<br>trigger                | TGRA_0<br>compare<br>match or<br>input capture<br>TGRE_0<br>compare<br>match | TGRA_1<br>compare<br>match or<br>input<br>capture | TGRA_2<br>compare<br>match or<br>input capture | TGRA_3<br>compare<br>match or<br>input<br>capture | TGRA_4<br>compare<br>match or<br>input capture<br>TCNT_4<br>underflow<br>(trough) in<br>complement<br>ary PWM<br>mode | _                                           |

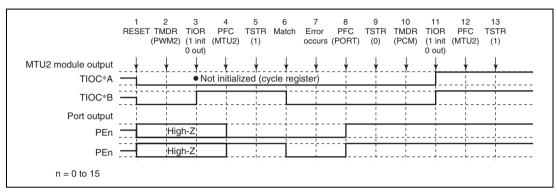

### (16) Operation when Error Occurs during PWM Mode 2 Operation, and Operation is Restarted in Phase Counting Mode

Figure 11.154 shows an explanatory diagram of the case where an error occurs in PWM mode 2 and operation is restarted in phase counting mode after re-setting.

1 to 9 are the same as in figure 11.151.

- 10. Set phase counting mode.

- 11. Initialize the pins with TIOR.

- 12. Set MTU2 output with the PFC.

- 13. Operation is restarted by TSTR.

| Bit | Bit Name | Initial<br>value | R/W | Description                                                |                                                                                                                                                                                                                                             |                                                        |  |  |  |  |

|-----|----------|------------------|-----|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|--|

| 2   | SPB1DT   | Undefined        | W   | Clock Port Data                                            | a in Serial Port                                                                                                                                                                                                                            |                                                        |  |  |  |  |

|     |          |                  |     | serial port. Out<br>(for details, refe<br>output is enable | Specifies the data output through the SCK pin in the serial port. Output should be enabled by the SPB1IO bi (for details, refer to the SPB1IO bit description). When output is enabled, the SPB1DT bit value is output through the SCK pin. |                                                        |  |  |  |  |

|     |          |                  |     | 0: Low level is                                            | output                                                                                                                                                                                                                                      |                                                        |  |  |  |  |

|     |          |                  |     | 1: High level is                                           | output                                                                                                                                                                                                                                      |                                                        |  |  |  |  |

| 1   | _        | 0                |     | Reserved                                                   |                                                                                                                                                                                                                                             |                                                        |  |  |  |  |

|     |          |                  |     | This bit is alway<br>always be 0.                          | ys read as 0. T                                                                                                                                                                                                                             | he write value should                                  |  |  |  |  |

| 0   | SPB0DT   | 1                | W   | Serial Port Brea                                           | ak Data                                                                                                                                                                                                                                     |                                                        |  |  |  |  |

|     |          |                  |     | Controls the TX                                            | (D pin by the T                                                                                                                                                                                                                             | E bit in SCSCR.                                        |  |  |  |  |

|     |          |                  |     |                                                            | ntroller (PFC).                                                                                                                                                                                                                             | ould be selected by the This is a read-only bit. The   |  |  |  |  |

|     |          |                  |     | TE bit setting<br>in SCSCR                                 | SPB0DT bit setting                                                                                                                                                                                                                          | TXD pin state                                          |  |  |  |  |

|     |          |                  |     | 0                                                          | 0                                                                                                                                                                                                                                           | Low output                                             |  |  |  |  |

|     |          |                  |     | 0 1 High output (initial state)                            |                                                                                                                                                                                                                                             |                                                        |  |  |  |  |

|     |          |                  |     | 1                                                          | *                                                                                                                                                                                                                                           | Transmit data output in accord with serial core logic. |  |  |  |  |

|     |          |                  | _   | Note: * Don't                                              | care                                                                                                                                                                                                                                        |                                                        |  |  |  |  |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                           |

|-----|----------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | RIE      | 0                | R/W | Receive Interrupt Enable                                                                                                                                                                                                                                                                                                                                                              |

|     |          |                  |     | Enables or disables the receive FIFO data full (RXI)<br>interrupts requested when the RDF flag or DR flag in<br>serial status register (SCFSR) is set to 1, receive-error<br>(ERI) interrupts requested when the ER flag in SCFSR<br>is set to 1, and break (BRI) interrupts requested when<br>the BRK flag in SCFSR or the ORER flag in line status<br>register (SCLSR) is set to 1. |

|     |          |                  |     | <ol> <li>Receive FIFO data full interrupt (RXI), receive-error<br/>interrupt (ERI), and break interrupt (BRI) requests<br/>are disabled</li> </ol>                                                                                                                                                                                                                                    |

|     |          |                  |     | <ol> <li>Receive FIFO data full interrupt (RXI), receive-error<br/>interrupt (ERI), and break interrupt (BRI) requests<br/>are enabled*</li> </ol>                                                                                                                                                                                                                                    |

|     |          |                  |     | Note: * RXI interrupt requests can be cleared by<br>reading the DR or RDF flag after it has been<br>set to 1, then clearing the flag to 0, or by<br>clearing RIE to 0. ERI or BRI interrupt requests<br>can be cleared by reading the ER, BR or<br>ORER flag after it has been set to 1, then<br>clearing the flag to 0, or by clearing RIE and<br>REIE to 0.                         |

| 5   | TE       | 0                | R/W | Transmit Enable                                                                                                                                                                                                                                                                                                                                                                       |

|     |          |                  |     | Enables or disables the serial transmitter.                                                                                                                                                                                                                                                                                                                                           |

|     |          |                  |     | 0: Transmitter disabled                                                                                                                                                                                                                                                                                                                                                               |

|     |          |                  |     | 1: Transmitter enabled*                                                                                                                                                                                                                                                                                                                                                               |

|     |          |                  |     | Note: * Serial transmission starts after writing of<br>transmit data into SCFTDR. Select the transmit<br>format in SCSMR and SCFCR and reset the<br>transmit FIFO before setting TE to 1.                                                                                                                                                                                             |

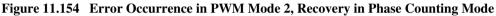

• Transmitting and Receiving Serial Data Simultaneously (Clocked Synchronous Mode) Figure 17.16 shows a sample flowchart for transmitting and receiving serial data simultaneously. Use the following procedure for the simultaneous transmission/reception of serial data, after enabling the SCIF for transmission/reception.

### 18.4.2 Controlling RSPI Pins

According to the MSTR, MODFEN and SPMS bits in the RSPI control register (SPCR) and the SPOM bit in the RSPI pin control register (SPPCR), the RSPI can automatically switch pin directions and output modes. Table 18.6 shows the relationship between pin states and bit settings.

| <b>Table 18.6</b> | Relationship between Pin States and Bit Settings |  |

|-------------------|--------------------------------------------------|--|

|-------------------|--------------------------------------------------|--|

|                                        |                            | Pin S            | State <sup>*1</sup>    |

|----------------------------------------|----------------------------|------------------|------------------------|

| Mode                                   | Pin                        | SPOM = 0         | SPOM = 1               |

| Single-master mode (SPI)               | RSPCK                      | CMOS output      | Open-drain output      |

| (MSTR = 1, MODFEN = 0,                 | SSL0 to SSL3               | CMOS output      | Open-drain output      |

| SPMS = 0)                              | MOSI                       | CMOS output      | Open-drain output      |

|                                        | MISO                       | Input            | Input                  |

| Multi-master mode (SPI)                | RSPCK* <sup>2</sup>        | CMOS output/Hi-Z | Open-drain output/Hi-Z |

| (MSTR = 1, MODFEN = 1,                 | SSL0                       | Input            | Input                  |

| SPMS = 0)                              | SSL1 to SSL3* <sup>2</sup> | CMOS output/Hi-Z | Open-drain output/Hi-Z |

|                                        | MOSI* <sup>2</sup>         | CMOS output/Hi-Z | Open-drain output/Hi-Z |

|                                        | MISO                       | Input            | Input                  |

| Slave mode (SPI)                       | RSPCK                      | Input            | Input                  |

| (MSTR = 0, SPMS = 0)                   | SSL0                       | Input            | Input                  |

|                                        | SSL1 to SSL3               | Hi-Z             | Hi-Z                   |

|                                        | MOSI                       | Input            | Input                  |

|                                        | MISO* <sup>3</sup>         | CMOS output/Hi-Z | Open-drain output/Hi-Z |

| Master (clock                          | RSPCK                      | CMOS output      | Open-drain output      |

| synchronous)                           | SSL0 to SSL3*4             | Hi-Z             | Hi-Z                   |

| (MSTR = 1, MODFEN = 0, SPMS = 1)       | MOSI                       | CMOS output      | Open-drain output      |

| ······································ | MISO                       | Input            | Input                  |

|                                        | 0                          |                  |                        |

# 21.4 Application Note

### 21.4.1 Test Mode Settings

The RCAN-ET has various test modes. The register TST[2:0] (MCR[10:8]) is used to select the RCAN-ET test mode. The default (initialised) settings allow RCAN-ET to operate in Normal mode. The following table is examples for test modes.

Test Mode can be selected only while in configuration mode. The user must then exit the configuration mode (ensuring BCR0/BCR1 is set) in order to run the selected test mode.

| Bit10:<br>TST2 | Bit9:<br>TST1 | Bit8:<br>TST0 | Description                          |  |  |  |  |

|----------------|---------------|---------------|--------------------------------------|--|--|--|--|

| 0              | 0             | 0             | Normal Mode (initial value)          |  |  |  |  |

| 0              | 0             | 1             | Listen-Only Mode (Receive-Only Mode) |  |  |  |  |

| 0              | 1             | 0             | If Test Mode 1 (External)            |  |  |  |  |

| 0              | 1             | 1             | Self Test Mode 2 (Internal)          |  |  |  |  |

| 1              | 0             | 0             | Write Error Counter                  |  |  |  |  |

| 1              | 0             | 1             | Error Passive Mode                   |  |  |  |  |

| 1              | 1             | 0             | Setting prohibited                   |  |  |  |  |

| 1              | 1             | 1             | Setting prohibited                   |  |  |  |  |

Normal Mode: RCAN-ET operates in the normal mode.

- Listen-Only Mode: ISO-11898 requires this mode for baud rate detection. The Error Counters are cleared and disabled so that the TEC/REC does not increase the values, and the Tx Output is disabled so that RCAN-ET does not generate error frames or acknowledgment bits. IRR13 is set when a message error occurs.

- Self Test Mode 1: RCAN-ET generates its own Acknowledge bit, and can store its own messages into a reception mailbox (if required). The Rx/Tx pins must be connected to the CAN bus.

- Self Test Mode 2: RCAN-ET generates its own Acknowledge bit, and can store its own messages into a reception mailbox (if required). The Rx/Tx pins do not need to be connected to the CAN bus or any external devices, as the internal Tx is looped back to the internal Rx. Tx pin outputs only recessive bits and Rx pin is disabled.

# Table 22.3 Multiplexed Pins (Port C)

| Port | Function 1<br>(Related<br>Module) | Function 2<br>(Related<br>Module) | Function 3<br>(Related<br>Module) | Function 4<br>(Related<br>Module) | Function 5<br>(Related<br>Module) | Function 6<br>(Related<br>Module) | Function 7<br>(Related<br>Module) | Function 8<br>(Related<br>Module) |

|------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|

| С    | PC15 I/O<br>(Port)                | A15 output<br>(BSC)               | —                                 | IRQ2 input<br>(INTC)              | TCLKD input<br>(MTU2)             | _                                 | _                                 | _                                 |

|      | PC14 I/O<br>(Port)                | A14 output<br>(BSC)               | _                                 | IRQ1 input<br>(INTC)              | TCLKC input<br>(MTU2)             | —                                 | _                                 | _                                 |

|      | PC13 I/O<br>(Port)                | A13 output<br>(BSC)               | _                                 | IRQ0 input<br>(INTC)              | TCLKB input<br>(MTU2)             | _                                 | _                                 | _                                 |

|      | PC12 I/O<br>(Port)                | A12 output<br>(BSC)               | _                                 | _                                 | TCLKA input<br>(MTU2)             | _                                 | _                                 | _                                 |

|      | PC11 I/O<br>(Port)                | A11 output<br>(BSC)               | _                                 | _                                 | TIOC1B I/O<br>(MTU2)              | CTx0 output<br>(RCAN-ET)          | TXD0 output<br>(SCI)              | _                                 |

|      | PC10 I/O<br>(Port)                | A10 output<br>(BSC)               | _                                 | _                                 | TIOC1A I/O<br>(MTU2)              | CRx0 input<br>(RCAN-ET)           | RXD0 input<br>(SCI)               | _                                 |

|      | PC9 I/O<br>(Port)                 | A9 output<br>(BSC)                | _                                 | _                                 | _                                 | CTx0 output<br>(RCAN-ET)          | TXD0 output<br>(SCI)              | _                                 |

|      | PC8 I/O<br>(Port)                 | A8 output<br>(BSC)                | _                                 | _                                 | _                                 | CRx0 input<br>(RCAN-ET)           | RXD0 input<br>(SCI)               | _                                 |

|      | PC7 I/O<br>(Port)                 | A7 output<br>(BSC)                | _                                 | _                                 | _                                 | —                                 | _                                 | _                                 |

|      | PC6 I/O<br>(Port)                 | A6 output<br>(BSC)                | _                                 | _                                 | —                                 | _                                 | _                                 | _                                 |

|      | PC5 I/O<br>(Port)                 | A5 output<br>(BSC)                | _                                 | _                                 | _                                 | _                                 | _                                 | _                                 |

|      | PC4 I/O<br>(Port)                 | A4 output<br>(BSC)                | _                                 | _                                 | _                                 | _                                 | _                                 | _                                 |

|      | PC3 I/O<br>(Port)                 | A3 output<br>(BSC)                | _                                 | _                                 | _                                 | _                                 | _                                 | _                                 |

|      | PC2 I/O<br>(Port)                 | A2 output<br>(BSC)                | _                                 | _                                 | _                                 | _                                 | _                                 | _                                 |

|      | PC1 I/O<br>(Port)                 | A1 output<br>(BSC)                | _                                 | _                                 | _                                 | _                                 | _                                 | _                                 |

|      | PC0 I/O<br>(Port)                 | A0 output<br>(BSC)                | _                                 | IRQ4 input<br>(INTC)              | _                                 | POE0 input<br>(POE2)              | _                                 | _                                 |

| Register | Bit | Transfer<br>Mode              | Interrupt<br>Source | Description                  | Interrupt<br>Request<br>Signal | DMAC/DTC<br>Activation |  |  |

|----------|-----|-------------------------------|---------------------|------------------------------|--------------------------------|------------------------|--|--|

| USBIFR2  | 0   | Bulk_out<br>transfer<br>(EP1) | EP1FULL             | EP1FULL EP1FIFO full USI0 or |                                |                        |  |  |

|          | 1   | Bulk_in                       | EP2ALLEMP           | EP2FIFO all empty            | USI0 or USI1                   | ×                      |  |  |

|          | 2   | transfer<br>_ (EP2)           | EP2EMPTY            | EP2FIFO empty                | USI0 or USI1                   | USBTXI0                |  |  |

|          | 3   | _(LI Z)                       | EP2TR               | EP2 transfer request         | USI0 or USI1                   | ×                      |  |  |

|          | 4   | Interrupt_in                  | EP3TS               | EP3 transmit complete        | USI0 or USI1                   | ×                      |  |  |

|          | 5   | transfer<br>(EP3)             | EP3TR               | EP3 transfer request         | USI0 or USI1                   | ×                      |  |  |

|          | 6   | —                             | Reserved            | —                            | —                              | _                      |  |  |

|          | 7   | _                             | Reserved            | _                            |                                | _                      |  |  |

| USBIFR3  | 0   | Bulk_out<br>transfer<br>(EP4) | EP4FULL             | EP4FIFO full                 | USI0 or USI1                   | USBRXI1                |  |  |

|          | 1   | Bulk_in                       | EP5ALLEMP           | EP5FIFO all empty            | USI0 or USI1                   | ×                      |  |  |

|          | 2   | transfer<br>(EP5)             | EP5EMPTY            | EP5FIFO empty                | USI0 or USI1                   | USBTXI1                |  |  |

|          | 3   | = (ĽF3)                       | EP5TR               | EP5 transfer request         | USI0 or USI1                   | ×                      |  |  |

|          | 4   | Interrupt_in                  | EP6TS               | EP6 transmit complete        | USI0 or USI1                   | ×                      |  |  |

|          | 5   | transfer<br>(EP6)             | EP6TR               | EP6 transfer request         | USI0 or USI1                   | ×                      |  |  |

|          | 6   | _                             | Reserved            | _                            |                                | _                      |  |  |

|          | 7   | _                             | Reserved            | _                            |                                | _                      |  |  |

| USBIFR4  | 0   | Bulk_out<br>transfer<br>(EP7) | EP7FULL             | EP7FIFO full                 | USI0 or USI1                   | ×                      |  |  |

|          | 1   | _                             | Reserved            | _                            |                                | _                      |  |  |

|          | 2   | Bulk_in                       | EP8EMPTY            | EP8FIFO empty                | USI0 or USI1                   | ×                      |  |  |

|          | 3   | transfer<br>(EP8)             | EP8TR               | EP8 transfer request         | USI0 or USI1                   | ×                      |  |  |

|          | 4   | Interrupt_in                  | EP9TS               | EP9 transmit complete        | USI0 or USI1                   | ×                      |  |  |

|          | 5   | transfer<br>(EP9)             | EP9TR               | EP9 transfer request         | USI0 or USI1                   | ×                      |  |  |

|          | 6   | _                             | Reserved            | _                            | _                              | _                      |  |  |

|          | 7   | _                             | Reserved            | _                            | _                              | _                      |  |  |

Note: \* EP0-related interrupt sources must be assigned to the same interrupt request signal.

### 25.3.6 MAC Address Low Register (MALR)

MALR is a 32-bit readable/writable register that specifies the lower 16 bits of 48-bit MAC address. This register is normally set in the initialization process after a reset. The MAC address setting must not be changed while the transmitting and receiving functions are enabled. Reset the EtherC and E-DMAC with the SWR bit in EDMR of the E-DMAC, and then set the MAC address again.

| Bit:           | 31  | 30       | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|----------------|-----|----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|                | -   | -        | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

| Initial value: | 0   | 0        | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W:           | R   | R        | R   | R   | R   | R   | R   | R   | R   | R   | R   | R   | R   | R   | R   | R   |

|                |     |          |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Bit:           | 15  | 14       | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|                |     | MA[15:0] |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Initial value: | 0   | 0        | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W:           | R/W | R/W      | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

|          |          | Initial |     |                                                                                     |

|----------|----------|---------|-----|-------------------------------------------------------------------------------------|

| Bit      | Bit Name | Value   | R/W | Description                                                                         |

| 31 to 16 | _        | All 0   | R   | Reserved                                                                            |

|          |          |         |     | These bits are always read as 0. The write value should always be 0.                |

| 15 to 0  | MA[15:0] | All 0   | R/W | MAC Address Bits 15 to 0                                                            |

|          |          |         |     | These bits are used to set the lower 16 bits of the MAC address.                    |

|          |          |         |     | If the MAC address is 01-23-45-67-89-AB (hexadecimal), set H'89AB in this register. |

### 25.3.20 Automatic PAUSE Frame Register (APR)

APR is used to set the TIME parameter value of an automatic PAUSE frame. When an automatic PAUSE frame is transmitted, the value set in this register is used as the TIME parameter of the PAUSE frame.

| Bit:                   | 31       | 30       | 29       | 28       | 27       | 26       | 25       | 24       | 23       | 22       | 21       | 20       | 19       | 18       | 17       | 16       |

|------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

|                        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        |

| Initial value:<br>R/W: | 0<br>R   |

| Bit:                   | 15       | 14       | 13       | 12       | 11       | 10       | 9        | 8        | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|                        |          |          |          |          |          |          |          | AP[1     | 5:0]     |          |          |          |          |          |          |          |

| Initial value:<br>R/W: | 0<br>R/W |

| Bit      | Bit Name | Initial<br>Value | R/W | Description                                                                                                 |

|----------|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------|

| 31 to 16 | _        | All 0            | R   | Reserved                                                                                                    |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0.                                        |

| 15 to 0  | AP[15:0] | All 0            | R/W | Automatic PAUSE                                                                                             |

|          |          |                  |     | These bits set the TIME parameter value of an automatic PAUSE frame. One bit is equivalent to 512-bit time. |

|        |                      | Initial |     |                                                                                    |

|--------|----------------------|---------|-----|------------------------------------------------------------------------------------|

| Bit    | Bit Name             | Value   | R/W | Description                                                                        |

| 7      | USBSEL*1             | 1       | R/W | USB Clock Select                                                                   |

|        |                      |         |     | Selects the on-chip CPG or the USB oscillator as the source of the USB clock.      |

|        |                      |         |     | 0: On-chip CPG                                                                     |

|        |                      |         |     | 1: USB oscillator                                                                  |

| 6      | MSTP66* <sup>2</sup> | 1       | R/W | Module Stop 66                                                                     |

|        |                      |         |     | When the MSTP66 bit is set to 1, the supply of the clock to the USB is halted.     |

|        |                      |         |     | 0: USB runs.                                                                       |

|        |                      |         |     | 1: Clock supply to USB halted.                                                     |

| 5      | USBCLK               | 0       | R/W | USB Oscillator Stop                                                                |

|        |                      |         |     | When the USBCLK bit is set to 1, the oscillator dedicated for the USB stops.       |

|        |                      |         |     | 0: USB oscillator operates.                                                        |

|        |                      |         |     | 1: USB oscillator stops.                                                           |

| 4      | MSTP64               | 1       | R/W | Module Stop 64                                                                     |

|        |                      |         |     | When the MSTP64 bit is set to 1, the supply of the clock to the RCAN-ET is halted. |

|        |                      |         |     | 0: RCAN-ET runs.                                                                   |

|        |                      |         |     | 1: Clock supply to RCAN-ET halted.                                                 |

| 3 to 0 |                      | All 1   | R   | Reserved                                                                           |

|        |                      |         |     | These bits are always read as 1. The write value should always be 1.               |

Notes: When using the USB, Follow the notes shown below. Otherwise the clock will not be generated correctly so that USB can be operated improperly.

1. When selecting the on-chip CPG, set the frequency of the input clock to 12MHz.

2. When using the USB, set the frequency of the peripheral clock (P $\phi$ ) to 13 MHz or more.

## 33.3.12 RSPI Timing

### Table 33.16 SPI Timing

Conditions:  $V_{cc}Q = PLLV_{cc} = DrV_{cc} = 3.0 \text{ to } 3.6 \text{ V}, AV_{cc} = AVREF = 4.5 \text{ to } 5.5 \text{ V},$   $V_{ss} = PLLV_{ss} = DrV_{ss} = AVREFV_{ss} = AV_{ss} = 0 \text{ V},$  $Ta = -40^{\circ}\text{C to } +85^{\circ}\text{C}$  (Industrial specifications)

|                                    |        |                            | Min.                                                                 | Тур. | Max.                                                                           | Unit               | Figure        |

|------------------------------------|--------|----------------------------|----------------------------------------------------------------------|------|--------------------------------------------------------------------------------|--------------------|---------------|

| RSPCK clock cycle*1                | Master | t <sub>sPcyc</sub>         | 2                                                                    |      | 4096                                                                           | t <sub>Pcyc</sub>  | Figure 33.49  |

|                                    | Slave  | _                          | 8                                                                    | _    | 4096                                                                           | -                  |               |

| RSPCK clock cycle high pulse width | Master | t <sub>spckwh</sub>        | $(t_{_{SPCyc}} - t_{_{SPCKR}} - t_{_{SPCKF}})/2 - 3$                 |      |                                                                                | ns                 |               |

|                                    | Slave  | _                          | (t <sub>spcyc</sub> – t <sub>spckr</sub> –<br>t <sub>spckr</sub> )/2 | _    | _                                                                              | -                  |               |

| RSPCK clock cycle low pulse width  | Master | t <sub>spckwl</sub>        | $(t_{_{SPCyc}} - t_{_{SPCKR}} - t_{_{SPCKF}})/2 - 3$                 |      | _                                                                              | ns                 |               |

|                                    | Slave  | _                          | $(t_{_{SPCyc}} - t_{_{SPCKR}} - t_{_{SPCKF}})/2$                     | ·    | _                                                                              | -                  |               |

| RSPCK clock rise/fall              | Master | t <sub>spckr</sub> ,       | _                                                                    |      | 5                                                                              | ns                 |               |

| time* <sup>2</sup>                 | Slave  | t <sub>spckf</sub>         | _                                                                    |      | 1                                                                              | t <sub>Pcyc</sub>  |               |

| Data input setup time              | Master | t <sub>su</sub>            | 25                                                                   | _    | _                                                                              | ns                 | Figures 33.50 |

|                                    | Slave  | _                          | $20-2\times t_{_{Pcyc}}$                                             | _    | _                                                                              | _                  | to 33.53      |

| Data input hold time               | Master | t <sub>H</sub>             | 0                                                                    | _    | _                                                                              | ns                 |               |

|                                    | Slave  | _                          | $20 + 2 \times t_{_{Pcyc}}$                                          |      | _                                                                              | _                  |               |

| SSL setup time                     | Master | $\mathbf{t}_{\text{LEAD}}$ | 1                                                                    |      | 8                                                                              | $t_{_{\rm SPcyc}}$ |               |

|                                    | Slave  | _                          | 4                                                                    | _    | _                                                                              | t <sub>Pcyc</sub>  |               |

| SSL hold time                      | Master | t <sub>LAG</sub>           | 1                                                                    |      | 8                                                                              | $t_{_{\rm SPcyc}}$ |               |

|                                    | Slave  | _                          | 4                                                                    |      | _                                                                              | t <sub>Pcyc</sub>  |               |

| Data output delay time             | Master | t <sub>op</sub>            | _                                                                    | _    | 10                                                                             | ns                 |               |

|                                    | Slave  | —                          |                                                                      |      | $3 \times t_{_{Pcyc}} + 15$                                                    | -                  |               |

| Data output hold time              | Master | t <sub>он</sub>            | 0                                                                    |      | _                                                                              | ns                 |               |

|                                    | Slave  | _                          | 0                                                                    | _    | _                                                                              | _                  |               |

| Continuous transmission delay time | Master | t <sub>tD</sub>            | $t_{_{SPcyc}} + 2 \times t_{_{Pcyc}}$                                |      | $\begin{array}{l} 8 \times t_{_{SPcyc}} + 2 \\ \times t_{_{Pcyc}} \end{array}$ | ns                 |               |

|                                    | Slave  |                            | $4 \times t_{_{\text{Pcyc}}}$                                        | _    | _                                                                              | _                  |               |

|       | Pin Function                                                                                                  |   |     |                       |                       | Pin        | State                                                                        |     |                              |                                 |                         |

|-------|---------------------------------------------------------------------------------------------------------------|---|-----|-----------------------|-----------------------|------------|------------------------------------------------------------------------------|-----|------------------------------|---------------------------------|-------------------------|

|       |                                                                                                               |   | I   | Reset State           |                       | Power-Dowr | n State                                                                      |     |                              |                                 |                         |

|       |                                                                                                               |   | Pow | ver-On                |                       |            |                                                                              |     |                              |                                 |                         |

| Туре  | Pin Name                                                                                                      |   |     | Expansion<br>with ROM | Single<br>Chip Manual |            | Software<br>Standby Sleep                                                    |     | Bus<br>Mastership<br>Release | Oscillation<br>Stop<br>Detected | POE<br>Function<br>Used |

| MTU2  | TIOC1B (PE5),<br>TIOC2A (PE6)                                                                                 | Z |     |                       |                       | I/O        | Z<br>(MZIZEL in<br>HCPCR = 0)<br>K* <sup>1</sup><br>(MZIZEL in<br>HCPCR = 1) | I/O | I/O                          | I/O* <sup>8</sup>               | I/O                     |

|       | TIOC1B (PC11),<br>TIOC2A (PB0)                                                                                |   |     | Z                     |                       | I/O        | K*1                                                                          | I/O | I/O                          | I/O                             | I/O                     |

|       | TIOC2B                                                                                                        |   |     | Z                     |                       | I/O        | K*1                                                                          | I/O | I/O                          | I/O                             | I/O                     |

|       | TIOC3A,<br>TIOC3C                                                                                             |   |     | Z                     |                       | I/O        | <b>K</b> * <sup>1</sup>                                                      | I/O | I/O                          | I/O                             | I/O                     |

|       | TIOC3B,<br>TIOC3D                                                                                             |   |     | Z                     |                       | I/O        | Z<br>(MZIZEH in<br>HCPCR = 0)<br>K* <sup>1</sup><br>(MZIZEH in<br>HCPCR = 1) | I/O | I/O                          | I/O* <sup>7</sup>               | Z                       |

|       | TIOC4A,<br>TIOC4B,<br>TIOC4C,<br>TIOC4D                                                                       |   |     | Z                     |                       | I/O        | Z<br>(MZIZEH in<br>HCPCR = 0)<br>K* <sup>1</sup><br>(MZIZEH in<br>HCPCR = 1) | I/O | I/O                          | I/O∗ <sup>7</sup>               | Z                       |

|       | TIC5U,<br>TIC5V,<br>TIC5W                                                                                     |   |     | Z                     |                       | I          | Z                                                                            | I   | I                            | I                               | I                       |

| MTU2S | TIOC3AS,<br>TIOC3CS                                                                                           |   |     | Z                     |                       | I/O        | K*1                                                                          | I/O | I/O                          | I/O                             | I/O                     |

|       | TIOC3BS (PD10),<br>TIOC3DS (PD11),<br>TIOC4AS (PD12),<br>TIOC4BS (PD13),<br>TIOC4CS (PD13),<br>TIOC4CS (PD15) |   |     | Z                     |                       | 1/0        | Z (MZIZDL in<br>HCPCR = 0)<br>K* <sup>1</sup><br>(MZIZDL in<br>HCPCR = 1)    | I/O | I/O                          | I/O* <sup>€</sup>               | Z                       |

| Item                                                                                                                                                                                                             | Page             | Revision (See Manua             | Il for Details)                                                                                                                                                                                                                               |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Figure 9.37 Basic<br>Access Timing for<br>SRAM with Byte<br>Selection (BAS = 0)<br>to<br>Figure 9.39 Wait Timing<br>for SRAM with Byte<br>Selection (BAS = 1)<br>(SW[1:0] = 01, WR[3:0]<br>= 0001, HW[1:0] = 01) | 372<br>to<br>374 | Amended                         | $Read \begin{cases} RD/WR \\ RD \\ D31 \text{ to } D0 \\ RD/WR \\ RD \\ D31 \text{ to } D0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 $                                                                                                     |  |  |  |

| Figure 9.40 Example of<br>Connection with 16-Bit<br>Data-Width SRAM with<br>Byte Selection                                                                                                                       | 375              | Figure replaced                 |                                                                                                                                                                                                                                               |  |  |  |

| Figure 9.41 Example<br>of Connection with 16-<br>Bit Data-Width SRAM<br>with Byte Selection                                                                                                                      | 376              | Figure added                    |                                                                                                                                                                                                                                               |  |  |  |

| Table 9.21 Conditions                                                                                                                                                                                            | 380              | Amended and added               |                                                                                                                                                                                                                                               |  |  |  |

| for Determining Number                                                                                                                                                                                           |                  | No. Condition                   | Description                                                                                                                                                                                                                                   |  |  |  |

| of Idle Cycles                                                                                                                                                                                                   |                  | (5) Read data<br>transfer cycle | One idle cycle is inserted after a read<br>access is completed. This idle cycle is<br>not generated for the first or middle<br>cycles in divided access cycles. This is<br>neither generated when the HW[1:0] bits<br>in CSnWCR are not B'00. |  |  |  |

|                                                                                                                                                                                                                  |                  |                                 | for consecutive read operations when the data                                                                                                                                                                                                 |  |  |  |

|                                                                                                                                                                                                                  |                  | read are stored i               | n separate registers.                                                                                                                                                                                                                         |  |  |  |