Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Active                                                     |

| Core Processor             | 56800E                                                     |

| Core Size                  | 16-Bit                                                     |

| Speed                      | 40MHz                                                      |

| Connectivity               | EBI/EMI, SCI, SPI                                          |

| Peripherals                | POR, PWM, WDT                                              |

| Number of I/O              | 76                                                         |

| Program Memory Size        | 512KB (256K x 16)                                          |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 16K x 16                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.25V ~ 3.6V                                               |

| Data Converters            | A/D 16x12b                                                 |

| Oscillator Type            | External                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 160-LQFP                                                   |

| Supplier Device Package    | 160-LQFP (24x24)                                           |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc56f8167vpye |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Part 2 Signal/Connection Descriptions

# 2.1 Introduction

The input and output signals of the 56F8367 and 56F8167 are organized into functional groups, as detailed in **Table 2-1** and as illustrated in **Figure 2-1**. In **Table 2-2**, each table row describes the signal or signals present on a pin.

| Everetianel Ocean                                        | Number of Pins in Package |         |  |

|----------------------------------------------------------|---------------------------|---------|--|

| Functional Group                                         | 56F8367                   | 56F8167 |  |

| Power (V <sub>DD</sub> or V <sub>DDA</sub> )             | 9                         | 9       |  |

| Power Option Control                                     | 1                         | 1       |  |

| Ground (V <sub>SS</sub> or V <sub>SSA</sub> )            | 7                         | 7       |  |

| Supply Capacitors <sup>1</sup> & V <sub>PP</sub>         | 6                         | 6       |  |

| PLL and Clock                                            | 4                         | 4       |  |

| Address Bus                                              | 24                        | 24      |  |

| Data Bus                                                 | 16                        | 16      |  |

| Bus Control                                              | 10                        | 10      |  |

| Interrupt and Program Control                            | 6                         | 6       |  |

| Pulse Width Modulator (PWM) Ports                        | 26                        | 13      |  |

| Serial Peripheral Interface (SPI) Port 0                 | 4                         | 4       |  |

| Serial Peripheral Interface (SPI) Port 1                 | —                         | 4       |  |

| Quadrature Decoder Port 0 <sup>2</sup>                   | 4                         | 4       |  |

| Quadrature Decoder Port 1 <sup>3</sup>                   | 4                         | _       |  |

| Serial Communications Interface (SCI) Ports <sup>2</sup> | 4                         | 4       |  |

| CAN Ports                                                | 2                         | —       |  |

| Analog to Digital Converter (ADC) Ports                  | 21                        | 21      |  |

| Timer Module Ports                                       | 6                         | 2       |  |

| JTAG/Enhanced On-Chip Emulation (EOnCE)                  | 5                         | 5       |  |

| Temperature Sense                                        | 1                         | —       |  |

| Dedicated GPIO                                           | —                         | 7       |  |

1. If the on-chip regulator is disabled, the V<sub>CAP</sub> pins serve as 2.5V V<sub>DD\_CORE</sub> power inputs

2. Alternately, can function as Quad Timer pins

3. Pins in this section can function as Quad Timer, SPI #1, or GPIO

## Table 2-2 Signal and Package Information for the 160-Pin LQFP and MBGA (Continued)

| Signal<br>Name  | Pin<br>No. | Ball No. | Туре             | State<br>During<br>Reset                                     | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|------------|----------|------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7              | 28         | К1       | Input/<br>Output | In reset,<br>output is<br>disabled,<br>pull-up is<br>enabled | <ul> <li>Data Bus — D7 - D15 specify part of the data for external program or data memory accesses.</li> <li>Depending upon the state of the DRV bit in the EMI bus control register (BCR), D7 - D15 are tri-stated when the external bus is inactive.</li> <li>Most designs will want to change the DRV state to DRV = 1 instead of using the default setting.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                |

| (GPIOF0)        |            |          | Input/<br>Output |                                                              | <b>Port F GPIO</b> — These nine GPIO pins can be individually programmed as input or output pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D8<br>(GPIOF1)  | 29         | К3       | Ouput            |                                                              | At reset, these pins default to Data Bus functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D9<br>(GPIOF2)  | 30         | K2       |                  |                                                              | To deactivate the internal pull-up resistor, clear the appropriate GPIO bit in the GPIOF_PUR register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| D10<br>(GPIOF3) | 32         | K4       |                  |                                                              | Example: GPIOF0, clear bit 0 in the GPIOF_PUR register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D11<br>(GPIOF4) | 149        | A5       |                  |                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| D12<br>(GPIOF5) | 150        | A4       |                  |                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| D13<br>(GPIOF6) | 151        | B5       |                  |                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| D14<br>(GPIOF7) | 152        | C4       |                  |                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| D15<br>(GPIOF8) | 153        | A3       |                  |                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RD              | 52         | Ρ5       | Output           | In reset,<br>output is<br>disabled,<br>pull-up is<br>enabled | <ul> <li>Read Enable — RD is asserted during external memory read cycles. When RD is asserted low, pins D0 - D15 become inputs and an external device is enabled onto the data bus. When RD is deasserted high, the external data is latched inside the device. When RD is asserted, it qualifies the A0 - A23, PS, DS, and CSn pins. RD can be connected directly to the OE pin of a static RAM or ROM.</li> <li>Depending upon the state of the DRV bit in the EMI bus control register (BCR), RD is tri-stated when the external bus is inactive.</li> <li>Most designs will want to change the DRV state to DRV = 1 instead of using the default setting.</li> <li>To deactivate the internal pull-up resistor, set the CTRL bit in the SIM_PUDR register.</li> </ul> |

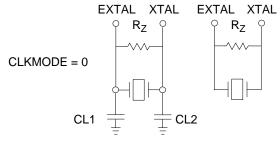

start-up. The crystal and associated components should be mounted as near as possible to the EXTAL and XTAL pins to minimize output distortion and start-up stabilization time.

#### Crystal Frequency = 4 - 8MHz (optimized for 8MHz)

Sample External Crystal Parameters:  $R_z = 750 \text{ K}\Omega$

Note: If the operating temperature range is limited to below  $85^{\circ}$ C (105°C junction), then R<sub>z</sub> = 10 Meg  $\Omega$

### Figure 3-2 Connecting to a Crystal Oscillator

**Note:** The OCCS\_COHL bit must be set to 1 when a crystal oscillator is used. The reset condition on the OCCS\_COHL bit is 0. Please see the COHL bit in the Oscillator Control (OSCTL) register, discussed in the **56F8300 Peripheral User Manual**.

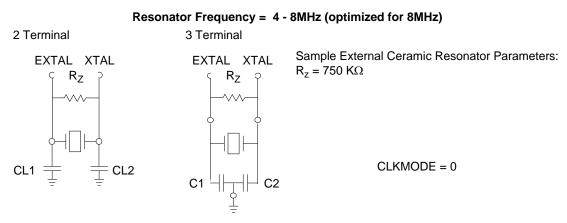

# 3.2.2 Ceramic Resonator (Default)

It is also possible to drive the internal oscillator with a ceramic resonator, assuming the overall system design can tolerate the reduced signal integrity. A typical ceramic resonator circuit is shown in **Figure 3-3**. Refer to the supplier's recommendations when selecting a ceramic resonator and associated components. The resonator and components should be mounted as near as possible to the EXTAL and XTAL pins.

Figure 3-3 Connecting a Ceramic Resonator

**Note:** The OCCS\_COHL bit must be set to 0 when a ceramic resonator is used. The reset condition on the OCCS\_COHL bit is 0. Please see the COHL bit in the Oscillator Control (OSCTL) register, discussed in the **56F8300 Peripheral User Manual**.

## 3.2.3 External Clock Source

The recommended method of connecting an external clock is given in **Figure 3-4**. The external clock source is connected to XTAL and the EXTAL pin is grounded. When using an external clock source, set

| Peripheral<br>FLEXCAN<br>FLEXCAN | <b>Number</b><br>26<br>27 | Priority<br>Level | Address + | Interrupt Function                            |

|----------------------------------|---------------------------|-------------------|-----------|-----------------------------------------------|

|                                  |                           | 0-2               |           |                                               |

| FLEXCAN                          | 27                        | 0 -               | P:\$34    | FLEXCAN Bus Off                               |

|                                  |                           | 0-2               | P:\$36    | FLEXCAN Error                                 |

| FLEXCAN                          | 28                        | 0-2               | P:\$38    | FLEXCAN Wake Up                               |

| FLEXCAN                          | 29                        | 0-2               | P:\$3A    | FLEXCAN Message Buffer Interrupt              |

| GPIOF                            | 30                        | 0-2               | P:\$3C    | GPIO F                                        |

| GPIOE                            | 31                        | 0-2               | P:\$3E    | GPIO E                                        |

| GPIOD                            | 32                        | 0-2               | P:\$40    | GPIO D                                        |

| GPIOC                            | 33                        | 0-2               | P:\$42    | GPIO C                                        |

| GPIOB                            | 34                        | 0-2               | P:\$44    | GPIO B                                        |

| GPIOA                            | 35                        | 0-2               | P:\$46    | GPIO A                                        |

|                                  |                           |                   |           | Reserved                                      |

| SPI1                             | 38                        | 0-2               | P:\$4C    | SPI 1 Receiver Full                           |

| SPI1                             | 39                        | 0-2               | P:\$4E    | SPI 1 Transmitter Empty                       |

| SPI0                             | 40                        | 0-2               | P:\$50    | SPI 0 Receiver Full                           |

| SPI0                             | 41                        | 0-2               | P:\$52    | SPI 0 Transmitter Empty                       |

| SCI1                             | 42                        | 0-2               | P:\$54    | SCI 1 Transmitter Empty                       |

| SCI1                             | 43                        | 0-2               | P:\$56    | SCI 1 Transmitter Idle                        |

|                                  |                           |                   |           | Reserved                                      |

| SCI1                             | 45                        | 0-2               | P:\$5A    | SCI 1 Receiver Error                          |

| SCI1                             | 46                        | 0-2               | P:\$5C    | SCI 1 Receiver Full                           |

| DEC1                             | 47                        | 0-2               | P:\$5E    | Quadrature Decoder #1 Home Switch or Watchdog |

| DEC1                             | 48                        | 0-2               | P:\$60    | Quadrature Decoder #1 INDEX Pulse             |

| DEC0                             | 49                        | 0-2               | P:\$62    | Quadrature Decoder #0 Home Switch or Watchdog |

| DEC0                             | 50                        | 0-2               | P:\$64    | Quadrature Decoder #0 INDEX Pulse             |

|                                  |                           |                   |           | Reserved                                      |

| TMRD                             | 52                        | 0-2               | P:\$68    | Timer D, Channel 0                            |

| TMRD                             | 53                        | 0-2               | P:\$6A    | Timer D, Channel 1                            |

| TMRD                             | 54                        | 0-2               | P:\$6C    | Timer D, Channel 2                            |

| TMRD                             | 55                        | 0-2               | P:\$6E    | Timer D, Channel 3                            |

| TMRC                             | 56                        | 0-2               | P:\$70    | Timer C, Channel 0                            |

| TMRC                             | 57                        | 0-2               | P:\$72    | Timer C, Channel 1                            |

| TMRC                             | 58                        | 0-2               | P:\$74    | Timer C, Channel 2                            |

| TMRC                             | 59                        | 0-2               | P:\$76    | Timer C, Channel 3                            |

# Table 4-5 Interrupt Vector Table Contents<sup>1</sup> (Continued)

# 4.6 EOnCE Memory Map

### Table 4-8 EOnCE Memory Map

| Address      | Register Acronym       | Register Name                                               |

|--------------|------------------------|-------------------------------------------------------------|

|              |                        | Reserved                                                    |

| X:\$FF FF8A  | OESCR                  | External Signal Control Register                            |

|              |                        | Reserved                                                    |

| X:\$FF FF8E  | OBCNTR                 | Breakpoint Unit [0] Counter                                 |

|              |                        | Reserved                                                    |

| X:\$FF FF90  | OBMSK (32 bits)        | Breakpoint 1 Unit [0] Mask Register                         |

| X:\$FF FF91  | —                      | Breakpoint 1 Unit [0] Mask Register                         |

| X:\$FF FF92  | OBAR2 (32 bits)        | Breakpoint 2 Unit [0] Address Register                      |

| X:\$FF FF93  | —                      | Breakpoint 2 Unit [0] Address Register                      |

| X:\$FF FF94  | OBAR1 (24 bits)        | Breakpoint 1 Unit [0] Address Register                      |

| X:\$FF FF95  | —                      | Breakpoint 1 Unit [0] Address Register                      |

| X:\$FF FF96  | OBCR (24 bits)         | Breakpoint Unit [0] Control Register                        |

| X:\$FF FF97  | —                      | Breakpoint Unit [0] Control Register                        |

| X:\$FF FF98  | OTB (21-24 bits/stage) | Trace Buffer Register Stages                                |

| X:\$FF FF99  | —                      | Trace Buffer Register Stages                                |

| X:\$FF FF9A  | OTBPR (8 bits)         | Trace Buffer Pointer Register                               |

| X:\$FF FF9B  | OTBCR                  | Trace Buffer Control Register                               |

| X:\$FF FF9C  | OBASE (8 bits)         | Peripheral Base Address Register                            |

| X:\$FF FF9D  | OSR                    | Status Register                                             |

| X:\$FF FF9E  | OSCNTR (24 bits)       | Instruction Step Counter                                    |

| X:\$FF FF9F  | —                      | Instruction Step Counter                                    |

| :X:\$FF FFA0 | OCR (bits)             | Control Register                                            |

|              |                        | Reserved                                                    |

| X:\$FF FFFC  | OCLSR (8 bits)         | Core Lock / Unlock Status Register                          |

| X:\$FF FFFD  | OTXRXSR (8 bits)       | Transmit and Receive Status and Control Register            |

| X:\$FF FFFE  | OTX / ORX (32 bits)    | Transmit Register / Receive Register                        |

| X:\$FF FFFF  | OTX1 / ORX1            | Transmit Register Upper Word<br>Receive Register Upper Word |

# 4.7 Peripheral Memory Mapped Registers

On-chip peripheral registers are part of the data memory map on the 56800E series. These locations may be accessed with the same addressing modes used for ordinary Data memory, except all peripheral registers should be read/written using word accesses only.

| Register Acronym | Address Offset | Register Description           |

|------------------|----------------|--------------------------------|

| ADCA_CR 1        | \$0            | Control Register 1             |

| ADCA_CR 2        | \$1            | Control Register 2             |

| ADCA_ZCC         | \$2            | Zero Crossing Control Register |

| ADCA_LST 1       | \$3            | Channel List Register 1        |

| ADCA_LST 2       | \$4            | Channel List Register 2        |

| ADCA_SDIS        | \$5            | Sample Disable Register        |

| ADCA_STAT        | \$6            | Status Register                |

| ADCA_LSTAT       | \$7            | Limit Status Register          |

| ADCA_ZCSTAT      | \$8            | Zero Crossing Status Register  |

| ADCA_RSLT 0      | \$9            | Result Register 0              |

| ADCA_RSLT 1      | \$A            | Result Register 1              |

| ADCA_RSLT 2      | \$B            | Result Register 2              |

| ADCA_RSLT 3      | \$C            | Result Register 3              |

| ADCA_RSLT 4      | \$D            | Result Register 4              |

| ADCA_RSLT 5      | \$E            | Result Register 5              |

| ADCA_RSLT 6      | \$F            | Result Register 6              |

| ADCA_RSLT 7      | \$10           | Result Register 7              |

| ADCA_LLMT 0      | \$11           | Low Limit Register 0           |

| ADCA_LLMT 1      | \$12           | Low Limit Register 1           |

| ADCA_LLMT 2      | \$13           | Low Limit Register 2           |

| ADCA_LLMT 3      | \$14           | Low Limit Register 3           |

| ADCA_LLMT 4      | \$15           | Low Limit Register 4           |

| ADCA_LLMT 5      | \$16           | Low Limit Register 5           |

| ADCA_LLMT 6      | \$17           | Low Limit Register 6           |

| ADCA_LLMT 7      | \$18           | Low Limit Register 7           |

| ADCA_HLMT 0      | \$19           | High Limit Register 0          |

| ADCA_HLMT 1      | \$1A           | High Limit Register 1          |

| ADCA_HLMT 2      | \$1B           | High Limit Register 2          |

| ADCA_HLMT 3      | \$1C           | High Limit Register 3          |

| ADCA_HLMT 4      | \$1D           | High Limit Register 4          |

| ADCA_HLMT 5      | \$1E           | High Limit Register 5          |

| ADCA_HLMT 6      | \$1F           | High Limit Register 6          |

| ADCA_HLMT 7      | \$20           | High Limit Register 7          |

### Table 4-20 Analog-to-Digital Converter Registers Address Map (ADCA\_BASE = \$00 F200)

#### Table 4-20 Analog-to-Digital Converter Registers Address Map (Continued) (ADCA\_BASE = \$00 F200)

| Register Acronym | Address Offset | Register Description     |

|------------------|----------------|--------------------------|

| ADCA_OFS 0       | \$21           | Offset Register 0        |

| ADCA_OFS 1       | \$22           | Offset Register 1        |

| ADCA_OFS 2       | \$23           | Offset Register 2        |

| ADCA_OFS 3       | \$24           | Offset Register 3        |

| ADCA_OFS 4       | \$25           | Offset Register 4        |

| ADCA_OFS 5       | \$26           | Offset Register 5        |

| ADCA_OFS 6       | \$27           | Offset Register 6        |

| ADCA_OFS 7       | \$28           | Offset Register 7        |

| ADCA_POWER       | \$29           | Power Control Register   |

| ADCA_CAL         | \$2A           | ADC Calibration Register |

#### Table 4-21 Analog-to-Digital Converter Registers Address Map (ADCB\_BASE = \$00 F240)

| Register Acronym | Address Offset | Register Description           |

|------------------|----------------|--------------------------------|

| ADCB_CR 1        | \$0            | Control Register 1             |

| ADCB_CR 2        | \$1            | Control Register 2             |

| ADCB_ZCC         | \$2            | Zero Crossing Control Register |

| ADCB_LST 1       | \$3            | Channel List Register 1        |

| ADCB_LST 2       | \$4            | Channel List Register 2        |

| ADCB_SDIS        | \$5            | Sample Disable Register        |

| ADCB_STAT        | \$6            | Status Register                |

| ADCB_LSTAT       | \$7            | Limit Status Register          |

| ADCB_ZCSTAT      | \$8            | Zero Crossing Status Register  |

| ADCB_RSLT 0      | \$9            | Result Register 0              |

| ADCB_RSLT 1      | \$A            | Result Register 1              |

| ADCB_RSLT 2      | \$B            | Result Register 2              |

| ADCB_RSLT 3      | \$C            | Result Register 3              |

| ADCB_RSLT 4      | \$D            | Result Register 4              |

| ADCB_RSLT 5      | \$E            | Result Register 5              |

| ADCB_RSLT 6      | \$F            | Result Register 6              |

| ADCB_RSLT 7      | \$10           | Result Register 7              |

| ADCB_LLMT 0      | \$11           | Low Limit Register 0           |

| Register Acronym | Address Offset | Register Description              | Reset Value                                  |

|------------------|----------------|-----------------------------------|----------------------------------------------|

| GPIOB_PUR        | \$0            | Pull-up Enable Register           | 0 x 00FF                                     |

| GPIOB_DR         | \$1            | Data Register                     | 0 x 0000                                     |

| GPIOB_DDR        | \$2            | Data Direction Register           | 0 x 0000                                     |

| GPIOB_PER        | \$3            | Peripheral Enable Register        | 0 x 000F for 20-bit EMI<br>address at reset. |

|                  |                |                                   | 0 x 0000 for all other cases.                |

|                  |                |                                   | See Table 4-4 for details.                   |

| GPIOB_IAR        | \$4            | Interrupt Assert Register         | 0 x 0000                                     |

| GPIOB_IENR       | \$5            | Interrupt Enable Register         | 0 x 0000                                     |

| GPIOB_IPOLR      | \$6            | Interrupt Polarity Register       | 0 x 0000                                     |

| GPIOB_IPR        | \$7            | Interrupt Pending Register        | 0 x 0000                                     |

| GPIOB_IESR       | \$8            | Interrupt Edge-Sensitive Register | 0 x 0000                                     |

| GPIOB_PPMODE     | \$9            | Push-Pull Mode Register           | 0 x 0000                                     |

| GPIOB_RAWDATA    | \$A            | Raw Data Input Register           | —                                            |

#### Table 4-30 GPIOB Registers Address Map (GPIOB\_BASE = \$00 F300)

### Table 4-31 GPIOC Registers Address Map (GPIOC\_BASE = \$00F310)

| Register Acronym | Address Offset | Register Description              | Reset Value |

|------------------|----------------|-----------------------------------|-------------|

| GPIOC_PUR        | \$0            | Pull-up Enable Register           | 0 x 07FF    |

| GPIOC_DR         | \$1            | Data Register                     | 0 x 0000    |

| GPIOC_DDR        | \$2            | Data Direction Register           | 0 x 0000    |

| GPIOC_PER        | \$3            | Peripheral Enable Register        | 0 x 07FF    |

| GPIOC_IAR        | \$4            | Interrupt Assert Register         | 0 x 0000    |

| GPIOC_IENR       | \$5            | Interrupt Enable Register         | 0 x 0000    |

| GPIOC_IPOLR      | \$6            | Interrupt Polarity Register       | 0 x 0000    |

| GPIOC_IPR        | \$7            | Interrupt Pending Register        | 0 x 0000    |

| GPIOC_IESR       | \$8            | Interrupt Edge-Sensitive Register | 0 x 0000    |

| GPIOC_PPMODE     | \$9            | Push-Pull Mode Register           | 0 x 07FF    |

| GPIOC_RAWDATA    | \$A            | Raw Data Input Register           | _           |

#### Table 4-39 FlexCAN2 Registers Address Map (Continued) (FC2\_BASE = \$00 FA00) FlexCAN2 is NOT available in the 56F8167 device

| Register Acronym | Address Offset | Register Description                        |

|------------------|----------------|---------------------------------------------|

| FC2MB11_DATA     | \$9C           | Message Buffer 11 Data Register             |

| FC2MB11_DATA     | \$9D           | Message Buffer 11 Data Register             |

| FC2MB11_DATA     | \$9E           | Message Buffer 11 Data Register             |

|                  |                | Reserved                                    |

| FC2MB12_CONTROL  | \$A0           | Message Buffer 12 Control / Status Register |

| FC2MB12_ID_HIGH  | \$A1           | Message Buffer 12 ID High Register          |

| FC2MB12_ID_LOW   | \$A2           | Message Buffer 12 ID Low Register           |

| FC2MB12_DATA     | \$A3           | Message Buffer 12 Data Register             |

| FC2MB12_DATA     | \$A4           | Message Buffer 12 Data Register             |

| FC2MB12_DATA     | \$A5           | Message Buffer 12 Data Register             |

| FC2MB12_DATA     | \$A6           | Message Buffer 12 Data Register             |

|                  |                | Reserved                                    |

| FC2MB13_CONTROL  | \$A8           | Message Buffer 13 Control / Status Register |

| FC2MB13_ID_HIGH  | \$A9           | Message Buffer 13 ID High Register          |

| FC2MB13_ID_LOW   | \$AA           | Message Buffer 13 ID Low Register           |

| FC2MB13_DATA     | \$AB           | Message Buffer 13 Data Register             |

| FC2MB13_DATA     | \$AC           | Message Buffer 13 Data Register             |

| FC2MB13_DATA     | \$AD           | Message Buffer 13 Data Register             |

| FC2MB13_DATA     | \$AE           | Message Buffer 13 Data Register             |

|                  |                | Reserved                                    |

| FC2MB14_CONTROL  | \$B0           | Message Buffer 14 Control / Status Register |

| FC2MB14_ID_HIGH  | \$B1           | Message Buffer 14 ID High Register          |

| FC2MB14_ID_LOW   | \$B2           | Message Buffer 14 ID Low Register           |

| FC2MB14_DATA     | \$B3           | Message Buffer 14 Data Register             |

| FC2MB14_DATA     | \$B4           | Message Buffer 14 Data Register             |

| FC2MB14_DATA     | \$B5           | Message Buffer 14 Data Register             |

| FC2MB14_DATA     | \$B6           | Message Buffer 14 Data Register             |

|                  |                | Reserved                                    |

| FC2MB15_CONTROL  | \$B8           | Message Buffer 15 Control / Status Register |

| FC2MB15_ID_HIGH  | \$B9           | Message Buffer 15 ID High Register          |

| FC2MB15_ID_LOW   | \$BA           | Message Buffer 15 ID Low Register           |

| FC2MB15_DATA     | \$BB           | Message Buffer 15 Data Register             |

| FC2MB15_DATA     | \$BC           | Message Buffer 15 Data Register             |

| FC2MB15_DATA     | \$BD           | Message Buffer 15 Data Register             |

# 5.6.1 Interrupt Priority Register 0 (IPR0)

| Base + \$0 | 15 | 14 | 13    | 12 | 11     | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|----|----|-------|----|--------|----|---|---|---|---|---|---|---|---|---|---|

| Read       | 0  | 0  | BKPT_ |    | STPCI  |    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Write      |    |    |       |    | 011 01 |    |   |   |   |   |   |   |   |   |   |   |

| RESET      | 0  | 0  | 0     | 0  | 0      | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Figure 5-3 Interrupt Priority Register 0 (IPR0)

### 5.6.1.1 Reserved—Bits 15–14

This bit field is reserved or not implemented. It is read as 0 and cannot be modified by writing.

### 5.6.1.2 EOnCE Breakpoint Unit 0 Interrupt Priority Level (BKPT\_U0 IPL)— Bits13–12

This field is used to set the interrupt priority levels for IRQs. This IRQ is limited to priorities 1 through 3. It is disabled by default.

- 00 = IRQ disabled (default)

- 01 = IRQ is priority level 1

- 10 = IRQ is priority level 2

- 11 = IRQ is priority level 3

### 5.6.1.3 EOnCE Step Counter Interrupt Priority Level (STPCNT IPL)— Bits 11–10

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 1 through 3. It is disabled by default.

- 00 = IRQ disabled (default)

- 01 = IRQ is priority level 1

- 10 = IRQ is priority level 2

- 11 = IRQ is priority level 3

### 5.6.1.4 Reserved—Bits 9–0

This bit field is reserved or not implemented. It is read as 0 and cannot be modified by writing.

## 5.6.2 Interrupt Priority Register 1 (IPR1)

| Base + \$1 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5            | 4 | 3          | 2 | 1         | 0 |

|------------|----|----|----|----|----|----|---|---|---|---|--------------|---|------------|---|-----------|---|

| Read       | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 |              |   | TY P       |   | TRBI      |   |

| Write      |    |    |    |    |    |    |   |   |   |   | - RX_REG IPL |   | TX_REG IPL |   | TRBUF IPL |   |

| RESET      | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0            | 0 | 0          | 0 | 0         | 0 |

Figure 5-4 Interrupt Priority Register 1 (IPR1)

# 6.5 Register Descriptions

| Table | 6-1 | SIM | Reg | isters |

|-------|-----|-----|-----|--------|

|       |     |     |     | F350)  |

| Address Offset      | Address Acronym | Register Name                            | Section Location |

|---------------------|-----------------|------------------------------------------|------------------|

| Base + \$0          | SIM_CONTROL     | Control Register                         | 6.5.1            |

| Base + \$1          | SIM_RSTSTS      | Reset Status Register                    | 6.5.2            |

| Base + \$2          | SIM_SCR0        | Software Control Register 0              | 6.5.3            |

| Base + \$3          | SIM_SCR1        | Software Control Register 1              | 6.5.3            |

| Base + \$4          | SIM_SCR2        | Software Control Register 2              | 6.5.3            |

| Base + \$5          | SIM_SCR3        | Software Control Register 3              | 6.5.3            |

| Base + \$6          | SIM_MSH_ID      | Most Significant Half of JTAG ID         | 6.5.4            |

| Base + \$7          | SIM_LSH_ID      | Least Significant Half of JTAG ID        | 6.5.5            |

| Base + \$8          | SIM_PUDR        | Pull-up Disable Register                 | 6.5.6            |

|                     |                 | Reserved                                 |                  |

| Base + \$A          | SIM_CLKOSR      | CLKO Select Register                     | 6.5.7            |

| Base + \$B          | SIM_GPS         | GPIO Peripheral Select Register          | 6.5.8            |

| Base + \$C          | SIM_PCE         | Peripheral Clock Enable Register         | 6.5.9            |

| Base + \$D          | SIM_ISALH       | I/O Short Address Location High Register | 6.5.10           |

| Base + \$E          | SIM_ISALL       | I/O Short Address Location Low Register  | 6.5.10           |

| Base + \$F SIM_PCE2 |                 | Peripheral Clock Enable Register 2       | 6.5.11           |

### 6.5.8.2 GPIOD1 (D1)—Bit 5

This bit selects the alternate function for GPIOD1.

- $0 = \overline{CS3}$

- $1 = CAN2_RX$

### 6.5.8.3 GPIOD0 (D0)—Bit 4

- $0 = \overline{CS2}$

- $1 = CAN2_TX$

### 6.5.8.4 GPIOC3 (C3)—Bit 3

This bit selects the alternate function for GPIOC3.

- 0 = HOME1/TB3 (default see "Switch Matrix Mode" bits of the Quad Decoder DECCR register in the **56F8300 Peripheral User Manual**)

- $1 = \overline{SS1}$

### 6.5.8.5 GPIOC2 (C2)—Bit 2

This bit selects the alternate function for GPIOC2.

- 0 = INDEX1/TB2 (default)

- 1 = MISO1

### 6.5.8.6 GPIOC1 (C1)—Bit 1

This bit selects the alternate function for GPIOC1.

- 0 = PHASEB1/TB1 (default)

- 1 = MOSI1

### 6.5.8.7 GPIOC0 (C0)—Bit 0

This bit selects the alternate function for GPIOC0.

- 0 = PHASEA1/TB0 (default)

- 1 = SCLK1

## 6.5.9 Peripheral Clock Enable Register (SIM\_PCE)

The Peripheral Clock Enable register is used enable or disable clocks to the peripherals as a power savings feature. The clocks can be individually controlled for each peripheral on the chip.

| Base + \$C | 15  | 14   | 13     | 12   | 11   | 10   | 9     | 8       | 7      | 6       | 5     | 4     | 3     | 2     | 1      | 0        |

|------------|-----|------|--------|------|------|------|-------|---------|--------|---------|-------|-------|-------|-------|--------|----------|

| Read       | EMI | ADCB | ADCA   | CAN  | DEC1 | DEC0 | TMRD  | TMRC    | TMRB   | TMRA    | SCI 1 | SCI 0 | SPI 1 | SPI 0 | PWMB   | PWMA     |

| Write      |     | ABOB | //DO// | 0/11 | DEOI | DLOU | TWITE | - Wirke | TIMILE | TIMITON | 0011  | 0010  | OFFT  | 0110  | I WIND | 1 001007 |

| RESET      | 1   | 1    | 1      | 1    | 1    | 1    | 1     | 1       | 1      | 1       | 1     | 1     | 1     | 1     | 1      | 1        |

Figure 6-13 Peripheral Clock Enable Register (SIM\_PCE)

## 6.5.9.1 External Memory Interface Enable (EMI)—Bit 15

Each bit controls clocks to the indicated peripheral.

- 1 = Clocks are enabled

- 0 = The clock is not provided to the peripheral (the peripheral is disabled)

## 6.5.9.2 Analog-to-Digital Converter B Enable (ADCB)—Bit 14

Each bit controls clocks to the indicated peripheral.

- 1 = Clocks are enabled

- 0 = The clock is not provided to the peripheral (the peripheral is disabled)

## 6.5.9.3 Analog-to-Digital Converter A Enable (ADCA)—Bit 13

Each bit controls clocks to the indicated peripheral.

- 1 = Clocks are enabled

- 0 = The clock is not provided to the peripheral (the peripheral is disabled)

## 6.5.9.4 FlexCAN Enable (CAN)—Bit 12

Each bit controls clocks to the indicated peripheral.

- 1 = Clocks are enabled

- 0 = The clock is not provided to the peripheral (the peripheral is disabled)

## 6.5.9.5 Decoder 1 Enable (DEC1)—Bit 11

Each bit controls clocks to the indicated peripheral.

- 1 = Clocks are enabled

- 0 = The clock is not provided to the peripheral (the peripheral is disabled)

## 6.5.9.6 Decoder 0 Enable (DEC0)—Bit 10

Each bit controls clocks to the indicated peripheral.

- 1 = Clocks are enabled

- 0 = The clock is not provided to the peripheral (the peripheral is disabled)

# 6.5.9.7 Quad Timer D Enable (TMRD)—Bit 9

Each bit controls clocks to the indicated peripheral.

- 1 = Clocks are enabled

- 0 = The clock is not provided to the peripheral (the peripheral is disabled)

# 6.5.9.8 Quad Timer C Enable (TMRC)—Bit 8

Each bit controls clocks to the indicated peripheral.

- 1 = Clocks are enabled

- 0 = The clock is not provided to the peripheral (the peripheral is disabled)

# 6.5.10 I/O Short Address Location Register (SIM\_ISALH and SIM\_ISALL)

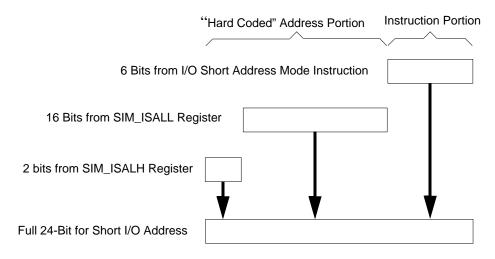

The I/O Short Address Location registers are used to specify the memory referenced via the I/O short address mode. The I/O short address mode allows the instruction to specify the lower six bits of address; the upper address bits are not directly controllable. This register set allows limited control of the full address, as shown in **Figure 6-14**.

**Note:** If this register is set to something other than the top of memory (EOnCE register space) and the EX bit in the OMR is set to 1, the JTAG port cannot access the on-chip EOnCE registers, and debug functions will be affected.

Figure 6-14 I/O Short Address Determination

With this register set, an interrupt driver can set the SIM\_ISALL register pair to point to its peripheral registers and then use the I/O Short addressing mode to reference them. The ISR should restore this register to its previous contents prior to returning from interrupt.

- **Note:** The default value of this register set points to the EOnCE registers.

- **Note:** The pipeline delay between setting this register set and using short I/O addressing with the new value is three cycles.

| Base + \$D | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1       | 0      |

|------------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---------|--------|

| Read       | 1  | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | ISAL[:  | 23.221 |

| Write      |    |    |    |    |    |    |   |   |   |   |   |   |   |   | 10/ 12/ | 20.22] |

| RESET      | 1  | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1       | 1      |

Figure 6-15 I/O Short Address Location High Register (SIM\_ISALH)

## 6.5.10.1 Input/Output Short Address Low (ISAL[23:22])—Bit 1–0

This field represents the upper two address bits of the "hard coded" I/O short address.

The 56800E core contains both STOP and WAIT instructions. Both put the CPU to sleep. For lowest power consumption in Stop mode, the PLL can be shut down. This must be done explicitly before entering Stop mode, since there is no automatic mechanism for this. When the PLL is shut down, the 56800E system clock must be set equal to the oscillator output.

Some applications require the 56800E STOP/WAIT instructions be disabled. To disable those instructions, write to the SIM control register (SIM\_CONTROL) described in **Part 6.5.1**. This procedure can be on either a permanent or temporary basis. Permanently assigned applications last only until their next reset.

# 6.9 Resets

The SIM supports four sources of reset. The two asynchronous sources are the external reset pin and the Power-On Reset (POR). The two synchronous sources are the software reset, which is generated within the SIM itself by writting to the SIM\_CONTROL register, and the COP reset.

Reset begins with the assertion of any of the reset sources. Release of reset to various blocks is sequenced to permit proper operation of the device. A POR reset is first extended for  $2^{21}$  clock cycles to permit stabilization of the clock source, followed by a 32 clock window in which SIM clocking is initiated. It is then followed by a 32 clock window in which peripherals are released to implement Flash security, and, finally, followed by a 32 clock window in which the core is initialized. After completion of the described reset sequence, application code will begin execution.

Resets may be asserted asynchronously, but are always released internally on a rising edge of the system clock.

# Part 7 Security Features

The 56F8367/56F8167 offer security features intended to prevent unauthorized users from reading the contents of the Flash Memory (FM) array. The Flash security consists of several hardware interlocks that block the means by which an unauthorized user could gain access to the Flash array.

However, part of the security must lie with the user's code. An extreme example would be user's code that dumps the contents of the internal program, as this code would defeat the purpose of security. At the same time, the user may also wish to put a "backdoor" in his program. As an example, the user downloads a security key through the SCI, allowing access to a programming routine that updates parameters stored in another section of the Flash.

# 7.1 Operation with Security Enabled

Once the user has programmed the Flash with his application code, the device can be secured by programming the security bytes located in the FM configuration field, which occupies a portion of the FM array. These non-volatile bytes will keep the part secured through reset and through power-down of the device. Only two bytes within this field are used to enable or disable security. Refer to the Flash Memory section in the **56F8300 Peripheral User Manual** for the state of the security bytes and the resulting state

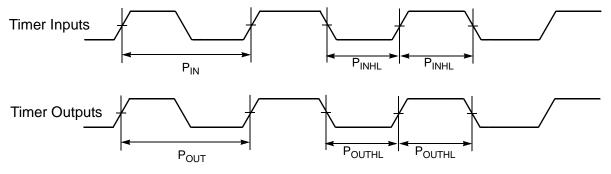

# 10.11 Quad Timer Timing

## Table 10-19 Timer Timing<sup>1, 2</sup>

| Characteristic                 | Symbol            | Min      | Мах | Unit | See Figure |

|--------------------------------|-------------------|----------|-----|------|------------|

| Timer input period             | P <sub>IN</sub>   | 2T + 6   | _   | ns   | 10-15      |

| Timer input high / low period  | P <sub>INHL</sub> | 1T + 3   | _   | ns   | 10-15      |

| Timer output period            | P <sub>OUT</sub>  | 1T - 3   | _   | ns   | 10-15      |

| Timer output high / low period | POUTHL            | 0.5T - 3 | _   | ns   | 10-15      |

1. In the formulas listed, T = the clock cycle. For 60MHz operation, T = 16.67ns.

2. Parameters listed are guaranteed by design.

Figure 10-15 Timer Timing

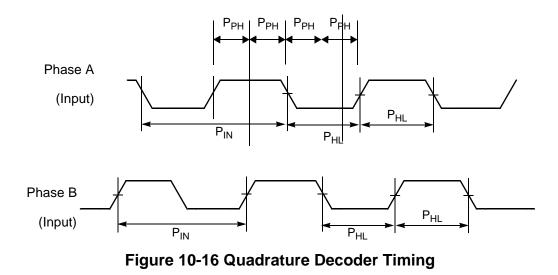

# **10.12** Quadrature Decoder Timing

| Characteristic                     | Symbol          | Min     | Max | Unit | See Figure |

|------------------------------------|-----------------|---------|-----|------|------------|

| Quadrature input period            | P <sub>IN</sub> | 4T + 12 | _   | ns   | 10-16      |

| Quadrature input high / low period | P <sub>HL</sub> | 2T + 6  | _   | ns   | 10-16      |

| Quadrature phase period            | P <sub>PH</sub> | 1T + 3  | _   | ns   | 10-16      |

### Table 10-20 Quadrature Decoder Timing<sup>1, 2</sup>

1. In the formulas listed, T = the clock cycle. For 60MHz operation, T=16.67ns.

2. Parameters listed are guaranteed by design.

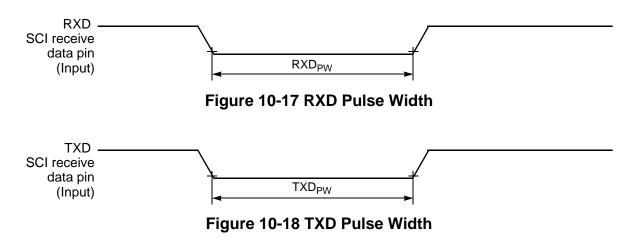

# **10.13** Serial Communication Interface (SCI) Timing

|  | Table | 10-21 | SCI | Timing <sup>1</sup> |

|--|-------|-------|-----|---------------------|

|--|-------|-------|-----|---------------------|

| Characteristic               | Symbol            | Min      | Мах                    | Unit | See Figure |

|------------------------------|-------------------|----------|------------------------|------|------------|

| Baud Rate <sup>2</sup>       | BR                | _        | (f <sub>MAX</sub> /16) | Mbps | _          |

| RXD <sup>3</sup> Pulse Width | RXD <sub>PW</sub> | 0.965/BR | 1.04/BR                | ns   | 10-17      |

| TXD <sup>4</sup> Pulse Width | TXD <sub>PW</sub> | 0.965/BR | 1.04/BR                | ns   | 10-18      |

1. Parameters listed are guaranteed by design.

f<sub>MAX</sub> is the frequency of operation of the system clock, ZCLK, in MHz, which is 60MHz for the 56F8367 device , and 40MHz for the 56F8167 device.

3. The RXD pin in SCI0 is named RXD0 and the RXD pin in SCI1 is named RXD1.

4. The TXD pin in SCI0 is named TXD0 and the TXD pin in SCI1 is named TXD1.

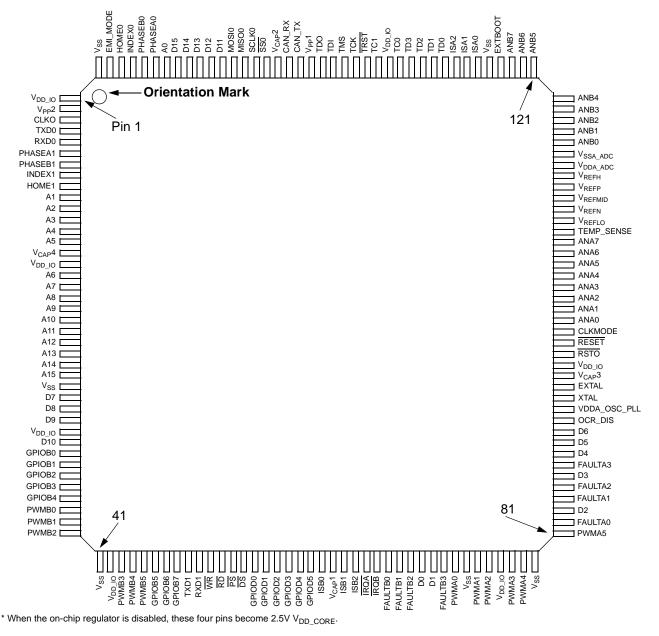

# Part 11 Packaging

Note: The 160 Map Ball Grid Array is not available in the 56F8167 device.

# 11.1 56F8367 Package and Pin-Out Information

This section contains package and pin-out information for the 56F8367. This device comes in a 160-pin Low-profile Quad Flat Pack (LQFP) and *160 Map Ball Grid Array*. Figure 11-1 shows the package lay-out for the 160-pin LQFP, and Figure 11-2 for the160 Map Ball Grid Array. Figure 11-5 shows the mechanical parameters for the LQFP package and Figure 11-3 for the MAPBGA, Table 11-1 lists the pin-out for the 160-pin LQFP and Table 11-2 lists the pin-out for the 160 MAPBGA.

### Figure 11-1 Top View, 56F8367 160-Pin LQFP Package

| Pin No.   | Signal<br>Name                                                                             | Pin No. | Signal Name         | Pin No. | Signal Name              | Pin No. | Signal Name         |  |  |  |  |

|-----------|--------------------------------------------------------------------------------------------|---------|---------------------|---------|--------------------------|---------|---------------------|--|--|--|--|

| 1         | V <sub>DD_IO</sub>                                                                         | 41      | V <sub>SS</sub>     | 81      | NC                       | 121     | ANB5                |  |  |  |  |

| 2         | V <sub>PP</sub> 2                                                                          | 42      | V <sub>DD_IO</sub>  | 82      | NC                       | 122     | ANB6                |  |  |  |  |

| 3         | CLKO                                                                                       | 43      | PWMB3               | 83      | D2                       | 123     | ANB7                |  |  |  |  |

| 4         | TXD0                                                                                       | 44      | PWMB4               | 84      | NC                       | 124     | EXTBOOT             |  |  |  |  |

| 5         | RXD0                                                                                       | 45      | PWMB5               | 85      | NC                       | 125     | V <sub>SS</sub>     |  |  |  |  |

| 6         | SCLK1                                                                                      | 46      | GPIOB5              | 86      | D3                       | 126     | GPIOC8              |  |  |  |  |

| 7         | MOSI1                                                                                      | 47      | GPIOB6              | 87      | NC                       | 127     | GPIOC9              |  |  |  |  |

| 8         | MISO1                                                                                      | 48      | GPIOB7              | 88      | D4                       | 128     | GPIOC10             |  |  |  |  |

| 9         | SS1                                                                                        | 49      | TXD1                | 89      | D5                       | 129     | GPIOE10             |  |  |  |  |

| 10        | A1                                                                                         | 50      | RXD1                | 90      | D6                       | 130     | GPIOE11             |  |  |  |  |

| 11        | A2                                                                                         | 51      | WR                  | 91      | OCR_DIS                  | 131     | GPIOE12             |  |  |  |  |

| 12        | A3                                                                                         | 52      | RD                  | 92      | V <sub>DDA_OSC_PLL</sub> | 132     | GPIOE13             |  |  |  |  |

| 13        | A4                                                                                         | 53      | PS                  | 93      | XTAL                     | 133     | TC0                 |  |  |  |  |

| 14        | A5                                                                                         | 54      | DS                  | 94      | EXTAL                    | 134     | V <sub>DD_IO</sub>  |  |  |  |  |

| 15        | V <sub>CAP</sub> 4*                                                                        | 55      | GPIOD0              | 95      | V <sub>CAP</sub> 3*      | 135     | TC1                 |  |  |  |  |

| 16        | V <sub>DD_IO</sub>                                                                         | 56      | GPIOD1              | 96      | V <sub>DD_IO</sub>       | 136     | TRST                |  |  |  |  |

| 17        | A6                                                                                         | 57      | GPIOD2              | 97      | RSTO                     | 137     | ТСК                 |  |  |  |  |

| 18        | A7                                                                                         | 58      | GPIOD3              | 98      | RESET                    | 138     | TMS                 |  |  |  |  |

| 19        | A8                                                                                         | 59      | GPIOD4              | 99      | CLKMODE                  | 139     | TDI                 |  |  |  |  |

| 20        | A9                                                                                         | 60      | GPIOD5              | 100     | ANA0                     | 140     | TDO                 |  |  |  |  |

| 21        | A10                                                                                        | 61      | ISB0                | 101     | ANA1                     | 141     | V <sub>PP</sub> 1   |  |  |  |  |

| 22        | A11                                                                                        | 62      | V <sub>CAP</sub> 1* | 102     | ANA2                     | 142     | NC                  |  |  |  |  |

| 23        | A12                                                                                        | 63      | ISB1                | 103     | ANA3                     | 143     | NC                  |  |  |  |  |

| 24        | A13                                                                                        | 64      | ISB2                | 104     | ANA4                     | 144     | V <sub>CAP</sub> 2* |  |  |  |  |

| 25        | A14                                                                                        | 65      | IRQA                | 105     | ANA5                     | 145     | SS0                 |  |  |  |  |

| * When th | * When the on-chip regulator is disabled, these four pins become 2.5V V <sub>DD_CORE</sub> |         |                     |         |                          |         |                     |  |  |  |  |

Table 11-3 56F8167 160-Pin LQFP Package Identification by Pin Number

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

For Literature Requests Only: Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see <u>http://www.freescale.com</u> or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty. representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale <sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. This product incorporates SuperFlash® technology licensed from SST. © Freescale Semiconductor, Inc. 2005–2009. All rights reserved.

MC56F8367 Rev. 9 11/2009