Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                     |

| Core Size                  | 16/32-Bit                                                                 |

| Speed                      | 55MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, SSC, UART/USART, USB                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 32                                                                        |

| Program Memory Size        | 256KB (256K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                             |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 64-QFN (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at91sam7s256-mu |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

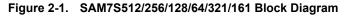

## 2. Block Diagram

| DDM           | USB Device Port Data -            | Analog |     | not present on SAM7S32/16                 |

|---------------|-----------------------------------|--------|-----|-------------------------------------------|

| DDP           | USB Device Port Data +            | Analog |     | not present on SAM7S32/16                 |

| SCK0 - SCK1   | Serial Clock                      | I/O    |     | CCIVI not present on CAMZC22/40           |

|               |                                   |        |     | SCK1 not present on SAM7S32/16            |

| TXD0 - TXD1   | Transmit Data                     | I/O    |     | TXD1 not present on SAM7S32/16            |

| RXD0 - RXD1   | Receive Data                      | Input  |     | RXD1 not present on SAM7S32/16            |

| RTS0 - RTS1   | Request To Send                   | Output |     | RTS1 not present on SAM7S32/16            |

| CTS0 - CTS1   | Clear To Send                     | Input  |     | CTS1 not present on SAM7S32/16            |

| DCD1          | Data Carrier Detect               | Input  |     | not present on SAM7S32/16                 |

| DTR1          | Data Terminal Ready               | Output |     | not present on SAM7S32/16                 |

| DSR1          | Data Set Ready                    | Input  |     | not present on SAM7S32/16                 |

| RI1           | Ring Indicator                    | Input  |     | not present on SAM7S32/16                 |

| TD            | Transmit Data                     | Output |     |                                           |

| RD            | Receive Data                      | Input  |     |                                           |

| TK            | Transmit Clock                    | I/O    |     |                                           |

| RK            | Receive Clock                     | I/O    |     |                                           |

| TF            | Transmit Frame Sync               | I/O    |     |                                           |

| RF            | Receive Frame Sync                | I/O    |     |                                           |

|               |                                   |        |     |                                           |

| TCLK0 - TCLK2 | External Clock Inputs             | Input  |     | TCLK1 and TCLK2 not present on SAM7S32/16 |

| TIOA0 - TIOA2 | I/O Line A                        | I/O    |     | TIOA2 not present on SAM7S32/16           |

| TIOB0 - TIOB2 | I/O Line B                        | I/O    |     | TIOB2 not present on SAM7S32/16           |

| PWM0 - PWM3   | PWM Channels                      | Output |     |                                           |

|               |                                   | Output |     |                                           |

| MISO          | Master In Slave Out               | I/O    |     |                                           |

| MOSI          | Master Out Slave In               | I/O    |     |                                           |

| SPCK          | SPI Serial Clock                  | I/O    |     |                                           |

| NPCS0         | SPI Peripheral Chip Select 0      | I/O    | Low |                                           |

| NPCS1-NPCS3   | SPI Peripheral Chip Select 1 to 3 | Output | Low |                                           |

#### Table 3-1. Signal Description List (Continued)

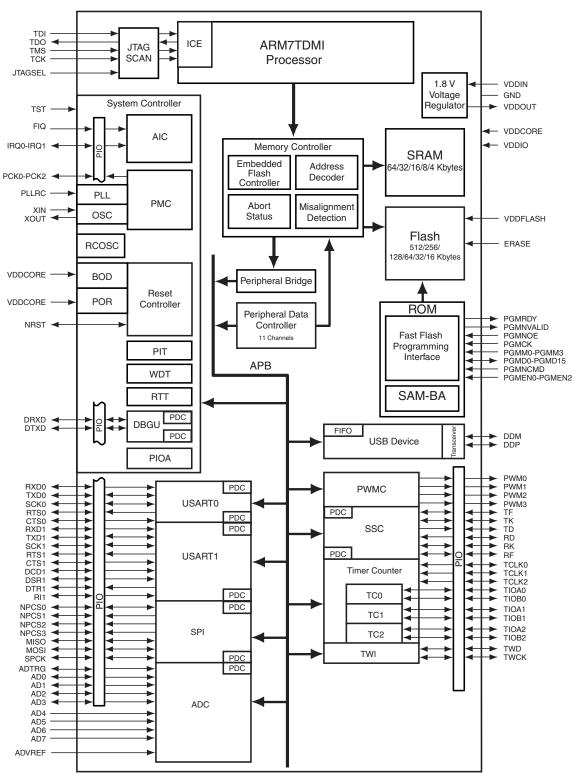

Figure 5-1. 3.3V System Single Power Supply Schematic

## 7. Processor and Architecture

#### 7.1 ARM7TDMI Processor

- RISC processor based on ARMv4T Von Neumann architecture

- Runs at up to 55 MHz, providing 0.9 MIPS/MHz

- Two instruction sets

- ARM<sup>®</sup> high-performance 32-bit instruction set

- Thumb<sup>®</sup> high code density 16-bit instruction set

- Three-stage pipeline architecture

- Instruction Fetch (F)

- Instruction Decode (D)

- Execute (E)

#### 7.2 Debug and Test Features

- Integrated EmbeddedICE<sup>™</sup> (embedded in-circuit emulator)

- Two watchpoint units

- Test access port accessible through a JTAG protocol

- Debug communication channel

- Debug Unit

- Two-pin UART

- Debug communication channel interrupt handling

- Chip ID Register

- IEEE1149.1 JTAG Boundary-scan on all digital pins

#### 7.3 Memory Controller

- Bus Arbiter

- Handles requests from the ARM7TDMI and the Peripheral DMA Controller

- Address decoder provides selection signals for

- Three internal 1 Mbyte memory areas

- One 256 Mbyte embedded peripheral area

- Abort Status Registers

- Source, Type and all parameters of the access leading to an abort are saved

- Facilitates debug by detection of bad pointers

- Misalignment Detector

- Alignment checking of all data accesses

- Abort generation in case of misalignment

- Remap Command

- Remaps the SRAM in place of the embedded non-volatile memory

- Allows handling of dynamic exception vectors

- Embedded Flash Controller

- Embedded Flash interface, up to three programmable wait states

- Prefetch buffer, buffering and anticipating the 16-bit requests, reducing the required wait states

- Key-protected program, erase and lock/unlock sequencer

- Single command for erasing, programming and locking operations

- Interrupt generation in case of forbidden operation

#### 7.4 Peripheral DMA Controller

- Handles data transfer between peripherals and memories

- Eleven channels: SAM7S512/256/128/64/321/161

- Nine channels: SAM7S32/16

- Two for each USART

- Two for the Debug Unit

- Two for the Serial Synchronous Controller

- Two for the Serial Peripheral Interface

- One for the Analog-to-digital Converter

- Low bus arbitration overhead

- One Master Clock cycle needed for a transfer from memory to peripheral

- Two Master Clock cycles needed for a transfer from peripheral to memory

- Next Pointer management for reducing interrupt latency requirements

- Peripheral DMA Controller (PDC) priority is as follows (from the highest priority to the lowest):

| Receive  | DBGU   |

|----------|--------|

| Receive  | USART0 |

| Receive  | USART1 |

| Receive  | SSC    |

| Receive  | ADC    |

| Receive  | SPI    |

| Transmit | DBGU   |

| Transmit | USART0 |

| Transmit | USART1 |

| Transmit | SSC    |

| Transmit | SPI    |

|          |        |

### 8. Memories

#### 8.1 SAM7S512

- 512 Kbytes of Flash Memory, dual plane

- 2 contiguous banks of 1024 pages of 256 bytes

- Fast access time, 30 MHz single-cycle access in Worst Case conditions

- Page programming time: 6 ms, including page auto-erase

- Page programming without auto-erase: 3 ms

- Full chip erase time: 15 ms

- 10,000 write cycles, 10-year data retention capability

- 32 lock bits, protecting 32 sectors of 64 pages

- Protection Mode to secure contents of the Flash

- 64 Kbytes of Fast SRAM

- Single-cycle access at full speed

#### 8.2 SAM7S256

- 256 Kbytes of Flash Memory, single plane

- 1024 pages of 256 bytes

- Fast access time, 30 MHz single-cycle access in Worst Case conditions

- Page programming time: 6 ms, including page auto-erase

- Page programming without auto-erase: 3 ms

- Full chip erase time: 15 ms

- 10,000 write cycles, 10-year data retention capability

- 16 lock bits, protecting 16 sectors of 64 pages

- Protection Mode to secure contents of the Flash

- 64 Kbytes of Fast SRAM

- Single-cycle access at full speed

#### 8.3 SAM7S128

- 128 Kbytes of Flash Memory, single plane

- 512 pages of 256 bytes

- Fast access time, 30 MHz single-cycle access in Worst Case conditions

- Page programming time: 6 ms, including page auto-erase

- Page programming without auto-erase: 3 ms

- Full chip erase time: 15 ms

- 10,000 write cycles, 10-year data retention capability

- 8 lock bits, protecting 8 sectors of 64 pages

- Protection Mode to secure contents of the Flash

- 32 Kbytes of Fast SRAM

- Single-cycle access at full speed

# 8.4 SAM7S64

- 64 Kbytes of Flash Memory, single plane

- 512 pages of 128 bytes

- Fast access time, 30 MHz single-cycle access in Worst Case conditions

- Page programming time: 6 ms, including page auto-erase

- Page programming without auto-erase: 3 ms

- Full chip erase time: 15 ms

- 10,000 write cycles, 10-year data retention capability

- 16 lock bits, protecting 16 sectors of 32 pages

- Protection Mode to secure contents of the Flash

- 16 Kbytes of Fast SRAM

- Single-cycle access at full speed

#### 8.5 SAM7S321/32

- 32 Kbytes of Flash Memory, single plane

- 256 pages of 128 bytes

- Fast access time, 30 MHz single-cycle access in Worst Case conditions

- Page programming time: 6 ms, including page auto-erase

- Page programming without auto-erase: 3 ms

- Full chip erase time: 15 ms

- 10,000 write cycles, 10-year data retention capability

- 8 lock bits, protecting 8 sectors of 32 pages

- Protection Mode to secure contents of the Flash

- 8 Kbytes of Fast SRAM

- Single-cycle access at full speed

#### 8.6 SAM7S161/16

- 16 Kbytes of Flash Memory, single plane

- 256 pages of 64 bytes

- Fast access time, 30 MHz single-cycle access in Worst Case conditions

- Page programming time: 6 ms, including page auto-erase

- Page programming without auto-erase: 3 ms

- Full chip erase time: 15 ms

- 10,000 write cycles, 10-year data retention capability

- 8 lock bits, protecting 8 sectors of 32 pages

- Protection Mode to secure contents of the Flash

- 4 Kbytes of Fast SRAM

- Single-cycle access at full speed

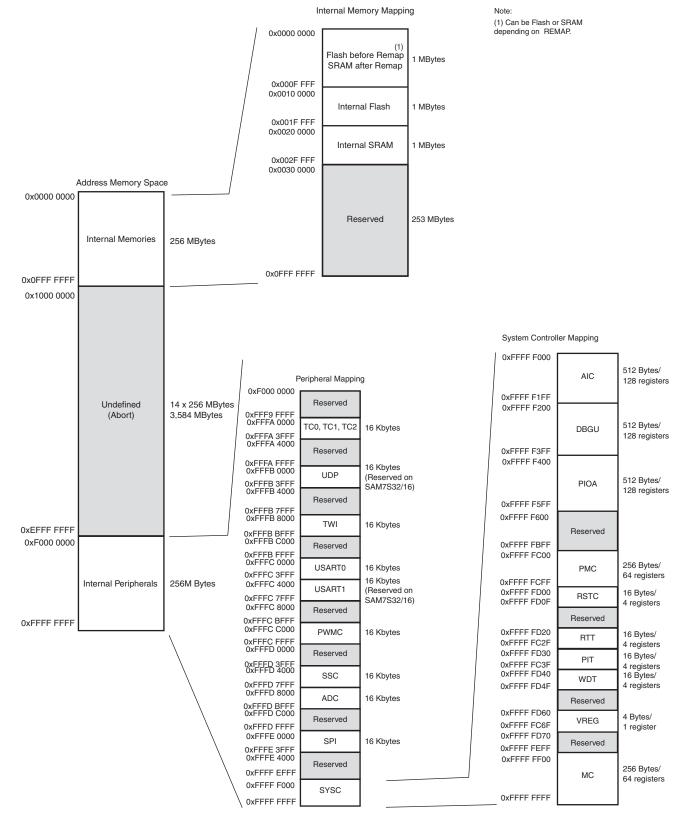

#### Figure 8-1. SAM SAM7S512/256/128/64/321/32/161/16 Memory Mapping

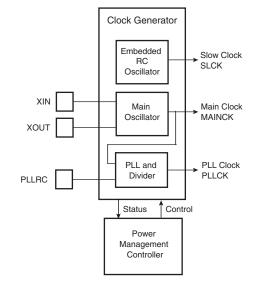

#### 9.2 Clock Generator

The Clock Generator embeds one low-power RC Oscillator, one Main Oscillator and one PLL with the following characteristics:

- RC Oscillator ranges between 22 kHz and 42 kHz

- Main Oscillator frequency ranges between 3 and 20 MHz

- Main Oscillator can be bypassed

- PLL output ranges between 80 and 220 MHz

It provides SLCK, MAINCK and PLLCK.

#### Figure 9-3. Clock Generator Block Diagram

#### 9.3 Power Management Controller

The Power Management Controller uses the Clock Generator outputs to provide:

- the Processor Clock PCK

- the Master Clock MCK

- the USB Clock UDPCK (not present on SAM7S32/16)

- all the peripheral clocks, independently controllable

- three programmable clock outputs

The Master Clock (MCK) is programmable from a few hundred Hz to the maximum operating frequency of the device.

The Processor Clock (PCK) switches off when entering processor idle mode, thus allowing reduced power consumption while waiting for an interrupt.

- One set of Chip ID Registers

- One Interface providing ICE Access Prevention

- Two-pin UART

- Implemented features are compatible with the USART

- Programmable Baud Rate Generator

- Parity, Framing and Overrun Error

- Automatic Echo, Local Loopback and Remote Loopback Channel Modes

- Debug Communication Channel Support

- Offers visibility of COMMRX and COMMTX signals from the ARM Processor

- Chip ID Registers

- Identification of the device revision, sizes of the embedded memories, set of peripherals

- Chip ID is 0x270B0A40 for AT91SAM7S512 Rev A

- Chip ID is 0x270B0A4F for AT91SAM7S512 Rev B

- Chip ID is 0x270D0940 for AT91SAM7S256 Rev A

- Chip ID is 0x270B0941 for AT91SAM7S256 Rev B

- Chip ID is 0x270B0942 for AT91SAM7S256 Rev C

- Chip ID is TBD for AT91SAM7S256 Rev D

- Chip ID is 0x270C0740 for AT91SAM7S128 Rev A

- Chip ID is 0x270A0741 for AT91SAM7S128 Rev B

- Chip ID is 0x270A0742 for AT91SAM7S128 Rev C

- Chip ID is TBD for AT91SAM7S128 Rev D

- Chip ID is 0x27090540 for AT91SAM7S64 Rev A

- Chip ID is 0x27090543 for AT91SAM7S64 Rev B

- Chip ID is 0x27090544 for AT91SAM7S64 Rev C

- Chip ID is 0x27080342 for AT91SAM7S321 Rev A

- Chip ID is 0x27080340 for AT91SAM7S32 Rev A

- Chip ID is 0x27080341 for AT91SAM7S32 Rev B

- Chip ID is 0x27050241 for AT9SAM7S161 Rev A

- Chip ID is 0x27050240 for AT91SAM7S16 Rev A

Note: Refer to the errata section of the datasheet for updates on chip ID.

#### 9.6 Periodic Interval Timer

20-bit programmable counter plus 12-bit interval counter

#### 9.7 Watchdog Timer

- 12-bit key-protected Programmable Counter running on prescaled SCLK

- Provides reset or interrupt signals to the system

- Counter may be stopped while the processor is in debug state or in idle mode

#### 9.8 Real-time Timer

- 32-bit free-running counter with alarm running on prescaled SCLK

- Programmable 16-bit prescaler for SLCK accuracy compensation

### 10. Peripherals

#### 10.1 User Interface

The User Peripherals are mapped in the 256 MBytes of address space between 0xF000 0000 and 0xFFF EFFF. Each peripheral is allocated 16 Kbytes of address space.

A complete memory map is provided in Figure 8-1 on page 20.

#### 10.2 Peripheral Identifiers

The SAM7S Series embeds a wide range of peripherals. Table 10-1 defines the Peripheral Identifiers of the SAM7S512/256/128/64/321/161. Table 10-2 defines the Peripheral Identifiers of the SAM7S32/16. A peripheral identifier is required for the control of the peripheral interrupt with the Advanced Interrupt Controller and for the control of the peripheral clock with the Power Management Controller.

| 0       | AIC                 | Advanced Interrupt Controller | FIQ  |

|---------|---------------------|-------------------------------|------|

| 1       | SYSC <sup>(1)</sup> | System                        |      |

| 2       | PIOA                | Parallel I/O Controller A     |      |

| 3       | Reserved            |                               |      |

| 4       | ADC <sup>(1)</sup>  | Analog-to Digital Converter   |      |

| 5       | SPI                 | Serial Peripheral Interface   |      |

| 6       | US0                 | USART 0                       |      |

| 7       | US1                 | USART 1                       |      |

| 8       | SSC                 | Synchronous Serial Controller |      |

| 9       | тwi                 | Two-wire Interface            |      |

| 10      | PWMC                | PWM Controller                |      |

| 11      | UDP                 | USB Device Port               |      |

| 12      | TC0                 | Timer/Counter 0               |      |

| 13      | TC1                 | Timer/Counter 1               |      |

| 14      | TC2                 | Timer/Counter 2               |      |

| 15 - 29 | Reserved            |                               |      |

| 30      | AIC                 | Advanced Interrupt Controller | IRQ0 |

| 31      | AIC                 | Advanced Interrupt Controller | IRQ1 |

#### Table 10-1. Peripheral Identifiers (SAM7S512/256/128/64/321/161)

Note: 1. Setting SYSC and ADC bits in the clock set/clear registers of the PMC has no effect. The System Controller is continuously clocked. The ADC clock is automatically started for the first conversion. In Sleep Mode the ADC clock is automatically stopped after each conversion.

Note: 1. Setting SYSC and ADC bits in the clock set/clear registers of the PMC has no effect. The System Controller is continuously clocked. The ADC clock is automatically started for the first conversion. In Sleep Mode the ADC clock is automatically stopped after each conversion.

| 0       | AIC                 | Advanced Interrupt Controller | FIQ  |  |  |  |

|---------|---------------------|-------------------------------|------|--|--|--|

| 1       | SYSC <sup>(1)</sup> | System                        |      |  |  |  |

| 2       | PIOA                | Parallel I/O Controller A     |      |  |  |  |

| 3       | Reserved            |                               |      |  |  |  |

| 4       | ADC <sup>(1)</sup>  | Analog-to Digital Converter   |      |  |  |  |

| 5       | SPI                 | Serial Peripheral Interface   |      |  |  |  |

| 6       | US                  | USART                         |      |  |  |  |

| 7       | Reserved            |                               |      |  |  |  |

| 8       | SSC                 | Synchronous Serial Controller |      |  |  |  |

| 9       | TWI                 | Two-wire Interface            |      |  |  |  |

| 10      | PWMC                | PWM Controller                |      |  |  |  |

| 11      | Reserved            |                               |      |  |  |  |

| 12      | TC0                 | Timer/Counter 0               |      |  |  |  |

| 13      | TC1                 | Timer/Counter 1               |      |  |  |  |

| 14      | TC2                 | Timer/Counter 2               |      |  |  |  |

| 15 - 29 | Reserved            |                               |      |  |  |  |

| 30      | AIC                 | Advanced Interrupt Controller | IRQ0 |  |  |  |

| 31      | Reserved            |                               |      |  |  |  |

Table 10-2. Peripheral Identifiers (SAM7S32/16)

#### 10.3 Peripheral Multiplexing on PIO Lines

The SAM7S Series features one PIO controller, PIOA, that multiplexes the I/O lines of the peripheral set.

PIO Controller A controls 32 lines (21 lines for SAM7S32/16). Each line can be assigned to one of two peripheral functions, A or B. Some of them can also be multiplexed with the analog inputs of the ADC Controller.

Table 10-3, "Multiplexing on PIO Controller A (SAM7S512/256/128/64/321/161)," on page 35 and Table 10-4, "Multiplexing on PIO Controller A (SAM7S32/16)," on page 36 define how the I/O lines of the peripherals A, B or the analog inputs are multiplexed on the PIO Controller A. The two columns "Function" and "Comments" have been inserted for the user's own comments; they may be used to track how pins are defined in an application.

Note that some peripheral functions that are output only may be duplicated in the table.

All pins reset in their Parallel I/O lines function are configured as input with the programmable pull-up enabled, so that the device is maintained in a static state as soon as a reset is detected.

#### 10.4 PIO Controller A Multiplexing

#### Table 10-3. Multiplexing on PIO Controller A (SAM7S512/256/128/64/321/161)

| PA0  | PWM0  | TIOA0 | High-Drive |  |

|------|-------|-------|------------|--|

| PA1  | PWM1  | TIOB0 | High-Drive |  |

| PA2  | PWM2  | SCK0  | High-Drive |  |

| PA3  | TWD   | NPCS3 | High-Drive |  |

| PA4  | TWCK  | TCLK0 |            |  |

| PA5  | RXD0  | NPCS3 |            |  |

| PA6  | TXD0  | PCK0  |            |  |

| PA7  | RTS0  | PWM3  |            |  |

| PA8  | CTS0  | ADTRG |            |  |

| PA9  | DRXD  | NPCS1 |            |  |

| PA10 | DTXD  | NPCS2 |            |  |

| PA11 | NPCS0 | PWM0  |            |  |

| PA12 | MISO  | PWM1  |            |  |

| PA13 | MOSI  | PWM2  |            |  |

| PA14 | SPCK  | PWM3  |            |  |

| PA15 | TF    | TIOA1 |            |  |

| PA16 | ТК    | TIOB1 |            |  |

| PA17 | TD    | PCK1  | AD0        |  |

| PA18 | RD    | PCK2  | AD1        |  |

| PA19 | RK    | FIQ   | AD2        |  |

| PA20 | RF    | IRQ0  | AD3        |  |

| PA21 | RXD1  | PCK1  |            |  |

| PA22 | TXD1  | NPCS3 |            |  |

| PA23 | SCK1  | PWM0  |            |  |

| PA24 | RTS1  | PWM1  |            |  |

| PA25 | CTS1  | PWM2  |            |  |

| PA26 | DCD1  | TIOA2 |            |  |

| PA27 | DTR1  | TIOB2 |            |  |

| PA28 | DSR1  | TCLK1 |            |  |

| PA29 | RI1   | TCLK2 |            |  |

| PA30 | IRQ1  | NPCS2 |            |  |

| PA31 | NPCS1 | PCK2  |            |  |

#### 10.5 Serial Peripheral Interface

- Supports communication with external serial devices

- Four chip selects with external decoder allow communication with up to 15 peripherals

- Serial memories, such as DataFlash® and 3-wire EEPROMs

- Serial peripherals, such as ADCs, DACs, LCD Controllers, CAN Controllers and Sensors

- External co-processors

- Master or slave serial peripheral bus interface

- 8- to 16-bit programmable data length per chip select

- Programmable phase and polarity per chip select

- Programmable transfer delays between consecutive transfers and between clock and data per chip select

- Programmable delay between consecutive transfers

- Selectable mode fault detection

- Maximum frequency at up to Master Clock

#### 10.6 Two-wire Interface

- Master Mode only (SAM7S512/256/128/64/321/32)

- Master, Multi-Master and Slave Mode support (SAM7S161/16)

- General Call supported in Slave Mode (SAM7S161/16)

- Compatibility with I<sup>2</sup>C compatible devices (refer to the TWI sections of the datasheet)

- One, two or three bytes internal address registers for easy Serial Memory access

- 7-bit or 10-bit slave addressing

- Sequential read/write operations

#### 10.7 USART

- Programmable Baud Rate Generator

- 5- to 9-bit full-duplex synchronous or asynchronous serial communications

- 1, 1.5 or 2 stop bits in Asynchronous Mode

- 1 or 2 stop bits in Synchronous Mode

- Parity generation and error detection

- Framing error detection, overrun error detection

- MSB or LSB first

- Optional break generation and detection

- By 8 or by 16 over-sampling receiver frequency

- Hardware handshaking RTS CTS

- Modem Signals Management DTR-DSR-DCD-RI on USART1 (not present on SAM7S32/16)

- Receiver time-out and transmitter timeguard

- Multi-drop Mode with address generation and detection

- RS485 with driver control signal

- ISO7816, T = 0 or T = 1 Protocols for interfacing with smart cards

- NACK handling, error counter with repetition and iteration limit

- IrDA modulation and demodulation

- Communication at up to 115.2 Kbps

- Test Modes

- Remote Loopback, Local Loopback, Automatic Echo

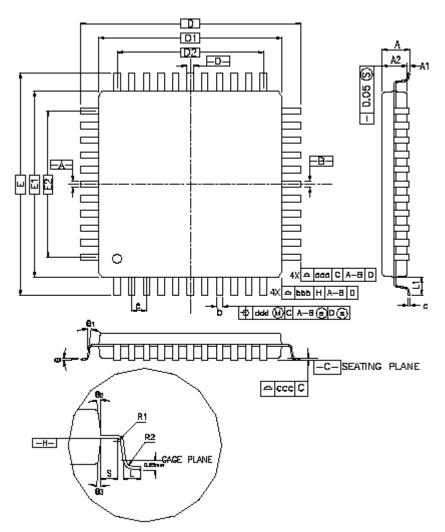

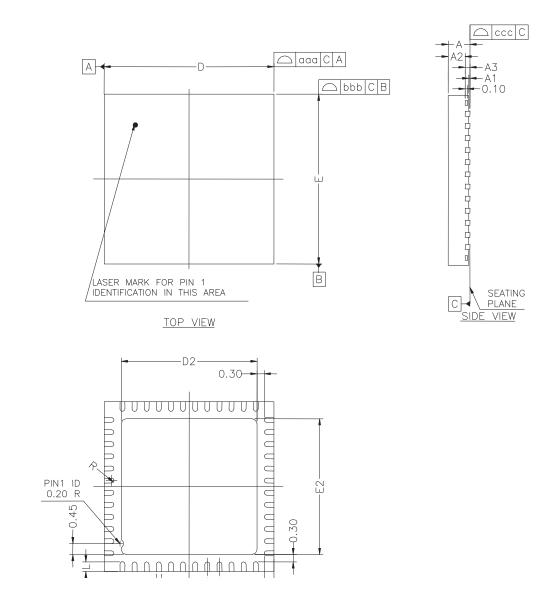

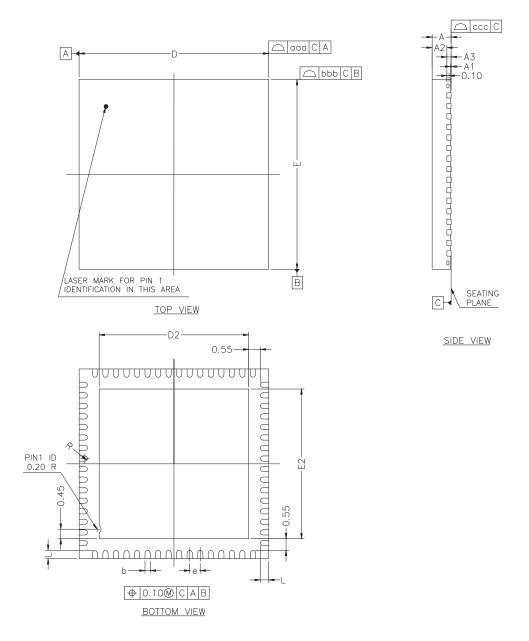

## 11. Package Drawings

The SAM7S series devices are available in LQFP and QFN package types.

#### 11.1 LQFP Packages

#### Figure 11-1. 48-and 64-lead LQFP Package Drawing

#### 11.2 QFN Packages

Figure 11-2. 48-pad QFN Package

## 12. SAM7S Ordering Information

| MLR A Ordering<br>Code               | MLR B<br>Ordering Code                 | MLR C<br>Ordering Code               | MLR D<br>Ordering Code               | Package           | Package<br>Type | Temperature<br>Operating<br>Range |

|--------------------------------------|----------------------------------------|--------------------------------------|--------------------------------------|-------------------|-----------------|-----------------------------------|

| AT91SAM7S16-AU<br>AT91SAM7S16-MU     | _                                      | _                                    | _                                    | LQFP 48<br>QFN 48 | Green           | Industrial<br>(-40· C to 85· C)   |

| AT91SAM7S161-AU                      | _                                      | _                                    | _                                    | LQFP 64           | Green           | Industrial<br>(-40· C to 85· C)   |

| AT91SAM7S32-AU-001<br>AT91SAM7S32-MU | AT91SAM7S32B-AU<br>AT91SAM7S32B-MU     |                                      |                                      | LQFP 48<br>QFN 48 | Green           | Industrial<br>(-40· C to 85· C)   |

| AT91SAM7S321-AU<br>AT91SAM7S321-MU   | _                                      | _                                    | _                                    | LQFP 64<br>QFN 64 | Green           | Industrial<br>(-40- C to 85- C)   |

| _                                    | AT91SAM7S64B-AU<br>AT91SAM7S64B-MU     | AT91SAM7S64C-AU<br>AT91SAM7S64C-MU   | _                                    | LQFP 64<br>QFN 64 | Green           | Industrial<br>(-40- C to 85- C)   |

| _                                    | AT91SAM7S128-AU-001<br>AT91SAM7S128-MU | AT91SAM7S128C-AU<br>AT91SAM7S128C-MU | AT91SAM7S128D-AU<br>AT91SAM7S128D-MU | LQFP 64<br>QFN 64 | Green           | Industrial<br>(-40· C to 85· C)   |

| _                                    | AT91SAM7S256-AU-001<br>AT91SAM7S256-MU | AT91SAM7S256C-AU<br>AT91SAM7S256C-MU | AT91SAM7S256D-AU<br>AT91SAM7S256D-MU | LQFP 64<br>QFN 64 | Green           | Industrial<br>(-40- C to 85- C)   |

| AT91SAM7S512-AU<br>AT91SAM7S512-MU   | AT91SAM7S512B-AU<br>AT91SAM7S512B-MU   | _                                    | -                                    | LQFP 64<br>QFN 64 | Green           | Industrial<br>(-40· C to 85· C)   |

Table 12-1. SAM7S Series Ordering Information

# Atmel Enabling Unlimited Possibilities<sup>®</sup>

Atmel Corporation 1600 Technology Drive San Jose, CA 95110 USA Tel: (+1) (408) 441-0311 Fax: (+1) (408) 487-2600 www.atmel.com Atmel Asia Limited Unit 01-5 & 16, 19F BEA Tower, Millennium City 5 418 Kwun Tong Roa Kwun Tong, Kowloon HONG KONG Tel: (+852) 2245-6100 Fax: (+852) 2722-1369 Atmel Munich GmbH Business Campus Parkring 4 D-85748 Garching b. Munich GERMANY Tel: (+49) 89-31970-0 Fax: (+49) 89-3194621 Atmel Japan G.K. 16F Shin-Osaki Kangyo Bldg 1-6-4 Osaki, Shinagawa-ku Tokyo 141-0032 JAPAN Tel: (+81) (3) 6417-0300 Fax: (+81) (3) 6417-0370

© 2012 Atmel Corporation. All rights reserved. / Rev.: 6175KS-ATARM-25-Oct-12

Atmel<sup>®</sup>, Atmel logo and combinations thereof, Enabling Unlimited Possibilities<sup>®</sup>, SAM-BA<sup>®</sup> and others, are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Windows<sup>®</sup> and others are registered trademarks or trademarks of Microsoft Corporation in the US and/or in other countries. ARM<sup>®</sup>, the ARM Powered<sup>®</sup> logo, ARM7TDMI<sup>®</sup>, Thumb<sup>®</sup>, and others are registered trademarks or trademarks of ARM Limited. Other terms and product names may be the trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.