Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Dataila                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Details                    |                                                                          |

| Product Status             | Obsolete                                                                 |

| Core Processor             | ARM7®                                                                    |

| Core Size                  | 16/32-Bit                                                                |

| Speed                      | 55MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, SSC, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 16K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                            |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 64-QFN (9x9)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at91sam7s64-mu |

- Debug Unit (DBGU)

- 2-wire UART and Support for Debug Communication Channel interrupt, Programmable ICE Access Prevention

- Mode for General Purpose 2-wire UART Serial Communication

- Periodic Interval Timer (PIT)

- 20-bit Programmable Counter plus 12-bit Interval Counter

- Windowed Watchdog (WDT)

- 12-bit key-protected Programmable Counter

- Provides Reset or Interrupt Signals to the System

- Counter May Be Stopped While the Processor is in Debug State or in Idle Mode

- Real-time Timer (RTT)

- 32-bit Free-running Counter with Alarm

- Runs Off the Internal RC Oscillator

- One Parallel Input/Output Controller (PIOA)

- Thirty-two (SAM7S512/256/128/64/321/161) or twenty-one (SAM7S32/16) Programmable I/O Lines Multiplexed with up to Two Peripheral I/Os

- Input Change Interrupt Capability on Each I/O Line

- Individually Programmable Open-drain, Pull-up resistor and Synchronous Output

- Eleven (SAM7S512/256/128/64/321/161) or Nine (SAM7S32/16) Peripheral DMA Controller (PDC) Channels

- One USB 2.0 Full Speed (12 Mbits per Second) Device Port (Except for the SAM7S32/16).

- On-chip Transceiver, 328-byte Configurable Integrated FIFOs

- One Synchronous Serial Controller (SSC)

- Independent Clock and Frame Sync Signals for Each Receiver and Transmitter

- I2S Analog Interface Support, Time Division Multiplex Support

- High-speed Continuous Data Stream Capabilities with 32-bit Data Transfer

- Two (SAM7S512/256/128/64/321/161) or One (SAM7S32/16) Universal Synchronous/Asynchronous Receiver Transmitters (USART)

- Individual Baud Rate Generator, IrDA® Infrared Modulation/Demodulation

- Support for ISO7816 T0/T1 Smart Card, Hardware Handshaking, RS485 Support

- Full Modem Line Support on USART1 (SAM7S512/256/128/64/321/161)

- One Master/Slave Serial Peripheral Interface (SPI)

- 8- to 16-bit Programmable Data Length, Four External Peripheral Chip Selects

- One Three-channel 16-bit Timer/Counter (TC)

- Three External Clock Input and Two Multi-purpose I/O Pins per Channel (SAM7S512/256/128/64/321/161)

- One External Clock Input and Two Multi-purpose I/O Pins for the first Two Channels Only (SAM7S32/16)

- Double PWM Generation, Capture/Waveform Mode, Up/Down Capability

- One Four-channel 16-bit PWM Controller (PWMC)

- One Two-wire Interface (TWI)

- Master Mode Support Only, All Two-wire Atmel EEPROMs and I<sup>2</sup>C Compatible Devices Supported (SAM7S512/256/128/64/321/32)

- Master, Multi-Master and Slave Mode Support, All Two-wire Atmel EEPROMs and I<sup>2</sup>C Compatible Devices Supported (SAM7S161/16)

- One 8-channel 10-bit Analog-to-Digital Converter, Four Channels Multiplexed with Digital I/Os

- SAM-BA<sup>™</sup> Boot Assistant

- Default Boot program

- Interface with SAM-BA Graphic User Interface

- IEEE® 1149.1 JTAG Boundary Scan on All Digital Pins

- 5V-tolerant I/Os, including Four High-current Drive I/O lines, Up to 16 mA Each (SAM7S161/16 I/Os Not 5V-tolerant)

- Power Supplies

- Embedded 1.8V Regulator, Drawing up to 100 mA for the Core and External Components

- 3.3V or 1.8V VDDIO I/O Lines Power Supply, Independent 3.3V VDDFLASH Flash Power Supply

- 1.8V VDDCORE Core Power Supply with Brown-out Detector

- Fully Static Operation: Up to 55 MHz at 1.65V and 85. C Worst Case Conditions

- Available in 64-lead LQFP Green or 64-pad QFN Green Package (SAM7S512/256/128/64/321/161) and 48-lead LQFP Green or 48-pad QFN Green Package (SAM7S32/16)

# 1. Description

Atmel's SAM7S is a series of low pincount Flash microcontrollers based on the 32-bit ARM RISC processor. It features a high-speed Flash and an SRAM, a large set of peripherals, including a USB 2.0 device (except for the SAM7S32 and SAM7S16), and a complete set of system functions minimizing the number of external components. The device is an ideal migration path for 8-bit microcontroller users looking for additional performance and extended memory.

The embedded Flash memory can be programmed in-system via the JTAG-ICE interface or via a parallel interface on a production programmer prior to mounting. Built-in lock bits and a security bit protect the firmware from accidental overwrite and preserves its confidentiality.

The SAM7S Series system controller includes a reset controller capable of managing the power-on sequence of the microcontroller and the complete system. Correct device operation can be monitored by a built-in brownout detector and a watchdog running off an integrated RC oscillator.

The SAM7S Series are general-purpose microcontrollers. Their integrated USB Device port makes them ideal devices for peripheral applications requiring connectivity to a PC or cellular phone. Their aggressive price point and high level of integration pushes their scope of use far into the cost-sensitive, high-volume consumer market.

# 1.1 Configuration Summary of the SAM7S512, SAM7S256, SAM7S128, SAM7S64, SAM7S321, SAM7S32, SAM7S161 and SAM7S16

The SAM7S512, SAM7S256, SAM7S128, SAM7S64, SAM7S321, SAM7S32, SAM7S161 and SAM7S16 differ in memory size, peripheral set and package. Table 1-1 summarizes the configuration of the six devices.

Except for the SAM7S32/16, all other SAM7S devices are package and pinout compatible.

Table 1-1. Configuration Summary

|          | - June 1   |                  | <b>,</b>     | 1         |                |                      |   |    |                  |     |    | _               |

|----------|------------|------------------|--------------|-----------|----------------|----------------------|---|----|------------------|-----|----|-----------------|

|          |            |                  |              |           |                |                      |   |    |                  |     |    |                 |

| SAM7S512 | 512 Kbytes | Master           | dual plane   | 64 Kbytes | 1              | 2 <sup>(1)</sup> (2) | 2 | 11 | 3                | Yes | 32 | LQFP/<br>QFN 64 |

| SAM7S256 | 256 Kbytes | Master           | single plane | 64 Kbytes | 1              | 2 <sup>(1)</sup> (2) | 2 | 11 | 3                | Yes | 32 | LQFP/<br>QFN 64 |

| SAM7S128 | 128 Kbytes | Master           | single plane | 32 Kbytes | 1              | 2 <sup>(1) (2)</sup> | 2 | 11 | 3                | Yes | 32 | LQFP/<br>QFN 64 |

| SAM7S64  | 64 Kbytes  | Master           | single plane | 16 Kbytes | 1              | 2 <sup>(2)</sup>     | 2 | 11 | 3                | Yes | 32 | LQFP/<br>QFN 64 |

| SAM7S321 | 32 Kbytes  | Master           | single plane | 8 Kbytes  | 1              | 2 <sup>(2)</sup>     | 2 | 11 | 3                | Yes | 32 | LQFP/<br>QFN 64 |

| SAM7S32  | 32 Kbytes  | Master           | single plane | 8 Kbytes  | not<br>present | 1                    | 1 | 9  | 3 <sup>(3)</sup> | Yes | 21 | LQFP/<br>QFN 48 |

| SAM7S161 | 16 Kbytes  | Master/<br>Slave | single plane | 4 Kbytes  | 1              | 2 <sup>(2)</sup>     | 2 | 11 | 3                | No  | 32 | LQFP            |

| SAM7S16  | 16 Kbytes  | Master/<br>Slave | single plane | 4 Kbytes  | not<br>present | 1                    | 1 | 9  | 3 <sup>(3)</sup> | No  | 21 | LQFP/<br>QFN 48 |

Notes: 1. Fractional Baud Rate.

- 2. Full modem line support on USART1.

- 3. Only two TC channels are accessible through the PIO.

Table 3-1. Signal Description List (Continued)

| Table 0-1. Olgilar | able 3-1. Signal Description List (Continued) |        |      |                                   |  |  |  |

|--------------------|-----------------------------------------------|--------|------|-----------------------------------|--|--|--|

|                    |                                               |        |      |                                   |  |  |  |

|                    |                                               | "      | l .  |                                   |  |  |  |

| TWD                | Two-wire Serial Data                          | I/O    |      |                                   |  |  |  |

| TWCK               | Two-wire Serial Clock                         | I/O    |      |                                   |  |  |  |

|                    |                                               |        |      |                                   |  |  |  |

| AD0-AD3            | Analog Inputs                                 | Analog |      | Digital pulled-up inputs at reset |  |  |  |

| AD4-AD7            | Analog Inputs                                 | Analog |      | Analog Inputs                     |  |  |  |

| ADTRG              | ADC Trigger                                   | Input  |      |                                   |  |  |  |

| ADVREF             | ADC Reference                                 | Analog |      |                                   |  |  |  |

|                    |                                               |        |      |                                   |  |  |  |

| PGMEN0-PGMEN2      | Programming Enabling                          | Input  |      |                                   |  |  |  |

| PGMM0-PGMM3        | Programming Mode                              | Input  |      |                                   |  |  |  |

| PGMD0-PGMD15       | Programming Data                              | I/O    |      | PGMD0-PGMD7 only on SAM7S32/16    |  |  |  |

| PGMRDY             | Programming Ready                             | Output | High |                                   |  |  |  |

| PGMNVALID          | Data Direction                                | Output | Low  |                                   |  |  |  |

| PGMNOE             | Programming Read                              | Input  | Low  |                                   |  |  |  |

| PGMCK              | Programming Clock                             | Input  |      |                                   |  |  |  |

| PGMNCMD            | Programming Command                           | Input  | Low  |                                   |  |  |  |

Note: 1. Refer to Section 6. "I/O Lines Considerations" on page 14.

# 4.2 64-lead LQFP and 64-pad QFN Pinout

Table 4-1. SAM7S512/256/128/64/321/161 Pinout<sup>(1)</sup>

| 1  | ADVREF         |

|----|----------------|

| 2  | GND            |

| 3  | AD4            |

| 4  | AD5            |

| 5  | AD6            |

| 6  | AD7            |

| 7  | VDDIN          |

| 8  | VDDOUT         |

| 9  | PA17/PGMD5/AD0 |

| 10 | PA18/PGMD6/AD1 |

| 11 | PA21/PGMD9     |

| 12 | VDDCORE        |

| 13 | PA19/PGMD7/AD2 |

| 14 | PA22/PGMD10    |

| 15 | PA23/PGMD11    |

| 16 | PA20/PGMD8/AD3 |

| 17    | GND                      |  |  |  |  |

|-------|--------------------------|--|--|--|--|

| 18    | VDDIO                    |  |  |  |  |

| 19    | PA16/PGMD4               |  |  |  |  |

| 20    | PA15/PGMD3               |  |  |  |  |

| 21    | PA14/PGMD2               |  |  |  |  |

| 22    | PA13/PGMD1               |  |  |  |  |

| 23    | PA24/PGMD12              |  |  |  |  |

| 24    | VDDCORE                  |  |  |  |  |

| 25    | PA25/PGMD13              |  |  |  |  |

| 26    | PA26/PGMD14              |  |  |  |  |

| 27    | PA12/PGMD0               |  |  |  |  |

| 28    | PA11/PGMM3               |  |  |  |  |

| 29    | PA10/PGMM2               |  |  |  |  |

| 30    | PA9/PGMM1                |  |  |  |  |

| 31    | PA8/PGMM0                |  |  |  |  |

| 32    | PA7/PGMNVALID            |  |  |  |  |

| 0 = 1 | OFN poolsons must be son |  |  |  |  |

| 33 | TDI         |

|----|-------------|

| 34 | PA6/PGMNOE  |

| 35 | PA5/PGMRDY  |

| 36 | PA4/PGMNCMD |

| 37 | PA27/PGMD15 |

| 38 | PA28        |

| 39 | NRST        |

| 40 | TST         |

| 41 | PA29        |

| 42 | PA30        |

| 43 | PA3         |

| 44 | PA2/PGMEN2  |

| 45 | VDDIO       |

| 46 | GND         |

| 47 | PA1/PGMEN1  |

| 48 | PA0/PGMEN0  |

|    |             |

| 49 | TDO       |

|----|-----------|

| 50 | JTAGSEL   |

| 51 | TMS       |

| 52 | PA31      |

| 53 | TCK       |

| 54 | VDDCORE   |

| 55 | ERASE     |

| 56 | DDM       |

| 57 | DDP       |

| 58 | VDDIO     |

| 59 | VDDFLASH  |

| 60 | GND       |

| 61 | XOUT      |

| 62 | XIN/PGMCK |

| 63 | PLLRC     |

| 64 | VDDPLL    |

|    |           |

Note: 1. The bottom pad of the QFN package must be connected to ground.

# 5. Power Considerations

# 5.1 Power Supplies

The SAM7S Series has six types of power supply pins and integrates a voltage regulator, allowing the device to be supplied with only one voltage. The six power supply pin types are:

- VDDIN pin. It powers the voltage regulator and the ADC; voltage ranges from 3.0V to 3.6V, 3.3V nominal.

- VDDOUT pin. It is the output of the 1.8V voltage regulator.

- VDDIO pin. It powers the I/O lines and the USB transceivers; dual voltage range is supported. Ranges from 3.0V to 3.6V, 3.3V nominal or from 1.65V to 1.95V, 1.8V nominal. Note that supplying less than 3.0V to VDDIO prevents any use of the USB transceivers.

- VDDFLASH pin. It powers a part of the Flash and is required for the Flash to operate correctly; voltage ranges from 3.0V to 3.6V, 3.3V nominal.

- VDDCORE pins. They power the logic of the device; voltage ranges from 1.65V to 1.95V, 1.8V typical. It can be connected to the VDDOUT pin with decoupling capacitor. VDDCORE is required for the device, including its embedded Flash, to operate correctly.

During startup, core supply voltage (VDDCORE) slope must be superior or equal to 6V/ms.

VDDPLL pin. It powers the oscillator and the PLL. It can be connected directly to the VDDOUT pin.

No separate ground pins are provided for the different power supplies. Only GND pins are provided and should be connected as shortly as possible to the system ground plane.

In order to decrease current consumption, if the voltage regulator and the ADC are not used, VDDIN, ADVREF, AD4, AD5, AD6 and AD7 should be connected to GND. In this case VDDOUT should be left unconnected.

# 5.2 Power Consumption

The SAM7S Series has a static current of less than 60  $\mu$ A on VDDCORE at 25°C, including the RC oscillator, the voltage regulator and the power-on reset. When the brown-out detector is activated, 20  $\mu$ A static current is added.

The dynamic power consumption on VDDCORE is less than 50 mA at full speed when running out of the Flash. Under the same conditions, the power consumption on VDDFLASH does not exceed 10 mA.

# 5.3 Voltage Regulator

The SAM7S Series embeds a voltage regulator that is managed by the System Controller.

In Normal Mode, the voltage regulator consumes less than 100 µA static current and draws 100 mA of output current.

The voltage regulator also has a Low-power Mode. In this mode, it consumes less than 25  $\mu$ A static current and draws 1 mA of output current.

Adequate output supply decoupling is mandatory for VDDOUT to reduce ripple and avoid oscillations. The best way to achieve this is to use two capacitors in parallel: one external 470 pF (or 1 nF) NPO capacitor must be connected between VDDOUT and GND as close to the chip as possible. One external 2.2  $\mu$ F (or 3.3  $\mu$ F) X7R capacitor must be connected between VDDOUT and GND.

Adequate input supply decoupling is mandatory for VDDIN in order to improve startup stability and reduce source voltage drop. The input decoupling capacitor should be placed close to the chip. For example, two capacitors can be used in parallel: 100 nF NPO and  $4.7 \mu\text{F X7R}$ .

# 5.4 Typical Powering Schematics

The SAM7S Series supports a 3.3V single supply mode. The internal regulator is connected to the 3.3V source and its output feeds VDDCORE and the VDDPLL. Figure 5-1 shows the power schematics to be used for USB bus-powered systems.

# 6. I/O Lines Considerations

#### 6.1 JTAG Port Pins

TMS, TDI and TCK are schmitt trigger inputs. TMS and TCK are 5-V tolerant, TDI is not. TMS, TDI and TCK do not integrate a pull-up resistor.

TDO is an output, driven at up to VDDIO, and has no pull-up resistor.

The JTAGSEL pin is used to select the JTAG boundary scan when asserted at a high level. The JTAGSEL pin integrates a permanent pull-down resistor of about 15 k $\Omega$  to GND, so that it can be left unconnected for normal operations.

#### 6.2 Test Pin

The TST pin is used for manufacturing test, fast programming mode or SAM-BA Boot Recovery of the SAM7S Series when asserted high. The TST pin integrates a permanent pull-down resistor of about 15 k $\Omega$  to GND, so that it can be left unconnected for normal operations.

To enter fast programming mode, the TST pin and the PA0 and PA1 pins should be tied high and PA2 tied to low.

To enter SAM-BA Boot Recovery, the TST pin and the PA0, PA1 and PA2 pins should be tied high for at least 10 seconds. Then a power cycle of the board is mandatory.

Driving the TST pin at a high level while PA0 or PA1 is driven at 0 leads to unpredictable results.

#### 6.3 Reset Pin

The NRST pin is bidirectional with an open drain output buffer. It is handled by the on-chip reset controller and can be driven low to provide a reset signal to the external components or asserted low externally to reset the microcontroller. There is no constraint on the length of the reset pulse, and the reset controller can guarantee a minimum pulse length. This allows connection of a simple push-button on the pin NRST as system user reset, and the use of the signal NRST to reset all the components of the system.

The NRST pin integrates a permanent pull-up resistor to VDDIO.

#### 6.4 ERASE Pin

The ERASE pin is used to re-initialize the Flash content and some of its NVM bits. It integrates a permanent pull-down resistor of about 15 k $\Omega$  to GND, so that it can be left unconnected for normal operations.

#### 6.5 PIO Controller A Lines

- All the I/O lines PA0 to PA31on SAM7S512/256/128/64/321 (PA0 to PA20 on SAM7S32) are 5V-tolerant and all integrate a programmable pull-up resistor.

- All the I/O lines PA0 to PA31 on SAM7S161 (PA0 to PA20 on SAM7S16) are not 5V-tolerant and all integrate a

programmable pull-up resistor.

Programming of this pull-up resistor is performed independently for each I/O line through the PIO controllers.

5V-tolerant means that the I/O lines can drive voltage level according to VDDIO, but can be driven with a voltage of up to 5.5V. However, driving an I/O line with a voltage over VDDIO while the programmable pull-up resistor is enabled will create a current path through the pull-up resistor from the I/O line to VDDIO. Care should be taken, in particular at reset, as all the I/O lines default to input with the pull-up resistor enabled at reset.

#### 6.6 I/O Line Drive Levels

The PIO lines PA0 to PA3 are high-drive current capable. Each of these I/O lines can drive up to 16 mA permanently. The remaining I/O lines can draw only 8 mA.

However, the total current drawn by all the I/O lines cannot exceed 150 mA (100 mA for SAM7S32/16).

#### 7. Processor and Architecture

#### 7.1 ARM7TDMI Processor

- RISC processor based on ARMv4T Von Neumann architecture

- Runs at up to 55 MHz, providing 0.9 MIPS/MHz

- Two instruction sets

- ARM® high-performance 32-bit instruction set

- Thumb<sup>®</sup> high code density 16-bit instruction set

- Three-stage pipeline architecture

- Instruction Fetch (F)

- Instruction Decode (D)

- Execute (E)

### 7.2 Debug and Test Features

- Integrated EmbeddedICE<sup>™</sup> (embedded in-circuit emulator)

- Two watchpoint units

- Test access port accessible through a JTAG protocol

- Debug communication channel

- Debug Unit

- Two-pin UART

- Debug communication channel interrupt handling

- Chip ID Register

- IEEE1149.1 JTAG Boundary-scan on all digital pins

# 7.3 Memory Controller

- Bus Arbiter

- Handles requests from the ARM7TDMI and the Peripheral DMA Controller

- Address decoder provides selection signals for

- Three internal 1 Mbyte memory areas

- One 256 Mbyte embedded peripheral area

- Abort Status Registers

- Source, Type and all parameters of the access leading to an abort are saved

- Facilitates debug by detection of bad pointers

- Misalignment Detector

- Alignment checking of all data accesses

- Abort generation in case of misalignment

- Remap Command

- Remaps the SRAM in place of the embedded non-volatile memory

- Allows handling of dynamic exception vectors

- Embedded Flash Controller

- Embedded Flash interface, up to three programmable wait states

- Prefetch buffer, buffering and anticipating the 16-bit requests, reducing the required wait states

- Key-protected program, erase and lock/unlock sequencer

- Single command for erasing, programming and locking operations

- Interrupt generation in case of forbidden operation

# 7.4 Peripheral DMA Controller

- Handles data transfer between peripherals and memories

- Eleven channels: SAM7S512/256/128/64/321/161

- Nine channels: SAM7S32/16

- Two for each USART

- Two for the Debug Unit

- Two for the Serial Synchronous Controller

- Two for the Serial Peripheral Interface

- One for the Analog-to-digital Converter

- Low bus arbitration overhead

- One Master Clock cycle needed for a transfer from memory to peripheral

- Two Master Clock cycles needed for a transfer from peripheral to memory

- Next Pointer management for reducing interrupt latency requirements

- Peripheral DMA Controller (PDC) priority is as follows (from the highest priority to the lowest):

| Receive  | DBGU   |

|----------|--------|

| Receive  | USART0 |

| Receive  | USART1 |

| Receive  | SSC    |

| Receive  | ADC    |

| Receive  | SPI    |

| Transmit | DBGU   |

| Transmit | USART0 |

| Transmit | USART1 |

| Transmit | SSC    |

| Transmit | SPI    |

- Fast access time, 30 MHz single-cycle access in Worst Case conditions

- Page programming time: 6 ms, including page auto-erase

- Page programming without auto-erase: 3 ms

- Full chip erase time: 15 ms

- 10,000 write cycles, 10-year data retention capability

- 16 lock bits, protecting 16 sectors of 32 pages

- Protection Mode to secure contents of the Flash

- 16 Kbytes of Fast SRAM

- Single-cycle access at full speed

#### 8.5 SAM7S321/32

- 32 Kbytes of Flash Memory, single plane

- 256 pages of 128 bytes

- Fast access time, 30 MHz single-cycle access in Worst Case conditions

- Page programming time: 6 ms, including page auto-erase

- Page programming without auto-erase: 3 ms

- Full chip erase time: 15 ms

- 10,000 write cycles, 10-year data retention capability

- 8 lock bits, protecting 8 sectors of 32 pages

- Protection Mode to secure contents of the Flash

- 8 Kbvtes of Fast SRAM

- Single-cycle access at full speed

#### 8.6 SAM7S161/16

- 16 Kbytes of Flash Memory, single plane

- 256 pages of 64 bytes

- Fast access time, 30 MHz single-cycle access in Worst Case conditions

- Page programming time: 6 ms, including page auto-erase

- Page programming without auto-erase: 3 ms

- Full chip erase time: 15 ms

- 10,000 write cycles, 10-year data retention capability

- 8 lock bits, protecting 8 sectors of 32 pages

- Protection Mode to secure contents of the Flash

- 4 Kbytes of Fast SRAM

- Single-cycle access at full speed

The 8 NVM bits are software programmable through the EFC User Interface. The command "Set Lock Bit" enables the protection. The command "Clear Lock Bit" unlocks the lock region.

Asserting the ERASE pin clears the lock bits, thus unlocking the entire Flash.

#### 8.8.3.6 SAM7S161/16

The Embedded Flash Controller manages 8 lock bits to protect 8 regions of the flash against inadvertent flash erasing or programming commands. The SAM7S161/16 contains 8 lock regions and each lock region contains 32 pages of 64 bytes. Each lock region has a size of 2 Kbytes.

If a locked-region's erase or program command occurs, the command is aborted and the LOCKE bit in the MC\_FSR register rises and the interrupt line rises if the LOCKE bit has been written at 1 in the MC\_FMR register.

The 8 NVM bits are software programmable through the EFC User Interface. The command "Set Lock Bit" enables the protection. The command "Clear Lock Bit" unlocks the lock region.

Asserting the ERASE pin clears the lock bits, thus unlocking the entire Flash.

Table 8-1 summarizes the configuration of the eight devices.

Table 8-1. Flash Configuration Summary

| SAM7S512    | 32 | 64 | 256 bytes |

|-------------|----|----|-----------|

| SAM7S256    | 16 | 64 | 256 bytes |

| SAM7S128    | 8  | 64 | 256 bytes |

| SAM7S64     | 16 | 32 | 128 bytes |

| SAM7S321/32 | 8  | 32 | 128 bytes |

| SAM7S161/16 | 8  | 32 | 64 bytes  |

#### 8.8.4 Security Bit Feature

The SAM7S Series features a security bit, based on a specific NVM Bit. When the security is enabled, any access to the Flash, either through the ICE interface or through the Fast Flash Programming Interface, is forbidden. This ensures the confidentiality of the code programmed in the Flash.

This security bit can only be enabled, through the Command "Set Security Bit" of the EFC User Interface. Disabling the security bit can only be achieved by asserting the ERASE pin at 1, and after a full flash erase is performed. When the security bit is deactivated, all accesses to the flash are permitted.

It is important to note that the assertion of the ERASE pin should always be longer than 50 ms.

As the ERASE pin integrates a permanent pull-down, it can be left unconnected during normal operation. However, it is safer to connect it directly to GND for the final application.

#### 8.8.5 Non-volatile Brownout Detector Control

Two general purpose NVM (GPNVM) bits are used for controlling the brownout detector (BOD), so that even after a power loss, the brownout detector operations remain in their state.

These two GPNVM bits can be cleared or set respectively through the commands "Clear General-purpose NVM Bit" and "Set General-purpose NVM Bit" of the EFC User Interface.

- GPNVM Bit 0 is used as a brownout detector enable bit. Setting the GPNVM Bit 0 enables the BOD, clearing it

disables the BOD. Asserting ERASE clears the GPNVM Bit 0 and thus disables the brownout detector by default.

- The GPNVM Bit 1 is used as a brownout reset enable signal for the reset controller. Setting the GPNVM Bit 1 enables the brownout reset when a brownout is detected, Clearing the GPNVM Bit 1 disables the brownout reset. Asserting ERASE disables the brownout reset by default.

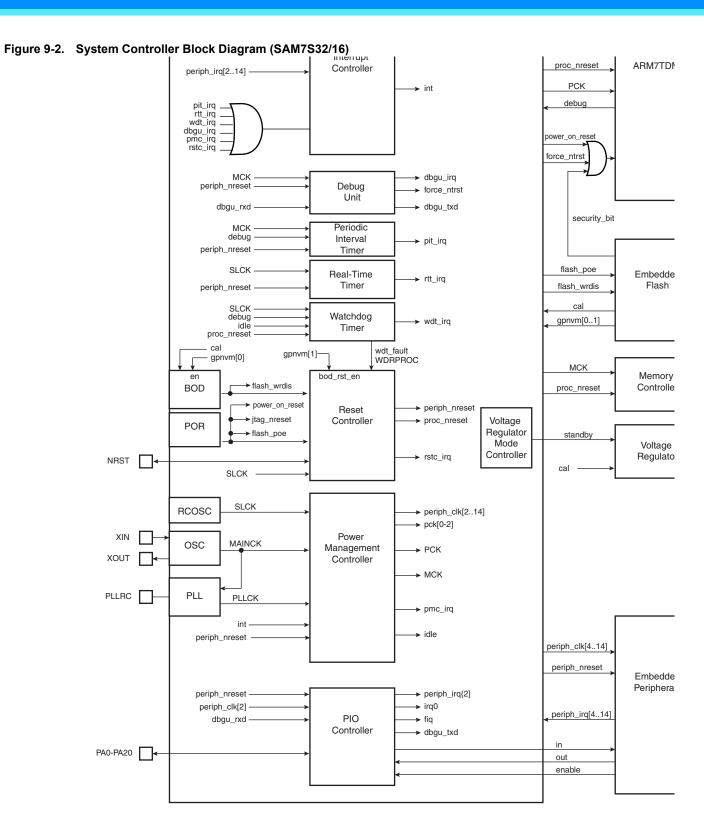

dbgu\_irq power\_on\_reset pmc\_irq rstc\_irq force ntrst MCK periph\_nreset dbgu\_irq Debug → force\_ntrst Unit dbgu\_rxd dbgu\_txd security\_bit MCK debug Periodic Interval → pit\_irq periph\_nreset Timer flash\_poe SLCK Real-Time → rtt\_irq Timer flash\_wrdis periph\_nreset cal SLCK debug idle Watchdog gpnvm[0..1] → wdt\_irq Timer proc\_nreset wdt\_fault WDRPROC gpnvm[1]gpnvm[0] MCK bod\_rst\_en → flash\_wrdis BOD proc\_nreset power\_on\_reset periph\_nreset Reset → jtag\_nreset → proc\_nreset Voltage Controller POR ➤ flash\_poe Regulator standby Mode Controller rstc\_irq NRST cal · SLCK SLCK RCOSC → periph\_clk[2..14] **UDPCK** → pck[0-2] periph\_clk[11] Power XIN MAINCK OSC Management → PCK periph\_nreset XOUT Controller → UDPCK periph\_irq[11] → MCK usb\_suspend PLLRC PLL PLLCK → pmc\_irq → idle periph\_nreset periph\_clk[4..14] usb\_suspend periph\_nreset periph\_irq{2] periph\_nreset periph\_clk[2] → irq0-irq1 periph\_irq[4..14] dbgu\_rxd PIO → fiq Controller → dbgu\_txd in PA0-PA31 out enable

Figure 9-1. System Controller Block Diagram (SAM7S512/256/128/64/321/161)

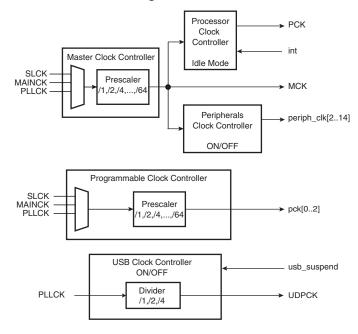

Figure 9-4. Power Management Controller Block Diagram

### 9.4 Advanced Interrupt Controller

- Controls the interrupt lines (nIRQ and nFIQ) of an ARM Processor

- Individually maskable and vectored interrupt sources

- Source 0 is reserved for the Fast Interrupt Input (FIQ)

- Source 1 is reserved for system peripherals RTT, PIT, EFC, PMC, DBGU, etc.)

- Other sources control the peripheral interrupts or external interrupts

- Programmable edge-triggered or level-sensitive internal sources

- Programmable positive/negative edge-triggered or high/low level-sensitive external sources

- 8-level Priority Controller

- Drives the normal interrupt of the processor

- Handles priority of the interrupt sources

- Higher priority interrupts can be served during service of lower priority interrupt

- Vectoring

- Optimizes interrupt service routine branch and execution

- One 32-bit vector register per interrupt source

- Interrupt vector register reads the corresponding current interrupt vector

- Protect Mode

- Easy debugging by preventing automatic operations

- Fast Forcing

- Permits redirecting any interrupt source on the fast interrupt

- General Interrupt Mask

- Provides processor synchronization on events without triggering an interrupt

#### 9.5 Debug Unit

- Comprises:

- One two-pin UART

- One Interface for the Debug Communication Channel (DCC) support

Table 10-2. Peripheral Identifiers (SAM7S32/16)

|         | · · · · · · · · · · · · · · · · · · · |                               |      |

|---------|---------------------------------------|-------------------------------|------|

|         |                                       |                               |      |

| 0       | AIC                                   | Advanced Interrupt Controller | FIQ  |

| 1       | SYSC <sup>(1)</sup>                   | System                        |      |

| 2       | PIOA                                  | Parallel I/O Controller A     |      |

| 3       | Reserved                              |                               |      |

| 4       | ADC <sup>(1)</sup>                    | Analog-to Digital Converter   |      |

| 5       | SPI                                   | Serial Peripheral Interface   |      |

| 6       | US                                    | USART                         |      |

| 7       | Reserved                              |                               |      |

| 8       | SSC                                   | Synchronous Serial Controller |      |

| 9       | TWI                                   | Two-wire Interface            |      |

| 10      | PWMC                                  | PWM Controller                |      |

| 11      | Reserved                              |                               |      |

| 12      | TC0                                   | Timer/Counter 0               |      |

| 13      | TC1                                   | Timer/Counter 1               |      |

| 14      | TC2                                   | Timer/Counter 2               |      |

| 15 - 29 | Reserved                              |                               |      |

| 30      | AIC                                   | Advanced Interrupt Controller | IRQ0 |

| 31      | Reserved                              |                               |      |

|         |                                       |                               |      |

# 10.3 Peripheral Multiplexing on PIO Lines

The SAM7S Series features one PIO controller, PIOA, that multiplexes the I/O lines of the peripheral set.

PIO Controller A controls 32 lines (21 lines for SAM7S32/16). Each line can be assigned to one of two peripheral functions, A or B. Some of them can also be multiplexed with the analog inputs of the ADC Controller.

Table 10-3, "Multiplexing on PIO Controller A (SAM7S512/256/128/64/321/161)," on page 35 and Table 10-4, "Multiplexing on PIO Controller A (SAM7S32/16)," on page 36 define how the I/O lines of the peripherals A, B or the analog inputs are multiplexed on the PIO Controller A. The two columns "Function" and "Comments" have been inserted for the user's own comments; they may be used to track how pins are defined in an application.

Note that some peripheral functions that are output only may be duplicated in the table.

All pins reset in their Parallel I/O lines function are configured as input with the programmable pull-up enabled, so that the device is maintained in a static state as soon as a reset is detected.

Table 10-4. Multiplexing on PIO Controller A (SAM7S32/16)

| Table 10-4. | wuttplexing on F | 210 Controller A (SA | IVI 7 3 3 2 / 10 ) |  |

|-------------|------------------|----------------------|--------------------|--|

|             |                  |                      |                    |  |

| PA0         | PWM0             | TIOA0                | High-Drive         |  |

| PA1         | PWM1             | TIOB0                | High-Drive         |  |

| PA2         | PWM2             | SCK0                 | High-Drive         |  |

| PA3         | TWD              | NPCS3                | High-Drive         |  |

| PA4         | TWCK             | TCLK0                |                    |  |

| PA5         | RXD0             | NPCS3                |                    |  |

| PA6         | TXD0             | PCK0                 |                    |  |

| PA7         | RTS0             | PWM3                 |                    |  |

| PA8         | CTS0             | ADTRG                |                    |  |

| PA9         | DRXD             | NPCS1                |                    |  |

| PA10        | DTXD             | NPCS2                |                    |  |

| PA11        | NPCS0            | PWM0                 |                    |  |

| PA12        | MISO             | PWM1                 |                    |  |

| PA13        | MOSI             | PWM2                 |                    |  |

| PA14        | SPCK             | PWM3                 |                    |  |

| PA15        | TF               | TIOA1                |                    |  |

| PA16        | TK               | TIOB1                |                    |  |

| PA17        | TD               | PCK1                 | AD0                |  |

| PA18        | RD               | PCK2                 | AD1                |  |

| PA19        | RK               | FIQ                  | AD2                |  |

| PA20        | RF               | IRQ0                 | AD3                |  |

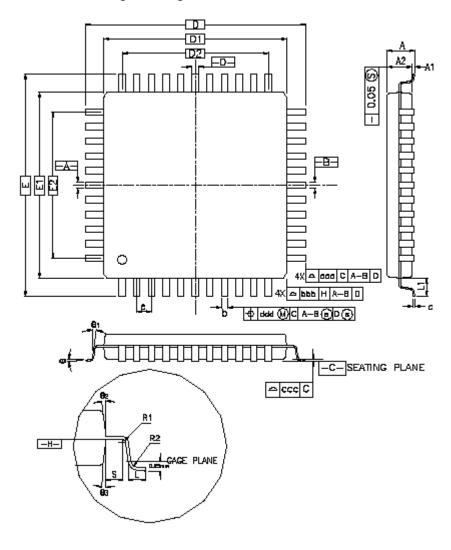

# 11. Package Drawings

The SAM7S series devices are available in LQFP and QFN package types.

# 11.1 LQFP Packages

Figure 11-1. 48-and 64-lead LQFP Package Drawing

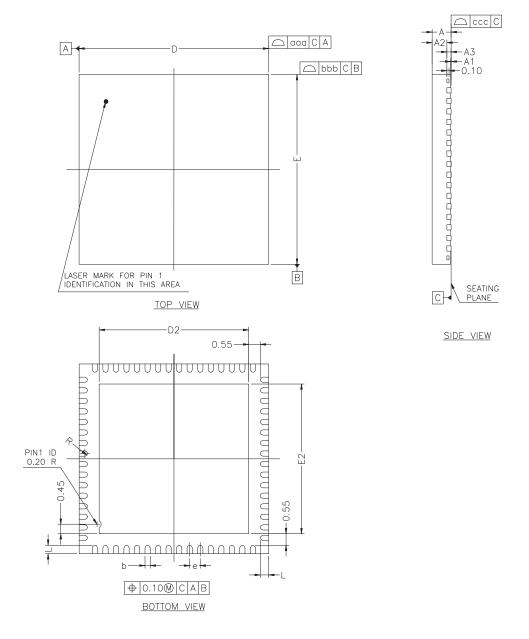

Figure 11-3. 64-pad QFN Package Drawing

Table 11-4. 64-pad QFN Package Dimensions (in mm)

| Symbol |       |          |                |           |           |       |  |

|--------|-------|----------|----------------|-----------|-----------|-------|--|

| А      | _     | _        | 090            | _         | -         | 0.035 |  |

| A1     | _     | _        | 0.05           | _         | _         | 0.001 |  |

| A2     | _     | 0.65     | 0.70           | _         | 0.026     | 0.028 |  |

| А3     |       | 0.20 REF | I              |           | 0.008 REF |       |  |

| b      | 0.23  | 0.25     | 0.28           | 0.009     | 0.010     | 0.011 |  |

| D      |       | 9.00 bsc |                |           | 0.354 bsc |       |  |

| D2     | 6.95  | 7.10     | 7.25           | 0.274     | 0.280     | 0.285 |  |

| E      |       | 9.00 bsc | I              | 0.354 bsc |           |       |  |

| E2     | 6.95  | 7.10     | 7.25           | 0.274     | 0.280     | 0.285 |  |

| L      | 0.35  | 0.40     | 0.45           | 0.014     | 0.016     | 0.018 |  |

| е      |       | 0.50 bsc | I              |           | 0.020 bsc |       |  |

| R      | 0.125 | _        | _              | 0.0005    | _         | _     |  |

|        | •     | Toleranc | es of Form and | Position  |           |       |  |

| aaa    | 0.10  |          |                |           | 0.004     |       |  |

| bbb    | 0.10  |          |                | 0.004     |           |       |  |

| ccc    |       | 0.05     |                |           | 0.002     |       |  |

# 12. SAM7S Ordering Information

Table 12-1.

SAM7S Series Ordering Information

| MLR A Ordering<br>Code               | MLR B<br>Ordering Code                 | MLR C<br>Ordering Code               | MLR D<br>Ordering Code               | Package           | Package<br>Type | Temperature<br>Operating<br>Range |

|--------------------------------------|----------------------------------------|--------------------------------------|--------------------------------------|-------------------|-----------------|-----------------------------------|

| AT91SAM7S16-AU<br>AT91SAM7S16-MU     | -                                      | -                                    | -                                    | LQFP 48<br>QFN 48 | Green           | Industrial (-40· C to 85· C)      |

| AT91SAM7S161-AU                      | _                                      | -                                    | -                                    | LQFP 64           | Green           | Industrial<br>(-40· C to 85· C)   |

| AT91SAM7S32-AU-001<br>AT91SAM7S32-MU | AT91SAM7S32B-AU<br>AT91SAM7S32B-MU     |                                      |                                      | LQFP 48<br>QFN 48 | Green           | Industrial<br>(-40· C to 85· C)   |

| AT91SAM7S321-AU<br>AT91SAM7S321-MU   | _                                      | -                                    | -                                    | LQFP 64<br>QFN 64 | Green           | Industrial<br>(-40· C to 85· C)   |

| -                                    | AT91SAM7S64B-AU<br>AT91SAM7S64B-MU     | AT91SAM7S64C-AU<br>AT91SAM7S64C-MU   | -                                    | LQFP 64<br>QFN 64 | Green           | Industrial<br>(-40· C to 85· C)   |

| -                                    | AT91SAM7S128-AU-001<br>AT91SAM7S128-MU | AT91SAM7S128C-AU<br>AT91SAM7S128C-MU | AT91SAM7S128D-AU<br>AT91SAM7S128D-MU | LQFP 64<br>QFN 64 | Green           | Industrial (-40· C to 85· C)      |

| -                                    | AT91SAM7S256-AU-001<br>AT91SAM7S256-MU | AT91SAM7S256C-AU<br>AT91SAM7S256C-MU | AT91SAM7S256D-AU<br>AT91SAM7S256D-MU | LQFP 64<br>QFN 64 | Green           | Industrial<br>(-40· C to 85· C)   |

| AT91SAM7S512-AU<br>AT91SAM7S512-MU   | AT91SAM7S512B-AU<br>AT91SAM7S512B-MU   | -                                    | -                                    | LQFP 64<br>QFN 64 | Green           | Industrial<br>(-40· C to 85· C)   |

**Atmel Corporation**

1600 Technology Drive San Jose, CA 95110 USA

**Tel:** (+1) (408) 441-0311 **Fax:** (+1) (408) 487-2600

www.atmel.com

**Atmel Asia Limited**

Unit 01-5 & 16, 19F BEA Tower, Millennium City 5 418 Kwun Tong Roa Kwun Tong, Kowloon

HONG KONG **Tel:** (+852) 2245-6100

Fax: (+852) 2722-1369

Atmel Munich GmbH

Business Campus Parkring 4 D-85748 Garching b. Munich

GERMANY

Tel: (+49) 89-31970-0

Fax: (+49) 89-3194621

Atmel Japan G.K.

16F Shin-Osaki Kangyo Bldg 1-6-4 Osaki, Shinagawa-ku

Tokyo 141-0032

JAPAN

**Tel:** (+81) (3) 6417-0300 **Fax:** (+81) (3) 6417-0370

© 2012 Atmel Corporation. All rights reserved. / Rev.: 6175KS-ATARM-25-Oct-12

Atmel<sup>®</sup>, Atmel logo and combinations thereof, Enabling Unlimited Possibilities<sup>®</sup>, SAM-BA<sup>®</sup> and others, are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Windows<sup>®</sup> and others are registered trademarks or trademarks of Microsoft Corporation in the US and/or in other countries. ARM<sup>®</sup>, the ARM Powered<sup>®</sup> logo, ARM7TDMI<sup>®</sup>, Thumb<sup>®</sup>, and others are registered trademarks or trademarks of ARM Limited. Other terms and product names may be the trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.