Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Purchase URL              | https://www.e-xfl.com/product-detail/infineon-technologies/xc167ci16f40fbbfxuma |

|---------------------------|---------------------------------------------------------------------------------|

| upplier Device Package    | -                                                                               |

| ckage / Case              | -                                                                               |

| ounting Type              | -                                                                               |

| perating Temperature      | -40°C ~ 85°C (TA)                                                               |

| scillator Type            | Internal                                                                        |

| ata Converters            | A/D 16x8/10b                                                                    |

| oltage - Supply (Vcc/Vdd) | 2.35V ~ 2.7V                                                                    |

| AM Size                   | 8K x 8                                                                          |

| EPROM Size                | -                                                                               |

| ogram Memory Type         | FLASH                                                                           |

| rogram Memory Size        | 128KB (128K x 8)                                                                |

| imber of I/O              | 103                                                                             |

| ripherals                 | PWM, WDT                                                                        |

| nnectivity                | CANbus, EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                              |

| eed                       | 40MHz                                                                           |

| re Size                   | 16-Bit                                                                          |

| ore Processor             | C166SV2                                                                         |

| roduct Status             | Last Time Buy                                                                   |

| etails                    |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2006-08

Published by

Infineon Technologies AG

81726 München, Germany

© Infineon Technologies AG 2006.

All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

## **Table of Contents**

# **Table of Contents**

| 1               | Summary of Features 4                                     |

|-----------------|-----------------------------------------------------------|

| <b>2</b><br>2.1 | General Device Information   7     Introduction   7       |

| 2.2             | Pin Configuration and Definition 8                        |

| 3               | Functional Description                                    |

| 3.1             | Memory Subsystem and Organization                         |

| 3.2             | External Bus Controller                                   |

| 3.3             | Central Processing Unit (CPU)                             |

| 3.4             | Interrupt System                                          |

| 3.5             | On-Chip Debug Support (OCDS)                              |

| 3.6             | Capture/Compare Units (CAPCOM1/2)                         |

| 3.7             | The Capture/Compare Unit CAPCOM6                          |

| 3.8             | General Purpose Timer (GPT12E) Unit                       |

| 3.9             | Real Time Clock 42                                        |

| 3.10            | A/D Converter                                             |

| 3.11            | Asynchronous/Synchronous Serial Interfaces (ASC0/ASC1) 45 |

| 3.12            | High Speed Synchronous Serial Channels (SSC0/SSC1) 46     |

| 3.13            | TwinCAN Module                                            |

| 3.14            | IIC Bus Module                                            |

| 3.15            | Watchdog Timer 49                                         |

| 3.16            | Clock Generation                                          |

| 3.17            | Parallel Ports                                            |

| 3.18            | Power Management                                          |

| 3.19            | Instruction Set Summary 53                                |

| 4               | Electrical Parameters56                                   |

| 4.1             | General Parameters 56                                     |

| 4.2             | DC Parameters 59                                          |

| 4.3             | Analog/Digital Converter Parameters                       |

| 4.4             | AC Parameters                                             |

| 4.4.1           | Definition of Internal Timing                             |

| 4.4.2           | On-chip Flash Operation                                   |

| 4.4.3           | External Clock Drive XTAL1 73                             |

| 4.4.4           | Testing Waveforms 74                                      |

| 4.4.5           | External Bus Timing                                       |

| 5               | Package and Reliability                                   |

| 5.1             | Packaging                                                 |

| 5.2             | Flash Memory Parameters                                   |

## **Summary of Features**

Table 1 XC167 Derivative Synopsis

| Derivative <sup>1)</sup>                  | Temp.<br>Range      | Program<br>Memory   | On-Chip RAM                                          | Interfaces                                       |

|-------------------------------------------|---------------------|---------------------|------------------------------------------------------|--------------------------------------------------|

| SAK-XC167CI-16F40F,<br>SAK-XC167CI-16F20F | -40 °C to<br>125 °C | 128 Kbytes<br>Flash | 2 Kbytes DPRAM,<br>4 Kbytes DSRAM,<br>2 Kbytes PSRAM | ASC0, ASC1,<br>SSC0, SSC1,<br>CAN0, CAN1,<br>IIC |

| SAF-XC167CI-16F40F,<br>SAF-XC167CI-16F20F | -40 °C to<br>85 °C  | 128 Kbytes<br>Flash | 2 Kbytes DPRAM,<br>4 Kbytes DSRAM,<br>2 Kbytes PSRAM | ASC0, ASC1,<br>SSC0, SSC1,<br>CAN0, CAN1,<br>IIC |

<sup>1)</sup> This Data Sheet is valid for devices starting with and including design step BB.

#### **General Device Information**

## 2 General Device Information

#### 2.1 Introduction

The XC167 derivatives are high-performance members of the Infineon XC166 Family of full featured single-chip CMOS microcontrollers. These devices extend the functionality and performance of the C166 Family in terms of instructions (MAC unit), peripherals, and speed. They combine high CPU performance (up to 40 million instructions per second) with high peripheral functionality and enhanced IO-capabilities. They also provide clock generation via PLL and various on-chip memory modules such as program Flash, program RAM, and data RAM.

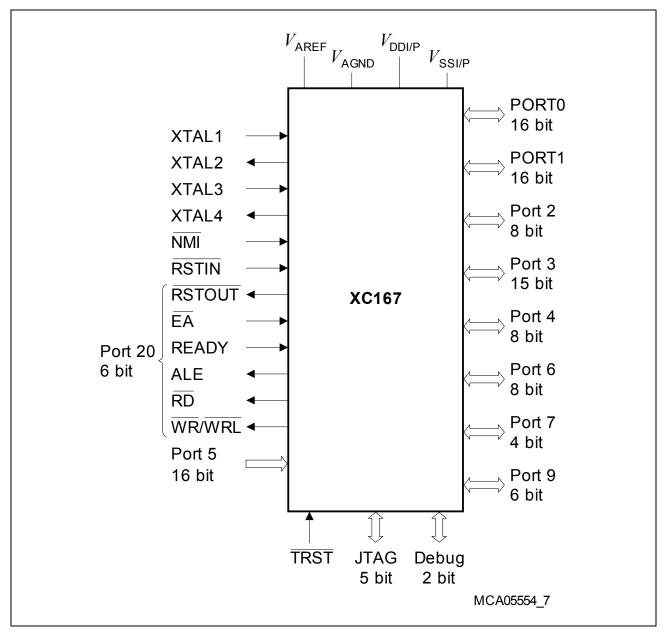

Figure 1 Logic Symbol

Data Sheet 7 V1.3, 2006-08

#### **General Device Information**

## 2.2 Pin Configuration and Definition

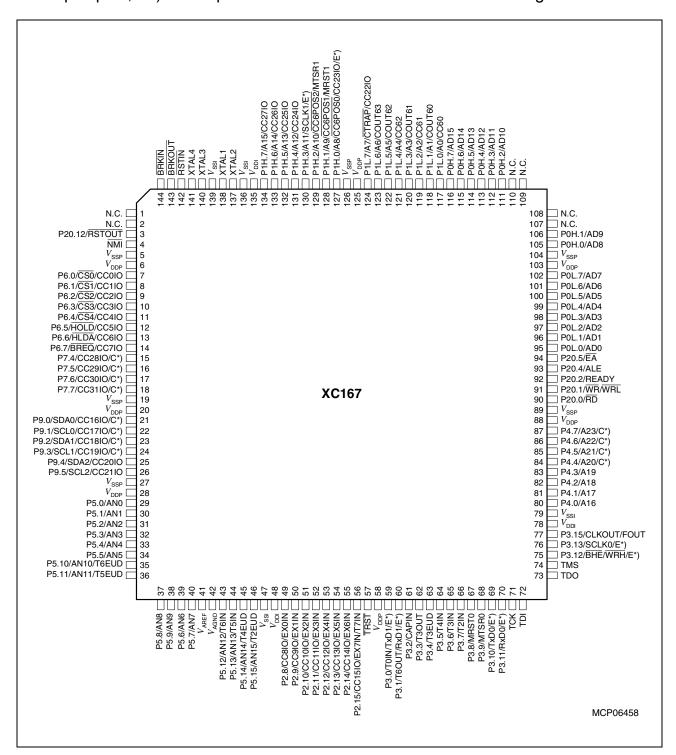

The pins of the XC167 are described in detail in **Table 2**, including all their alternate functions. **Figure 2** summarizes all pins in a condensed way, showing their location on the 4 sides of the package. E\*) and C\*) mark pins to be used as alternate external interrupt inputs, C\*) marks pins that can have CAN interface lines assigned to them.

Figure 2 Pin Configuration (top view)

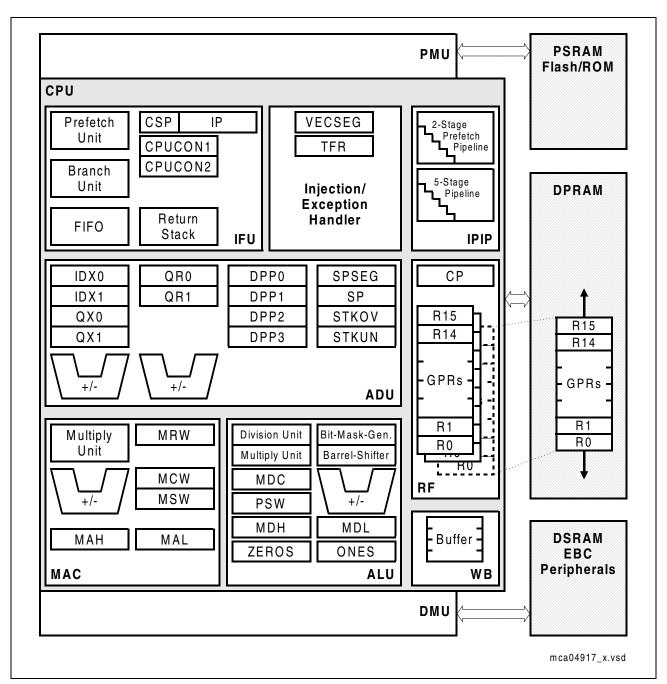

## 3.3 Central Processing Unit (CPU)

The main core of the CPU consists of a 5-stage execution pipeline with a 2-stage instruction-fetch pipeline, a 16-bit arithmetic and logic unit (ALU), a 32-bit/40-bit multiply and accumulate unit (MAC), a register-file providing three register banks, and dedicated SFRs. The ALU features a multiply and divide unit, a bit-mask generator, and a barrel shifter.

Figure 4 CPU Block Diagram

Based on these hardware provisions, most of the XC167's instructions can be executed in just one machine cycle which requires 25 ns at 40 MHz CPU clock. For example, shift

Table 7 Summary of the XC167's Parallel Ports

| I able I | 7 Summary of the ACTO'S Faramer Forts          |                                                                                                                          |  |  |  |

|----------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Port     | Control                                        | Alternate Functions                                                                                                      |  |  |  |

| PORT0    | Pad drivers                                    | Address/Data lines or data lines <sup>1)</sup>                                                                           |  |  |  |

| PORT1    | Pad drivers                                    | Address lines <sup>2)</sup>                                                                                              |  |  |  |

|          |                                                | Capture inputs or compare outputs, Serial interface lines                                                                |  |  |  |

| Port 2   | Pad drivers,<br>Open drain,<br>Input threshold | Capture inputs or compare outputs, Timer control signal, Fast external interrupt inputs                                  |  |  |  |

| Port 3   | Pad drivers,<br>Open drain,<br>Input threshold | Timer control signals, serial interface lines, Optional bus control signal BHE/WRH, System clock output CLKOUT (or FOUT) |  |  |  |

| Port 4   | Pad drivers,                                   | Segment address lines <sup>3)</sup>                                                                                      |  |  |  |

|          | Open drain,<br>Input threshold                 | CAN interface lines <sup>4)</sup>                                                                                        |  |  |  |

| Port 5   | _                                              | Analog input channels to the A/D converter, Timer control signals                                                        |  |  |  |

| Port 6   | Open drain,<br>Input threshold                 | Capture inputs or compare outputs, Bus arbitration signals BREQ, HLDA, HOLD, Optional chip select signals                |  |  |  |

| Port 7   | Open drain,<br>Input threshold                 | Capture inputs or compare outputs, CAN interface lines <sup>4)</sup>                                                     |  |  |  |

| Port 9   | Pad drivers,                                   | Capture inputs or compare outputs                                                                                        |  |  |  |

|          | Open drain,<br>Input threshold                 | CAN interface lines <sup>4)</sup> , IIC bus interface lines <sup>4)</sup>                                                |  |  |  |

| Port 20  | Pad drivers,<br>Open drain                     | Bus control signals RD, WR/WRL, READY, ALE, External access enable pin EA, Reset indication output RSTOUT                |  |  |  |

<sup>1)</sup> For multiplexed bus cycles.

<sup>2)</sup> For demultiplexed bus cycles.

<sup>3)</sup> For more than 64 Kbytes of external resources.

<sup>4)</sup> Can be assigned by software.

# 3.19 Instruction Set Summary

Table 8 lists the instructions of the XC167 in a condensed way.

The various addressing modes that can be used with a specific instruction, the operation of the instructions, parameters for conditional execution of instructions, and the opcodes for each instruction can be found in the "Instruction Set Manual".

This document also provides a detailed description of each instruction.

Table 8

Instruction Set Summary

| Mnemonic      | Description                                                                                       | Bytes |  |

|---------------|---------------------------------------------------------------------------------------------------|-------|--|

| ADD(B)        | Add word (byte) operands                                                                          | 2/4   |  |

| ADDC(B)       | Add word (byte) operands with Carry                                                               | 2/4   |  |

| SUB(B)        | Subtract word (byte) operands                                                                     |       |  |

| SUBC(B)       | Subtract word (byte) operands with Carry                                                          | 2/4   |  |

| MUL(U)        | (Un)Signed multiply direct GPR by direct GPR (16- × 16-bit)                                       | 2     |  |

| DIV(U)        | (Un)Signed divide register MDL by direct GPR (16-/16-bit)                                         | 2     |  |

| DIVL(U)       | (Un)Signed long divide reg. MD by direct GPR (32-/16-bit)                                         | 2     |  |

| CPL(B)        | Complement direct word (byte) GPR                                                                 | 2     |  |

| NEG(B)        | Negate direct word (byte) GPR                                                                     | 2     |  |

| AND(B)        | Bitwise AND, (word/byte operands)                                                                 | 2/4   |  |

| OR(B)         | Bitwise OR, (word/byte operands)                                                                  | 2/4   |  |

| XOR(B)        | Bitwise exclusive OR, (word/byte operands)                                                        | 2/4   |  |

| BCLR/BSET     | Clear/Set direct bit                                                                              | 2     |  |

| BMOV(N)       | Move (negated) direct bit to direct bit                                                           | 4     |  |

| BAND/BOR/BXOR | AND/OR/XOR direct bit with direct bit                                                             | 4     |  |

| BCMP          | Compare direct bit to direct bit                                                                  | 4     |  |

| BFLDH/BFLDL   | Bitwise modify masked high/low byte of bit-addressable direct word memory with immediate data     | 4     |  |

| CMP(B)        | Compare word (byte) operands                                                                      | 2/4   |  |

| CMPD1/2       | Compare word data to GPR and decrement GPR by 1/2                                                 | 2/4   |  |

| CMPI1/2       | Compare word data to GPR and increment GPR by 1/2                                                 | 2/4   |  |

| PRIOR         | Determine number of shift cycles to normalize direct word GPR and store result in direct word GPR | 2     |  |

| SHL/SHR       | Shift left/right direct word GPR                                                                  | 2     |  |

Table 8 Instruction Set Summary (cont'd)

| Mnemonic     | Description                                                                           | Bytes |

|--------------|---------------------------------------------------------------------------------------|-------|

| ROL/ROR      | Rotate left/right direct word GPR                                                     | 2     |

| ASHR         | Arithmetic (sign bit) shift right direct word GPR                                     | 2     |

| MOV(B)       | Move word (byte) data                                                                 | 2/4   |

| MOVBS/Z      | Move byte operand to word op. with sign/zero extension                                | 2/4   |

| JMPA/I/R     | Jump absolute/indirect/relative if condition is met                                   | 4     |

| JMPS         | Jump absolute to a code segment                                                       | 4     |

| JB(C)        | Jump relative if direct bit is set (and clear bit)                                    | 4     |

| JNB(S)       | Jump relative if direct bit is not set (and set bit)                                  | 4     |

| CALLA/I/R    | Call absolute/indirect/relative subroutine if condition is met                        | 4     |

| CALLS        | Call absolute subroutine in any code segment                                          | 4     |

| PCALL        | Push direct word register onto system stack and call absolute subroutine              | 4     |

| TRAP         | Call interrupt service routine via immediate trap number                              | 2     |

| PUSH/POP     | Push/pop direct word register onto/from system stack                                  | 2     |

| SCXT         | Push direct word register onto system stack and update register with word operand     | 4     |

| RET(P)       | Return from intra-segment subroutine (and pop direct word register from system stack) | 2     |

| RETS         | Return from inter-segment subroutine                                                  | 2     |

| RETI         | Return from interrupt service subroutine                                              | 2     |

| SBRK         | Software Break                                                                        | 2     |

| SRST         | Software Reset                                                                        | 4     |

| IDLE         | Enter Idle Mode                                                                       | 4     |

| PWRDN        | Enter Power Down Mode (supposes NMI-pin being low)                                    | 4     |

| SRVWDT       | Service Watchdog Timer                                                                | 4     |

| DISWDT/ENWDT | Disable/Enable Watchdog Timer                                                         | 4     |

| EINIT        | End-of-Initialization Register Lock                                                   | 4     |

| ATOMIC       | Begin ATOMIC sequence                                                                 | 2     |

| EXTR         | Begin EXTended Register sequence                                                      | 2     |

| EXTP(R)      | Begin EXTended Page (and Register) sequence                                           | 2/4   |

| EXTS(R)      | Begin EXTended Segment (and Register) sequence                                        | 2/4   |

### **Operating Conditions**

The following operating conditions must not be exceeded to ensure correct operation of the XC167. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

Table 10 Operating Condition Parameters

| Parameter                                 | Symbol Limit Values |      | Unit                   | Notes |                                                |

|-------------------------------------------|---------------------|------|------------------------|-------|------------------------------------------------|

|                                           |                     | Min. | Max.                   |       |                                                |

| Digital supply voltage for the core       | $V_{DDI}$           | 2.35 | 2.7                    | V     | Active mode,<br>$f_{CPU} = f_{CPUmax}^{(1)2)}$ |

| Digital supply voltage for IO pads        | $V_{DDP}$           | 4.4  | 5.5                    | V     | Active mode <sup>2)</sup>                      |

| Supply Voltage Difference                 | $\Delta V_{DD}$     | -0.5 | _                      | V     | $V_{\rm DDP}$ - $V_{\rm DDI}^{3)}$             |

| Digital ground voltage                    | $V_{SS}$            | 0    |                        | V     | Reference voltage                              |

| Overload current                          | $I_{OV}$            | -5   | 5                      | mA    | Per IO pin <sup>4)5)</sup>                     |

|                                           |                     | -2   | 5                      | mA    | Per analog input pin <sup>4)5)</sup>           |

| Overload current coupling                 | $K_{OVA}$           | _    | $1.0 \times 10^{-4}$   | _     | <i>I</i> <sub>OV</sub> > 0                     |

| factor for analog inputs <sup>6)</sup>    |                     | _    | $1.5 \times 10^{-3}$   | _     | <i>I</i> <sub>OV</sub> < 0                     |

| Overload current coupling                 | $K_{OVD}$           | _    | 5.0 × 10 <sup>-3</sup> | _     | <i>I</i> <sub>OV</sub> > 0                     |

| factor for digital I/O pins <sup>6)</sup> |                     | _    | 1.0 × 10 <sup>-2</sup> | _     | <i>I</i> <sub>OV</sub> < 0                     |

| Absolute sum of overload currents         | $\Sigma  I_{OV} $   | -    | 50                     | mA    | 5)                                             |

| External Load<br>Capacitance              | $C_{L}$             | _    | 50                     | pF    | Pin drivers in default mode <sup>7)</sup>      |

| Ambient temperature                       | $T_{A}$             | _    | _                      | °C    | see Table 1                                    |

<sup>1)</sup>  $f_{\text{CPUmax}}$  = 40 MHz for devices marked ... 40F,  $f_{\text{CPUmax}}$  = 20 MHz for devices marked ... 20F.

<sup>2)</sup> External circuitry must guarantee low level at the RSTIN pin at least until both power supply voltages have reached their operating range.

<sup>3)</sup> This limitation must be fulfilled under all operating conditions including power-ramp-up, power-ramp-down, and power-save modes.

<sup>4)</sup> Overload conditions occur if the standard operating conditions are exceeded, i.e. the voltage on any pin exceeds the specified range:  $V_{\rm OV} > V_{\rm DDP} + 0.5 \ {\rm V} \ (I_{\rm OV} > 0)$  or  $V_{\rm OV} < V_{\rm SS}$  - 0.5 V ( $I_{\rm OV} < 0$ ). The absolute sum of input overload currents on all pins may not exceed **50 mA**. The supply voltages must remain within the specified limits.

Proper operation is not guaranteed if overload conditions occur on functional pins such as XTAL1, RD, WR, etc.

<sup>5)</sup> Not subject to production test - verified by design/characterization.

Table 12 Current Limits for Port Output Drivers

| Port Output Driver<br>Mode |        | Nominal Output Current $(I_{OLnom}, -I_{OHnom})$ |

|----------------------------|--------|--------------------------------------------------|

| Strong driver              | 10 mA  | 2.5 mA                                           |

| Medium driver              | 4.0 mA | 1.0 mA                                           |

| Weak driver                | 0.5 mA | 0.1 mA                                           |

<sup>1)</sup> An output current above  $|I_{\rm OXnom}|$  may be drawn from up to three pins at the same time. For any group of 16 neighboring port output pins the total output current in each direction ( $\Sigma I_{\rm OL}$  and  $\Sigma I_{\rm OH}$ ) must remain below 50 mA.

Table 13

Power Consumption XC167 (Operating Conditions apply)

| Parameter                                                                                                                                   | Sym-           | Limit Values |                                               | Unit | <b>Test Condition</b>                                                                                |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------|-----------------------------------------------|------|------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                             | bol            | Min.         | Max.                                          |      |                                                                                                      |  |

| Power supply current (active) with all peripherals active                                                                                   | $I_{DDI}$      | _            | 15 + $2.6 \times f_{\text{CPU}}$              | mA   | $f_{\mathrm{CPU}}$ in [MHz] <sup>1)2)</sup>                                                          |  |

| Pad supply current                                                                                                                          | $I_{DDP}$      | _            | 5                                             | mA   | 3)                                                                                                   |  |

| Idle mode supply current with all peripherals active                                                                                        | $I_{IDX}$      | _            | 15 +<br>1.2 × $f_{\text{CPU}}$                | mA   | $f_{\rm CPU}$ in [MHz] <sup>2)</sup>                                                                 |  |

| Sleep and Power down mode supply current caused by leakage <sup>4)</sup>                                                                    | $I_{PDL}^{5)}$ | _            | 128,000<br>× e <sup>-α</sup>                  | mA   | $V_{\rm DDI} = V_{\rm DDImax}^{6)}$<br>$T_{\rm J}$ in [°C]<br>$\alpha =$ 4670 / (273 + $T_{\rm J}$ ) |  |

| Sleep and Power down mode supply current caused by leakage and the RTC running, clocked by the main oscillator <sup>4)</sup>                | $I_{PDM}^{7)}$ | -            | $0.6 + 0.02 \times f_{\rm OSC} + I_{\rm PDL}$ | mA   | $V_{\rm DDI}$ = $V_{\rm DDImax}$ $f_{\rm OSC}$ in [MHz]                                              |  |

| Sleep and Power down mode supply current caused by leakage and the RTC running, clocked by the auxiliary oscillator at 32 kHz <sup>4)</sup> | $I_{PDA}$      | _            | 0.1 + I <sub>PDL</sub>                        | mA   | $V_{\rm DDI} = V_{\rm DDImax}$                                                                       |  |

<sup>1)</sup> During Flash programming or erase operations the supply current is increased by max. 5 mA.

Data Sheet 61 V1.3, 2006-08

<sup>2)</sup> The supply current is a function of the operating frequency. This dependency is illustrated in **Figure 11**. These parameters are tested at  $V_{\rm DDImax}$  and maximum CPU clock frequency with all outputs disconnected and all inputs at  $V_{\rm IL}$  or  $V_{\rm IH}$ .

<sup>3)</sup> The pad supply voltage pins ( $V_{\rm DDP}$ ) mainly provides the current consumed by the pin output drivers. A small amount of current is consumed even though no outputs are driven, because the drivers' input stages are switched and also the Flash module draws some power from the  $V_{\rm DDP}$  supply.

- 4) The total supply current in Sleep and Power down mode is the sum of the temperature dependent leakage current and the frequency dependent current for RTC and main oscillator or auxiliary oscillator (if active).

- 5) This parameter is determined mainly by the transistor leakage currents. This current heavily depends on the junction temperature (see **Figure 13**). The junction temperature  $T_J$  is the same as the ambient temperature  $T_A$  if no current flows through the port output drivers. Otherwise, the resulting temperature difference must be taken into account.

- 6) All inputs (including pins configured as inputs) at 0 V to 0.1 V or at  $V_{\text{DDP}}$  0.1 V to  $V_{\text{DDP}}$ , all outputs (including pins configured as outputs) disconnected. This parameter is tested at 25 °C and is valid for  $T_{\text{J}} \ge$  25 °C.

- 7) This parameter is determined mainly by the current consumed by the oscillator switched to low gain mode (see Figure 12). This current, however, is influenced by the external oscillator circuitry (crystal, capacitors). The given values refer to a typical circuitry and may change in case of a not optimized external oscillator circuitry.

Data Sheet 62 V1.3, 2006-08

#### 4.4 AC Parameters

## 4.4.1 Definition of Internal Timing

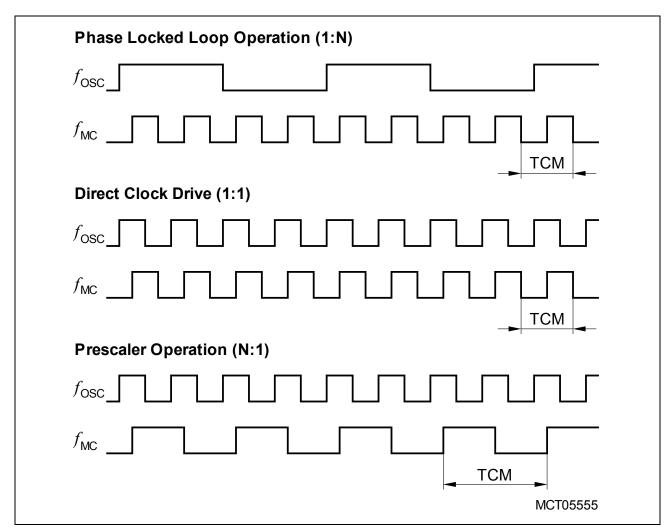

The internal operation of the XC167 is controlled by the internal master clock  $f_{\rm MC}$ .

The master clock signal  $f_{\rm MC}$  can be generated from the oscillator clock signal  $f_{\rm OSC}$  via different mechanisms. The duration of master clock periods (TCMs) and their variation (and also the derived external timing) depend on the used mechanism to generate  $f_{\rm MC}$ . This influence must be regarded when calculating the timings for the XC167.

Figure 15 Generation Mechanisms for the Master Clock

Note: The example for PLL operation shown in **Figure 15** refers to a PLL factor of 1:4, the example for prescaler operation refers to a divider factor of 2:1.

The used mechanism to generate the master clock is selected by register PLLCON.

CPU and EBC are clocked with the CPU clock signal  $f_{\rm CPU}$ . The CPU clock can have the same frequency as the master clock ( $f_{\rm CPU}$  =  $f_{\rm MC}$ ) or can be the master clock divided by two:  $f_{\rm CPU}$  =  $f_{\rm MC}$  / 2. This factor is selected by bit CPSYS in register SYSCON1.

Table 16 VCO Bands for PLL Operation<sup>1)</sup>

| PLLCON.PLLVB | VCO Frequency Range | Base Frequency Range |

|--------------|---------------------|----------------------|

| 00           | 100 150 MHz         | 20 80 MHz            |

| 01           | 150 200 MHz         | 40 130 MHz           |

| 10           | 200 250 MHz         | 60 180 MHz           |

| 11           | Reserved            |                      |

<sup>1)</sup> Not subject to production test - verified by design/characterization.

### 4.4.2 On-chip Flash Operation

The XC167's Flash module delivers data within a fixed access time (see Table 17).

Accesses to the Flash module are controlled by the PMI and take 1+WS clock cycles, where WS is the number of Flash access waitstates selected via bitfield WSFLASH in register IMBCTRL. The resulting duration of the access phase must cover the access time  $t_{\rm ACC}$  of the Flash array. Therefore, the required Flash waitstates depend on the actual system frequency.

Note: The Flash access waitstates only affect non-sequential accesses. Due to prefetching mechanisms, the performance for sequential accesses (depending on the software structure) is only partially influenced by waitstates.

In typical applications, eliminating one waitstate increases the average performance by 5% ... 15%.

**Table 17** Flash Characteristics (Operating Conditions apply)

| Parameter                           | Symbol    |    | Limit Values |                 |      | Unit |

|-------------------------------------|-----------|----|--------------|-----------------|------|------|

|                                     |           |    | Min.         | Тур.            | Max. |      |

| Flash module access time            | $t_{ACC}$ | CC | _            | _               | 50   | ns   |

| Programming time per 128-byte block | $t_{PR}$  | CC | _            | 2 <sup>1)</sup> | 5    | ms   |

| Erase time per sector               | $t_{ER}$  | CC | _            | 2001)           | 500  | ms   |

<sup>1)</sup> Programming and erase time depends on the system frequency. Typical values are valid for 40 MHz.

Example: For an operating frequency of 40 MHz (clock cycle = 25 ns), devices can be operated with 1 waitstate:  $((1+1) \times 25 \text{ ns}) \ge 50 \text{ ns}$ .

**Table 18** indicates the interrelation of waitstates and system frequency.

**Table 18** Flash Access Waitstates

| Required Waitstates               | Frequency Range for             |

|-----------------------------------|---------------------------------|

| 0 WS (WSFLASH = 00 <sub>B</sub> ) | $f_{CPU} \leq 20 \; MHz$        |

| 1 WS (WSFLASH = 01 <sub>B</sub> ) | $f_{\sf CPU} \le 40 \; \sf MHz$ |

Note: The maximum achievable system frequency is limited by the properties of the respective derivative, i.e. 40 MHz (or 20 MHz for xxx-16F20F devices).

Data Sheet 72 V1.3, 2006-08

#### 4.4.3 External Clock Drive XTAL1

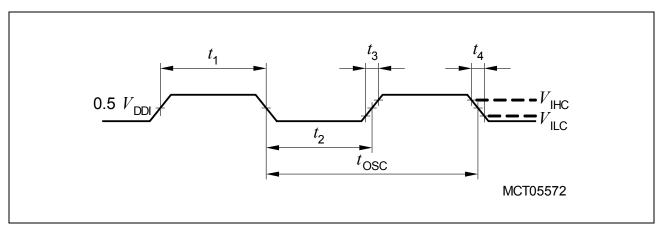

Table 19 External Clock Drive Characteristics (Operating Conditions apply)

| Parameter               | Symbol    |    | Limit Values |                   | Unit |

|-------------------------|-----------|----|--------------|-------------------|------|

|                         |           |    | Min.         | Max.              |      |

| Oscillator period       | $t_{OSC}$ | SR | 25           | 250 <sup>1)</sup> | ns   |

| High time <sup>2)</sup> | $t_1$     | SR | 6            | _                 | ns   |

| Low time <sup>2)</sup>  | $t_2$     | SR | 6            | _                 | ns   |

| Rise time <sup>2)</sup> | $t_3$     | SR | _            | 8                 | ns   |

| Fall time <sup>2)</sup> | $t_4$     | SR | _            | 8                 | ns   |

<sup>1)</sup> The maximum limit is only relevant for PLL operation to ensure the minimum input frequency for the PLL.

<sup>2)</sup> The clock input signal must reach the defined levels  $V_{\rm ILC}$  and  $V_{\rm IHC}$ .

Figure 17 External Clock Drive XTAL1

Note: If the on-chip oscillator is used together with a crystal or a ceramic resonator, the oscillator frequency is limited to a range of 4 MHz to 16 MHz.

It is strongly recommended to measure the oscillation allowance (negative resistance) in the final target system (layout) to determine the optimum parameters for the oscillator operation. Please refer to the limits specified by the crystal supplier.

When driven by an external clock signal it will accept the specified frequency range. Operation at lower input frequencies is possible but is verified by design only (not subject to production test).

Data Sheet 73 V1.3, 2006-08

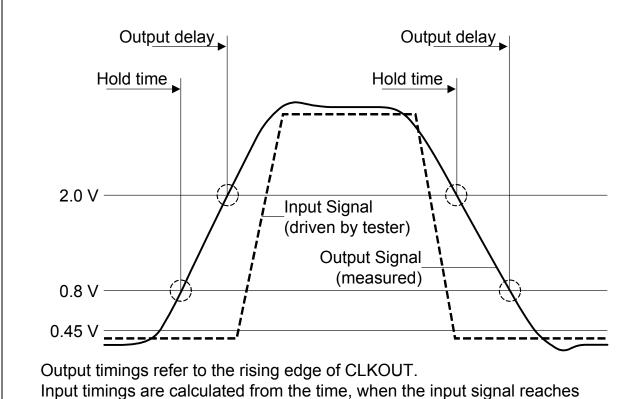

#### **Testing Waveforms** 4.4.4

$V_{\rm IH}$  or  $V_{\rm II}$ , respectively.

MCD05556

Figure 18 **Input Output Waveforms**

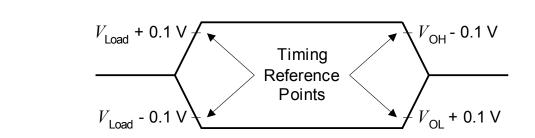

For timing purposes a port pin is no longer floating when a 100 mV change from load voltage occurs, but begins to float when a 100 mV change from the loaded  $V_{\rm OH}/V_{\rm OI}$  level occurs ( $I_{\rm OH}/I_{\rm OI}$  = 20 mA).

MCA05565

**Float Waveforms** Figure 19

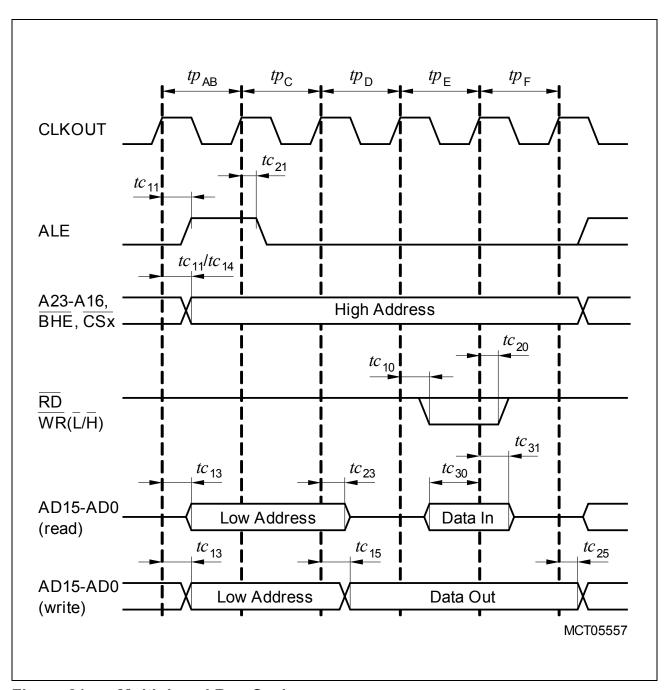

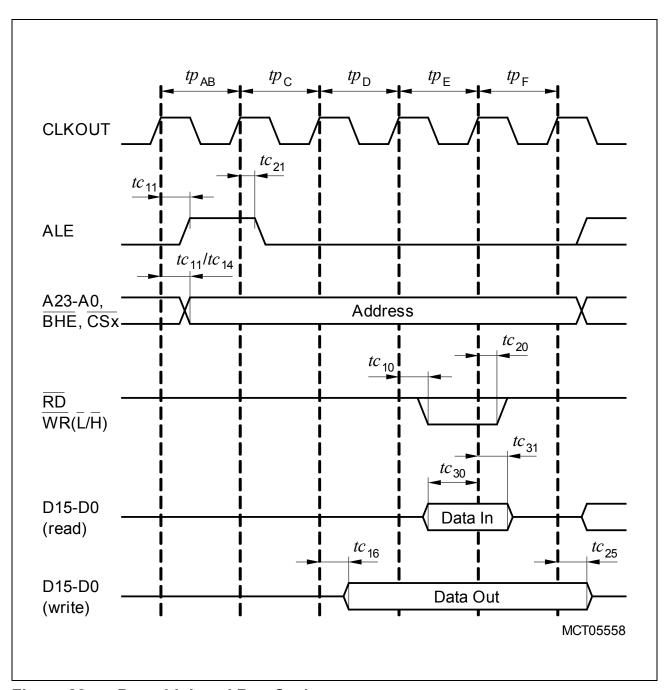

Figure 21 Multiplexed Bus Cycle

Figure 22 Demultiplexed Bus Cycle

## Package and Reliability

## **5.2** Flash Memory Parameters

The data retention time of the XC167's Flash memory (i.e. the time after which stored data can still be retrieved) depends on the number of times the Flash memory has been erased and programmed.

**Table 25** Flash Parameters (XC167, 128 Kbytes)

| Parameter             | Symbol    | Limit Values         |      | Unit   | Notes                                |  |

|-----------------------|-----------|----------------------|------|--------|--------------------------------------|--|

|                       |           | Min.                 | Max. |        |                                      |  |

| Data retention time   | $t_{RET}$ | 15                   | _    | years  | 10 <sup>3</sup> erase/program cycles |  |

| Flash Erase Endurance | $N_{ER}$  | 20 × 10 <sup>3</sup> | _    | cycles | Data retention time 5 years          |  |

Data Sheet 87 V1.3, 2006-08