Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Last Time Buy                                                                    |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                       |

| Peripherals                | PWM, WDT                                                                         |

| Number of I/O              | 103                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 2.7V                                                                     |

| Data Converters            | A/D 16x8/10b                                                                     |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP                                                                         |

| Supplier Device Package    | PG-TQFP-144-7                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc167ci16f40fbbkxqma1 |

## **Table of Contents**

# **Table of Contents**

| 1               | Summary of Features 4                                     |

|-----------------|-----------------------------------------------------------|

| <b>2</b><br>2.1 | General Device Information   7     Introduction   7       |

| 2.2             | Pin Configuration and Definition 8                        |

| 3               | Functional Description                                    |

| 3.1             | Memory Subsystem and Organization                         |

| 3.2             | External Bus Controller                                   |

| 3.3             | Central Processing Unit (CPU)                             |

| 3.4             | Interrupt System                                          |

| 3.5             | On-Chip Debug Support (OCDS)                              |

| 3.6             | Capture/Compare Units (CAPCOM1/2)                         |

| 3.7             | The Capture/Compare Unit CAPCOM6                          |

| 3.8             | General Purpose Timer (GPT12E) Unit                       |

| 3.9             | Real Time Clock 42                                        |

| 3.10            | A/D Converter                                             |

| 3.11            | Asynchronous/Synchronous Serial Interfaces (ASC0/ASC1) 45 |

| 3.12            | High Speed Synchronous Serial Channels (SSC0/SSC1) 46     |

| 3.13            | TwinCAN Module                                            |

| 3.14            | IIC Bus Module                                            |

| 3.15            | Watchdog Timer 49                                         |

| 3.16            | Clock Generation                                          |

| 3.17            | Parallel Ports                                            |

| 3.18            | Power Management                                          |

| 3.19            | Instruction Set Summary 53                                |

| 4               | Electrical Parameters56                                   |

| 4.1             | General Parameters 56                                     |

| 4.2             | DC Parameters 59                                          |

| 4.3             | Analog/Digital Converter Parameters                       |

| 4.4             | AC Parameters                                             |

| 4.4.1           | Definition of Internal Timing                             |

| 4.4.2           | On-chip Flash Operation                                   |

| 4.4.3           | External Clock Drive XTAL1 73                             |

| 4.4.4           | Testing Waveforms 74                                      |

| 4.4.5           | External Bus Timing                                       |

| 5               | Package and Reliability                                   |

| 5.1             | Packaging                                                 |

| 5.2             | Flash Memory Parameters                                   |

## **General Device Information**

Table 2

Pin Definitions and Functions (cont'd)

| Sym-<br>bol | Pin<br>Num. | Input<br>Outp. | Function                                                                                                                                                                                                                                               |                                                                                                                                                                           |  |  |

|-------------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| P3          |             | Ю              | Port 3 is a 15-bit bidirectional I/O port. Each pin can be programmed for input (output driver in high-impedance state) or output (configurable as push/pull or open drain driver). The input threshold of Port 3 is selectable (standard or special). |                                                                                                                                                                           |  |  |

| P3.0        | 59          | 0              | TOIN<br>TxD1<br>EX1IN                                                                                                                                                                                                                                  | ing Port 3 pins also serve for alternate functions: CAPCOM1 Timer T0 Count Input, ASC1 Clock/Data Output (Async./Sync), Fast External Interrupt 1 Input (alternate pin B) |  |  |

| P3.1        | 60          | 0<br>I/O<br>I  | T6OUT<br>RxD1<br>EX1IN                                                                                                                                                                                                                                 | GPT2 Timer T6 Toggle Latch Output, ASC1 Data Input (Async.) or Inp./Outp. (Sync.), Fast External Interrupt 1 Input (alternate pin A)                                      |  |  |

| P3.2        | 61          | 1              | CAPIN                                                                                                                                                                                                                                                  | GPT2 Register CAPREL Capture Input                                                                                                                                        |  |  |

| P3.3        | 62          | 0              | T3OUT                                                                                                                                                                                                                                                  | GPT1 Timer T3 Toggle Latch Output                                                                                                                                         |  |  |

| P3.4        | 63          | 1              | T3EUD                                                                                                                                                                                                                                                  | GPT1 Timer T3 External Up/Down Control Input                                                                                                                              |  |  |

| P3.5        | 64          | I              | T4IN                                                                                                                                                                                                                                                   | GPT1 Timer T4 Count/Gate/Reload/Capture Inp                                                                                                                               |  |  |

| P3.6        | 65          | I              | T3IN GPT1 Timer T3 Count/Gate Input                                                                                                                                                                                                                    |                                                                                                                                                                           |  |  |

| P3.7        | 66          | I              | T2IN                                                                                                                                                                                                                                                   | GPT1 Timer T2 Count/Gate/Reload/Capture Inp                                                                                                                               |  |  |

| P3.8        | 67          | I/O            | MRST0                                                                                                                                                                                                                                                  | SSC0 Master-Receive/Slave-Transmit In/Out.                                                                                                                                |  |  |

| P3.9        | 68          | I/O            | MTSR0 SSC0 Master-Transmit/Slave-Receive Out/In.                                                                                                                                                                                                       |                                                                                                                                                                           |  |  |

| P3.10       | 69          | 0              | TxD0 ASC0 Clock/Data Output (Async./Sync.),                                                                                                                                                                                                            |                                                                                                                                                                           |  |  |

|             |             |                | EX2IN                                                                                                                                                                                                                                                  | Fast External Interrupt 2 Input (alternate pin B)                                                                                                                         |  |  |

| P3.11       | 70          | I/O            | RxD0                                                                                                                                                                                                                                                   | ASC0 Data Input (Async.) or Inp./Outp. (Sync.),                                                                                                                           |  |  |

| P3.12       | 75          | 0              | EX2IN<br>BHE                                                                                                                                                                                                                                           | Fast External Interrupt 2 Input (alternate pin A)                                                                                                                         |  |  |

| F3.12       | 75          | 0              | WRH                                                                                                                                                                                                                                                    | External Memory High Byte Enable Signal, External Memory High Byte Write Strobe,                                                                                          |  |  |

|             |             |                | EX3IN                                                                                                                                                                                                                                                  | Fast External Interrupt 3 Input (alternate pin B)                                                                                                                         |  |  |

| P3.13       | 76          | 1/0            | SCLK0                                                                                                                                                                                                                                                  | SSC0 Master Clock Output/Slave Clock Input.,                                                                                                                              |  |  |

| 1 3.13      | 70          | 1,0            | EX3IN                                                                                                                                                                                                                                                  | Fast External Interrupt 3 Input (alternate pin A)                                                                                                                         |  |  |

| P3.15       | 77          | 0              | CLKOUT                                                                                                                                                                                                                                                 | Master Clock Output,                                                                                                                                                      |  |  |

| . 0.10      | ' '         | Ö              | FOUT                                                                                                                                                                                                                                                   | Programmable Frequency Output                                                                                                                                             |  |  |

| TCK         | 71          | I              | Debug System: JTAG Clock Input                                                                                                                                                                                                                         |                                                                                                                                                                           |  |  |

| TDI         | 72          |                | Debug System: JTAG Data In                                                                                                                                                                                                                             |                                                                                                                                                                           |  |  |

| TDO         | 73          | 0              | Debug System: JTAG Data Out                                                                                                                                                                                                                            |                                                                                                                                                                           |  |  |

| TMS         | 74          | I              | Debug System: JTAG Test Mode Selection                                                                                                                                                                                                                 |                                                                                                                                                                           |  |  |

## **General Device Information**

Table 2 Pin Definitions and Functions (cont'd)

| Sym-<br>bol | Pin<br>Num. | Input<br>Outp. | Function                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|-------------|----------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P20         |             | Ю              | programme<br>state) or ou<br>(standard of | a 6-bit bidirectional I/O port. Each pin can be ed for input (output driver in high-impedance utput. The input threshold of Port 20 is selectable or special).  ng Port 20 pins also serve for alternate functions:                                                                                                                                                                                                                            |

| P20.0       | 90          | 0              | RD                                        | External Memory Read Strobe, activated for every external instruction or data read access.                                                                                                                                                                                                                                                                                                                                                     |

| P20.1       | 91          | О              | WR/WRL                                    | External Memory Write Strobe. In WR-mode this pin is activated for every external data write access. In WRL-mode this pin is activated for low byte data write accesses on a 16-bit bus, and for every data write access on an 8-bit bus.                                                                                                                                                                                                      |

| P20.2       | 92          | I              | READY                                     | READY Input. When the READY function is enabled, memory cycle time waitstates can be forced via this pin during an external access.                                                                                                                                                                                                                                                                                                            |

| P20.4       | 93          | 0              | ALE                                       | Address Latch Enable Output. Can be used for latching the address into external memory or an address latch in the                                                                                                                                                                                                                                                                                                                              |

| P20.5       | 94          | I              | ĒĀ                                        | multiplexed bus modes. External Access Enable pin.  A low-level at this pin during and after Reset forces the XC167 to latch the configuration from PORT0 and pin RD, and to begin instruction execution out of external memory.  A high-level forces the XC167 to latch the configuration from pins RD, ALE, and WR, and to begin instruction execution out of the internal program memory. "ROMless" versions must have this pin fied to '0' |

| P20.12      | 3           | O              | RSTOUT  Note: Port                        | have this pin tied to '0'.  Internal Reset Indication Output.  Is activated asynchronously with an external hardware reset. It may also be activated (selectable) synchronously with an internal software or watchdog reset.  Is deactivated upon the execution of the EINIT instruction, optionally at the end of reset, or at any time (before EINIT) via user software.  20 pins may input configuration values (see EA).                   |

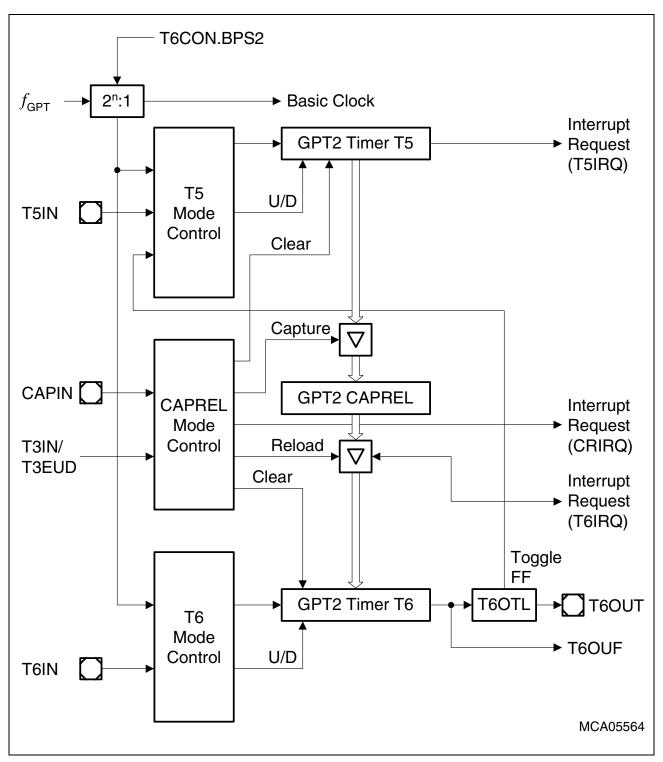

Figure 8 Block Diagram of GPT2

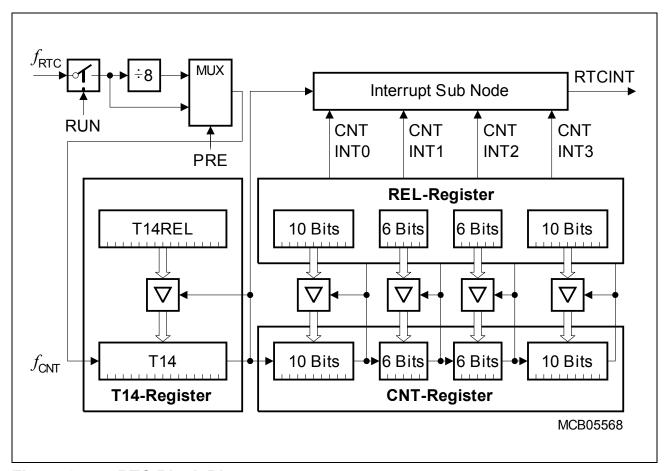

## 3.9 Real Time Clock

The Real Time Clock (RTC) module of the XC167 is directly clocked via a separate clock driver either with the on-chip auxiliary oscillator frequency ( $f_{\rm RTC}$  =  $f_{\rm OSCa}$ ) or with the prescaled on-chip main oscillator frequency ( $f_{\rm RTC}$  =  $f_{\rm OSCm}$ /32). It is therefore independent from the selected clock generation mode of the XC167.

The RTC basically consists of a chain of divider blocks:

- a selectable 8:1 divider (on off)

- the reloadable 16-bit timer T14

- the 32-bit RTC timer block (accessible via registers RTCH and RTCL), made of:

- a reloadable 10-bit timer

- a reloadable 6-bit timer

- a reloadable 6-bit timer

- a reloadable 10-bit timer

All timers count up. Each timer can generate an interrupt request. All requests are combined to a common node request.

Figure 9 RTC Block Diagram

Note: The registers associated with the RTC are not affected by a reset in order to maintain the correct system time even when intermediate resets are executed.

Data Sheet 42 V1.3, 2006-08

The RTC module can be used for different purposes:

- System clock to determine the current time and date, optionally during idle mode, sleep mode, and power down mode

- Cyclic time based interrupt, to provide a system time tick independent of CPU frequency and other resources, e.g. to wake up regularly from idle mode.

- 48-bit timer for long term measurements (maximum timespan is > 100 years).

- Alarm interrupt for wake-up on a defined time

Data Sheet 43 V1.3, 2006-08

## 3.11 Asynchronous/Synchronous Serial Interfaces (ASC0/ASC1)

The Asynchronous/Synchronous Serial Interfaces ASCO/ASC1 (USARTs) provide serial communication with other microcontrollers, processors, terminals or external peripheral components. They are upward compatible with the serial ports of the Infineon 8-bit microcontroller families and support full-duplex asynchronous communication and half-duplex synchronous communication. A dedicated baud rate generator with a fractional divider precisely generates all standard baud rates without oscillator tuning. For transmission, reception, error handling, and baudrate detection 5 separate interrupt vectors are provided.

In asynchronous mode, 8- or 9-bit data frames (with optional parity bit) are transmitted or received, preceded by a start bit and terminated by one or two stop bits. For multiprocessor communication, a mechanism to distinguish address from data bytes has been included (8-bit data plus wake-up bit mode). IrDA data transmissions up to 115.2 kbit/s with fixed or programmable IrDA pulse width are supported.

In synchronous mode, bytes (8 bits) are transmitted or received synchronously to a shift clock which is generated by the ASC0/1. The LSB is always shifted first.

In both modes, transmission and reception of data is FIFO-buffered. An autobaud detection unit allows to detect asynchronous data frames with its baudrate and mode with automatic initialization of the baudrate generator and the mode control bits.

A number of optional hardware error detection capabilities has been included to increase the reliability of data transfers. A parity bit can automatically be generated on transmission or be checked on reception. Framing error detection allows to recognize data frames with missing stop bits. An overrun error will be generated, if the last character received has not been read out of the receive buffer register at the time the reception of a new character is complete.

#### **Summary of Features**

- Full-duplex asynchronous operating modes

- 8- or 9-bit data frames, LSB first, one or two stop bits, parity generation/checking

- Baudrate from 2.5 Mbit/s to 0.6 bit/s (@ 40 MHz)

- Multiprocessor mode for automatic address/data byte detection

- Support for IrDA data transmission/reception up to max. 115.2 kbit/s (@ 40 MHz)

- Loop-back capability

- Auto baudrate detection

- Half-duplex 8-bit synchronous operating mode at 5 Mbit/s to 406.9 bit/s (@ 40 MHz)

- Buffered transmitter/receiver with FIFO support (8 entries per direction)

- Loop-back option available for testing purposes

- Interrupt generation on transmitter buffer empty condition, last bit transmitted condition, receive buffer full condition, error condition (frame, parity, overrun error), start and end of an autobaud detection

Data Sheet 45 V1.3, 2006-08

## **Summary of Features**

- CAN functionality according to CAN specification V2.0 B active

- Data transfer rate up to 1 Mbit/s

- Flexible and powerful message transfer control and error handling capabilities

- Full-CAN functionality and Basic CAN functionality for each message object

- 32 flexible message objects

- Assignment to one of the two CAN nodes

- Configuration as transmit object or receive object

- Concatenation to a 2-, 4-, 8-, 16-, or 32-message buffer with FIFO algorithm

- Handling of frames with 11-bit or 29-bit identifiers

- Individual programmable acceptance mask register for filtering for each object

- Monitoring via a frame counter

- Configuration for Remote Monitoring Mode

- Up to eight individually programmable interrupt nodes can be used

- CAN Analyzer Mode for bus monitoring is implemented

Note: When a CAN node has the interface lines assigned to Port 4, the segment address output on Port 4 must be limited. CS lines can be used to increase the total amount of addressable external memory.

#### 3.14 IIC Bus Module

The integrated IIC Bus Module handles the transmission and reception of frames over the two-line IIC bus in accordance with the IIC Bus specification. The IIC Module can operate in slave mode, in master mode or in multi-master mode. It can receive and transmit data using 7-bit or 10-bit addressing. Up to 4 send/receive data bytes can be stored in the extended buffers.

Several physical interfaces (port pins) can be established under software control. Data can be transferred at speeds up to 400 kbit/s.

Two interrupt nodes dedicated to the IIC module allow efficient interrupt service and also support operation via PEC transfers.

Note: The port pins associated with the IIC interfaces must be switched to open drain mode, as required by the IIC specification.

Data Sheet 48 V1.3, 2006-08

## 4 Electrical Parameters

#### 4.1 General Parameters

Table 9 Absolute Maximum Ratings

| Parameter                                                             | Symbol    | Limit Values |                        | Unit | Notes      |

|-----------------------------------------------------------------------|-----------|--------------|------------------------|------|------------|

|                                                                       |           | Min.         | Max.                   |      |            |

| Storage temperature                                                   | $T_{ST}$  | -65          | 150                    | °C   | 1)         |

| Junction temperature                                                  | $T_{J}$   | -40          | 150                    | °C   | under bias |

| Voltage on $V_{\rm DDI}$ pins with respect to ground ( $V_{\rm SS}$ ) | $V_{DDI}$ | -0.5         | 3.25                   | V    | _          |

| Voltage on $V_{\rm DDP}$ pins with respect to ground ( $V_{\rm SS}$ ) | $V_{DDP}$ | -0.5         | 6.2                    | V    | _          |

| Voltage on any pin with respect to ground ( $V_{\rm SS}$ )            | $V_{IN}$  | -0.5         | V <sub>DDP</sub> + 0.5 | V    | 2)         |

| Input current on any pin during overload condition                    | _         | -10          | 10                     | mA   | _          |

| Absolute sum of all input currents during overload condition          | _         | _            | 100                    | mA   | _          |

<sup>1)</sup> Moisture Sensitivity Level (MSL) 3, conforming to Jedec J-STD-020C for 260 °C for PG-TQFP-144-7, and 240 °C for P-TQFP-144-19.

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{\rm IN} > V_{\rm DDP}$  or  $V_{\rm IN} < V_{\rm SS}$ ) the voltage on  $V_{\rm DDP}$  pins with respect to ground ( $V_{\rm SS}$ ) must not exceed the values defined by the absolute maximum ratings.

<sup>2)</sup> Input pins XTAL1/XTAL3 belong to the core voltage domain. Therefore, input voltages must be within the range defined for  $V_{

m DDI}$ .

#### **Operating Conditions**

The following operating conditions must not be exceeded to ensure correct operation of the XC167. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

Table 10 Operating Condition Parameters

| Parameter                                 | Symbol            | Limit Values |                        | Unit | Notes                                         |  |

|-------------------------------------------|-------------------|--------------|------------------------|------|-----------------------------------------------|--|

|                                           |                   | Min.         | Max.                   |      |                                               |  |

| Digital supply voltage for the core       | $V_{DDI}$         | 2.35         | 2.7                    | V    | Active mode,<br>$f_{CPU} = f_{CPUmax}^{1)2)}$ |  |

| Digital supply voltage for IO pads        | $V_{DDP}$         | 4.4          | 5.5                    | V    | Active mode <sup>2)</sup>                     |  |

| Supply Voltage Difference                 | $\Delta V_{DD}$   | -0.5         | _                      | V    | $V_{\rm DDP}$ - $V_{\rm DDI}^{3)}$            |  |

| Digital ground voltage                    | $V_{SS}$          | 0            |                        | V    | Reference voltage                             |  |

| Overload current                          | $I_{OV}$          | -5           | 5                      | mA   | Per IO pin <sup>4)5)</sup>                    |  |

|                                           |                   | -2           | 5                      | mA   | Per analog input pin <sup>4)5)</sup>          |  |

| Overload current coupling                 | $K_{OVA}$         | _            | $1.0 \times 10^{-4}$   | _    | <i>I</i> <sub>OV</sub> > 0                    |  |

| factor for analog inputs <sup>6)</sup>    |                   | _            | $1.5 \times 10^{-3}$   | _    | <i>I</i> <sub>OV</sub> < 0                    |  |

| Overload current coupling                 | $K_{OVD}$         | _            | 5.0 × 10 <sup>-3</sup> | _    | <i>I</i> <sub>OV</sub> > 0                    |  |

| factor for digital I/O pins <sup>6)</sup> |                   | _            | $1.0 \times 10^{-2}$   | _    | I <sub>OV</sub> < 0                           |  |

| Absolute sum of overload currents         | $\Sigma  I_{OV} $ | _            | 50                     | mA   | 5)                                            |  |

| External Load<br>Capacitance              | $C_{L}$           | _            | 50                     | pF   | Pin drivers in default mode <sup>7)</sup>     |  |

| Ambient temperature                       | $T_{A}$           | _            | _                      | °C   | see Table 1                                   |  |

<sup>1)</sup>  $f_{\text{CPUmax}}$  = 40 MHz for devices marked ... 40F,  $f_{\text{CPUmax}}$  = 20 MHz for devices marked ... 20F.

<sup>2)</sup> External circuitry must guarantee low level at the RSTIN pin at least until both power supply voltages have reached their operating range.

<sup>3)</sup> This limitation must be fulfilled under all operating conditions including power-ramp-up, power-ramp-down, and power-save modes.

<sup>4)</sup> Overload conditions occur if the standard operating conditions are exceeded, i.e. the voltage on any pin exceeds the specified range:  $V_{\rm OV} > V_{\rm DDP} + 0.5 \ {\rm V} \ (I_{\rm OV} > 0)$  or  $V_{\rm OV} < V_{\rm SS}$  - 0.5 V ( $I_{\rm OV} < 0$ ). The absolute sum of input overload currents on all pins may not exceed **50 mA**. The supply voltages must remain within the specified limits.

Proper operation is not guaranteed if overload conditions occur on functional pins such as XTAL1,  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ , etc.

<sup>5)</sup> Not subject to production test - verified by design/characterization.

- 4) The total supply current in Sleep and Power down mode is the sum of the temperature dependent leakage current and the frequency dependent current for RTC and main oscillator or auxiliary oscillator (if active).

- 5) This parameter is determined mainly by the transistor leakage currents. This current heavily depends on the junction temperature (see **Figure 13**). The junction temperature  $T_J$  is the same as the ambient temperature  $T_A$  if no current flows through the port output drivers. Otherwise, the resulting temperature difference must be taken into account.

- 6) All inputs (including pins configured as inputs) at 0 V to 0.1 V or at  $V_{\text{DDP}}$  0.1 V to  $V_{\text{DDP}}$ , all outputs (including pins configured as outputs) disconnected. This parameter is tested at 25 °C and is valid for  $T_{\text{J}} \ge$  25 °C.

- 7) This parameter is determined mainly by the current consumed by the oscillator switched to low gain mode (see Figure 12). This current, however, is influenced by the external oscillator circuitry (crystal, capacitors). The given values refer to a typical circuitry and may change in case of a not optimized external oscillator circuitry.

Data Sheet 62 V1.3, 2006-08

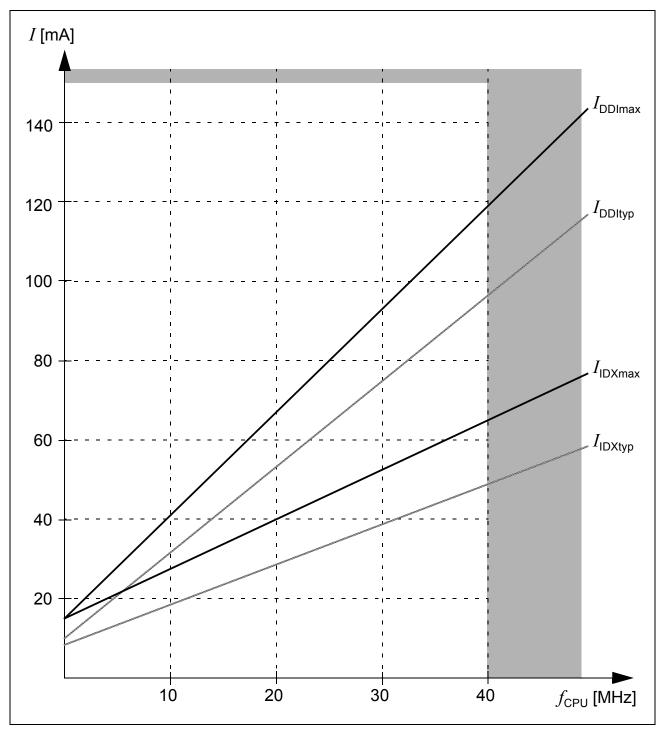

Figure 11 Supply/Idle Current as a Function of Operating Frequency

Sample time and conversion time of the XC167's A/D Converter are programmable. In compatibility mode, the above timing can be calculated using **Table 15**. The limit values for  $f_{BC}$  must not be exceeded when selecting ADCTC.

Table 15 A/D Converter Computation Table 1)

| ADCON.15 14<br>(ADCTC) | A/D Converter Basic Clock $f_{\rm BC}$ | ADCON.13 12<br>(ADSTC) | Sample Time $t_{\rm S}$ |

|------------------------|----------------------------------------|------------------------|-------------------------|

| 00                     | $f_{SYS}$ / 4                          | 00                     | $t_{\rm BC} \times 8$   |

| 01                     | $f_{SYS}$ / 2                          | 01                     | $t_{\rm BC} \times 16$  |

| 10                     | f <sub>SYS</sub> / 16                  | 10                     | $t_{\rm BC} \times 32$  |

| 11                     | f <sub>SYS</sub> / 8                   | 11                     | $t_{\rm BC} \times 64$  |

<sup>1)</sup> These selections are available in compatibility mode. An improved mechanism to control the ADC input clock can be selected.

## **Converter Timing Example:**

Assumptions:  $f_{SYS} = 40 \text{ MHz}$  (i.e.  $t_{SYS} = 25 \text{ ns}$ ), ADCTC = '01', ADSTC = '00'

Basic clock  $f_{BC} = f_{SYS} / 2 = 20 \text{ MHz, i.e. } t_{BC} = 50 \text{ ns}$

Sample time  $t_S = t_{BC} \times 8 = 400 \text{ ns}$

Conversion 10-bit:

With post-calibr.  $t_{\text{C10P}} = 52 \times t_{\text{BC}} + t_{\text{S}} + 6 \times t_{\text{SYS}} = (2600 + 400 + 150) \text{ ns} = 3.15 \,\mu\text{s}$

Post-calibr. off  $t_{C10} = 40 \times t_{BC} + t_{S} + 6 \times t_{SYS} = (2000 + 400 + 150) \text{ ns} = 2.55 \text{ }\mu\text{s}$

Conversion 8-bit:

With post-calibr.  $t_{C8P} = 44 \times t_{BC} + t_{S} + 6 \times t_{SYS} = (2200 + 400 + 150) \text{ ns} = 2.75 \ \mu\text{s}$

Post-calibr. off  $t_{C8} = 32 \times t_{BC} + t_{S} + 6 \times t_{SYS} = (1600 + 400 + 150) \text{ ns} = 2.15 \,\mu\text{s}$

The specification of the external timing (AC Characteristics) depends on the period of the CPU clock, called "TCP".

The other peripherals are supplied with the system clock signal  $f_{SYS}$  which has the same frequency as the CPU clock signal  $f_{CPU}$ .

## **Bypass Operation**

When bypass operation is configured (PLLCTRL =  $0x_B$ ) the master clock is derived from the internal oscillator (input clock signal XTAL1) through the input- and output-prescalers:

$$f_{MC} = f_{OSC} / ((PLLIDIV+1) \times (PLLODIV+1)).$$

If both divider factors are selected as '1' (PLLIDIV = PLLODIV = '0') the frequency of  $f_{\rm MC}$  directly follows the frequency of  $f_{\rm OSC}$  so the high and low time of  $f_{\rm MC}$  is defined by the duty cycle of the input clock  $f_{\rm OSC}$ .

The lowest master clock frequency is achieved by selecting the maximum values for both divider factors:

$$f_{MC} = f_{OSC} / ((3 + 1) \times (14 + 1)) = f_{OSC} / 60.$$

## Phase Locked Loop (PLL)

When PLL operation is configured (PLLCTRL =  $11_B$ ) the on-chip phase locked loop is enabled and provides the master clock. The PLL multiplies the input frequency by the factor  $\mathbf{F}$  ( $f_{MC} = f_{OSC} \times \mathbf{F}$ ) which results from the input divider, the multiplication factor, and the output divider ( $\mathbf{F} = \text{PLLMUL+1}$  / (PLLIDIV+1  $\times$  PLLODIV+1)). The PLL circuit synchronizes the master clock to the input clock. This synchronization is done smoothly, i.e. the master clock frequency does not change abruptly.

Due to this adaptation to the input clock the frequency of  $f_{\rm MC}$  is constantly adjusted so it is locked to  $f_{\rm OSC}$ . The slight variation causes a jitter of  $f_{\rm MC}$  which also affects the duration of individual TCMs.

The timing listed in the AC Characteristics refers to TCPs. Because  $f_{\rm CPU}$  is derived from  $f_{\rm MC}$ , the timing must be calculated using the minimum TCP possible under the respective circumstances.

The actual minimum value for TCP depends on the jitter of the PLL. As the PLL is constantly adjusting its output frequency so it corresponds to the applied input frequency (crystal or oscillator) the relative deviation for periods of more than one TCP is lower than for one single TCP (see formula and **Figure 16**).

This is especially important for bus cycles using waitstates and e.g. for the operation of timers, serial interfaces, etc. For all slower operations and longer periods (e.g. pulse train generation or measurement, lower baudrates, etc.) the deviation caused by the PLL jitter is negligible.

Data Sheet 69 V1.3, 2006-08

## 4.4.2 On-chip Flash Operation

The XC167's Flash module delivers data within a fixed access time (see Table 17).

Accesses to the Flash module are controlled by the PMI and take 1+WS clock cycles, where WS is the number of Flash access waitstates selected via bitfield WSFLASH in register IMBCTRL. The resulting duration of the access phase must cover the access time  $t_{\rm ACC}$  of the Flash array. Therefore, the required Flash waitstates depend on the actual system frequency.

Note: The Flash access waitstates only affect non-sequential accesses. Due to prefetching mechanisms, the performance for sequential accesses (depending on the software structure) is only partially influenced by waitstates.

In typical applications, eliminating one waitstate increases the average performance by 5% ... 15%.

**Table 17** Flash Characteristics (Operating Conditions apply)

| Parameter                           | Symb      | ool | Limit Values |                 |      | Unit |

|-------------------------------------|-----------|-----|--------------|-----------------|------|------|

|                                     |           |     | Min.         | Тур.            | Max. |      |

| Flash module access time            | $t_{ACC}$ | CC  | _            | _               | 50   | ns   |

| Programming time per 128-byte block | $t_{PR}$  | CC  | _            | 2 <sup>1)</sup> | 5    | ms   |

| Erase time per sector               | $t_{ER}$  | CC  | _            | 2001)           | 500  | ms   |

<sup>1)</sup> Programming and erase time depends on the system frequency. Typical values are valid for 40 MHz.

Example: For an operating frequency of 40 MHz (clock cycle = 25 ns), devices can be operated with 1 waitstate:  $((1+1) \times 25 \text{ ns}) \ge 50 \text{ ns}$ .

**Table 18** indicates the interrelation of waitstates and system frequency.

**Table 18** Flash Access Waitstates

| Required Waitstates               | Frequency Range for      |

|-----------------------------------|--------------------------|

| 0 WS (WSFLASH = 00 <sub>B</sub> ) | $f_{CPU} \leq 20 \; MHz$ |

| 1 WS (WSFLASH = 01 <sub>B</sub> ) | $f_{CPU} \leq 40 \; MHz$ |

Note: The maximum achievable system frequency is limited by the properties of the respective derivative, i.e. 40 MHz (or 20 MHz for xxx-16F20F devices).

Data Sheet 72 V1.3, 2006-08

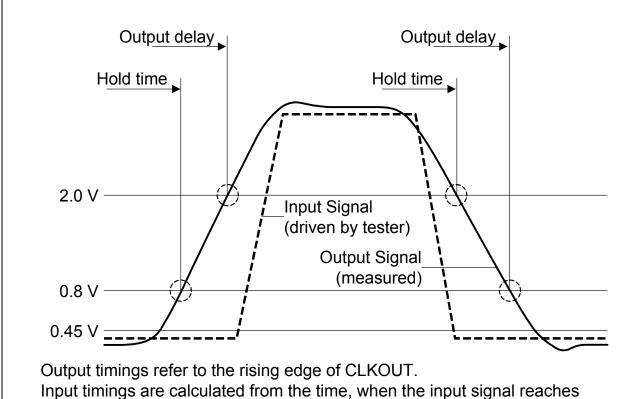

#### **Testing Waveforms** 4.4.4

$V_{\rm IH}$  or  $V_{\rm II}$ , respectively.

MCD05556

Figure 18 **Input Output Waveforms**

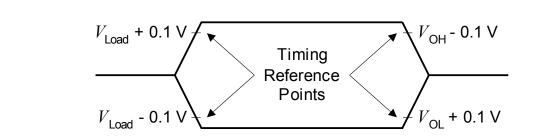

For timing purposes a port pin is no longer floating when a 100 mV change from load voltage occurs, but begins to float when a 100 mV change from the loaded  $V_{\rm OH}/V_{\rm OI}$  level occurs ( $I_{\rm OH}/I_{\rm OI}$  = 20 mA).

MCA05565

**Float Waveforms** Figure 19

## **Bus Cycle Control via READY Input**

The duration of an external bus cycle can be controlled by the external circuitry via the READY input signal. The polarity of this input signal can be selected.

**Synchronous** READY permits the shortest possible bus cycle but requires the input signal to be synchronous to the reference signal CLKOUT.

**Asynchronous** READY puts no timing constraints on the input signal but incurs one waitstate minimum due to the additional synchronization stage. The minimum duration of an asynchronous READY signal to be safely synchronized must be one CLKOUT period plus the input setup time.

An active READY signal can be deactivated in response to the trailing (rising) edge of the corresponding command (RD or WR).

If the next following bus cycle is READY-controlled, an active READY signal must be disabled before the first valid sample point for the next bus cycle. This sample point depends on the programmed phases of the next following cycle.

Data Sheet 80 V1.3, 2006-08

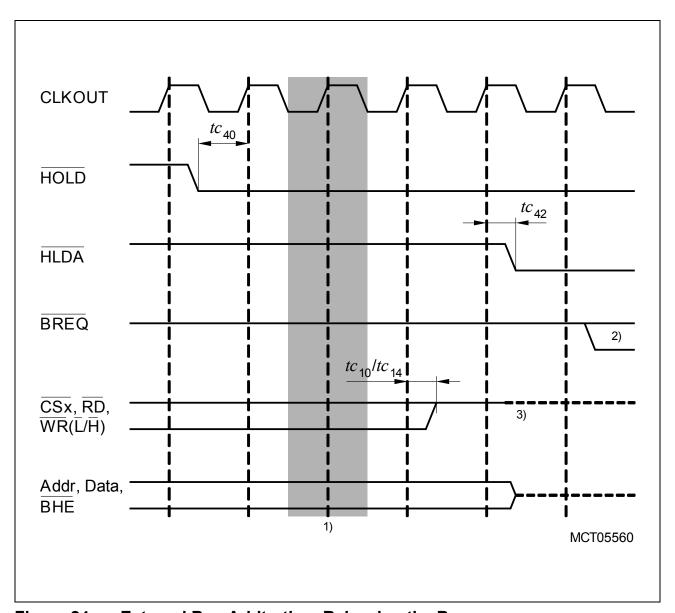

Figure 24 External Bus Arbitration, Releasing the Bus

#### **Notes**

- 1. The XC167 will complete the currently running bus cycle before granting bus access.

- 2. This is the first possibility for  $\overline{BREQ}$  to get active.

- 3. The control outputs will be resistive high (pull-up) after being driven inactive (ALE will be low).

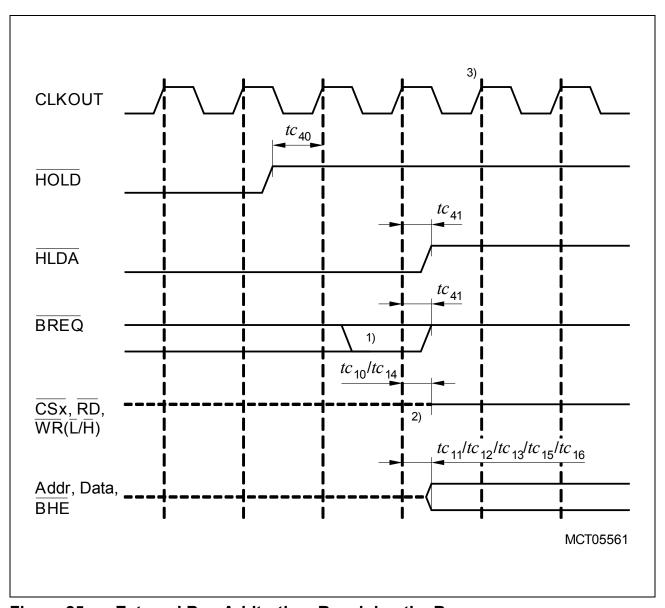

Figure 25 External Bus Arbitration, Regaining the Bus

#### **Notes**

- 1. This is the last chance for BREQ to trigger the indicated regain-sequence.

Even if BREQ is activated earlier, the regain-sequence is initiated by HOLD going high. Please note that HOLD may also be deactivated without the XC167 requesting the bus.

- 2. The control outputs will be resistive high (pull-up) before being driven inactive (ALE will be low).

- 3. The next XC167 driven bus cycle may start here.

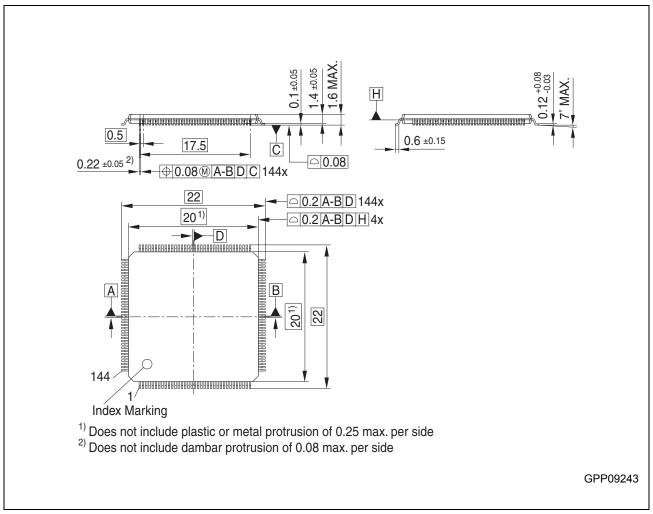

## Package and Reliability

Figure 27 P-TQFP-144-19 (Plastic Thin Quad Flat Package)