Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Last Time Buy                                                                    |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                       |

| Peripherals                | PWM, WDT                                                                         |

| Number of I/O              | 103                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 2.7V                                                                     |

| Data Converters            | A/D 16x8/10b                                                                     |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP                                                                         |

| Supplier Device Package    | PG-TQFP-144-7                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc167ci16f40fbbkxuma1 |

## **Table of Contents**

# **Table of Contents**

| 1               | Summary of Features 4                                     |

|-----------------|-----------------------------------------------------------|

| <b>2</b><br>2.1 | General Device Information   7     Introduction   7       |

| 2.2             | Pin Configuration and Definition 8                        |

| 3               | Functional Description                                    |

| 3.1             | Memory Subsystem and Organization                         |

| 3.2             | External Bus Controller                                   |

| 3.3             | Central Processing Unit (CPU)                             |

| 3.4             | Interrupt System                                          |

| 3.5             | On-Chip Debug Support (OCDS)                              |

| 3.6             | Capture/Compare Units (CAPCOM1/2)                         |

| 3.7             | The Capture/Compare Unit CAPCOM6                          |

| 3.8             | General Purpose Timer (GPT12E) Unit                       |

| 3.9             | Real Time Clock 42                                        |

| 3.10            | A/D Converter                                             |

| 3.11            | Asynchronous/Synchronous Serial Interfaces (ASC0/ASC1) 45 |

| 3.12            | High Speed Synchronous Serial Channels (SSC0/SSC1) 46     |

| 3.13            | TwinCAN Module                                            |

| 3.14            | IIC Bus Module                                            |

| 3.15            | Watchdog Timer 49                                         |

| 3.16            | Clock Generation                                          |

| 3.17            | Parallel Ports                                            |

| 3.18            | Power Management                                          |

| 3.19            | Instruction Set Summary 53                                |

| 4               | Electrical Parameters56                                   |

| 4.1             | General Parameters 56                                     |

| 4.2             | DC Parameters 59                                          |

| 4.3             | Analog/Digital Converter Parameters                       |

| 4.4             | AC Parameters                                             |

| 4.4.1           | Definition of Internal Timing                             |

| 4.4.2           | On-chip Flash Operation                                   |

| 4.4.3           | External Clock Drive XTAL1 73                             |

| 4.4.4           | Testing Waveforms 74                                      |

| 4.4.5           | External Bus Timing                                       |

| 5               | Package and Reliability                                   |

| 5.1             | Packaging                                                 |

| 5.2             | Flash Memory Parameters                                   |

#### **General Device Information**

## 2.2 Pin Configuration and Definition

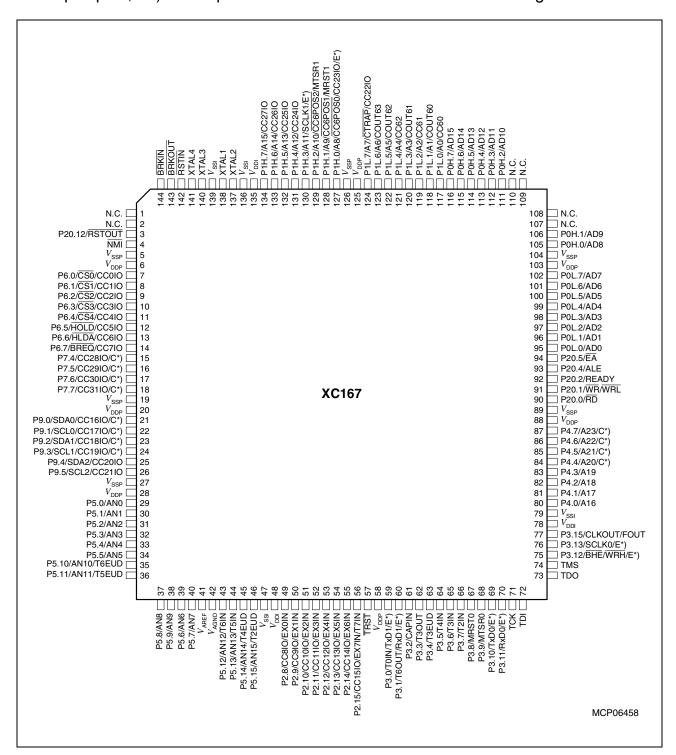

The pins of the XC167 are described in detail in **Table 2**, including all their alternate functions. **Figure 2** summarizes all pins in a condensed way, showing their location on the 4 sides of the package. E\*) and C\*) mark pins to be used as alternate external interrupt inputs, C\*) marks pins that can have CAN interface lines assigned to them.

Figure 2 Pin Configuration (top view)

## **General Device Information**

Table 2

Pin Definitions and Functions (cont'd)

| Sym-<br>bol | Pin<br>Num. | Input<br>Outp. | Function                                                 |                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|-------------|-------------|----------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| P3          |             | Ю              | programme<br>state) or or<br>driver). The<br>or special) | Port 3 is a 15-bit bidirectional I/O port. Each pin can be programmed for input (output driver in high-impedance state) or output (configurable as push/pull or open drain driver). The input threshold of Port 3 is selectable (standard or special).  The following Port 3 pins also serve for alternate functions: |  |  |  |  |

| P3.0        | 59          | I<br>0<br>I    | TOIN<br>TxD1<br>EX1IN                                    | CAPCOM1 Timer T0 Count Input, ASC1 Clock/Data Output (Async./Sync), Fast External Interrupt 1 Input (alternate pin B)                                                                                                                                                                                                 |  |  |  |  |

| P3.1        | 60          | 0<br>I/O<br>I  | T6OUT<br>RxD1<br>EX1IN                                   | GPT2 Timer T6 Toggle Latch Output, ASC1 Data Input (Async.) or Inp./Outp. (Sync.), Fast External Interrupt 1 Input (alternate pin A)                                                                                                                                                                                  |  |  |  |  |

| P3.2        | 61          | 1              | CAPIN                                                    | GPT2 Register CAPREL Capture Input                                                                                                                                                                                                                                                                                    |  |  |  |  |

| P3.3        | 62          | 0              | T3OUT                                                    | GPT1 Timer T3 Toggle Latch Output                                                                                                                                                                                                                                                                                     |  |  |  |  |

| P3.4        | 63          | 1              | T3EUD                                                    | GPT1 Timer T3 External Up/Down Control Input                                                                                                                                                                                                                                                                          |  |  |  |  |

| P3.5        | 64          | 1              | T4IN                                                     | GPT1 Timer T4 Count/Gate/Reload/Capture Inp                                                                                                                                                                                                                                                                           |  |  |  |  |

| P3.6        | 65          | I              | T3IN                                                     | · ·                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| P3.7        | 66          | I              | T2IN                                                     | GPT1 Timer T2 Count/Gate/Reload/Capture Inp                                                                                                                                                                                                                                                                           |  |  |  |  |

| P3.8        | 67          | I/O            | MRST0                                                    |                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| P3.9        | 68          | I/O            |                                                          | MTSR0 SSC0 Master-Transmit/Slave-Receive Out/In.                                                                                                                                                                                                                                                                      |  |  |  |  |

| P3.10       | 69          | 0              | TxD0                                                     |                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|             |             |                |                                                          | EX2IN Fast External Interrupt 2 Input (alternate pin B)                                                                                                                                                                                                                                                               |  |  |  |  |

| P3.11       | 70          | I/O            | RxD0                                                     | ASC0 Data Input (Async.) or Inp./Outp. (Sync.),                                                                                                                                                                                                                                                                       |  |  |  |  |

| P3.12       | 75          |                | EX2IN<br>BHE                                             | Fast External Interrupt 2 Input (alternate pin A)                                                                                                                                                                                                                                                                     |  |  |  |  |

| P3.12       | 75          | 0              | WRH                                                      | External Memory High Byte Enable Signal, External Memory High Byte Write Strobe,                                                                                                                                                                                                                                      |  |  |  |  |

|             |             |                | EX3IN                                                    | Fast External Interrupt 3 Input (alternate pin B)                                                                                                                                                                                                                                                                     |  |  |  |  |

| P3.13       | 76          | 1/0            | SCLK0                                                    | SSC0 Master Clock Output/Slave Clock Input.,                                                                                                                                                                                                                                                                          |  |  |  |  |

| 1 3.13      | 10          |                | EX3IN                                                    | Fast External Interrupt 3 Input (alternate pin A)                                                                                                                                                                                                                                                                     |  |  |  |  |

| P3.15       | 77          | o              | CLKOUT                                                   | Master Clock Output,                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 1 0.10      |             | Ö              | FOUT                                                     | Programmable Frequency Output                                                                                                                                                                                                                                                                                         |  |  |  |  |

| TCK         | 71          | I              | Debug Sys                                                | stem: JTAG Clock Input                                                                                                                                                                                                                                                                                                |  |  |  |  |

| TDI         | 72          | I              | Debug Sys                                                | stem: JTAG Data In                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| TDO         | 73          | 0              | Debug Sys                                                | Debug System: JTAG Data Out                                                                                                                                                                                                                                                                                           |  |  |  |  |

| TMS         | 74          | I              | Debug Sys                                                | stem: JTAG Test Mode Selection                                                                                                                                                                                                                                                                                        |  |  |  |  |

## **General Device Information**

Table 2

Pin Definitions and Functions (cont'd)

| Sym-<br>bol    | Pin<br>Num.           | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|----------------|-----------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| XTAL2<br>XTAL1 | 137<br>138            | O              | <ul> <li>XTAL2: Output of the main oscillator amplifier circuit</li> <li>XTAL1: Input to the main oscillator amplifier and input to the internal clock generator</li> <li>To clock the device from an external source, drive XTAL1, while leaving XTAL2 unconnected. Minimum and maximum high/low and rise/fall times specified in the AC Characteristics must be observed.</li> <li>Note: Input pin XTAL1 belongs to the core voltage domain Therefore, input voltages must be within the range</li> </ul>         |  |  |  |  |

|                |                       |                | defined for $V_{\mathrm{DDI}}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| XTAL3<br>XTAL4 | 140<br>141            | 0              | XTAL3: Input to the auxiliary (32-kHz) oscillator amplifier XTAL4: Output of the auxiliary (32-kHz) oscillator amplifier circuit  To clock the device from an external source, drive XTAL3, while leaving XTAL4 unconnected. Minimum and maximum high/low and rise/fall times specified in the AC Characteristics must be observed.                                                                                                                                                                                 |  |  |  |  |

|                |                       |                | Note: Input pin XTAL3 belongs to the core voltage domain. Therefore, input voltages must be within the range defined for $V_{\mathrm{DDI}}$ .                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| RSTIN          | 142                   | I              | Reset Input with Schmitt-Trigger characteristics. A low-level at this pin while the oscillator is running resets the XC167. A spike filter suppresses input pulses < 10 ns. Input pulses > 100 ns safely pass the filter. The minimum duration for a safe recognition should be 100 ns + 2 CPU clock cycles.  Note: The reset duration must be sufficient to let the hardware configuration signals settle.  External circuitry must guarantee low-level at the RSTIN pin at least until both power supply voltages |  |  |  |  |

|                |                       |                | have reached the operating range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| BRK<br>OUT     | 143                   | О              | Debug System: Break Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| BRKIN          | 144                   | I              | Debug System: Break In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| NC             | 1, 2,<br>107 -<br>110 | _              | No connection. It is recommended not to connect these pins to the PCB.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

The EBC also controls accesses to resources connected to the on-chip LXBus. The LXBus is an internal representation of the external bus and allows accessing integrated peripherals and modules in the same way as external components.

The TwinCAN module is connected and accessed via the LXBus.

Table 4 XC167 Interrupt Nodes (cont'd)

| Source of Interrupt or PEC<br>Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                    |

|-----------------------------------------------|---------------------|----------------------------------|-----------------------------------|

| ASC1 Autobaud                                 | ASC1_ABIC           | xx'0108 <sub>H</sub>             | 42 <sub>H</sub> / 66 <sub>D</sub> |

| End of PEC Subchannel                         | EOPIC               | xx'0130 <sub>H</sub>             | 4C <sub>H</sub> / 76 <sub>D</sub> |

| CAPCOM6 Timer T12                             | CCU6_T12IC          | xx'0134 <sub>H</sub>             | 4D <sub>H</sub> / 77 <sub>D</sub> |

| CAPCOM6 Timer T13                             | CCU6_T13IC          | xx'0138 <sub>H</sub>             | 4E <sub>H</sub> / 78 <sub>D</sub> |

| CAPCOM6 Emergency                             | CCU6_EIC            | xx'013C <sub>H</sub>             | 4F <sub>H</sub> / 79 <sub>D</sub> |

| CAPCOM6                                       | CCU6_IC             | xx'0140 <sub>H</sub>             | 50 <sub>H</sub> / 80 <sub>D</sub> |

| SSC1 Transmit                                 | SSC1_TIC            | xx'0144 <sub>H</sub>             | 51 <sub>H</sub> / 81 <sub>D</sub> |

| SSC1 Receive                                  | SSC1_RIC            | xx'0148 <sub>H</sub>             | 52 <sub>H</sub> / 82 <sub>D</sub> |

| SSC1 Error                                    | SSC1_EIC            | xx'014C <sub>H</sub>             | 53 <sub>H</sub> / 83 <sub>D</sub> |

| CAN0                                          | CAN_0IC             | xx'0150 <sub>H</sub>             | 54 <sub>H</sub> / 84 <sub>D</sub> |

| CAN1                                          | CAN_1IC             | xx'0154 <sub>H</sub>             | 55 <sub>H</sub> / 85 <sub>D</sub> |

| CAN2                                          | CAN_2IC             | xx'0158 <sub>H</sub>             | 56 <sub>H</sub> / 86 <sub>D</sub> |

| CAN3                                          | CAN_3IC             | xx'015C <sub>H</sub>             | 57 <sub>H</sub> / 87 <sub>D</sub> |

| CAN4                                          | CAN_4IC             | xx'0164 <sub>H</sub>             | 59 <sub>H</sub> / 89 <sub>D</sub> |

| CAN5                                          | CAN_5IC             | xx'0168 <sub>H</sub>             | 5A <sub>H</sub> / 90 <sub>D</sub> |

| CAN6                                          | CAN_6IC             | xx'016C <sub>H</sub>             | 5B <sub>H</sub> / 91 <sub>D</sub> |

| CAN7                                          | CAN_7IC             | xx'0170 <sub>H</sub>             | 5C <sub>H</sub> / 92 <sub>D</sub> |

| RTC                                           | RTC_IC              | xx'0174 <sub>H</sub>             | 5D <sub>H</sub> / 93 <sub>D</sub> |

| Unassigned node                               | _                   | xx'012C <sub>H</sub>             | 4B <sub>H</sub> / 75 <sub>D</sub> |

| Unassigned node                               | _                   | xx'00FC <sub>H</sub>             | 3F <sub>H</sub> / 63 <sub>D</sub> |

| Unassigned node                               | _                   | xx'0160 <sub>H</sub>             | 58 <sub>H</sub> / 88 <sub>D</sub> |

Register VECSEG defines the segment where the vector table is located to.

Bitfield VECSC in register CPUCON1 defines the distance between two adjacent vectors. This table represents the default setting, with a distance of 4 (two words) between two vectors.

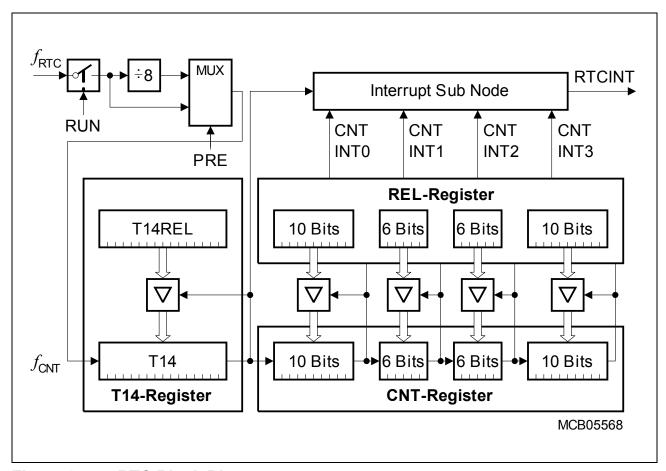

## 3.9 Real Time Clock

The Real Time Clock (RTC) module of the XC167 is directly clocked via a separate clock driver either with the on-chip auxiliary oscillator frequency ( $f_{\rm RTC}$  =  $f_{\rm OSCa}$ ) or with the prescaled on-chip main oscillator frequency ( $f_{\rm RTC}$  =  $f_{\rm OSCm}$ /32). It is therefore independent from the selected clock generation mode of the XC167.

The RTC basically consists of a chain of divider blocks:

- a selectable 8:1 divider (on off)

- the reloadable 16-bit timer T14

- the 32-bit RTC timer block (accessible via registers RTCH and RTCL), made of:

- a reloadable 10-bit timer

- a reloadable 6-bit timer

- a reloadable 6-bit timer

- a reloadable 10-bit timer

All timers count up. Each timer can generate an interrupt request. All requests are combined to a common node request.

Figure 9 RTC Block Diagram

Note: The registers associated with the RTC are not affected by a reset in order to maintain the correct system time even when intermediate resets are executed.

Data Sheet 42 V1.3, 2006-08

Table 7 Summary of the XC167's Parallel Ports

| I able I | Guillinary Or i                                | ille ACTOF 3 Farallel FOLLS                                                                                              |

|----------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Port     | Control                                        | Alternate Functions                                                                                                      |

| PORT0    | Pad drivers                                    | Address/Data lines or data lines <sup>1)</sup>                                                                           |

| PORT1    | Pad drivers                                    | Address lines <sup>2)</sup>                                                                                              |

|          |                                                | Capture inputs or compare outputs, Serial interface lines                                                                |

| Port 2   | Pad drivers,<br>Open drain,<br>Input threshold | Capture inputs or compare outputs, Timer control signal, Fast external interrupt inputs                                  |

| Port 3   | Pad drivers,<br>Open drain,<br>Input threshold | Timer control signals, serial interface lines, Optional bus control signal BHE/WRH, System clock output CLKOUT (or FOUT) |

| Port 4   | Pad drivers,                                   | Segment address lines <sup>3)</sup>                                                                                      |

|          | Open drain,<br>Input threshold                 | CAN interface lines <sup>4)</sup>                                                                                        |

| Port 5   | _                                              | Analog input channels to the A/D converter, Timer control signals                                                        |

| Port 6   | Open drain,<br>Input threshold                 | Capture inputs or compare outputs, Bus arbitration signals BREQ, HLDA, HOLD, Optional chip select signals                |

| Port 7   | Open drain,<br>Input threshold                 | Capture inputs or compare outputs, CAN interface lines <sup>4)</sup>                                                     |

| Port 9   | Pad drivers,                                   | Capture inputs or compare outputs                                                                                        |

|          | Open drain,<br>Input threshold                 | CAN interface lines <sup>4)</sup> , IIC bus interface lines <sup>4)</sup>                                                |

| Port 20  | Pad drivers,<br>Open drain                     | Bus control signals RD, WR/WRL, READY, ALE, External access enable pin EA, Reset indication output RSTOUT                |

<sup>1)</sup> For multiplexed bus cycles.

<sup>2)</sup> For demultiplexed bus cycles.

<sup>3)</sup> For more than 64 Kbytes of external resources.

<sup>4)</sup> Can be assigned by software.

## 3.18 Power Management

The XC167 provides several means to control the power it consumes either at a given time or averaged over a certain timespan. Three mechanisms can be used (partly in parallel):

- Power Saving Modes switch the XC167 into a special operating mode (control via instructions).

- Idle Mode stops the CPU while the peripherals can continue to operate. Sleep Mode and Power Down Mode stop all clock signals and all operation (RTC may

- optionally continue running). Sleep Mode can be terminated by external interrupt signals.

- Clock Generation Management controls the distribution and the frequency of internal and external clock signals. While the clock signals for currently inactive parts of logic are disabled automatically, the user can reduce the XC167's CPU clock frequency which drastically reduces the consumed power.

- External circuitry can be controlled via the programmable frequency output FOUT.

- **Peripheral Management** permits temporary disabling of peripheral modules (control via register SYSCON3). Each peripheral can separately be disabled/enabled.

The on-chip RTC supports intermittent operation of the XC167 by generating cyclic wake-up signals. This offers full performance to quickly react on action requests while the intermittent sleep phases greatly reduce the average power consumption of the system.

Data Sheet 52 V1.3, 2006-08

## 3.19 Instruction Set Summary

Table 8 lists the instructions of the XC167 in a condensed way.

The various addressing modes that can be used with a specific instruction, the operation of the instructions, parameters for conditional execution of instructions, and the opcodes for each instruction can be found in the "Instruction Set Manual".

This document also provides a detailed description of each instruction.

Table 8

Instruction Set Summary

| Mnemonic      | Description                                                                                       | Bytes |

|---------------|---------------------------------------------------------------------------------------------------|-------|

| ADD(B)        | Add word (byte) operands                                                                          | 2/4   |

| ADDC(B)       | Add word (byte) operands with Carry                                                               | 2/4   |

| SUB(B)        | Subtract word (byte) operands                                                                     | 2/4   |

| SUBC(B)       | Subtract word (byte) operands with Carry                                                          | 2/4   |

| MUL(U)        | (Un)Signed multiply direct GPR by direct GPR (16- × 16-bit)                                       | 2     |

| DIV(U)        | (Un)Signed divide register MDL by direct GPR (16-/16-bit)                                         | 2     |

| DIVL(U)       | (Un)Signed long divide reg. MD by direct GPR (32-/16-bit)                                         | 2     |

| CPL(B)        | Complement direct word (byte) GPR                                                                 | 2     |

| NEG(B)        | Negate direct word (byte) GPR                                                                     | 2     |

| AND(B)        | Bitwise AND, (word/byte operands)                                                                 | 2/4   |

| OR(B)         | Bitwise OR, (word/byte operands)                                                                  | 2/4   |

| XOR(B)        | Bitwise exclusive OR, (word/byte operands)                                                        | 2/4   |

| BCLR/BSET     | Clear/Set direct bit                                                                              | 2     |

| BMOV(N)       | Move (negated) direct bit to direct bit                                                           | 4     |

| BAND/BOR/BXOR | AND/OR/XOR direct bit with direct bit                                                             | 4     |

| BCMP          | Compare direct bit to direct bit                                                                  | 4     |

| BFLDH/BFLDL   | Bitwise modify masked high/low byte of bit-addressable direct word memory with immediate data     | 4     |

| CMP(B)        | Compare word (byte) operands                                                                      | 2/4   |

| CMPD1/2       | Compare word data to GPR and decrement GPR by 1/2                                                 | 2/4   |

| CMPI1/2       | Compare word data to GPR and increment GPR by 1/2                                                 | 2/4   |

| PRIOR         | Determine number of shift cycles to normalize direct word GPR and store result in direct word GPR | 2     |

| SHL/SHR       | Shift left/right direct word GPR                                                                  | 2     |

## 4 Electrical Parameters

#### 4.1 General Parameters

Table 9 Absolute Maximum Ratings

| Parameter                                                             | Symbol    | Limit Values |                        | Unit | Notes      |  |

|-----------------------------------------------------------------------|-----------|--------------|------------------------|------|------------|--|

|                                                                       |           | Min.         | Max.                   |      |            |  |

| Storage temperature                                                   | $T_{ST}$  | -65          | 150                    | °C   | 1)         |  |

| Junction temperature                                                  | $T_{J}$   | -40          | 150                    | °C   | under bias |  |

| Voltage on $V_{\rm DDI}$ pins with respect to ground ( $V_{\rm SS}$ ) | $V_{DDI}$ | -0.5         | 3.25                   | V    | _          |  |

| Voltage on $V_{\rm DDP}$ pins with respect to ground ( $V_{\rm SS}$ ) | $V_{DDP}$ | -0.5         | 6.2                    | V    | _          |  |

| Voltage on any pin with respect to ground ( $V_{\rm SS}$ )            | $V_{IN}$  | -0.5         | V <sub>DDP</sub> + 0.5 | V    | 2)         |  |

| Input current on any pin during overload condition                    | _         | -10          | 10                     | mA   | _          |  |

| Absolute sum of all input currents during overload condition          | _         | _            | 100                    | mA   | _          |  |

<sup>1)</sup> Moisture Sensitivity Level (MSL) 3, conforming to Jedec J-STD-020C for 260 °C for PG-TQFP-144-7, and 240 °C for P-TQFP-144-19.

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{\rm IN} > V_{\rm DDP}$  or  $V_{\rm IN} < V_{\rm SS}$ ) the voltage on  $V_{\rm DDP}$  pins with respect to ground ( $V_{\rm SS}$ ) must not exceed the values defined by the absolute maximum ratings.

<sup>2)</sup> Input pins XTAL1/XTAL3 belong to the core voltage domain. Therefore, input voltages must be within the range defined for  $V_{

m DDI}$ .

Table 12 Current Limits for Port Output Drivers

| Port Output Driver<br>Mode |        | Nominal Output Current $(I_{OLnom}, -I_{OHnom})$ |

|----------------------------|--------|--------------------------------------------------|

| Strong driver              | 10 mA  | 2.5 mA                                           |

| Medium driver              | 4.0 mA | 1.0 mA                                           |

| Weak driver                | 0.5 mA | 0.1 mA                                           |

<sup>1)</sup> An output current above  $|I_{\rm OXnom}|$  may be drawn from up to three pins at the same time. For any group of 16 neighboring port output pins the total output current in each direction ( $\Sigma I_{\rm OL}$  and  $\Sigma I_{\rm OH}$ ) must remain below 50 mA.

Table 13

Power Consumption XC167 (Operating Conditions apply)

| <u> </u>                                                                                                                                    | •              | •    |                                               | 11 37 |                                                                                                      |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|-----------------------------------------------|-------|------------------------------------------------------------------------------------------------------|--|

| Parameter                                                                                                                                   | Sym-           | Lim  | it Values                                     | Unit  | <b>Test Condition</b>                                                                                |  |

|                                                                                                                                             | bol            | Min. | Max.                                          |       |                                                                                                      |  |

| Power supply current (active) with all peripherals active                                                                                   | $I_{DDI}$      | _    | 15 + $2.6 \times f_{\text{CPU}}$              | mA    | $f_{\mathrm{CPU}}$ in [MHz] <sup>1)2)</sup>                                                          |  |

| Pad supply current                                                                                                                          | $I_{DDP}$      | _    | 5                                             | mA    | 3)                                                                                                   |  |

| Idle mode supply current with all peripherals active                                                                                        | $I_{IDX}$      | _    | 15 +<br>1.2 × $f_{\text{CPU}}$                | mA    | $f_{\rm CPU}$ in [MHz] <sup>2)</sup>                                                                 |  |

| Sleep and Power down mode supply current caused by leakage <sup>4)</sup>                                                                    | $I_{PDL}^{5)}$ | _    | 128,000<br>× e <sup>-α</sup>                  | mA    | $V_{\rm DDI} = V_{\rm DDImax}^{6)}$<br>$T_{\rm J}$ in [°C]<br>$\alpha =$ 4670 / (273 + $T_{\rm J}$ ) |  |

| Sleep and Power down mode supply current caused by leakage and the RTC running, clocked by the main oscillator <sup>4)</sup>                | $I_{PDM}^{7)}$ | -    | $0.6 + 0.02 \times f_{\rm OSC} + I_{\rm PDL}$ | mA    | $V_{\rm DDI}$ = $V_{\rm DDImax}$ $f_{\rm OSC}$ in [MHz]                                              |  |

| Sleep and Power down mode supply current caused by leakage and the RTC running, clocked by the auxiliary oscillator at 32 kHz <sup>4)</sup> | $I_{PDA}$      | _    | 0.1 + I <sub>PDL</sub>                        | mA    | $V_{\rm DDI} = V_{\rm DDImax}$                                                                       |  |

<sup>1)</sup> During Flash programming or erase operations the supply current is increased by max. 5 mA.

Data Sheet 61 V1.3, 2006-08

<sup>2)</sup> The supply current is a function of the operating frequency. This dependency is illustrated in **Figure 11**. These parameters are tested at  $V_{\rm DDImax}$  and maximum CPU clock frequency with all outputs disconnected and all inputs at  $V_{\rm IL}$  or  $V_{\rm IH}$ .

<sup>3)</sup> The pad supply voltage pins ( $V_{\rm DDP}$ ) mainly provides the current consumed by the pin output drivers. A small amount of current is consumed even though no outputs are driven, because the drivers' input stages are switched and also the Flash module draws some power from the  $V_{\rm DDP}$  supply.

- 4) The total supply current in Sleep and Power down mode is the sum of the temperature dependent leakage current and the frequency dependent current for RTC and main oscillator or auxiliary oscillator (if active).

- 5) This parameter is determined mainly by the transistor leakage currents. This current heavily depends on the junction temperature (see **Figure 13**). The junction temperature  $T_J$  is the same as the ambient temperature  $T_A$  if no current flows through the port output drivers. Otherwise, the resulting temperature difference must be taken into account.

- 6) All inputs (including pins configured as inputs) at 0 V to 0.1 V or at  $V_{\text{DDP}}$  0.1 V to  $V_{\text{DDP}}$ , all outputs (including pins configured as outputs) disconnected. This parameter is tested at 25 °C and is valid for  $T_{\text{J}} \ge$  25 °C.

- 7) This parameter is determined mainly by the current consumed by the oscillator switched to low gain mode (see Figure 12). This current, however, is influenced by the external oscillator circuitry (crystal, capacitors). The given values refer to a typical circuitry and may change in case of a not optimized external oscillator circuitry.

Data Sheet 62 V1.3, 2006-08

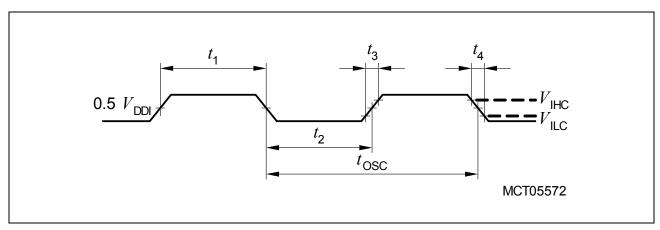

#### 4.4.3 External Clock Drive XTAL1

Table 19 External Clock Drive Characteristics (Operating Conditions apply)

| Parameter               | Symbol    |    | Limit Values |                   | Unit |

|-------------------------|-----------|----|--------------|-------------------|------|

|                         |           |    | Min.         | Max.              |      |

| Oscillator period       | $t_{OSC}$ | SR | 25           | 250 <sup>1)</sup> | ns   |

| High time <sup>2)</sup> | $t_1$     | SR | 6            | _                 | ns   |

| Low time <sup>2)</sup>  | $t_2$     | SR | 6            | _                 | ns   |

| Rise time <sup>2)</sup> | $t_3$     | SR | _            | 8                 | ns   |

| Fall time <sup>2)</sup> | $t_4$     | SR | _            | 8                 | ns   |

<sup>1)</sup> The maximum limit is only relevant for PLL operation to ensure the minimum input frequency for the PLL.

<sup>2)</sup> The clock input signal must reach the defined levels  $V_{\rm ILC}$  and  $V_{\rm IHC}$ .

Figure 17 External Clock Drive XTAL1

Note: If the on-chip oscillator is used together with a crystal or a ceramic resonator, the oscillator frequency is limited to a range of 4 MHz to 16 MHz.

It is strongly recommended to measure the oscillation allowance (negative resistance) in the final target system (layout) to determine the optimum parameters for the oscillator operation. Please refer to the limits specified by the crystal supplier.

When driven by an external clock signal it will accept the specified frequency range. Operation at lower input frequencies is possible but is verified by design only (not subject to production test).

Data Sheet 73 V1.3, 2006-08

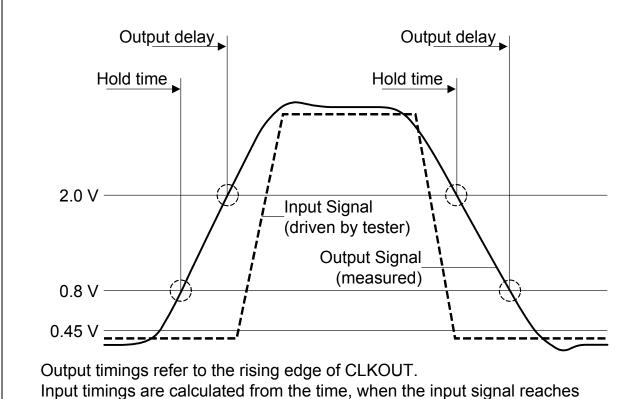

#### **Testing Waveforms** 4.4.4

$V_{\rm IH}$  or  $V_{\rm II}$ , respectively.

MCD05556

Figure 18 **Input Output Waveforms**

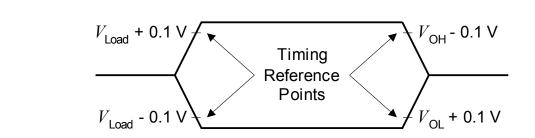

For timing purposes a port pin is no longer floating when a 100 mV change from load voltage occurs, but begins to float when a 100 mV change from the loaded  $V_{\rm OH}/V_{\rm OI}$  level occurs ( $I_{\rm OH}/I_{\rm OI}$  = 20 mA).

MCA05565

**Float Waveforms** Figure 19

### **Variable Memory Cycles**

External bus cycles of the XC167 are executed in five subsequent cycle phases (AB, C, D, E, F). The duration of each cycle phase is programmable (via the TCONCSx registers) to adapt the external bus cycles to the respective external module (memory, peripheral, etc.).

The duration of the access phase can optionally be controlled by the external module via the READY handshake input.

This table provides a summary of the phases and the respective choices for their duration.

**Table 21** Programmable Bus Cycle Phases (see timing diagrams)

| Bus Cycle Phase                                                                                                                | Parameter | Valid Values | Unit |

|--------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|------|

| Address setup phase, the standard duration of this phase (1 2 TCP) can be extended by 0 3 TCP if the address window is changed | $tp_{AB}$ | 1 2 (5)      | TCP  |

| Command delay phase                                                                                                            | $tp_{C}$  | 0 3          | TCP  |

| Write Data setup/MUX Tristate phase                                                                                            | $tp_{D}$  | 0 1          | TCP  |

| Access phase                                                                                                                   | $tp_{E}$  | 1 32         | TCP  |

| Address/Write Data hold phase                                                                                                  | $tp_{F}$  | 0 3          | TCP  |

Note: The bandwidth of a parameter (minimum and maximum value) covers the whole operating range (temperature, voltage) as well as process variations. Within a given device, however, this bandwidth is smaller than the specified range. This is also due to interdependencies between certain parameters. Some of these interdependencies are described in additional notes (see standard timing).

Data Sheet 76 V1.3, 2006-08

## **Bus Cycle Control via READY Input**

The duration of an external bus cycle can be controlled by the external circuitry via the READY input signal. The polarity of this input signal can be selected.

**Synchronous** READY permits the shortest possible bus cycle but requires the input signal to be synchronous to the reference signal CLKOUT.

**Asynchronous** READY puts no timing constraints on the input signal but incurs one waitstate minimum due to the additional synchronization stage. The minimum duration of an asynchronous READY signal to be safely synchronized must be one CLKOUT period plus the input setup time.

An active READY signal can be deactivated in response to the trailing (rising) edge of the corresponding command (RD or WR).

If the next following bus cycle is READY-controlled, an active READY signal must be disabled before the first valid sample point for the next bus cycle. This sample point depends on the programmed phases of the next following cycle.

Data Sheet 80 V1.3, 2006-08

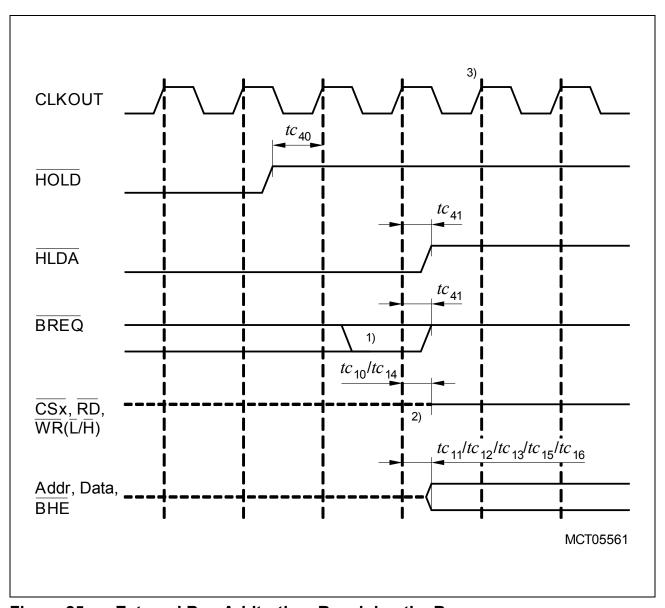

Figure 25 External Bus Arbitration, Regaining the Bus

#### **Notes**

- 1. This is the last chance for BREQ to trigger the indicated regain-sequence.

Even if BREQ is activated earlier, the regain-sequence is initiated by HOLD going high. Please note that HOLD may also be deactivated without the XC167 requesting the bus.

- 2. The control outputs will be resistive high (pull-up) before being driven inactive (ALE will be low).

- 3. The next XC167 driven bus cycle may start here.

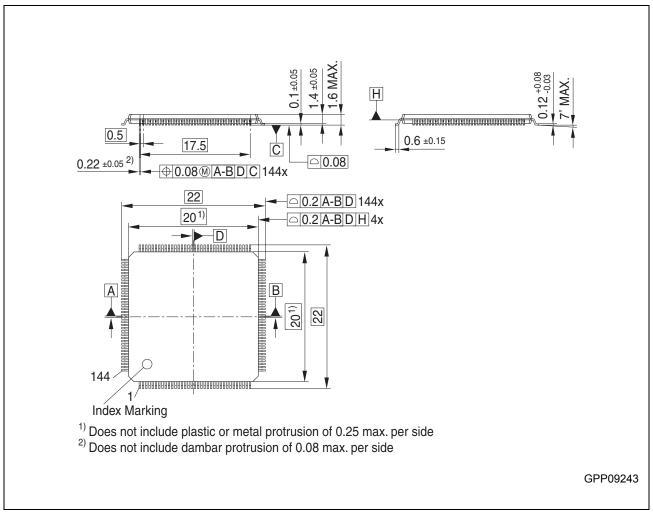

### Package and Reliability

Figure 27 P-TQFP-144-19 (Plastic Thin Quad Flat Package)

## Package and Reliability

## **5.2** Flash Memory Parameters

The data retention time of the XC167's Flash memory (i.e. the time after which stored data can still be retrieved) depends on the number of times the Flash memory has been erased and programmed.

**Table 25** Flash Parameters (XC167, 128 Kbytes)

| Parameter             | Symbol    | Limit Values         |      | Unit   | Notes                                |

|-----------------------|-----------|----------------------|------|--------|--------------------------------------|

|                       |           | Min.                 | Max. |        |                                      |

| Data retention time   | $t_{RET}$ | 15                   | _    | years  | 10 <sup>3</sup> erase/program cycles |

| Flash Erase Endurance | $N_{ER}$  | 20 × 10 <sup>3</sup> | _    | cycles | Data retention time 5 years          |

Data Sheet 87 V1.3, 2006-08