## Intel - 10M50DAF484C8G Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Active                                                    |

| Number of LABs/CLBs            | 3125                                                      |

| Number of Logic Elements/Cells | 50000                                                     |

| Total RAM Bits                 | 1677312                                                   |

| Number of I/O                  | 360                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.15V ~ 1.25V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 484-BGA                                                   |

| Supplier Device Package        | 484-FBGA (23x23)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/10m50daf484c8g |

|                                |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Operating Conditions**

Intel MAX 10 devices are rated according to a set of defined parameters. To maintain the highest possible performance and reliability of the Intel MAX 10 devices, you must consider the operating requirements described in this section.

## **Absolute Maximum Ratings**

This section defines the maximum operating conditions for Intel MAX 10 devices. The values are based on experiments conducted with the devices and theoretical modeling of breakdown and damage mechanisms. The functional operation of the device is not implied for these conditions.

**Caution:** Conditions outside the range listed in the absolute maximum ratings tables may cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse effects on the device.

### **Single Supply Devices Absolute Maximum Ratings**

#### Table 2. Absolute Maximum Ratings for Intel MAX 10 Single Supply Devices

| Symbol              | Parameter                                                                                                     | Min  | Мах | Unit |

|---------------------|---------------------------------------------------------------------------------------------------------------|------|-----|------|

| V <sub>CC_ONE</sub> | Supply voltage for core and periphery through on-die voltage regulator                                        | -0.5 | 3.9 | V    |

| V <sub>CCIO</sub>   | Supply voltage for input and output buffers                                                                   | -0.5 | 3.9 | V    |

| V <sub>CCA</sub>    | Supply voltage for phase-locked loop (PLL) regulator and analog-to-<br>digital converter (ADC) block (analog) | -0.5 | 3.9 | V    |

#### **Dual Supply Devices Absolute Maximum Ratings**

#### Table 3. Absolute Maximum Ratings for Intel MAX 10 Dual Supply Devices

| Symbol            | Parameter                                   | Min  | Мах  | Unit      |

|-------------------|---------------------------------------------|------|------|-----------|

| V <sub>CC</sub>   | Supply voltage for core and periphery       | -0.5 | 1.63 | V         |

| V <sub>CCIO</sub> | Supply voltage for input and output buffers | -0.5 | 3.9  | V         |

| V <sub>CCA</sub>  | Supply voltage for PLL regulator (analog)   | -0.5 | 3.41 | V         |

|                   | •                                           |      |      | continued |

## Table 11. ADC\_VREF Pin Leakage Current for Intel MAX 10 Devices

| Symbol                | Parameter                    | Condition          | Min | Мах | Unit |

|-----------------------|------------------------------|--------------------|-----|-----|------|

| I <sub>adc_vref</sub> | ADC_VREF pin leakage current | Single supply mode | _   | 10  | μA   |

|                       |                              | Dual supply mode   | —   | 20  | μA   |

### **Bus Hold Parameters**

Bus hold retains the last valid logic state after the source driving it either enters the high impedance state or is removed. Each I/O pin has an option to enable bus hold in user mode. Bus hold is always disabled in configuration mode.

## Table 12. Bus Hold Parameters for Intel MAX 10 Devices

| Parameter                         | Condition                                      | V <sub>CCI0</sub> (V) |      |       |       |      |        |     |      |     | Unit |     |      |    |

|-----------------------------------|------------------------------------------------|-----------------------|------|-------|-------|------|--------|-----|------|-----|------|-----|------|----|

|                                   |                                                | 1.                    | 1.2  |       | 1.5   |      | 1.8 2. |     | 2.5  |     | 3.0  |     | 3.3  |    |

|                                   |                                                | Min                   | Мах  | Min   | Мах   | Min  | Мах    | Min | Max  | Min | Мах  | Min | Мах  | ]  |

| Bus-hold low, sustaining current  | V <sub>IN</sub> > V <sub>IL</sub><br>(maximum) | 8                     | _    | 12    | _     | 30   | _      | 50  | -    | 70  | -    | 70  | -    | μA |

| Bus-hold high, sustaining current | V <sub>IN</sub> < V <sub>IH</sub><br>(minimum) | -8                    | _    | -12   | _     | -30  | _      | -50 | -    | -70 | _    | -70 | -    | μA |

| Bus-hold low, overdrive current   | $0 V < V_{IN} < V_{CCIO}$                      | _                     | 125  | -     | 175   | —    | 200    | _   | 300  | —   | 500  | —   | 500  | μA |

| Bus-hold high, overdrive current  | 0 V < V <sub>IN</sub> <<br>V <sub>CCIO</sub>   | _                     | -125 | -     | -175  | _    | -200   | _   | -300 | _   | -500 | _   | -500 | μA |

| Bus-hold trip point               | _                                              | 0.3                   | 0.9  | 0.375 | 1.125 | 0.68 | 1.07   | 0.7 | 1.7  | 0.8 | 2    | 0.8 | 2    | V  |

## **Series OCT without Calibration Specifications**

#### Table 13. Series OCT without Calibration Specifications for Intel MAX 10 Devices

This table shows the variation of on-chip termination (OCT) without calibration across process, voltage, and temperature (PVT).

| Description                    | V <sub>CCIO</sub> (V) | Resistance              | Tolerance | Unit |

|--------------------------------|-----------------------|-------------------------|-----------|------|

|                                |                       | -C7, -I6, -I7, -A6, -A7 | -C8       |      |

| Series OCT without calibration | 3.00                  | ±35                     | ±30       | %    |

|                                | 2.50                  | ±35                     | ±30       | %    |

|                                | 1.80                  | ±40                     | ±35       | %    |

|                                | 1.50                  | ±40                     | ±40       | %    |

|                                | 1.35                  | ±40                     | ±50       | %    |

|                                | 1.20                  | ±45                     | ±60       | %    |

## Series OCT with Calibration at Device Power-Up Specifications

#### Table 14. Series OCT with Calibration at Device Power-Up Specifications for Intel MAX 10 Devices

OCT calibration is automatically performed at device power-up for OCT enabled I/Os.

| Description                                    | V <sub>CCIO</sub> (V) | Calibration Accuracy | Unit |

|------------------------------------------------|-----------------------|----------------------|------|

| Series OCT with calibration at device power-up | 3.00                  | ±12                  | %    |

|                                                | 2.50                  | ±12                  | %    |

|                                                | 1.80                  | ±12                  | %    |

|                                                | 1.50                  | ±12                  | %    |

|                                                | 1.35                  | ±12                  | %    |

|                                                | 1.20                  | ±12                  | %    |

### **OCT Variation after Calibration at Device Power-Up**

The OCT resistance may vary with the variation of temperature and voltage after calibration at device power-up.

Use the following table and equation to determine the final OCT resistance considering the variations after calibration at device power-up.

- Subscript x refers to both V and T.

- $\Delta R_V$  is variation of resistance with voltage.

- $\Delta R_T$  is variation of resistance with temperature.

- dR/dT is the change percentage of resistance with temperature after calibration at device power-up.

- dR/dV is the change percentage of resistance with voltage after calibration at device power-up.

- V<sub>1</sub> is the initial voltage.

- V<sub>2</sub> is final voltage.

The following figure shows the example to calculate the change of 50  $\Omega$  I/O impedance from 25°C at 3.0 V to 85°C at 3.15 V.

## Figure 2. Example for OCT Resistance Calculation after Calibration at Device Power-Up

$\Delta R_V = (3.15 - 3) \times 1000 \times -0.027 = -4.05$  $\Delta R_T = (85 - 25) \times 0.25 = 15$

Because  $\Delta R_V$  is negative,

$MF_V = 1/(4.05/100 + 1) = 0.961$

Because  $\Delta R_T$  is positive,

$MF_T = 15/100 + 1 = 1.15$  $MF = 0.961 \times 1.15 = 1.105$

$R_{final} = 50 \times 1.105 = 55.25\Omega$

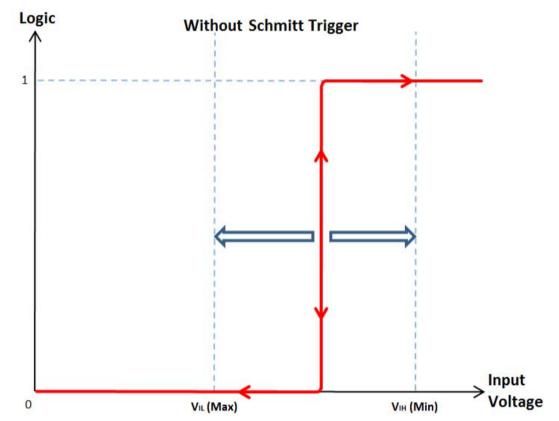

## Figure 3. LVTTL/LVCMOS Input Standard Voltage Diagram

| Symbol                                        | Parameter                                                        | Condition                                                                                                    | Min | Тур | Max   | Unit      |

|-----------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|-------|-----------|

| f <sub>VCO</sub> <sup>(29)</sup>              | PLL internal voltage-controlled oscillator (VCO) operating range | -                                                                                                            | 600 | _   | 1300  | MHz       |

| f <sub>INDUTY</sub>                           | Input clock duty cycle                                           | -                                                                                                            | 40  | _   | 60    | %         |

| t <sub>INJITTER_CCJ</sub> (30)                | Input clock cycle-to-cycle jitter                                | $F_{INPFD} \ge 100 \text{ MHz}$                                                                              | _   | _   | 0.15  | UI        |

|                                               |                                                                  | $F_{INPFD} < 100 \text{ MHz}$                                                                                | _   | _   | ±750  | ps        |

| f <sub>OUT_EXT</sub> <sup>(28)</sup>          | PLL output frequency for external clock output                   | -                                                                                                            | _   | -   | 472.5 | MHz       |

| f <sub>OUT</sub>                              | PLL output frequency to global clock                             | -6 speed grade                                                                                               | _   | _   | 472.5 | MHz       |

|                                               |                                                                  | -7 speed grade                                                                                               | _   | _   | 450   | MHz       |

|                                               |                                                                  | -8 speed grade                                                                                               | _   | -   | 402.5 | MHz       |

| toutduty                                      | Duty cycle for external clock output                             | Duty cycle set to 50%                                                                                        | 45  | 50  | 55    | %         |

| t <sub>LOCK</sub>                             | Time required to lock from end of device configuration           | -                                                                                                            | _   | _   | 1     | ms        |

| t <sub>DLOCK</sub>                            | Time required to lock dynamically                                | After switchover, reconfiguring<br>any non-post-scale counters or<br>delays, or when areset is<br>deasserted | _   | _   | 1     | ms        |

| t <sub>OUTJITTER_PERIOD_IO</sub>              | Regular I/O period jitter                                        | $F_{OUT} \ge 100 \text{ MHz}$                                                                                | _   | -   | 650   | ps        |

| (31)                                          |                                                                  | F <sub>OUT</sub> < 100 MHz                                                                                   | _   | _   | 75    | mUI       |

| t <sub>OUTJITTER_CCJ_IO</sub> <sup>(31)</sup> | Regular I/O cycle-to-cycle jitter                                | F <sub>OUT</sub> ≥ 100 MHz                                                                                   | _   | _   | 650   | ps        |

|                                               |                                                                  | F <sub>OUT</sub> < 100 MHz                                                                                   | _   | _   | 75    | mUI       |

|                                               |                                                                  |                                                                                                              |     | 1   |       | continued |

<sup>&</sup>lt;sup>(29)</sup> The VCO frequency reported by the Intel Quartus Prime software in the PLL summary section of the compilation report takes into consideration the VCO post-scale counter  $\kappa$  value. Therefore, if the counter  $\kappa$  has a value of 2, the frequency reported can be lower than the f<sub>VCO</sub> specification.

<sup>(30)</sup> A high input jitter directly affects the PLL output jitter. To have low PLL output clock jitter, you must provide a clean clock source, which is less than 200 ps.

<sup>(31)</sup> Peak-to-peak jitter with a probability level of 10<sup>-12</sup> (14 sigma, 99.9999999999974404% confidence level). The output jitter specification applies to the intrinsic jitter of the PLL, when an input jitter of 30 ps is applied.

## **Internal Oscillator Specifications**

## Table 32. Internal Oscillator Frequencies for Intel MAX 10 Devices

You can access to the internal oscillator frequencies in this table. The duty cycle of internal oscillator is approximately 45%–55%.

| Device |         | Frequency |         | Unit |

|--------|---------|-----------|---------|------|

|        | Minimum | Typical   | Maximum |      |

| 10M02  | 55      | 82        | 116     | MHz  |

| 10M04  |         |           |         |      |

| 10M08  |         |           |         |      |

| 10M16  |         |           |         |      |

| 10M25  |         |           |         |      |

| 10M40  | 35      | 52        | 77      | MHz  |

| 10M50  |         |           |         |      |

## **UFM Performance Specifications**

## Table 33. UFM Performance Specifications for Intel MAX 10 Devices

| Block | Mode                          | Interface              | Device                                      | Frequ   | iency   | Unit |

|-------|-------------------------------|------------------------|---------------------------------------------|---------|---------|------|

|       |                               |                        |                                             | Minimum | Maximum |      |

| UFM   | Avalon <sup>®</sup> -MM slave | Parallel (33)          | 10M02 <sup>(34)</sup>                       | 3.43    | 7.25    | MHz  |

|       |                               |                        | 10M04, 10M08, 10M16, 10M25, 10M40,<br>10M50 | 5       | 116     | MHz  |

|       |                               | Serial <sup>(34)</sup> | 10M02, 10M04, 10M08, 10M16, 10M25           | 3.43    | 7.25    | MHz  |

|       |                               |                        | 10M40, 10M50                                | 2.18    | 4.81    | MHz  |

<sup>&</sup>lt;sup>(33)</sup> Clock source is derived from user, except for 10M02 device.

$<sup>^{(34)}</sup>$  Clock source is derived from 1/16 of the frequency of the internal oscillator.

|                      | Parameter                      | Symbol         | Condition                                           | Min                 | Тур | Мах | Unit  |

|----------------------|--------------------------------|----------------|-----------------------------------------------------|---------------------|-----|-----|-------|

|                      | Integral non linearity         | INL            | -                                                   | -2                  | -   | 2   | LSB   |

| AC Accuracy          | Total harmonic distortion      | THD            | $F_{IN} = 50 \text{ kHz}, F_S = 1 \text{ MHz}, PLL$ | -65 <sup>(37)</sup> | -   | -   | dB    |

|                      | Signal-to-noise ratio          | SNR            | $F_{IN} = 50 \text{ kHz}, F_S = 1 \text{ MHz}, PLL$ | 54 <sup>(38)</sup>  | -   | -   | dB    |

|                      | Signal-to-noise and distortion | SINAD          | $F_{IN} = 50 \text{ kHz}, F_S = 1 \text{ MHz}, PLL$ | 53 <sup>(39)</sup>  | _   | -   | dB    |

| On-Chip Temperature  | Temperature sampling rate      | T <sub>S</sub> | -                                                   | _                   | -   | 50  | kSPS  |

| Sensor               | Absolute accuracy              | -              | -40 to 125°C,<br>with 64 samples averaging<br>(40)  | _                   | _   | ±10 | °C    |

| Conversion Rate (41) | Conversion time                | -              | Single measurement                                  | _                   | -   | 1   | Cycle |

|                      |                                |                | Continuous measurement                              | _                   | -   | 1   | Cycle |

|                      |                                |                | Temperature measurement                             | _                   | _   | 1   | Cycle |

## **Related Information**

SPICE Models for Intel FPGAs

<sup>(41)</sup> For more detailed description, refer to the Timing section in the *Intel MAX 10 Analog-to-Digital Converter User Guide*.

$<sup>^{(37)}</sup>$  THD with prescalar enabled is 6dB less than the specification.

$<sup>^{(38)}</sup>$  SNR with prescalar enabled is 6dB less than the specification.

<sup>&</sup>lt;sup>(39)</sup> SINAD with prescalar enabled is 6dB less than the specification.

<sup>(40)</sup> For the Intel Quartus Prime software version 15.0 and later, Modular ADC Core Intel FPGA IP and Modular Dual ADC Core Intel FPGA IP cores handle the 64 samples averaging. For the Intel Quartus Prime software versions prior to 14.1, you need to implement your own averaging calculation.

## True PPDS and Emulated PPDS\_E\_3R Transmitter Timing Specifications

## Table 36. True PPDS and Emulated PPDS\_E\_3R Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices

True PPDS transmitter is only supported at bottom I/O banks. Emulated PPDS transmitter is supported at the output pin of all I/O banks.

| Symbol                              | Parameter                                    | Mode | -16, | -A6, -C7 | , -17 |     | -A7 |     |     | - <b>C8</b> |     | Unit    |

|-------------------------------------|----------------------------------------------|------|------|----------|-------|-----|-----|-----|-----|-------------|-----|---------|

|                                     |                                              |      | Min  | Тур      | Max   | Min | Тур | Max | Min | Тур         | Max | ]       |

| f <sub>HSCLK</sub>                  | Input clock frequency                        | ×10  | 5    | -        | 155   | 5   | _   | 155 | 5   | -           | 155 | MHz     |

| (high-speed 1/O<br>performance pin) | (high-speed I/O<br>performance pin)          | ×8   | 5    | -        | 155   | 5   | _   | 155 | 5   | _           | 155 | MHz     |

|                                     |                                              | ×7   | 5    | -        | 155   | 5   | -   | 155 | 5   | -           | 155 | MHz     |

|                                     |                                              | ×4   | 5    | -        | 155   | 5   | -   | 155 | 5   | -           | 155 | MHz     |

|                                     |                                              | ×2   | 5    | -        | 155   | 5   | -   | 155 | 5   | -           | 155 | MHz     |

|                                     |                                              | ×1   | 5    | -        | 310   | 5   | -   | 310 | 5   | -           | 310 | MHz     |

|                                     | Data rate (high-speed                        | ×10  | 100  | -        | 310   | 100 | -   | 310 | 100 | -           | 310 | Mbps    |

|                                     | I/O performance pin)                         | ×8   | 80   | -        | 310   | 80  | -   | 310 | 80  | -           | 310 | Mbps    |

|                                     |                                              | ×7   | 70   | -        | 310   | 70  | -   | 310 | 70  | -           | 310 | Mbps    |

|                                     |                                              | ×4   | 40   | -        | 310   | 40  | -   | 310 | 40  | -           | 310 | Mbps    |

|                                     |                                              | ×2   | 20   | -        | 310   | 20  | -   | 310 | 20  | -           | 310 | Mbps    |

|                                     |                                              | ×1   | 10   | _        | 310   | 10  | _   | 310 | 10  | _           | 310 | Mbps    |

| f <sub>HSCLK</sub>                  | Input clock frequency<br>(low-speed I/O      | ×10  | 5    | -        | 150   | 5   | _   | 150 | 5   | -           | 150 | MHz     |

|                                     | performance pin)                             | ×8   | 5    | -        | 150   | 5   | -   | 150 | 5   | -           | 150 | MHz     |

|                                     |                                              | ×7   | 5    | _        | 150   | 5   | _   | 150 | 5   | -           | 150 | MHz     |

|                                     |                                              | ×4   | 5    | _        | 150   | 5   | _   | 150 | 5   | _           | 150 | MHz     |

|                                     |                                              | ×2   | 5    | -        | 150   | 5   | _   | 150 | 5   | -           | 150 | MHz     |

|                                     |                                              | ×1   | 5    | _        | 300   | 5   | _   | 300 | 5   | _           | 300 | MHz     |

| HSIODR                              | Data rate (low-speed<br>I/O performance pin) | ×10  | 100  | _        | 300   | 100 | _   | 300 | 100 | _           | 300 | Mbps    |

|                                     |                                              | ×8   | 80   | _        | 300   | 80  | _   | 300 | 80  | _           | 300 | Mbps    |

|                                     |                                              | ×7   | 70   | _        | 300   | 70  | _   | 300 | 70  | -           | 300 | Mbps    |

|                                     |                                              |      |      |          |       |     |     |     |     |             | cor | ntinued |

#### Intel<sup>®</sup> MAX<sup>®</sup> 10 FPGA Device Datasheet

| Symbol                                | Parameter                                                                                                                             | Mode                                  | -16, | -A6, -C7, | -17 |     | -A7 |     |     | <b>-C8</b> |     | Unit |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|-----------|-----|-----|-----|-----|-----|------------|-----|------|

|                                       |                                                                                                                                       |                                       | Min  | Тур       | Мах | Min | Тур | Мах | Min | Тур        | Мах |      |

|                                       |                                                                                                                                       | ×4                                    | 40   | -         | 170 | 40  | -   | 170 | 40  | -          | 170 | Mbps |

|                                       |                                                                                                                                       | ×2                                    | 20   | -         | 170 | 20  | -   | 170 | 20  | -          | 170 | Mbps |

|                                       |                                                                                                                                       | ×1                                    | 10   | -         | 170 | 10  | _   | 170 | 10  | -          | 170 | Mbps |

| t <sub>DUTY</sub>                     | Duty cycle on<br>transmitter output<br>clock                                                                                          | -                                     | 45   | -         | 55  | 45  | -   | 55  | 45  | -          | 55  | %    |

| TCCS <sup>(59)</sup>                  | Transmitter channel-<br>to-channel skew                                                                                               | _                                     | _    | -         | 300 | _   | -   | 300 | -   | -          | 300 | ps   |

| t <sub>x Jitter</sub> <sup>(60)</sup> | Output jitter (high-<br>speed I/O<br>performance pin)                                                                                 | -                                     | _    | -         | 425 | _   | -   | 425 | _   | -          | 425 | ps   |

|                                       | Output jitter (low-<br>speed I/O<br>performance pin)                                                                                  | -                                     | -    | -         | 470 | -   | -   | 470 | -   | -          | 470 | ps   |

| t <sub>RISE</sub>                     | Rise time                                                                                                                             | 20 – 80%, C <sub>LOAD</sub><br>= 5 pF | _    | 500       | -   | _   | 500 | _   | -   | 500        | _   | ps   |

| t <sub>FALL</sub>                     | Fall time                                                                                                                             | 20 – 80%, C <sub>LOAD</sub><br>= 5 pF | _    | 500       | -   | _   | 500 | -   | -   | 500        | _   | ps   |

| t <sub>lock</sub>                     | Time required for the<br>PLL to lock, after<br>CONF_DONE signal<br>goes high, indicating<br>the completion of<br>device configuration | _                                     | _    | _         | 1   | _   | _   | 1   | _   | _          | 1   | ms   |

$<sup>^{(59)}</sup>$  TCCS specifications apply to I/O banks from the same side only.

$<sup>^{\</sup>rm (60)}$  TX jitter is the jitter induced from core noise and I/O switching noise.

#### Intel<sup>®</sup> MAX<sup>®</sup> 10 FPGA Device Datasheet

M10-DATASHEET | 2018.06.29

| Symbol                                | Parameter                                                                                                                             | Mode                                  | -16, | -A6, -C7, | -17 |     | -A7 |     |     | - <b>C8</b> |     | Unit |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|-----------|-----|-----|-----|-----|-----|-------------|-----|------|

|                                       |                                                                                                                                       |                                       | Min  | Тур       | Max | Min | Тур | Max | Min | Тур         | Max | Ì    |

|                                       |                                                                                                                                       | ×7                                    | 70   | _         | 300 | 70  | -   | 300 | 70  | -           | 300 | Mbps |

|                                       |                                                                                                                                       | ×4                                    | 40   | _         | 300 | 40  | -   | 300 | 40  | -           | 300 | Mbps |

|                                       |                                                                                                                                       | ×2                                    | 20   | —         | 300 | 20  | —   | 300 | 20  | -           | 300 | Mbps |

|                                       |                                                                                                                                       | ×1                                    | 10   | _         | 300 | 10  | -   | 300 | 10  | -           | 300 | Mbps |

| t <sub>DUTY</sub>                     | Duty cycle on<br>transmitter output<br>clock                                                                                          | _                                     | 45   | _         | 55  | 45  | _   | 55  | 45  | _           | 55  | %    |

| TCCS <sup>(61)</sup>                  | Transmitter channel-<br>to-channel skew                                                                                               | _                                     | _    | _         | 300 | -   | _   | 300 | -   | -           | 300 | ps   |

| t <sub>x Jitter</sub> <sup>(62)</sup> | Output jitter (high-<br>speed I/O<br>performance pin)                                                                                 | _                                     | _    | _         | 425 | _   | _   | 425 | -   | _           | 425 | ps   |

|                                       | Output jitter (low-<br>speed I/O<br>performance pin)                                                                                  | -                                     | _    | -         | 470 | -   | -   | 470 | -   | -           | 470 | ps   |

| t <sub>RISE</sub>                     | Rise time                                                                                                                             | 20 - 80%, C <sub>LOAD</sub><br>= 5 pF | _    | 500       | -   | -   | 500 | -   | -   | 500         | _   | ps   |

| t <sub>FALL</sub>                     | Fall time                                                                                                                             | 20 - 80%, C <sub>LOAD</sub><br>= 5 pF | _    | 500       | -   | -   | 500 | -   | -   | 500         | _   | ps   |

| t <sub>lock</sub>                     | Time required for the<br>PLL to lock, after<br>CONF_DONE signal<br>goes high, indicating<br>the completion of<br>device configuration | _                                     | _    | _         | 1   | _   | _   | 1   | _   | _           | 1   | ms   |

$<sup>^{\</sup>rm (61)}$  TCCS specifications apply to I/O banks from the same side only.

$<sup>^{\</sup>rm (62)}$  TX jitter is the jitter induced from core noise and I/O switching noise.

| Symbol                     | Parameter                                                                                                                             | Mode                                  |     | -C7, -I7 |       |     | -A7 |       |     | -C8 |       | Unit |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----|----------|-------|-----|-----|-------|-----|-----|-------|------|

|                            |                                                                                                                                       |                                       | Min | Тур      | Max   | Min | Тур | Max   | Min | Тур | Max   |      |

|                            |                                                                                                                                       | ×8                                    | 80  | -        | 200   | 80  | -   | 200   | 80  | -   | 200   | Mbps |

|                            |                                                                                                                                       | ×7                                    | 70  | -        | 200   | 70  | -   | 200   | 70  | -   | 200   | Mbps |

|                            |                                                                                                                                       | ×4                                    | 40  | -        | 200   | 40  | _   | 200   | 40  | -   | 200   | Mbps |

|                            |                                                                                                                                       | ×2                                    | 20  | -        | 200   | 20  | -   | 200   | 20  | -   | 200   | Mbps |

|                            |                                                                                                                                       | ×1                                    | 10  | -        | 200   | 10  | _   | 200   | 10  | -   | 200   | Mbps |

| t <sub>duty</sub>          | Duty cycle on<br>transmitter output<br>clock                                                                                          | _                                     | 45  | -        | 55    | 45  | -   | 55    | 45  | -   | 55    | %    |

| TCCS <sup>(67)</sup>       | Transmitter channel-<br>to-channel skew                                                                                               | _                                     | _   | -        | 300   | _   | -   | 300   | _   | -   | 300   | ps   |

| t <sub>x Jitter</sub> (68) | Output jitter                                                                                                                         | _                                     | _   | -        | 1,000 | _   | -   | 1,000 | -   | -   | 1,000 | ps   |

| t <sub>RISE</sub>          | Rise time                                                                                                                             | 20 - 80%, C <sub>LOAD</sub><br>= 5 pF | _   | 500      | -     | _   | 500 | -     | _   | 500 | -     | ps   |

| t <sub>FALL</sub>          | Fall time                                                                                                                             | 20 - 80%, C <sub>LOAD</sub><br>= 5 pF | _   | 500      | -     | _   | 500 | -     | _   | 500 | -     | ps   |

| t <sub>lock</sub>          | Time required for the<br>PLL to lock, after<br>CONF_DONE signal<br>goes high, indicating<br>the completion of<br>device configuration | _                                     | _   | _        | 1     | _   | _   | 1     | _   | _   | 1     | ms   |

$^{(67)}$  TCCS specifications apply to I/O banks from the same side only.

<sup>(68)</sup> TX jitter is the jitter induced from core noise and I/O switching noise.

| Symbol                                | Parameter                                                                                                                          | Mode | - <b>C7</b> | , –17 | -/  | 47    | -0  | C8    | Unit |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|-------------|-------|-----|-------|-----|-------|------|

|                                       |                                                                                                                                    |      | Min         | Мах   | Min | Мах   | Min | Мах   |      |

|                                       |                                                                                                                                    | ×8   | 80          | 200   | 80  | 200   | 80  | 200   | Mbps |

|                                       |                                                                                                                                    | ×7   | 70          | 200   | 70  | 200   | 70  | 200   | Mbps |

|                                       |                                                                                                                                    | ×4   | 40          | 200   | 40  | 200   | 40  | 200   | Mbps |

|                                       |                                                                                                                                    | ×2   | 20          | 200   | 20  | 200   | 20  | 200   | Mbps |

|                                       |                                                                                                                                    | ×1   | 10          | 200   | 10  | 200   | 10  | 200   | Mbps |

| SW                                    | Sampling window (high-<br>speed I/O performance pin)                                                                               | _    | -           | 910   | -   | 910   | -   | 910   | ps   |

|                                       | Sampling window (low-<br>speed I/O performance pin)                                                                                | _    | -           | 1,110 | _   | 1,110 | _   | 1,110 | ps   |

| t <sub>x Jitter</sub> <sup>(71)</sup> | Input jitter                                                                                                                       | _    | -           | 1,000 | -   | 1,000 | -   | 1,000 | ps   |

| t <sub>lock</sub>                     | Time required for the PLL to<br>lock, after CONF_DONE<br>signal goes high, indicating<br>the completion of device<br>configuration | _    | _           | 1     | _   | 1     | _   | 1     | ms   |

## Dual Supply Devices LVDS, TMDS, HiSpi, SLVS, and Sub-LVDS Receiver Timing Specifications

# Table 46. LVDS, TMDS, HiSpi, SLVS, and Sub-LVDS Receiver Timing Specifications for Intel MAX 10 Dual Supply Devices LVDS, TMDS, HiSpi, SLVS, and Sub-LVDS receivers are supported at all banks.

| Symbol             | Parameter                    | Mode | -16, -A6, -C7, -17 |     | -A7 |     | -C8 |     | Unit      |

|--------------------|------------------------------|------|--------------------|-----|-----|-----|-----|-----|-----------|

|                    |                              |      | Min                | Max | Min | Max | Min | Мах |           |

| f <sub>HSCLK</sub> | Input clock frequency (high- | ×10  | 5                  | 350 | 5   | 320 | 5   | 320 | MHz       |

|                    | speed I/O performance pin)   | ×8   | 5                  | 360 | 5   | 320 | 5   | 320 | MHz       |

|                    |                              | ×7   | 5                  | 350 | 5   | 320 | 5   | 320 | MHz       |

|                    |                              | ×4   | 5                  | 360 | 5   | 320 | 5   | 320 | MHz       |

|                    | •                            |      |                    |     |     |     |     |     | continued |

<sup>(71)</sup> TX jitter is the jitter induced from core noise and I/O switching noise.

#### Intel<sup>®</sup> MAX<sup>®</sup> 10 FPGA Device Datasheet

M10-DATASHEET | 2018.06.29

| Symbol             | Parameter                                                 | Mode | -I6, -A6 | , -C7, -I7 |     | 47       | -0  | 8   | Unit      |

|--------------------|-----------------------------------------------------------|------|----------|------------|-----|----------|-----|-----|-----------|

|                    |                                                           |      | Min      | Max        | Min | Мах      | Min | Max | 1         |

|                    |                                                           | ×2   | 5        | 360        | 5   | 320      | 5   | 320 | MHz       |

|                    |                                                           | ×1   | 5        | 360        | 5   | 320      | 5   | 320 | MHz       |

| HSIODR             | Data rate (high-speed I/O                                 | ×10  | 100      | 700        | 100 | 640      | 100 | 640 | Mbps      |

|                    | performance pin)                                          | ×8   | 80       | 720        | 80  | 640      | 80  | 640 | Mbps      |

|                    |                                                           | ×7   | 70       | 700        | 70  | 640      | 70  | 640 | Mbps      |

|                    |                                                           | ×4   | 40       | 720        | 40  | 640      | 40  | 640 | Mbps      |

|                    |                                                           | ×2   | 20       | 720        | 20  | 640      | 20  | 640 | Mbps      |

|                    |                                                           | ×1   | 10       | 360        | 10  | 320      | 10  | 320 | Mbps      |

| f <sub>HSCLK</sub> | Input clock frequency (low-<br>speed I/O performance pin) | ×10  | 5        | 150        | 5   | 150      | 5   | 150 | MHz       |

|                    |                                                           | ×8   | 5        | 150        | 5   | 150      | 5   | 150 | MHz       |

|                    |                                                           | ×7   | 5        | 150        | 5   | 150      | 5   | 150 | MHz       |

|                    |                                                           | ×4   | 5        | 150        | 5   | 150      | 5   | 150 | MHz       |

|                    |                                                           | ×2   | 5        | 150        | 5   | 150      | 5   | 150 | MHz       |

|                    |                                                           | ×1   | 5        | 300        | 5   | 300      | 5   | 300 | MHz       |

| HSIODR             | Data rate (low-speed I/O                                  | ×10  | 100      | 300        | 100 | 300      | 100 | 300 | Mbps      |

|                    | performance pin)                                          | ×8   | 80       | 300        | 80  | 300      | 80  | 300 | Mbps      |

|                    |                                                           | ×7   | 70       | 300        | 70  | 300      | 70  | 300 | Mbps      |

|                    |                                                           | ×4   | 40       | 300        | 40  | 300      | 40  | 300 | Mbps      |

|                    |                                                           | ×2   | 20       | 300        | 20  | 300      | 20  | 300 | Mbps      |

|                    |                                                           | ×1   | 10       | 300        | 10  | 300      | 10  | 300 | Mbps      |

| SW                 | Sampling window (high-<br>speed I/O performance pin)      | -    | -        | 510        | -   | 510      | _   | 510 | ps        |

|                    | · · ·                                                     |      |          |            | ·   | <u> </u> | I   | (   | continued |

| Symbol                                | Parameter                                                                                                                          | Mode | -I6, -A6, -C7, -I7 |     | -A7 |     | -C8 |     | Unit |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|-----|-----|-----|-----|-----|------|

|                                       |                                                                                                                                    |      | Min                | Max | Min | Max | Min | Max |      |

|                                       | Sampling window (low-<br>speed I/O performance pin)                                                                                | _    | -                  | 910 | -   | 910 | _   | 910 | ps   |

| t <sub>x Jitter</sub> <sup>(72)</sup> | Input jitter                                                                                                                       | _    | -                  | 500 | _   | 500 | _   | 500 | ps   |

| t <sub>LOCK</sub>                     | Time required for the PLL to<br>lock, after CONF_DONE<br>signal goes high, indicating<br>the completion of device<br>configuration | _    | _                  | 1   | _   | 1   | _   | 1   | ms   |

## Memory Standards Supported by the Soft Memory Controller

### Table 47. Memory Standards Supported by the Soft Memory Controller for Intel MAX 10 Devices

Contact your local sales representatives for access to the -I6 or -A6 speed grade devices in the Intel Quartus Prime software.

| External Memory Interface<br>Standard | Rate Support | Speed Grade | Voltage (V) | Max Frequency (MHz) |

|---------------------------------------|--------------|-------------|-------------|---------------------|

| DDR3 SDRAM                            | Half         | -I6         | 1.5         | 303                 |

| DDR3L SDRAM                           | Half         | -I6         | 1.35        | 303                 |

| DDR2 SDRAM                            | Half         | -I6         | 1.8         | 200                 |

|                                       |              | -I7 and -C7 |             | 167                 |

| LPDDR2 <sup>(73)</sup>                | Half         | -I6         | 1.2         | 200 <sup>(74)</sup> |

#### **Related Information**

External Memory Interface Spec Estimator

Provides the specific details of the memory standards supported.

<sup>&</sup>lt;sup>(72)</sup> TX jitter is the jitter induced from core noise and I/O switching noise.

<sup>&</sup>lt;sup>(73)</sup> Intel MAX 10 devices support only single-die LPDDR2.

<sup>&</sup>lt;sup>(74)</sup> To achieve the specified performance, constrain the memory device I/O and core power supply variation to within ±3%. By default, the frequency is 167 MHz.

# **JTAG Timing Parameters**

## Table 49. JTAG Timing Parameters for Intel MAX 10 Devices

The values are based on  $C_L = 10 \text{ pF of TDO}$ .

The affected Boundary Scan Test (BST) instructions are SAMPLE/PRELOAD, EXTEST, INTEST, and CHECK\_STATUS.

| Symbol                | Parameter                                | Non-BST and non- | -CONFIG_IO Operation                                                                                                           | BST and C | ONFIG_IO Operation                                                                                                             | Unit |

|-----------------------|------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------|------|

|                       |                                          | Minimum          | Maximum                                                                                                                        | Minimum   | Maximum                                                                                                                        |      |

| t <sub>JCP</sub>      | TCK clock period                         | 40               | -                                                                                                                              | 50        | -                                                                                                                              | ns   |

| t <sub>JCH</sub>      | TCK clock high time                      | 20               | -                                                                                                                              | 25        | -                                                                                                                              | ns   |

| t <sub>JCL</sub>      | TCK clock low time                       | 20               | -                                                                                                                              | 25        | -                                                                                                                              | ns   |

| t <sub>JPSU_TDI</sub> | JTAG port setup time                     | 2                | -                                                                                                                              | 2         | -                                                                                                                              | ns   |

| t <sub>JPSU_TMS</sub> | JTAG port setup time                     | 3                | -                                                                                                                              | 3         | -                                                                                                                              | ns   |

| t <sub>JPH</sub>      | JTAG port hold time                      | 10               | -                                                                                                                              | 10        | -                                                                                                                              | ns   |

| t <sub>JPCO</sub>     | JTAG port clock to output                | _                | <ul> <li>15 (for V<sub>CCIO</sub> = 3.3, 3.0, and 2.5 V)</li> <li>17 (for V<sub>CCIO</sub> = 1.8 and 1.5 V)</li> </ul>         | _         | • 18 (for $V_{CCIO} = 3.3, 3.0,$<br>and 2.5 V)<br>• 20 (for $V_{CCIO} = 1.8$ and<br>1.5 V)                                     | ns   |

| t <sub>JPZX</sub>     | JTAG port high impedance to valid output | -                | <ul> <li>15 (for V<sub>CCIO</sub> = 3.3, 3.0,<br/>and 2.5 V)</li> <li>17 (for V<sub>CCIO</sub> = 1.8 and<br/>1.5 V)</li> </ul> | _         | <ul> <li>15 (for V<sub>CCIO</sub> = 3.3, 3.0,<br/>and 2.5 V)</li> <li>17 (for V<sub>CCIO</sub> = 1.8 and<br/>1.5 V)</li> </ul> | ns   |

| t <sub>JPXZ</sub>     | JTAG port valid output to high impedance | -                | <ul> <li>15 (for V<sub>CCIO</sub> = 3.3, 3.0,<br/>and 2.5 V)</li> <li>17 (for V<sub>CCIO</sub> = 1.8 and<br/>1.5 V)</li> </ul> | _         | <ul> <li>15 (for V<sub>CCIO</sub> = 3.3, 3.0,<br/>and 2.5 V)</li> <li>17 (for V<sub>CCIO</sub> = 1.8 and<br/>1.5 V)</li> </ul> | ns   |

| Device | CFM Data                      | Size (bits)                |

|--------|-------------------------------|----------------------------|

|        | Without Memory Initialization | With Memory Initialization |

| 10M25  | 4,140,000                     | 4,780,000                  |

| 10M40  | 7,840,000                     | 9,670,000                  |

| 10M50  | 7,840,000                     | 9,670,000                  |

## **Internal Configuration Time**

The internal configuration time measurement is from the rising edge of nSTATUS signal to the rising edge of  $CONF_DONE$  signal.

## Table 53. Internal Configuration Time for Intel MAX 10 Devices (Uncompressed .rbf)

| Device |               |                  |                            | Internal Configu | ration Time (ms) |                   |                            |       |

|--------|---------------|------------------|----------------------------|------------------|------------------|-------------------|----------------------------|-------|

|        |               | Unenci           | rypted                     |                  |                  | Encry             | pted                       |       |

|        | Without Memor | y Initialization | With Memory Initialization |                  | Without Memo     | ry Initialization | With Memory Initialization |       |

|        | Min           | Max              | Min                        | Мах              | Min              | Max               | Min                        | Max   |

| 10M02  | 0.3           | 1.7              | _                          | _                | 1.7              | 5.4               | _                          | _     |

| 10M04  | 0.6           | 2.7              | 1.0                        | 3.4              | 5.0              | 15.0              | 6.8                        | 19.6  |

| 10M08  | 0.6           | 2.7              | 1.0                        | 3.4              | 5.0              | 15.0              | 6.8                        | 19.6  |

| 10M16  | 1.1           | 3.7              | 1.4                        | 4.5              | 9.3              | 25.3              | 11.7                       | 31.5  |

| 10M25  | 1.0           | 3.7              | 1.3                        | 4.4              | 14.0             | 38.1              | 16.9                       | 45.7  |

| 10M40  | 2.6           | 6.9              | 3.2                        | 9.8              | 41.5             | 112.1             | 51.7                       | 139.6 |

| 10M50  | 2.6           | 6.9              | 3.2                        | 9.8              | 41.5             | 112.1             | 51.7                       | 139.6 |

| Date      | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |            | <ul> <li>Added -A6 speed grade in the following tables:         <ul> <li>Intel MAX 10 Device Grades and Speed Grades Supported</li> <li>Series OCT without Calibration Specifications for Intel MAX 10 Devices</li> <li>Clock Tree Specifications for Intel MAX 10 Devices</li> <li>Embedded Multiplier Specifications for Intel MAX 10 Devices</li> <li>Memory Block Performance Specifications for Intel MAX 10 Devices</li> <li>True PPDS and Emulated PPDS_E_3R Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>True RSDS and Emulated RSDS_E_3R Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>Emulated RSDS_E_1R Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>True Mini-LVDS and Emulated Mini-LVDS_E_3R Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>True LVDS Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>Emulated LVDS_E_3R, SLVS, and Sub-LVDS Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>LVDS, TMDS, HiSpi, SLVS, and Sub-LVDS Receiver Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>IOE Programmable Delay on Row Pins for Intel MAX 10 Devices</li> <li>UD Programmable Delay on Column Pins for Intel MAX 10 Devices</li> <li>Updated the dual supply mode performance in Embedded Multiplier Specifications for Intel MAX 10 Devices table.</li> </ul> </li> <li>Updated the dual supply mode performance in Embedded Multiplier Specifications for Intel MAX 10 Devices table.</li> <li>Updated the dual supply mode performance in Memory Block Performance Specifications for Intel MAX 10 Devices table.</li> <li>Updated the dual supply mode performance in Memory Block Performance Specifications for Intel MAX 10 Devices table.</li> <li>U</li></ul> |

| June 2015 | 2015.06.12 | <ul> <li>Updated the maximum values in Internal Weak Pull-Up Resistor for Intel MAX 10 Devices table.</li> <li>Removed Internal Weak Pull-Up Resistor equation.</li> <li>Updated the note for input resistance and input capacitance parameters in the ADC Performance Specifications table for both single supply and dual supply devices. Note: Download the SPICE models for simulation.</li> <li>Added a note to AC Accuracy - THD, SNR, and SINAD parameters in the ADC Performance Specifications for Intel MAX 10 Dual Supply Devices table. Note: When using internal V<sub>REF</sub>, THD = 66 dB, SNR = 58 dB and SINAD = 57.5 dB for dedicated ADC input channels.</li> <li>Updated clock period jitter and cycle-to-cycle period jitter parameters in the Memory Output Clock Jitter Specifications for Intel MAX 10 Devices table.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Image: State of the second | Date          | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| table. This note is not valid: All V <sub>CCA</sub> pins must be connected together for EQFP package.Corrected the maximum value for t <sub>OUTJITTER_CCJ_IO</sub> (F <sub>OUT</sub> ≥ 100 MHz) from 60 ps to 650 ps in PLL Specifications for Intel<br>MAX 10 Devices table.December 20142014.12.15Added statements in the I/O Pin Leakage Current section: Input channel leakage of ADC I/O pins due to hot socket is up<br>to maximum of 1.8 mA. The input channel leakage occurs when the ADC IP core is enabled or disabled. This is applicable<br>to all Intel MAX 10 devices with ADC IP core, which are 10M04, 10M08, 10M16, 10M25, 10M40, and 10M50 devices. The<br>ADC I/O pins are in Bank 1A.Added a statement in the I/O Standards Specifications section: You must perform timing closure analysis to determine the<br>maximum achievable frequency for general purpose I/O standards.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |            | <ul> <li>True PPDS and Emulated PPDS_E_3R Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>True RSDS and Emulated RSDS_E_3R Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>Emulated RSDS_E_1R Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>True Mini-LVDS and Emulated Mini-LVDS_E_3R Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>True LVDS Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>True LVDS Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>Emulated LVDS_E_3R, SLVS, and Sub-LVDS Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>Emulated LVDS_E_3R, SLVS, and Sub-LVDS Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>Updated tx jitter specifications in the following tables:</li> <li>True PPDS and Emulated RDDS_E_3R Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>Emulated RSDS_E_1R Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>Emulated RSDS_E_1R Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>True RDDS and Emulated Mini-LVDS_E_3R Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>Emulated RSDS_E_1R Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>Emulated RSDS_E_1R Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>True LVDS Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>Emulated RSDS_E_1R Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>Emulated RSDS_E_1R Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>Emulated RSDS_E_1R Transmitter Timing Specifications for Intel MAX 10 Dual Supply Devices</li> <li>Updated RS</li></ul> |