# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | 8051                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 100MHz                                                       |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT           |

| Number of I/O              | 64                                                           |

| Program Memory Size        | 128KB (128K x 8)                                             |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                |                                                              |

| RAM Size                   | 8.25K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                    |

| Data Converters            | A/D 8x8b, 8x10b; D/A 2x12b                                   |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 100-TQFP                                                     |

| Supplier Device Package    | 100-TQFP (14x14)                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f120r |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

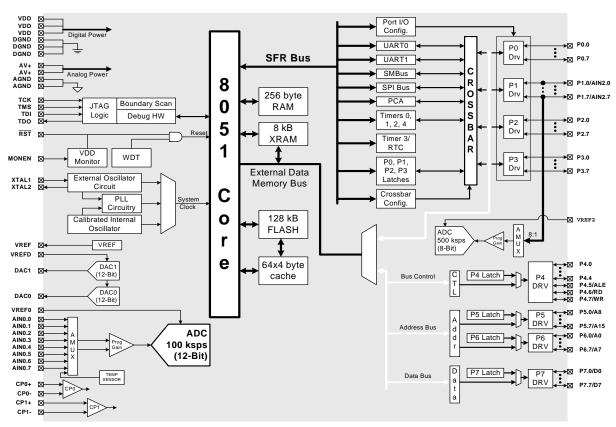

Figure 1.1. C8051F120/124 Block Diagram

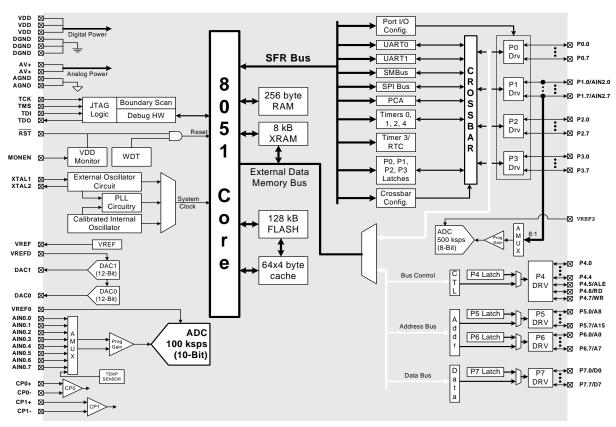

Figure 1.3. C8051F122/126 Block Diagram

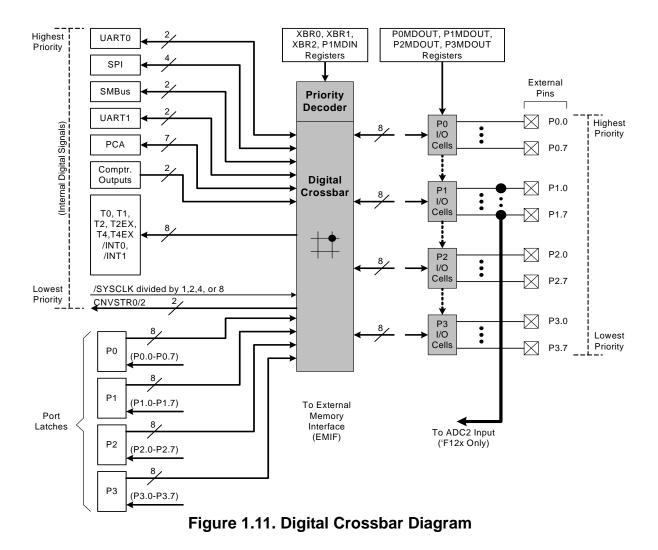

#### 1.5. Programmable Digital I/O and Crossbar

The standard 8051 8-bit Ports (0, 1, 2, and 3) are available on the MCUs. The devices in the larger (100pin TQFP) packaging have 4 additional ports (4, 5, 6, and 7) for a total of 64 general-purpose port I/O. The Port I/O behave like the standard 8051 with a few enhancements.

Each Port I/O pin can be configured as either a push-pull or open-drain output. Also, the "weak pullups" which are normally fixed on an 8051 can be globally disabled, providing additional power saving capabilities for low-power applications.

Perhaps the most unique enhancement is the Digital Crossbar. This is a large digital switching network that allows mapping of internal digital system resources to Port I/O pins on P0, P1, P2, and P3. (See Figure 1.11) Unlike microcontrollers with standard multiplexed digital I/O, all combinations of functions are supported.

The on-chip counter/timers, serial buses, HW interrupts, ADC Start of Conversion inputs, comparator outputs, and other digital signals in the controller can be configured to appear on the Port I/O pins specified in the Crossbar Control registers. This allows the user to select the exact mix of general purpose Port I/O and digital resources needed for the particular application.

### 2. Absolute Maximum Ratings

| Parameter                                                                                                                                                                                                                             | Conditions          | Min      | Тур       | Max                      | Units    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------|-----------|--------------------------|----------|

| Ambient temperature under bias                                                                                                                                                                                                        |                     | -55      |           | 125                      | °C       |

| Storage Temperature                                                                                                                                                                                                                   |                     | -65      | —         | 150                      | °C       |

| Voltage on any Pin (except V <sub>DD</sub> and Port I/O) with Respect to DGND                                                                                                                                                         |                     | -0.3     |           | V <sub>DD</sub> +<br>0.3 | V        |

| Voltage on any Port I/O Pin or RST with Respect to DGND                                                                                                                                                                               |                     | -0.3     | _         | 5.8                      | V        |

| Voltage on V <sub>DD</sub> with Respect to DGND                                                                                                                                                                                       |                     | -0.3     | _         | 4.2                      | V        |

| Maximum Total Current through V <sub>DD</sub> , AV+, DGND,<br>and AGND                                                                                                                                                                |                     | _        | _         | 800                      | mA       |

| Maximum Output Current Sunk by any Port pin                                                                                                                                                                                           |                     |          |           | 100                      | mA       |

| Maximum Output Current Sunk by any other I/O pin                                                                                                                                                                                      |                     |          |           | 50                       | mA       |

| Maximum Output Current Sourced by any Port pin                                                                                                                                                                                        |                     |          |           | 100                      | mA       |

| Maximum Output Current Sourced by any other I/O<br>Pin                                                                                                                                                                                |                     |          |           | 50                       | mA       |

| *Note: Stresses above those listed under "Absolute Maximu<br>This is a stress rating only and functional operation of<br>indicated in the operation listings of this specification<br>extended periods may affect device reliability. | the devices at thos | e or any | other con | ditions abo              | ve those |

### Table 2.1. Absolute Maximum Ratings<sup>\*</sup>

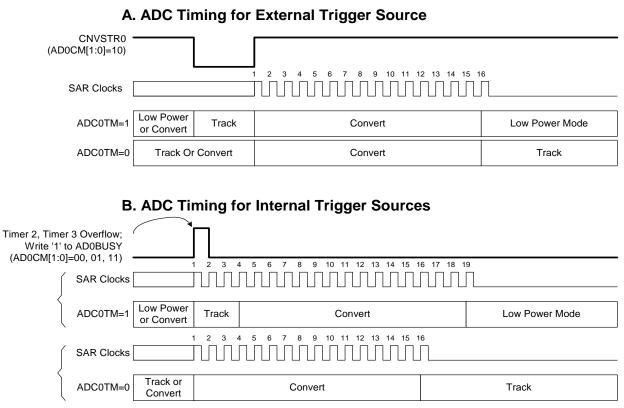

#### 6.2.2. Tracking Modes

The AD0TM bit in register ADC0CN controls the ADC0 track-and-hold mode. In its default state, the ADC0 input is continuously tracked when a conversion is not in progress. When the AD0TM bit is logic 1, ADC0 operates in low-power track-and-hold mode. In this mode, each conversion is preceded by a tracking period of 3 SAR clocks (after the start-of-conversion signal). When the CNVSTR0 signal is used to initiate conversions in low-power tracking mode, ADC0 tracks only when CNVSTR0 is low; conversion begins on the rising edge of CNVSTR0 (see Figure 6.3). Tracking can also be disabled (shutdown) when the entire chip is in low power standby or sleep modes. Low-power track-and-hold mode is also useful when AMUX or PGA settings are frequently changed, to ensure that settling time requirements are met (see **Section "6.2.3. Settling Time Requirements" on page 77**).

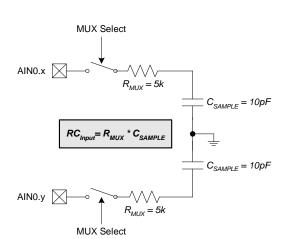

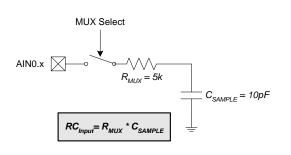

#### 6.2.3. Settling Time Requirements

A minimum tracking time is required before an accurate conversion can be performed. This tracking time is determined by the ADC0 MUX resistance, the ADC0 sampling capacitance, any external source resistance, and the accuracy required for the conversion. Figure 6.4 shows the equivalent ADC0 input circuits for both Differential and Single-ended modes. Notice that the equivalent time constant for both input circuits is the same. The required settling time for a given settling accuracy (*SA*) may be approximated by Equation 6.1. When measuring the Temperature Sensor output,  $R_{TOTAL}$  reduces to  $R_{MUX}$ . An absolute minimum settling time of 1.5 µs is required after any MUX or PGA selection. Note that in low-power tracking mode, three SAR clocks are used for tracking at the start of every conversion. For most applications, these three SAR clocks will meet the tracking requirements.

$$t = \ln\left(\frac{2^n}{SA}\right) \times R_{TOTAL} C_{SAMPLE}$$

#### Equation 6.1. ADC0 Settling Time Requirements

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the ADC0 MUX resistance and any external source resistance. *n* is the ADC resolution in bits (10).

**Differential Mode**

Single-Ended Mode

#### Figure 6.4. ADC0 Equivalent Input Circuits

#### Table 6.1. 10-Bit ADC0 Electrical Characteristics (C8051F122/3/6/7 and C8051F13x)

V<sub>DD</sub> = 3.0 V, AV+ = 3.0 V, VREF = 2.40 V (REFBE = 0), PGA Gain = 1, -40 to +85 °C unless otherwise specified.

| Parameter                                     | Conditions                         | Min      | Тур        | Max       | Units  |

|-----------------------------------------------|------------------------------------|----------|------------|-----------|--------|

|                                               | DC Accuracy                        |          | 1          |           | 1      |

| Resolution                                    |                                    |          | 10         |           | bits   |

| Integral Nonlinearity                         |                                    |          |            | ±1        | LSB    |

| Differential Nonlinearity                     | Guaranteed Monotonic               |          |            | ±1        | LSB    |

| Offset Error                                  |                                    |          | ±0.5       | _         | LSB    |

| Full Scale Error                              | Differential mode                  |          | -1.5±0.5   |           | LSB    |

| Offset Temperature Coefficient                |                                    |          | ±0.25      | _         | ppm/°C |

| Dynamic Performance (1                        | 0 kHz sine-wave input, 0 to 1      | dB below | Full Scale | e, 100 ks | ps     |

| Signal-to-Noise Plus Distortion               |                                    | 59       | —          | —         | dB     |

| Total Harmonic Distortion                     | Up to the 5 <sup>th</sup> harmonic |          | -70        |           | dB     |

| Spurious-Free Dynamic Range                   |                                    |          | 80         |           | dB     |

|                                               | Conversion Rate                    |          |            |           | L      |

| SAR Clock Frequency                           |                                    |          | _          | 2.5       | MHz    |

| Conversion Time in SAR Clocks                 |                                    | 16       |            | _         | clocks |

| Track/Hold Acquisition Time                   |                                    | 1.5      | _          |           | μs     |

| Throughput Rate                               |                                    |          |            | 100       | ksps   |

|                                               | Analog Inputs                      |          | 1          |           | I      |

| Input Voltage Range                           | Single-ended operation             | 0        | _          | VREF      | V      |

| *Common-mode Voltage Range                    | Differential operation             | AGND     |            | AV+       | V      |

| Input Capacitance                             |                                    | _        | 10         | _         | pF     |

|                                               | Temperature Sensor                 |          |            |           | I      |

| Linearity <sup>1</sup>                        |                                    |          | ±0.2       |           | °C     |

| Offset                                        | (Temp = 0 °C)                      |          | 776        | _         | mV     |

| Offset Error <sup>1,2</sup>                   | (Temp = 0 °C)                      |          | ±8.5       | _         | mV     |

| Slope                                         |                                    |          | 2.86       |           | mV/°C  |

| Slope Error <sup>2</sup>                      |                                    |          | ±0.034     | _         | mV/°C  |

|                                               | Power Specifications               |          | 1          |           |        |

| Power Supply Current<br>(AV+ supplied to ADC) | Operating Mode, 100 ksps           | —        | 450        | 900       | μA     |

| Power Supply Rejection                        |                                    | —        | ±0.3       | —         | mV/V   |

| Notes:<br>1. Includes ADC offset, gain, and   | linearity variations               |          | 1          |           | 1      |

1. Includes ADC offset, gain, and linearity variations.

2. Represents one standard deviation from the mean.

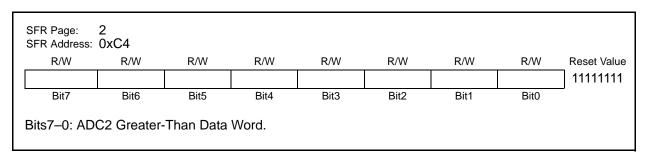

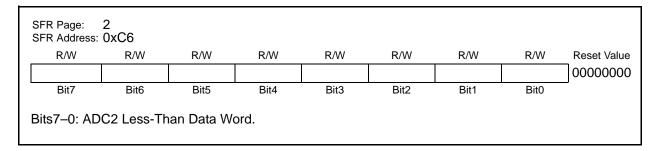

#### SFR Definition 7.6. ADC2GT: ADC2 Greater-Than Data Byte

#### SFR Definition 7.7. ADC2LT: ADC2 Less-Than Data Byte

### 11. CIP-51 Microcontroller

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. Included are five 16-bit counter/timers (see description in **Section 23**), two full-duplex UARTs (see description in **Section 21** and **Section 22**), 256 bytes of internal RAM, 128 byte Special Function Register (SFR) address space (see **Section 11.2.6**), and 8/4 byte-wide I/O Ports (see description in **Section 18**). The CIP-51 also includes on-chip debug hardware (see description in **Section 25**), and interfaces directly with the MCU's analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 11.1 for a block diagram).

- Fully Compatible with MCS-51 Instruction Set

- 100 or 50 MIPS Peak Using the On-Chip PLL

- 256 Bytes of Internal RAM

- 8/4 Byte-Wide I/O Ports

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

The CIP-51 includes the following features:

#### Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

With the CIP-51's system clock running at 100 MHz, it has a peak throughput of 100 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

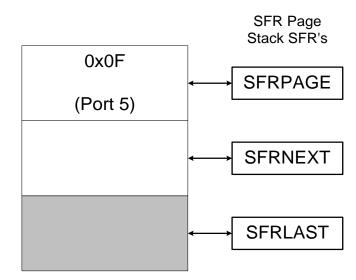

#### 11.2.6.3.SFR Page Stack Example

The following is an example that shows the operation of the SFR Page Stack during interrupts.

In this example, the SFR Page Control is left in the default enabled state (i.e., SFRPGEN = 1), and the CIP-51 is executing in-line code that is writing values to Port 5 (SFR "P5", located at address 0xD8 on SFR Page 0x0F). The device is also using the Programmable Counter Array (PCA) and the 10-bit ADC (ADC2) window comparator to monitor a voltage. The PCA is timing a critical control function in its interrupt service routine (ISR), so its interrupt is enabled and is set to *high* priority. The ADC2 is monitoring a voltage that is less important, but to minimize the software overhead its window comparator is being used with an associated ISR that is set to *low* priority. At this point, the SFR page is set to access the Port 5 SFR (SFRPAGE = 0x0F). See Figure 11.5 below.

#### Figure 11.5. SFR Page Stack While Using SFR Page 0x0F To Access Port 5

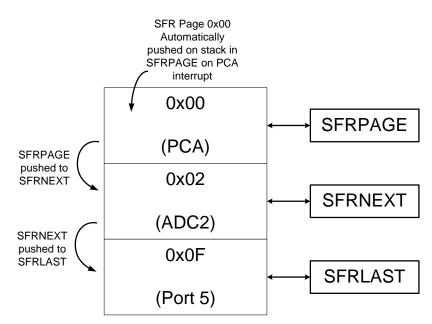

While CIP-51 executes in-line code (writing values to Port 5 in this example), ADC2 Window Comparator Interrupt occurs. The CIP-51 vectors to the ADC2 Window Comparator ISR and pushes the current SFR Page value (SFR Page 0x0F) into SFRNEXT in the SFR Page Stack. The SFR page needed to access ADC2's SFR's is then automatically placed in the SFRPAGE register (SFR Page 0x02). SFRPAGE is considered the "top" of the SFR Page Stack. Software can now access the ADC2 SFR's. Software may switch to any SFR Page by writing a new value to the SFRPAGE register at any time during the ADC2 ISR to access SFR's that are not on SFR Page 0x02. See Figure 11.6 below.

#### Figure 11.7. SFR Page Stack Upon PCA Interrupt Occurring During an ADC2 ISR

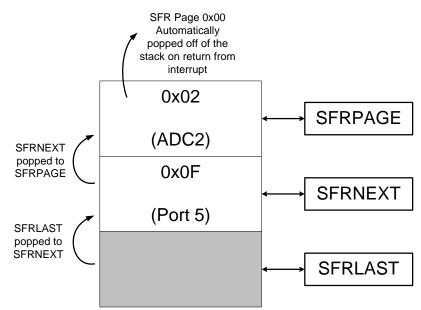

On exit from the PCA interrupt service routine, the CIP-51 will return to the ADC2 Window Comparator ISR. On execution of the RETI instruction, SFR Page 0x00 used to access the PCA registers will be automatically popped off of the SFR Page Stack, and the contents of the SFRNEXT register will be moved to the SFRPAGE register. Software in the ADC2 ISR can continue to access SFR's as it did prior to the PCA interrupt. Likewise, the contents of SFRLAST are moved to the SFRNEXT register. Recall this was the SFR Page value 0x0F being used to access Port 5 before the ADC2 interrupt occurred. See Figure 11.8 below.

Figure 11.8. SFR Page Stack Upon Return From PCA Interrupt

#### **15.2. Security Options**

The CIP-51 provides security options to protect the Flash memory from inadvertent modification by software as well as prevent the viewing of proprietary program code and constants. The Program Store Write Enable (PSCTL.0), Program Store Erase Enable (PSCTL.1), and Flash Write/Erase Enable (FLACL.0) bits protect the Flash memory from accidental modification by software. These bits must be explicitly set to logic 1 before software can write or erase the Flash memory. Additional security features prevent proprietary program code and data constants from being read or altered across the JTAG interface or by software running on the system controller.

A set of security lock bytes protect the Flash program memory from being read or altered across the JTAG interface. Each bit in a security lock-byte protects one 16k-byte block of memory. Clearing a bit to logic 0 in the Read Lock Byte prevents the corresponding block of Flash memory from being read across the JTAG interface. Clearing a bit in the Write/Erase Lock Byte protects the block from JTAG erasures and/or writes. The Scratchpad area is read or write/erase locked when all bits in the corresponding security byte are cleared to logic 0.

On the C8051F12x and C8051F130/1, the security lock bytes are located at 0x1FBFE (Write/Erase Lock) and 0x1FBFF (Read Lock), as shown in Figure 15.2. On the C8051F132/3, the security lock bytes are located at 0x0FFFE (Write/Erase Lock) and 0x0FFFF (Read Lock), as shown in Figure 15.3. The 1024-byte sector containing the lock bytes can be written to, but not erased, by software. An attempted read of a read-locked byte returns undefined data. Debugging code in a read-locked sector is not possible through the JTAG interface. The lock bits can always be read from and written to logic 0 regardless of the security setting applied to the block containing the security bytes. This allows additional blocks to be protected after the block containing the security bytes has been locked.

Important Note: To ensure protection from external access, the block containing the lock bytes must be Write/Erase locked. On the 128 kB devices (C8051F12x and C8051F130/1), the block containing the security bytes is 0x18000-0x1BFFF, and is locked by clearing bit 7 of the Write/Erase Lock Byte. On the 64 kB devices (C8051F132/3), the block containing the security bytes is 0x0C000-0x0FFFF, and is locked by clearing bit 3 of the Write/Erase Lock Byte. If the page containing the security bytes is not Write/Erase locked, it is still possible to erase this page of Flash memory through the JTAG port and reset the security bytes.

When the page containing the security bytes has been Write/Erase locked, a JTAG full device erase must be performed to unlock any areas of Flash protected by the security bytes. A JTAG full device erase is initiated by performing a normal JTAG erase operation on either of the security byte locations. This operation must be initiated through the JTAG port, and cannot be performed from firmware running on the device.

ple, to assign TX0 to a Port pin without assigning RX0 as well. Each combination of enabled peripherals results in a unique device pinout.

All Port pins on Ports 0 through 3 that are not allocated by the Crossbar can be accessed as General-Purpose I/O (GPIO) pins by reading and writing the associated Port Data registers (See SFR Definition 18.4, SFR Definition 18.6, SFR Definition 18.9, and SFR Definition 18.11), a set of SFR's which are both byteand bit-addressable. The output states of Port pins that are allocated by the Crossbar are controlled by the digital peripheral that is mapped to those pins. Writes to the Port Data registers (or associated Port bits) will have no effect on the states of these pins.

A Read of a Port Data register (or Port bit) will always return the logic state present at the pin itself, regardless of whether the Crossbar has allocated the pin for peripheral use or not. An exception to this occurs during the execution of a *read-modify-write* instruction (ANL, ORL, XRL, CPL, INC, DEC, DJNZ, JBC, CLR, SETB, and the bitwise MOV write operation). During the *read* cycle of the *read-modify-write* instruction, it is the contents of the Port Data register, not the state of the Port pins themselves, which is read. Note that at clock rates above 50 MHz, when a pin is written and then immediately read (i.e. a write instruction followed immediately by a read instruction), the propagation delay of the port drivers may cause the read instruction to return the previous logic level of the pin.

Because the Crossbar registers affect the pinout of the peripherals of the device, they are typically configured in the initialization code of the system before the peripherals themselves are configured. Once configured, the Crossbar registers are typically left alone.

Once the Crossbar registers have been properly configured, the Crossbar is enabled by setting XBARE (XBR2.4) to a logic 1. Until XBARE is set to a logic 1, the output drivers on Ports 0 through 3 are explicitly disabled in order to prevent possible contention on the Port pins while the Crossbar registers and other registers which can affect the device pinout are being written.

The output drivers on Crossbar-assigned input signals (like RX0, for example) are explicitly disabled; thus the values of the Port Data registers and the PnMDOUT registers have no effect on the states of these pins.

#### **18.1.2. Configuring the Output Modes of the Port Pins**

The output drivers on Ports 0 through 3 remain disabled until the Crossbar is enabled by setting XBARE (XBR2.4) to a logic 1.

The output mode of each port pin can be configured to be either Open-Drain or Push-Pull. In the Push-Pull configuration, writing a logic 0 to the associated bit in the Port Data register will cause the Port pin to be driven to GND, and writing a logic 1 will cause the Port pin to be driven to  $V_{DD}$ . In the Open-Drain configuration, writing a logic 0 to the associated bit in the Port Data register will cause the Port pin to be driven to GND, and a logic 1 will cause the Port pin to assume a high-impedance state. The Open-Drain configuration is useful to prevent contention between devices in systems where the Port pin participates in a shared interconnection in which multiple outputs are connected to the same physical wire (like the SDA signal on an SMBus connection).

The output modes of the Port pins on Ports 0 through 3 are determined by the bits in the associated PnMDOUT registers (See SFR Definition 18.5, SFR Definition 18.8, SFR Definition 18.10, and SFR Definition 18.12). For example, a logic 1 in P3MDOUT.7 will configure the output mode of P3.7 to Push-Pull; a logic 0 in P3MDOUT.7 will configure the output mode of P3.7 to Open-Drain. All Port pins default to Open-Drain output.

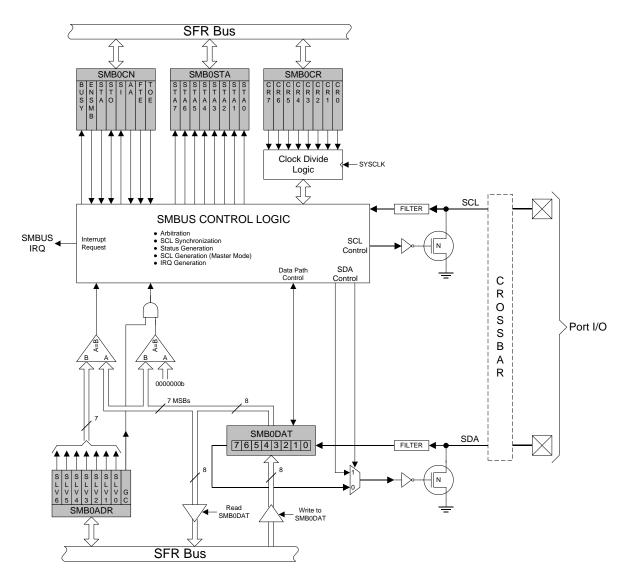

### 19. System Management Bus / I2C Bus (SMBus0)

The SMBus0 I/O interface is a two-wire, bi-directional serial bus. SMBus0 is compliant with the System Management Bus Specification, version 1.1, and compatible with the I2C serial bus. Reads and writes to the interface by the system controller are byte oriented with the SMBus0 interface autonomously controlling the serial transfer of the data. A method of extending the clock-low duration is available to accommodate devices with different speed capabilities on the same bus.

SMBus0 may operate as a master and/or slave, and may function on a bus with multiple masters. SMBus0 provides control of SDA (serial data), SCL (serial clock) generation and synchronization, arbitration logic, and START/STOP control and generation.

#### **19.4. SMBus Special Function Registers**

The SMBus0 serial interface is accessed and controlled through five SFR's: SMB0CN Control Register, SMB0CR Clock Rate Register, SMB0ADR Address Register, SMB0DAT Data Register and SMB0STA Status Register. The five special function registers related to the operation of the SMBus0 interface are described in the following sections.

#### 19.4.1. Control Register

The SMBus0 Control register SMB0CN is used to configure and control the SMBus0 interface. All of the bits in the register can be read or written by software. Two of the control bits are also affected by the SMBus0 hardware. The Serial Interrupt flag (SI, SMB0CN.3) is set to logic 1 by the hardware when a valid serial interrupt condition occurs. It can only be cleared by software. The Stop flag (STO, SMB0CN.4) is set to logic 1 by software. It is cleared to logic 0 by hardware when a STOP condition is detected on the bus.

Setting the ENSMB flag to logic 1 enables the SMBus0 interface. Clearing the ENSMB flag to logic 0 disables the SMBus0 interface and removes it from the bus. Momentarily clearing the ENSMB flag and then resetting it to logic 1 will reset SMBus0 communication. However, ENSMB should not be used to temporarily remove a device from the bus since the bus state information will be lost. Instead, the Assert Acknowledge (AA) flag should be used to temporarily remove the device from the bus (see description of AA flag below).

Setting the Start flag (STA, SMB0CN.5) to logic 1 will put SMBus0 in a master mode. If the bus is free, SMBus0 will generate a START condition. If the bus is not free, SMBus0 waits for a STOP condition to free the bus and then generates a START condition after a 5 µs delay per the SMB0CR value (In accordance with the SMBus protocol, the SMBus0 interface also considers the bus free if the bus is idle for 50 µs and no STOP condition was recognized). If STA is set to logic 1 while SMBus0 is in master mode and one or more bytes have been transferred, a repeated START condition will be generated.

When the Stop flag (STO, SMB0CN.4) is set to logic 1 while the SMBus0 interface is in master mode, the interface generates a STOP condition. In a slave mode, the STO flag may be used to recover from an error condition. In this case, a STOP condition is not generated on the bus, but the SMBus hardware behaves as if a STOP condition has been received and enters the "not addressed" slave receiver mode. Note that this simulated STOP will not cause the bus to appear free to SMBus0. The bus will remain occupied until a STOP appears on the bus or a Bus Free Timeout occurs. Hardware automatically clears the STO flag to logic 0 when a STOP condition is detected on the bus.

The Serial Interrupt flag (SI, SMB0CN.3) is set to logic 1 by hardware when the SMBus0 interface enters one of 27 possible states. If interrupts are enabled for the SMBus0 interface, an interrupt request is generated when the SI flag is set. The SI flag must be cleared by software.

**Important Note:** If SI is set to logic 1 while the SCL line is low, the clock-low period of the serial clock will be stretched and the serial transfer is suspended until SI is cleared to logic 0. A high level on SCL is not affected by the setting of the SI flag.

The Assert Acknowledge flag (AA, SMB0CN.2) is used to set the level of the SDA line during the acknowledge clock cycle on the SCL line. Setting the AA flag to logic 1 will cause an ACK (low level on SDA) to be sent during the acknowledge cycle if the device has been addressed. Setting the AA flag to logic 0 will cause a NACK (high level on SDA) to be sent during acknowledge cycle. After the transmission of a byte in slave mode, the slave can be temporarily removed from the bus by clearing the AA flag. The slave's own address and general call address will be ignored. To resume operation on the bus, the AA flag must be reset to logic 1 to allow the slave's address to be recognized.

#### 21.2. Multiprocessor Communications

Modes 2 and 3 support multiprocessor communication between a master processor and one or more slave processors by special use of the ninth data bit and the built-in UART0 address recognition hardware. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its ninth bit is logic 1; in a data byte, the ninth bit is always set to logic 0. UART0 will recognize as "valid" (i.e., capable of causing an interrupt) two types of addresses: (1) a masked address and (2) a broadcast address at any given time. Both are described below.

#### 21.2.1. Configuration of a Masked Address

The UART0 address is configured via two SFR's: SADDR0 (Serial Address) and SADEN0 (Serial Address Enable). SADEN0 sets the bit mask for the address held in SADDR0: bits set to logic 1 in SADEN0 correspond to bits in SADDR0 that are checked against the received address byte; bits set to logic 0 in SADEN0 correspond to "don't care" bits in SADDR0.

| Example 1, SLAVE #1    | Example 2, SLAVE #2        | Example 3, SLAVE #3      |  |  |

|------------------------|----------------------------|--------------------------|--|--|

| SADDR0 = 001101        | 1 SADDR0 = 00110101        | SADDR0 = 00110101        |  |  |

| SADEN0 = 000011        | 1 SADEN0 = 11110011        | SADEN0 = 11000000        |  |  |

| UART0 Address = xxxx01 | 1 UART0 Address = 0011xx01 | UART0 Address = 00xxxxxx |  |  |

Setting the SM20 bit (SCON0.5) configures UART0 such that when a stop bit is received, UART0 will generate an interrupt only if the ninth bit is logic 1 (RB80 = '1') and the received data byte matches the UARTO slave address. Following the received address interrupt, the slave will clear its SM20 bit to enable interrupts on the reception of the following data byte(s). Once the entire message is received, the addressed slave resets its SM20 bit to ignore all transmissions until it receives the next address byte. While SM20 is logic 1, UART0 ignores all bytes that do not match the UART0 address and include a ninth bit that is logic 1.

#### 21.2.2. Broadcast Addressing

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The broadcast address is the logical OR of registers SADDR0 and SADEN0, and '0's of the result are treated as "don't cares". Typically a broadcast address of 0xFF (hexadecimal) is acknowledged by all slaves, assuming "don't care" bits as '1's. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s)...

| Example 4, SI                                             | _AVE #1    | Example 5, SL     | AVE #2     | Example 6, SLAVE #3 |            |  |  |  |

|-----------------------------------------------------------|------------|-------------------|------------|---------------------|------------|--|--|--|

| SADDR0                                                    | = 00110101 | SADDR0            | = 00110101 | SADDR0              | = 00110101 |  |  |  |

| SADEN0                                                    | = 00001111 | SADEN0            | = 11110011 | SADEN0              | = 11000000 |  |  |  |

| Broadcast Address                                         | = 00111111 | Broadcast Address | = 11110111 | Broadcast Address   | = 11110101 |  |  |  |

| Where all ZEROES in the Broadcast address are don't cares |            |                   |            |                     |            |  |  |  |

Where all ZEROES in the Broadcast address are don't cares.

Note in the above examples 4, 5, and 6, each slave would recognize as "valid" an address of 0xFF as a broadcast address. Also note that examples 4, 5, and 6 uses the same SADDR0 and SADEN0 register values as shown in the examples 1, 2, and 3 respectively (slaves #1, 2, and 3). Thus, a master could address each slave device individually using a masked address, and also broadcast to all three slave devices. For example, if a Master were to send an address "11110101", only slave #1 would recognize the address as valid. If a master were to then send an address of "11111111", all three slave devices would recognize the address as a valid broadcast address.

NOTES:

#### JTAG Register Definition 25.4. FLASHDAT: JTAG Flash Data

|           |                 |             |               |               |              |              |             | Reset Value       |

|-----------|-----------------|-------------|---------------|---------------|--------------|--------------|-------------|-------------------|

|           |                 |             |               |               |              |              |             | 000000000         |

| Bit9      | •               |             |               |               |              |              | Bit0        |                   |

|           |                 |             |               |               |              |              |             |                   |

| This regi | ster is used to | o read or w | rite data to  | the Flash r   | memory acr   | ross the JT  | AG interfac | e.                |

| Bits9-2:  | DATA7-0: F      | lash Data I | Byte.         |               |              |              |             |                   |

| Bit1:     | FAIL: Flash     | Fail Bit.   | •             |               |              |              |             |                   |

|           | 0: Previous     |             |               |               |              |              |             |                   |

|           |                 |             | ory operat    | ion failed. L | Jsually indi | cates the a  | ssociated n | nemory loca-      |

| Dire      | tion was loc    |             |               |               |              |              |             |                   |

| Bit0:     | BUSY: Flas      | •           | · · · · · · · |               |              |              |             |                   |

|           | 0: Flash inte   | •           | -             |               |              |              |             | <b>A</b>          |

|           | ate another     | •           | is process    | ing a reque   | st. Reads c  | or writes wh | IIIE BUSY = | 1 will not initi- |

|           |                 | ·           |               |               |              |              |             |                   |

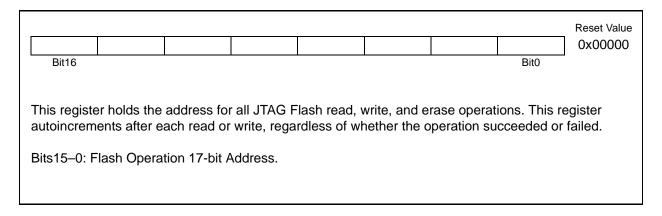

#### JTAG Register Definition 25.5. FLASHADR: JTAG Flash Address

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific to result in significant personal injury or death. Silicon Laboratories products are generally not intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

http://www.silabs.com