Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 100MHz                                                         |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 32                                                             |

| Program Memory Size        | 128KB (128K x 8)                                               |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 8.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                      |

| Data Converters            | A/D 8x8b, 8x12b; D/A 2x12b                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 64-TQFP                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f121-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 25. JTAG (IEEE 1149.1)          | 341 |

|---------------------------------|-----|

| 25.1.Boundary Scan              |     |

| 25.1.1.EXTEST Instruction       |     |

| 25.1.2.SAMPLE Instruction       | 343 |

| 25.1.3.BYPASS Instruction       | 343 |

| 25.1.4.IDCODE Instruction       | 343 |

| 25.2.Flash Programming Commands | 344 |

| 25.3.Debug Support              | 347 |

| Document Change List            |     |

| Contact Information             | 350 |

|                |                                  | Pin Nu | mbers          |                |               |                                                                                                                                                                                                                       |

|----------------|----------------------------------|--------|----------------|----------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name           | 'F120<br>'F122<br>'F124<br>'F126 | 'F125  | 'F130<br>'F132 | 'F131<br>'F133 | Туре          | Description                                                                                                                                                                                                           |

| DAC1           | 99                               | 63     |                |                | A Out         | Digital to Analog Converter 1 Voltage Output.<br>(See DAC Specification for complete descrip-<br>tion).                                                                                                               |

| P0.0           | 62                               | 55     | 62             | 55             | D I/O         | Port 0.0. See Port Input/Output section for complete description.                                                                                                                                                     |

| P0.1           | 61                               | 54     | 61             | 54             | D I/O         | Port 0.1. See Port Input/Output section for complete description.                                                                                                                                                     |

| P0.2           | 60                               | 53     | 60             | 53             | D I/O         | Port 0.2. See Port Input/Output section for complete description.                                                                                                                                                     |

| P0.3           | 59                               | 52     | 59             | 52             | D I/O         | Port 0.3. See Port Input/Output section for complete description.                                                                                                                                                     |

| P0.4           | 58                               | 51     | 58             | 51             | D I/O         | Port 0.4. See Port Input/Output section for complete description.                                                                                                                                                     |

| ALE/P0.5       | 57                               | 50     | 57             | 50             | D I/O         | ALE Strobe for External Memory Address bus<br>(multiplexed mode)<br>Port 0.5<br>See Port Input/Output section for complete<br>description.                                                                            |

| RD/P0.6        | 56                               | 49     | 56             | 49             | D I/O         | /RD Strobe for External Memory Address bus<br>Port 0.6<br>See Port Input/Output section for complete<br>description.                                                                                                  |

| WR/P0.7        | 55                               | 48     | 55             | 48             | D I/O         | /WR Strobe for External Memory Address bus<br>Port 0.7<br>See Port Input/Output section for complete<br>description.                                                                                                  |

| AIN2.0/A8/P1.0 | 36                               | 29     | 36             | 29             | A In<br>D I/O | ADC2 Input Channel 0 (See ADC2 Specification<br>for complete description).<br>Bit 8 External Memory Address bus (Non-multi-<br>plexed mode)<br>Port 1.0<br>See Port Input/Output section for complete<br>description. |

| AIN2.1/A9/P1.1 | 35                               | 28     | 35             | 28             | A In<br>D I/O | Port 1.1. See Port Input/Output section for complete description.                                                                                                                                                     |

Table 4.1. Pin Definitions (Continued)

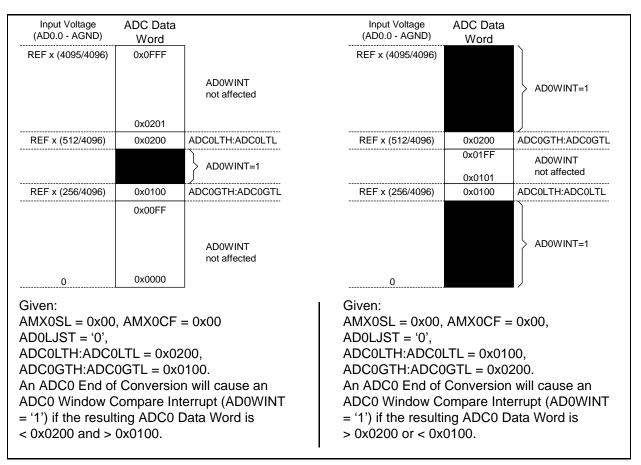

Figure 5.6. 12-Bit ADC0 Window Interrupt Example: Right Justified Single-Ended Data

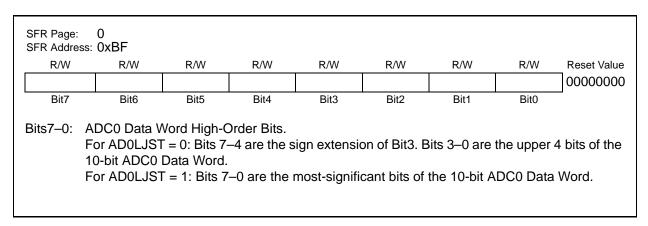

# SFR Definition 6.5. ADC0H: ADC0 Data Word MSB

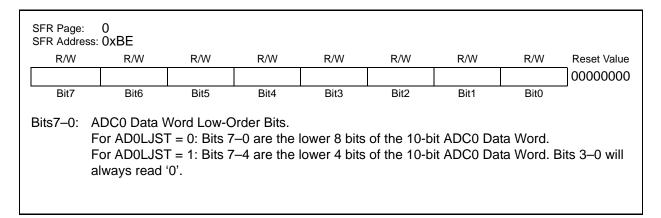

# SFR Definition 6.6. ADC0L: ADC0 Data Word LSB

| R/W      | R/W           | R/W             | R/W          | R/W            | R/W           | R/W            | R/W        | Reset Value |

|----------|---------------|-----------------|--------------|----------------|---------------|----------------|------------|-------------|

| -        | -             | -               | -            | PIN67IC        | PIN45IC       | PIN23IC        | PIN01IC    | 00000000    |

| Bit7     | Bit6          | Bit5            | Bit4         | Bit3           | Bit2          | Bit1           | Bit0       | -           |

| Bits7–4: | UNUSED. Re    | $e_{ad} = 0000$ | o: Write = d | on't care      |               |                |            |             |

| Bit3:    | PIN67IC: AIN  |                 |              |                | on Bit        |                |            |             |

| Dito.    | 0: AIN2.6 and |                 |              | •              |               | i              |            |             |

|          | 1: AIN2.6 and |                 |              | •              |               |                |            |             |

| Bit2:    | PIN45IC: AIN  |                 | · ·          | • • •          |               |                |            |             |

|          | 0: AIN2.4 and |                 |              | •              |               |                |            |             |

|          | 1: AIN2.4 and |                 |              | •              |               |                |            |             |

| Bit1:    | PIN23IC: AIN  |                 |              |                |               | •              |            |             |

|          | 0: AIN2.2 and |                 |              |                |               |                |            |             |

|          | 1: AIN2.2 and | d AIN2.3 ar     | e (respectiv | ely) +, – dif  | ferential inp | ut pair.       |            |             |

| Bit0:    | PIN01IC: AIN  | 2.0, AIN2.1     | I Input Pair | Configuratio   | on Bit.       |                |            |             |

|          | 0: AIN2.0 and | d AIN2.1 ar     | e independe  | ent single-e   | nded inputs   |                |            |             |

|          | 1: AIN2.0 and | d AIN2.1 ar     | e (respectiv | rely) +, – dif | ferential inp | ut pair.       |            |             |

|          |               |                 |              |                |               |                |            |             |

| Note: T  | he ADC2 Data  | Word is in 2'e  | s complemen  | t format for c | hannels con   | figured as dif | fferential |             |

## SFR Definition 7.1. AMX2CF: AMUX2 Configuration

| SFR Page: | 2                                                                                                  |  |  |  |  |  |  |  |  |  |

|-----------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| SFR Addre |                                                                                                    |  |  |  |  |  |  |  |  |  |

| R/W       | R/W R/W R/W R/W R/W R/W R/W Reset Value                                                            |  |  |  |  |  |  |  |  |  |

| AD2EN     | AD2TM AD2INT AD2BUSY AD2CM2 AD2CM1 AD2CM0 AD2WINT 00000000                                         |  |  |  |  |  |  |  |  |  |

| Bit7      | Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0                                                                 |  |  |  |  |  |  |  |  |  |

| Bit7:     | AD2EN: ADC2 Enable Bit.                                                                            |  |  |  |  |  |  |  |  |  |

|           | 0: ADC2 Disabled. ADC2 is in low-power shutdown.                                                   |  |  |  |  |  |  |  |  |  |

|           | 1: ADC2 Enabled. ADC2 is active and ready for data conversions.                                    |  |  |  |  |  |  |  |  |  |

| Bit6:     | AD2TM: ADC2 Track Mode Bit.                                                                        |  |  |  |  |  |  |  |  |  |

|           | 0: Normal Track Mode: When ADC2 is enabled, tracking is continuous unless a conversion             |  |  |  |  |  |  |  |  |  |

|           | is in process.                                                                                     |  |  |  |  |  |  |  |  |  |

|           | 1: Low-power Track Mode: Tracking Defined by AD2CM2-0 bits (see below).                            |  |  |  |  |  |  |  |  |  |

| Bit5:     | AD2INT: ADC2 Conversion Complete Interrupt Flag.                                                   |  |  |  |  |  |  |  |  |  |

|           | This flag must be cleared by software.                                                             |  |  |  |  |  |  |  |  |  |

|           | 0: ADC2 has not completed a data conversion since the last time this flag was cleared.             |  |  |  |  |  |  |  |  |  |

| Bit4:     | 1: ADC2 has completed a data conversion.<br>AD2BUSY: ADC2 Busy Bit.                                |  |  |  |  |  |  |  |  |  |

| DIL4.     | Read:                                                                                              |  |  |  |  |  |  |  |  |  |

|           | 0: ADC2 Conversion is complete or a conversion is not currently in progress. AD2INT is set         |  |  |  |  |  |  |  |  |  |

|           | to logic 1 on the falling edge of AD2BUSY.                                                         |  |  |  |  |  |  |  |  |  |

|           | 1: ADC2 Conversion is in progress.                                                                 |  |  |  |  |  |  |  |  |  |

|           | Write:                                                                                             |  |  |  |  |  |  |  |  |  |

|           | 0: No Effect.                                                                                      |  |  |  |  |  |  |  |  |  |

|           | 1: Initiates ADC2 Conversion if AD2CM2-0 = 000b                                                    |  |  |  |  |  |  |  |  |  |

| Bits3–1:  | AD2CM2–0: ADC2 Start of Conversion Mode Select.                                                    |  |  |  |  |  |  |  |  |  |

|           | AD2TM = 0:                                                                                         |  |  |  |  |  |  |  |  |  |

|           | 000: ADC2 conversion initiated on every write of '1' to AD2BUSY.                                   |  |  |  |  |  |  |  |  |  |

|           | 001: ADC2 conversion initiated on overflow of Timer 3.                                             |  |  |  |  |  |  |  |  |  |

|           | 010: ADC2 conversion initiated on rising edge of external CNVSTR2.                                 |  |  |  |  |  |  |  |  |  |

|           | 011: ADC2 conversion initiated on overflow of Timer 2.                                             |  |  |  |  |  |  |  |  |  |

|           | 1xx: ADC2 conversion initiated on write of '1' to AD0BUSY (synchronized with ADC0 soft-            |  |  |  |  |  |  |  |  |  |

|           | ware-commanded conversions).                                                                       |  |  |  |  |  |  |  |  |  |

|           | AD2TM = 1:                                                                                         |  |  |  |  |  |  |  |  |  |

|           | 000: Tracking initiated on write of '1' to AD2BUSY for 3 SAR2 clocks, followed by conver-          |  |  |  |  |  |  |  |  |  |

|           | sion.<br>001: Tracking initiated on overflow of Timer 3 for 3 SAR2 clocks, followed by conversion. |  |  |  |  |  |  |  |  |  |

|           | 010: ADC2 tracks only when CNVSTR2 input is logic low; conversion starts on rising                 |  |  |  |  |  |  |  |  |  |

|           | CNVSTR2 edge.                                                                                      |  |  |  |  |  |  |  |  |  |

|           | 011: Tracking initiated on overflow of Timer 2 for 3 SAR2 clocks, followed by conversion.          |  |  |  |  |  |  |  |  |  |

|           | 1xx: Tracking initiated on write of '1' to AD0BUSY and lasts 3 SAR2 clocks, followed by con-       |  |  |  |  |  |  |  |  |  |

|           | version.                                                                                           |  |  |  |  |  |  |  |  |  |

| Bit0:     | AD2WINT: ADC2 Window Compare Interrupt Flag.                                                       |  |  |  |  |  |  |  |  |  |

|           | This bit must be cleared by software.                                                              |  |  |  |  |  |  |  |  |  |

|           | 0: ADC2 Window Comparison Data match has not occurred since this flag was last cleared.            |  |  |  |  |  |  |  |  |  |

|           | 1: ADC2 Window Comparison Data match has occurred.                                                 |  |  |  |  |  |  |  |  |  |

# SFR Definition 7.4. ADC2CN: ADC2 Control

|          |                                                       | SFR Det                                                                                         | finition 8.                     | 3. DAC0C                          | N: DAC0     | Control             |                                              |             |

|----------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------|-------------|---------------------|----------------------------------------------|-------------|

| R/W      | R/W                                                   | R/W                                                                                             | R/W                             | R/W                               | R/W         | R/W                 | R/W                                          | Reset Valu  |

| DAC0EN   | - ۱                                                   | -                                                                                               | DAC0MD'                         | 1 DAC0MD0                         | DAC0DF2     | DAC0DF1             | DAC0DF0                                      | 0000000     |

| Bit7     | Bit6                                                  | Bit5                                                                                            | Bit4                            | Bit3                              | Bit2        | Bit1                | Bit0                                         | ,           |

|          |                                                       |                                                                                                 |                                 |                                   |             |                     | SFR Address:<br>SFR Page:                    | -           |

| Bit7:    |                                                       | isabled. DA                                                                                     | C0 Output p                     | oin is disable<br>in is active; [ |             |                     | er shutdowr                                  | n mode.     |

| Bits6–5: |                                                       |                                                                                                 | ; Write = do                    |                                   |             |                     |                                              |             |

| Bits4–3: |                                                       |                                                                                                 |                                 |                                   |             |                     |                                              |             |

|          | 00: DAC ou                                            | utput update                                                                                    | es occur on                     | a write to DA                     | C0H.        |                     |                                              |             |

|          | 01: DAC ou                                            | utput update                                                                                    | es occur on                     | Timer 3 over                      | flow.       |                     |                                              |             |

|          | 10: DAC οι                                            | utput update                                                                                    | es occur on                     | Timer 4 over                      | flow.       |                     |                                              |             |

|          | 11: DAC ou                                            | itput update                                                                                    | es occur on                     | Timer 2 over                      | flow.       |                     |                                              |             |

| Bits2–0: | DAC0DF2-                                              | -0: DAC0 D                                                                                      | ata Format                      | Bits:                             |             |                     |                                              |             |

|          |                                                       | -                                                                                               | ificant nibble<br>e is in DAC0  | e of the DAC                      | 0 Data Word | d is in DAC         | 0H[3:0], wh                                  | ile the lea |

|          |                                                       | DAC0H                                                                                           |                                 |                                   | L           |                     |                                              |             |

|          |                                                       | MSB                                                                                             |                                 |                                   |             |                     |                                              | LSE         |

|          | sig                                                   | -                                                                                               | its are in DA                   | s of the DAC(<br>COL[7:1].        |             | DAC                 |                                              |             |

|          | N                                                     | ISB                                                                                             |                                 | Ī                                 |             |                     |                                              | LSB         |

|          | 010: The                                              | e most sian                                                                                     | ificant 6-bits                  | s of the DAC                      | ) Data Word | d is in DAC         | 0H[5:0], wh                                  | ile the lea |

|          |                                                       |                                                                                                 | its are in DA                   | C0L[7:2].                         |             |                     |                                              |             |

|          |                                                       |                                                                                                 | its are in DA                   | C0L[7:2].                         |             | DAC0                | L                                            |             |

|          |                                                       | nificant 6-bi                                                                                   | its are in DA                   | C0L[7:2].                         |             | DACO                | L<br>LSB                                     |             |

|          | Sig<br>MSB<br>011: The                                | nificant 6-bi<br>DAC0H                                                                          | ificant 7-bits                  | s of the DAC                      | ) Data Word |                     | LSB                                          |             |

|          | Sig<br>MSB<br>011: The                                | nificant 6-bi<br>DAC0H                                                                          |                                 | s of the DAC                      | ) Data Word |                     | LSB<br>0H[6:0], wh                           |             |

|          | Sig<br>MSB<br>011: The                                | nificant 6-bi<br>DACOH                                                                          | ificant 7-bits                  | s of the DAC                      | ) Data Word | d is in DAC         | LSB<br>0H[6:0], wh                           |             |

| M        | sig<br>MSB  <br>011: The<br>sig<br>SB    <br>1xx: The | nificant 6-bi<br>DACOH<br>e most sign<br>nificant 5-bi<br>DACOH<br>e most sign                  | ificant 7-bits<br>its are in DA | s of the DAC(<br>COL[7:3].        |             | d is in DAC DAC0    | LSB<br>0H[6:0], wh<br>L<br>SB                | ile the lea |

| M        | SB   1xx: The sig                                     | nificant 6-bi<br>DACOH<br>e most sign<br>nificant 5-bi<br>DACOH<br>e most sign                  | ificant 7-bits<br>its are in DA | s of the DAC(<br>COL[7:3].        |             | d is in DAC<br>DACO | LSB<br>0H[6:0], wh<br>L<br>SB<br>0H[7:0], wh | ile the lea |

|          | SB   1xx: The sig                                     | nificant 6-bi<br>DACOH<br>e most sign<br>nificant 5-bi<br>DACOH<br>e most sign<br>nificant 4-bi | ificant 7-bits<br>its are in DA | s of the DAC(<br>COL[7:3].        |             | d is in DAC<br>DACO | LSB<br>0H[6:0], wh<br>L<br>SB<br>0H[7:0], wh | ile the lea |

| MSB      | SB   1xx: The sig                                     | nificant 6-bi<br>DACOH<br>e most sign<br>nificant 5-bi<br>DACOH<br>e most sign<br>nificant 4-bi | ificant 7-bits<br>its are in DA | s of the DAC(<br>COL[7:3].        |             | d is in DAC<br>DACO | LSB<br>0H[6:0], wh<br>L<br>SB<br>0H[7:0], wh | ile the lea |

|          | SB   1xx: The sig                                     | nificant 6-bi<br>DACOH<br>e most sign<br>nificant 5-bi<br>DACOH<br>e most sign<br>nificant 4-bi | ificant 7-bits<br>its are in DA | s of the DAC(<br>COL[7:3].        |             | d is in DAC<br>DACO | LSB<br>0H[6:0], wh<br>L<br>SB<br>0H[7:0], wh | ile the lea |

# Table 11.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

| Register                                | Address | SFR<br>Page             | Description                   | Page No.                |

|-----------------------------------------|---------|-------------------------|-------------------------------|-------------------------|

|                                         |         |                         |                               | page 114 <sup>5</sup> , |

| REF0CN 0xD1 0 Voltage Reference Control |         | page 116 <sup>6</sup> , |                               |                         |

|                                         |         |                         |                               | page 117 <sup>7</sup>   |

| RSTSRC                                  | 0xEF    | 0                       | Reset Source                  | page 182                |

| SADDR0                                  | 0xA9    | 0                       | UART 0 Slave Address          | page 298                |

| SADEN0                                  | 0xB9    | 0                       | UART 0 Slave Address Mask     | page 298                |

| SBUF0                                   | 0x99    | 0                       | UART 0 Data Buffer            | page 298                |

| SBUF1                                   | 0x99    | 1                       | UART 1 Data Buffer            | page 305                |

| SCON0                                   | 0x98    | 0                       | UART 0 Control                | page 296                |

| SCON1                                   | 0x98    | 1                       | UART 1 Control                | page 304                |

| SFRLAST                                 | 0x86    | All Pages               | SFR Stack Last Page           | page 143                |

| SFRNEXT                                 | 0x85    |                         | SFR Stack Next Page           | page 143                |

| SFRPAGE                                 | 0x84    |                         | SFR Page Select               | page 142                |

| SFRPGCN                                 | 0x96    | F                       | SFR Page Control              | page 142                |

| SMB0ADR                                 | 0xC3    | 0                       | SMBus Slave Address           | page 269                |

| SMB0CN                                  | 0xC0    | 0                       | SMBus Control                 | page 266                |

| SMB0CR                                  | 0xCF    | 0                       | SMBus Clock Rate              | page 267                |

| SMB0DAT                                 | 0xC2    | 0                       | SMBus Data                    | page 268                |

| SMB0STA                                 | 0xC1    | 0                       | SMBus Status                  | page 269                |

| SP                                      | 0x81    | All Pages               | Stack Pointer                 | page 151                |

| SPI0CFG                                 | 0x9A    | 0                       | SPI Configuration             | page 280                |

| SPI0CKR                                 | 0x9D    | 0                       | SPI Clock Rate Control        | page 282                |

| SPI0CN                                  | 0xF8    | 0                       | SPI Control                   | page 281                |

| SPIODAT                                 | 0x9B    | 0                       | SPI Data                      | page 282                |

| SSTA0                                   | 0x91    | 0                       | UART 0 Status                 | page 297                |

| TCON                                    | 0x88    | 0                       | Timer/Counter Control         | page 313                |

| TH0                                     | 0x8C    | 0                       | Timer/Counter 0 High Byte     | page 316                |

| TH1                                     | 0x8D    | 0                       | Timer/Counter 1 High Byte     | page 316                |

| TL0                                     | 0x8A    | 0                       | Timer/Counter 0 Low Byte      | page 315                |

| TL1                                     | 0x8B    | 0                       | Timer/Counter 1 Low Byte      | page 316                |

| TMOD                                    | 0x89    | 0                       | Timer/Counter Mode            | page 314                |

| TMR2CF                                  | 0xC9    | 0                       | Timer/Counter 2 Configuration | page 324                |

| TMR2CN                                  | 0xC8    | 0                       | Timer/Counter 2 Control       | page 324                |

| TMR2H                                   | 0xCD    | 0                       | Timer/Counter 2 High Byte     | page 324                |

| TMR2L                                   | 0xCC    | 0                       | Timer/Counter 2 Low Byte      | page 323                |

| TMR3CF                                  | 0xC9    | 1                       | Timer 3 Configuration         | page 324                |

| TMR3CN                                  | 0xC8    | 1                       | Timer 3 Control               | page 324                |

| TMR3H                                   | 0xCD    | 1                       | Timer 3 High Byte             | page 324                |

| TMR3L                                   | 0xCC    | 1                       | Timer 3 Low Byte              | page 323                |

| TMR4CF                                  | 0xC9    | 2                       | Timer/Counter 4 Configuration | page 324                |

| TMR4CN                                  | 0xC8    | 2                       | Timer/Counter 4 Control       | page 324                |

| TMR4H                                   | 0xCD    | 2                       | Timer/Counter 4 High Byte     | page 324                |

| Interrupt Source         | Interru<br>pt<br>Vector | Priority<br>Order | Pending Flags                     | Bit addressable? | Cleared by HW? | SFRPAGE (SFRPGEN = 1) | Enable<br>Flag     | Priority<br>Control |

|--------------------------|-------------------------|-------------------|-----------------------------------|------------------|----------------|-----------------------|--------------------|---------------------|

| Comparator 1 Rising Edge | 0x006B                  | 13                | CP1RIF (CPT1CN.5)                 | Y                |                | 2                     | ECP1R<br>(EIE1.7)  | PCP1F<br>(EIP1.7)   |

| Timer 3                  | 0x0073                  | 14                | TF3 (TMR3CN.7)<br>EXF3 (TMR3CN.6) | Y                | Y              |                       | ET3<br>(EIE2.0)    | PT3<br>(EIP2.0)     |

| ADC0 End of Conversion   | 0x007B                  | 15                | AD0INT (ADC0CN.5)                 | Y                |                | 0                     | EADC0<br>(EIE2.1)  | PADC0<br>(EIP2.1)   |

| Timer 4                  | 0x0083                  | 16                | TF4 (TMR4CN.7)<br>EXF4 (TMR4CN.7) | Y                |                | 2                     | ET4<br>(EIE2.2)    | PT4<br>(EIP2.2)     |

| ADC2 Window Comparator   | 0x008B                  | 17                | AD2WINT<br>(ADC2CN.0)             | Y                |                | 2                     | EWADC2<br>(EIE2.3) | PWADC2<br>(EIP2.3)  |

| ADC2 End of Conversion   | 0x0093                  | 18                | AD2INT (ADC2CN.5)                 | Y                |                | 2                     | EADC2<br>(EIE2.4)  | PADC2<br>(EIP2.4)   |

| RESERVED                 | 0x009B                  | 19                | N/A                               | N/A              | N/A            | N/A                   | N/A                | N/A                 |

| UART1                    | 0x00A3                  | 20                | RI1 (SCON1.0)<br>TI1 (SCON1.1)    | Y                |                | 1                     | ES1<br>(EIE2.6)    | PS1<br>(EIP2.6)     |

# Table 11.4. Interrupt Summary (Continued)

### 11.3.3. Interrupt Priorities

Each interrupt source can be individually programmed to one of two priority levels: low or high. A low priority interrupt service routine can be preempted by a high priority interrupt. A high priority interrupt cannot be preempted. Each interrupt has an associated interrupt priority bit in an SFR (IP-EIP2) used to configure its priority level. Low priority is the default. If two interrupts are recognized simultaneously, the interrupt with the higher priority is serviced first. If both interrupts have the same priority level, a fixed priority order is used to arbitrate, given in Table 11.4.

### 11.3.4. Interrupt Latency

Interrupt response time depends on the state of the CPU when the interrupt occurs. Pending interrupts are sampled and priority decoded each system clock cycle. Therefore, the fastest possible response time is 5 system clock cycles: 1 clock cycle to detect the interrupt and 4 clock cycles to complete the LCALL to the ISR. Additional clock cycles will be required if a cache miss occurs (see **Section "16. Branch Target Cache" on page 211** for more details). If an interrupt is pending when a RETI is executed, a single instruction is executed before an LCALL is made to service the pending interrupt. Therefore, the maximum response time for an interrupt (when no other interrupt is currently being serviced or the new interrupt is of greater priority) is when the CPU is performing an RETI instruction followed by a DIV as the next instruction, and a cache miss event also occurs. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the RETI and following instruction.

### 11.4. Power Management Modes

The CIP-51 core has two software programmable power management modes: Idle and Stop. Idle mode halts the CPU while leaving the external peripherals and internal clocks active. In Stop mode, the CPU is halted, all interrupts and timers (except the Missing Clock Detector) are inactive, and the system clock is stopped. Since clocks are running in Idle mode, power consumption is dependent upon the system clock frequency and the number of peripherals left in active mode before entering Idle. Stop mode consumes the least power. SFR Definition 11.18 describes the Power Control Register (PCON) used to control the CIP-51's power management modes.

Although the CIP-51 has Idle and Stop modes built in (as with any standard 8051 architecture), power management of the entire MCU is better accomplished by enabling/disabling individual peripherals as needed. Each analog peripheral can be disabled when not in use and put into low power mode. Digital peripherals, such as timers or serial buses, draw little power whenever they are not in use. Turning off the Flash memory saves power, similar to entering Idle mode. Turning off the oscillator saves even more power, but requires a reset to restart the MCU.

#### 11.4.1. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

Idle mode is terminated when an enabled interrupt or  $\overrightarrow{\mathsf{RST}}$  is asserted. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x00000.

If enabled, the WDT will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the Idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to **Section 13** for more information on the use and configuration of the WDT.

Note: Any instruction which sets the IDLE bit should be immediately followed by an instruction which has two or more opcode bytes. For example:

// in `C':

PCON |= 0x01; // Set IDLE bit

PCON = PCON; // ... Followed by a 3-cycle Dummy Instruction

; in assembly:

ORL PCON, #01h ; Set IDLE bit

MOV PCON, PCON ; ... Followed by a 3-cycle Dummy Instruction

If the instruction following the write to the IDLE bit is a single-byte instruction and an interrupt occurs during the execution of the instruction of the instruction which sets the IDLE bit, the CPU may not wake from IDLE mode when a future interrupt occurs.

### 13.3. External Reset

The external RST pin provides a means for external circuitry to force the MCU into a reset state. Asserting the RST pin low will cause the MCU to enter the reset state. It may be desirable to provide an external pullup and/or decoupling of the RST pin to avoid erroneous noise-induced resets. The MCU will remain in reset until at least 12 clock cycles after the active-low RST signal is removed. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

### 13.4. Missing Clock Detector Reset

The Missing Clock Detector is essentially a one-shot circuit that is triggered by the MCU system clock. If the system clock goes away for more than 100  $\mu$ s, the one-shot will time out and generate a reset. After a Missing Clock Detector reset, the MCDRSF flag (RSTSRC.2) will be set, signifying the MSD as the reset source; otherwise, this bit reads '0'. The state of the RST pin is unaffected by this reset. Setting the MCDRSF bit, RSTSRC.2 (see Section "14. Oscillators" on page 185) enables the Missing Clock Detector.

### 13.5. Comparator0 Reset

Comparator0 can be configured as a reset input by writing a '1' to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled using CPT0CN.7 (see Section "**10. Comparators**" on page **119**) prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (CP0+ pin) is less than the inverting input voltage (CP0- pin), the MCU is put into the reset state. After a Comparator0 Reset, the CORSEF flag (RSTSRC.5) will read '1' signifying Comparator0 as the reset source; otherwise, this bit reads '0'. The state of the RST pin is unaffected by this reset.

### 13.6. External CNVSTR0 Pin Reset

The external CNVSTR0 signal can be configured as a reset input by writing a '1' to the CNVRSEF flag (RSTSRC.6). The CNVSTR0 signal can appear on any of the P0, P1, P2 or P3 I/O pins as described in Section "**18.1. Ports 0 through 3 and the Priority Crossbar Decoder**" on page **238**. Note that the Crossbar must be configured for the CNVSTR0 signal to be routed to the appropriate Port I/O. The Crossbar should be configured and enabled before the CNVRSEF is set. When configured as a reset, CNVSTR0 is active-low and level sensitive. CNVSTR0 cannot be used to start ADC0 conversions when it is configured as a reset source. After a CNVSTR0 reset, the CNVRSEF flag (RSTSRC.6) will read '1' signifying CNVSTR0 as the reset source; otherwise, this bit reads '0'. The state of the /RST pin is unaffected by this reset.

### 13.7. Watchdog Timer Reset

The MCU includes a programmable Watchdog Timer (WDT) running off the system clock. A WDT overflow will force the MCU into the reset state. To prevent the reset, the WDT must be restarted by application software before overflow. If the system experiences a software or hardware malfunction preventing the software from restarting the WDT, the WDT will overflow and cause a reset. This should prevent the system from running out of control.

Following a reset the WDT is automatically enabled and running with the default maximum time interval. If desired the WDT can be disabled by system software or locked on to prevent accidental disabling. Once locked, the WDT cannot be disabled until the next system reset. The state of the RST pin is unaffected by this reset.

The WDT consists of a 21-bit timer running from the programmed system clock. The timer measures the period between specific writes to its control register. If this period exceeds the programmed limit, a WDT

Electrical specifications for the precision internal oscillator are given in Table 14.1. Note that the system clock may be derived from the programmed internal oscillator divided by 1, 2, 4, or 8, as defined by the IFCN bits in register OSCICN.

# SFR Definition 14.1. OSCICL: Internal Oscillator Calibration.

# SFR Definition 14.2. OSCICN: Internal Oscillator Control

| R/W       | R                                                                                                                     | R/W           | R           | R/W         | R/W   | R/W   | R/W                       | Reset Value |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------|---------------|-------------|-------------|-------|-------|---------------------------|-------------|--|--|--|

| IOSCEN    | I IFRDY                                                                                                               | -             | -           | -           | -     | IFCN1 | IFCN0                     | 11000000    |  |  |  |

| Bit7      | Bit6                                                                                                                  | Bit5          | Bit4        | Bit3        | Bit2  | Bit1  | Bit0                      | -           |  |  |  |

|           |                                                                                                                       |               |             |             |       |       | SFR Address:<br>SFR Page: |             |  |  |  |

| Bit 7:    | Bit 7: IOSCEN: Internal Oscillator Enable Bit.<br>0: Internal Oscillator Disabled.<br>1: Internal Oscillator Enabled. |               |             |             |       |       |                           |             |  |  |  |

| Bit 6:    |                                                                                                                       |               |             |             |       |       |                           |             |  |  |  |

| Bits 5-2: | Reserved.                                                                                                             |               |             | -           |       |       |                           |             |  |  |  |

| Bits 1–0: | IFCN1-0: Int                                                                                                          | ernal Oscilla | ator Freque | ncy Control | Bits. |       |                           |             |  |  |  |

|           | 00: Internal (                                                                                                        | Oscillator is | divided by  | 8.          |       |       |                           |             |  |  |  |

|           | 01: Internal (                                                                                                        | Oscillator is | divided by  | 4.          |       |       |                           |             |  |  |  |

|           | 10: Internal (                                                                                                        | Oscillator is | divided by  | 2.          |       |       |                           |             |  |  |  |

|           | 11: Internal (                                                                                                        | Oscillator is | divided by  | 1.          |       |       |                           |             |  |  |  |

# 14.2. External Oscillator Drive Circuit

The external oscillator circuit may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. For a crystal or ceramic resonator configuration, the crystal/ resonator must be wired across the XTAL1 and XTAL2 pins as shown in Option 1 of Figure 14.1. In RC, capacitor, or CMOS clock configuration, the clock source should be wired to the XTAL2 and/or XTAL1 pin(s) as shown in Option 2, 3, or 4 of Figure 14.1. The type of external oscillator must be selected in the OSCXCN register, and the frequency control bits (XFCN) must be selected appropriately (see SFR Definition 14.4).

# 14.3. System Clock Selection

The CLKSL1-0 bits in register CLKSEL select which oscillator source generates the system clock. CLK-SL1-0 must be set to '01' for the system clock to run from the external oscillator; however the external oscillator may still clock certain peripherals, such as the timers and PCA, when the internal oscillator or the PLL is selected as the system clock. The system clock may be switched on-the-fly between the internal and external oscillators or the PLL, so long as the selected oscillator source is enabled and settled. The internal oscillator requires little start-up time, and may be enabled and selected as the system clock in the same write to OSCICN. External crystals and ceramic resonators typically require a start-up time before they are settled and ready for use as the system clock. The Crystal Valid Flag (XTLVLD in register OSCXCN) is set to '1' by hardware when the external oscillator is settled. To avoid reading a false XTLVLD, in crystal mode software should delay at least 1 ms between enabling the external oscillator and checking XTLVLD. RC and C modes typically require no startup time. The PLL also requires time to lock onto the desired frequency, and the PLL Lock Flag (PLLLCK in register PLL0CN) is set to '1' by hardware once the PLL is locked on the correct frequency.

#### 15.2.1. Summary of Flash Security Options

There are three Flash access methods supported on the C8051F12x and C8051F13x devices; 1) Accessing Flash through the JTAG debug interface, 2) Accessing Flash from firmware residing below the Flash Access Limit, and 3) Accessing Flash from firmware residing at or above the Flash Access Limit.

#### Accessing Flash through the JTAG debug interface:

- 1. The Read and Write/Erase Lock bytes (security bytes) provide security for Flash access through the JTAG interface.

- 2. Any unlocked page may be read from, written to, or erased.

- 3. Locked pages cannot be read from, written to, or erased.

- 4. Reading the security bytes is always permitted.

- 5. Locking additional pages by writing to the security bytes is always permitted.

- 6. If the page containing the security bytes is **unlocked**, it can be directly erased. **Doing so will** reset the security bytes and unlock all pages of Flash.

- 7. If the page containing the security bytes is **locked**, it cannot be directly erased. **To unlock the page containing the security bytes**, a **full JTAG device erase is required**. A full JTAG device erase will erase all Flash pages, including the page containing the security bytes and the security bytes themselves.

- 8. The Reserved Area cannot be read from, written to, or erased at any time.

#### Accessing Flash from firmware residing below the Flash Access Limit:

- 1. The Read and Write/Erase Lock bytes (security bytes) do not restrict Flash access from user firmware.

- 2. Any page of Flash except the page containing the security bytes may be read from, written to, or erased.

- 3. The page containing the security bytes cannot be erased. Unlocking pages of Flash can only be performed via the JTAG interface.

- 4. The page containing the security bytes may be read from or written to. Pages of Flash can be locked from JTAG access by writing to the security bytes.

- 5. The Reserved Area cannot be read from, written to, or erased at any time.

#### Accessing Flash from firmware residing at or above the Flash Access Limit:

- 1. The Read and Write/Erase Lock bytes (security bytes) do not restrict Flash access from user firmware.

- 2. Any page of Flash at or above the Flash Access Limit except the page containing the security bytes may be read from, written to, or erased.

- 3. Any page of Flash below the Flash Access Limit cannot be read from, written to, or erased.

- 4. Code branches to locations below the Flash Access Limit are permitted.

- 5. **The page containing the security bytes cannot be erased.** Unlocking pages of Flash can only be performed via the JTAG interface.

- 6. The page containing the security bytes may be read from or written to. Pages of Flash can be locked from JTAG access by writing to the security bytes.

- 7. The Reserved Area cannot be read from, written to, or erased at any time.

| Parameter                    | Description                                                                           | Min                     | Max                      | Units |  |  |  |  |

|------------------------------|---------------------------------------------------------------------------------------|-------------------------|--------------------------|-------|--|--|--|--|

| T <sub>ACS</sub>             | Address/Control Setup Time                                                            | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |  |  |  |  |

| T <sub>ACW</sub>             | Address/Control Pulse Width                                                           | 1 x T <sub>SYSCLK</sub> | 16 x T <sub>SYSCLK</sub> | ns    |  |  |  |  |

| T <sub>ACH</sub>             | Address/Control Hold Time                                                             | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |  |  |  |  |

| T <sub>ALEH</sub>            | Address Latch Enable High Time                                                        | 1 x T <sub>SYSCLK</sub> | 4 x T <sub>SYSCLK</sub>  | ns    |  |  |  |  |

| T <sub>ALEL</sub>            | Address Latch Enable Low Time                                                         | 1 x T <sub>SYSCLK</sub> | 4 x T <sub>SYSCLK</sub>  | ns    |  |  |  |  |

| T <sub>WDS</sub>             | Write Data Setup Time                                                                 | 1 x T <sub>SYSCLK</sub> | 19 x T <sub>SYSCLK</sub> | ns    |  |  |  |  |

| T <sub>WDH</sub>             | Write Data Hold Time                                                                  | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |  |  |  |  |

| T <sub>RDS</sub>             | Read Data Setup Time                                                                  | 20                      | _                        | ns    |  |  |  |  |

| T <sub>RDH</sub>             | Read Data Hold Time                                                                   | 0                       | —                        | ns    |  |  |  |  |

| lote: T <sub>SYSCLK</sub> is | lote: T <sub>SYSCLK</sub> is equal to one period of the device system clock (SYSCLK). |                         |                          |       |  |  |  |  |

### Table 17.1. AC Parameters for External Memory Interface

The PnMDOUT registers control the output modes of the port pins regardless of whether the Crossbar has allocated the Port pin for a digital peripheral or not. The exceptions to this rule are: the Port pins connected to SDA, SCL, RX0 (if UART0 is in Mode 0), and RX1 (if UART1 is in Mode 0) are always configured as Open-Drain outputs, regardless of the settings of the associated bits in the PnMDOUT registers.

### 18.1.3. Configuring Port Pins as Digital Inputs

A Port pin is configured as a digital input by setting its output mode to "Open-Drain" and writing a logic 1 to the associated bit in the Port Data register. For example, P3.7 is configured as a digital input by setting P3MDOUT.7 to a logic 0 and P3.7 to a logic 1.

If the Port pin has been assigned to a digital peripheral by the Crossbar and that pin functions as an input (for example RX0, the UART0 receive pin), then the output drivers on that pin are automatically disabled.

### 18.1.4. Weak Pullups

By default, each Port pin has an internal weak pullup device enabled which provides a resistive connection (about 100 k $\Omega$ ) between the pin and V<sub>DD</sub>. The weak pullup devices can be globally disabled by writing a logic 1 to the Weak Pullup Disable bit, (WEAKPUD, XBR2.7). The weak pullup is automatically deactivated on any pin that is driving a logic 0; that is, an output pin will not contend with its own pullup device. The weak pullup device can also be explicitly disabled on any Port 1 pin by configuring the pin as an Analog Input, as described below.

### 18.1.5. Configuring Port 1 Pins as Analog Inputs

The pins on Port 1 can serve as analog inputs to the ADC2 analog MUX on the C8051F12x devices. A Port pin is configured as an Analog Input by writing a logic 0 to the associated bit in the PnMDIN registers. All Port pins default to a Digital Input mode. Configuring a Port pin as an analog input:

- Disables the digital input path from the pin. This prevents additional power supply current from being drawn when the voltage at the pin is near V<sub>DD</sub> / 2. A read of the Port Data bit will return a logic 0 regardless of the voltage at the Port pin.

- 2. Disables the weak pullup device on the pin.

- 3. Causes the Crossbar to "skip over" the pin when allocating Port pins for digital peripherals.

Note that the output drivers on a pin configured as an Analog Input are not explicitly disabled. Therefore, the associated P1MDOUT bits of pins configured as Analog Inputs should explicitly be set to logic 0 (Open-Drain output mode), and the associated Port1 Data bits should be set to logic 1 (high-impedance). Also note that it is not required to configure a Port pin as an Analog Input in order to use it as an input to ADC2, however, it is strongly recommended. See the ADC2 section in this datasheet for further information.

| R/W                                                                                                                                                                                                                                                                                                          | R/W                                                                                                                                                                                           | R/W  | R/W  | R/W  | R/W  | R/W             | R/W  | Reset Value |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-----------------|------|-------------|--|--|--|

| SLV6                                                                                                                                                                                                                                                                                                         | SLV5                                                                                                                                                                                          | SLV4 | SLV3 | SLV2 | SLV1 | SLV0            | GC   | 0000000     |  |  |  |

| Bit7                                                                                                                                                                                                                                                                                                         | Bit6                                                                                                                                                                                          | Bit5 | Bit4 | Bit3 | Bit2 | Bit1            | Bit0 |             |  |  |  |

|                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                               |      |      |      |      | SFR AG<br>SFR I |      | 0xC3<br>0   |  |  |  |

| Bits7–1: SLV6–SLV0: SMBus0 Slave Address.<br>These bits are loaded with the 7-bit slave address to which SMBus0 will respond when oper-<br>ating as a slave transmitter or slave receiver. SLV6 is the most significant bit of the address<br>and corresponds to the first bit of the address byte received. |                                                                                                                                                                                               |      |      |      |      |                 |      |             |  |  |  |

| Bit0:                                                                                                                                                                                                                                                                                                        | it0: GC: General Call Address Enable.<br>This bit is used to enable general call address (0x00) recognition.<br>0: General call address is ignored.<br>1: General call address is recognized. |      |      |      |      |                 |      |             |  |  |  |

#### 19.4.5. Status Register

The SMB0STA Status register holds an 8-bit status code indicating the current state of the SMBus0 interface. There are 28 possible SMBus0 states, each with a corresponding unique status code. The five most significant bits of the status code vary while the three least-significant bits of a valid status code are fixed at zero when SI = '1'. Therefore, all possible status codes are multiples of eight. This facilitates the use of status codes in software as an index used to branch to appropriate service routines (allowing 8 bytes of code to service the state or jump to a more extensive service routine).

For the purposes of user software, the contents of the SMB0STA register is only defined when the SI flag is logic 1. Software should never write to the SMB0STA register; doing so will yield indeterminate results. The 28 SMBus0 states, along with their corresponding status codes, are given in Table 1.1.

| R/W      | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W  | R/W           | R/W          | R/W       | R/W        | R/W                       | Reset Value |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|--------------|-----------|------------|---------------------------|-------------|--|--|

| STA7     | STA6                                                                                                                                                                                                                                                                                                                                                                                                                                    | STA5 | STA4          | STA3         | STA2      | STA1       | STA0                      | 11111000    |  |  |

| Bit7     | Bit6                                                                                                                                                                                                                                                                                                                                                                                                                                    | Bit5 | Bit4          | Bit3         | Bit2      | Bit1       | Bit0                      | -           |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |               |              |           |            | SFR Address:<br>SFR Page: |             |  |  |

| Bits7–3: | Bits7–3: STA7–STA3: SMBus0 Status Code.<br>These bits contain the SMBus0 Status Code. There are 28 possible status codes; each sta-<br>tus code corresponds to a single SMBus state. A valid status code is present in SMB0STA<br>when the SI flag (SMB0CN.3) is set to logic 1. The content of SMB0STA is not defined when<br>the SI flag is logic 0. Writing to the SMB0STA register at any time will yield indeterminate<br>results. |      |               |              |           |            |                           |             |  |  |

| Bits2–0: | STA2–STA0<br>the SI flag is                                                                                                                                                                                                                                                                                                                                                                                                             |      | least signifi | cant bits of | SMB0STA : | are always | read as log               | ic 0 when   |  |  |

### SFR Definition 19.5. SMB0STA: SMBus0 Status

| R/W   | R/W                                                                                                              | R/W                           | R/W                          | R/W                        | R/W                         | R/W           | R/W                   | Reset Value        |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------------|----------------------------|-----------------------------|---------------|-----------------------|--------------------|--|--|--|

| S1MOD | Ξ -                                                                                                              | MCE1                          | REN1                         | TB81                       | RB81                        | TI1           | RI1                   | 0100000            |  |  |  |

| Bit7  | Bit6                                                                                                             | Bit5                          | Bit4                         | Bit3                       | Bit2                        | Bit1          | Bit0                  | Bit<br>Addressable |  |  |  |

|       |                                                                                                                  |                               |                              |                            |                             |               | SFR Addres<br>SFR Pag | ss: 0x98           |  |  |  |

| Bit7: | S1MODE: S                                                                                                        |                               |                              |                            |                             |               |                       |                    |  |  |  |

|       | This bit sele<br>0: Mode 0: 8                                                                                    | B-bit UART                    | with Variabl                 | e Baud Rat                 |                             |               |                       |                    |  |  |  |

| Dire  | 1: Mode 1: 9                                                                                                     |                               |                              |                            | е                           |               |                       |                    |  |  |  |

| Bit6: | UNUSED. R                                                                                                        |                               |                              |                            |                             |               |                       |                    |  |  |  |

| Bit5: | MCE1: Multi                                                                                                      | •                             |                              |                            |                             |               | 1 a al a              |                    |  |  |  |

|       | The function of this bit is dependent on the Serial Port 0 Operation Mode.<br>Mode 0: Checks for valid stop bit. |                               |                              |                            |                             |               |                       |                    |  |  |  |

|       |                                                                                                                  |                               |                              | ignored                    |                             |               |                       |                    |  |  |  |

|       | 0: Logic level of stop bit is ignored.                                                                           |                               |                              |                            |                             |               |                       |                    |  |  |  |

|       | 1: RI1 will only be activated if stop bit is logic level 1.<br>Mode 1: Multiprocessor Communications Enable.     |                               |                              |                            |                             |               |                       |                    |  |  |  |

|       | 0: Logic level of ninth bit is ignored.                                                                          |                               |                              |                            |                             |               |                       |                    |  |  |  |

|       | 1: RI1 is set and an interrupt is generated only when the ninth bit is logic 1.                                  |                               |                              |                            |                             |               |                       |                    |  |  |  |

| Bit4: | REN1: Rece                                                                                                       |                               |                              | prio genere                |                             |               | in bit io iog         |                    |  |  |  |

|       | This bit enables/disables the UART receiver.                                                                     |                               |                              |                            |                             |               |                       |                    |  |  |  |

|       | 0: UART1 reception disabled.                                                                                     |                               |                              |                            |                             |               |                       |                    |  |  |  |

|       | 1: UART1 reception enabled.                                                                                      |                               |                              |                            |                             |               |                       |                    |  |  |  |

| Bit3: | TB81: Ninth Transmission Bit.                                                                                    |                               |                              |                            |                             |               |                       |                    |  |  |  |

|       | The logic level of this bit will be assigned to the ninth transmission bit in 9-bit UART Mode. It                |                               |                              |                            |                             |               |                       |                    |  |  |  |

|       | is not used in 8-bit UART Mode. Set or cleared by software as required.                                          |                               |                              |                            |                             |               |                       |                    |  |  |  |

| Bit2: | RB81: Ninth                                                                                                      | Receive Bi                    | t.                           |                            |                             |               |                       |                    |  |  |  |

|       | RB81 is assigned the value of the STOP bit in Mode 0; it is assigned the value of the 9th                        |                               |                              |                            |                             |               |                       |                    |  |  |  |

|       | data bit in Mode 1.                                                                                              |                               |                              |                            |                             |               |                       |                    |  |  |  |

| Bit1: | TI1: Transm                                                                                                      |                               |                              |                            |                             |               |                       |                    |  |  |  |

|       | Set by hardy<br>bit UART Mo<br>interrupt is e<br>routine. This                                                   | ode, or at th<br>enabled, set | e beginning<br>ting this bit | g of the STC<br>causes the | P bit in 9-bi<br>CPU to vec | it UART Mo    | ode). Wher            | n the UART1        |  |  |  |

| Bit0: | RI1: Receive                                                                                                     |                               |                              |                            |                             |               |                       |                    |  |  |  |

|       | Set to '1' by<br>sampling tim<br>to vector to t<br>ware.                                                         | hardware w<br>ne). When tl    | hen a byte<br>ne UART1 i     | nterrupt is o              | enabled, set                | ting this bit | t to '1' caus         | ses the CPU        |  |  |  |

### SFR Definition 22.1. SCON1: Serial Port 1 Control

| Frequency: 50.0 MHz          |                      |                                  |                       |                                     |      |                                  |  |  |  |  |

|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------|------|----------------------------------|--|--|--|--|

| Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload<br>Value (hex) |  |  |  |  |

| 230400                       | 0.45%                | 218                              | SYSCLK                | XX                                  | 1    | 0x93                             |  |  |  |  |

| 115200                       | -0.01%               | 434                              | SYSCLK                | XX                                  | 1    | 0x27                             |  |  |  |  |