# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 100MHz                                                         |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 64                                                             |

| Program Memory Size        | 128KB (128K x 8)                                               |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 8.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                      |

| Data Converters            | A/D 8x8b, 8x10b; D/A 2x12b                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 100-TQFP                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f122-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **List Of Tables**

| 1.  | System Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | Table 1.1. Product Selection Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20  |

| 2.  | Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|     | Table 2.1. Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 38  |

| 3.  | Global DC Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|     | Table 3.1. Global DC Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|     | (C8051F120/1/2/3 and C8051F130/1/2/3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|     | Table 3.2. Global DC Electrical Characteristics (C8051F124/5/6/7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 40  |

| 4.  | Pinout and Package Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| _   | Table 4.1. Pin Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41  |

| 5.  | ADC0 (12-Bit ADC, C8051F120/1/4/5 Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| _   | Table 5.1. 12-Bit ADC0 Electrical Characteristics (C8051F120/1/4/5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 72  |

| 6.  | ADC0 (10-Bit ADC, C8051F122/3/6/7 and C8051F13x Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|     | Table 6.1. 10-Bit ADC0 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | • • |

| _   | (C8051F122/3/6/7 and C8051F13x)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 90  |

| 7.  | ADC2 (8-Bit ADC, C8051F12x Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| ~   | Table 7.1. ADC2 Electrical Characteristics       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1 | 103 |

| 8.  | DACs, 12-Bit Voltage Mode (C8051F12x Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| •   | Table 8.1. DAC Electrical Characteristics       1         Value of Performance       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 111 |

| 9.  | Voltage Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 110 |

| 10  | Table 9.1. Voltage Reference Electrical Characteristics         1           Componenters         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ΙIð |

| 10. | .Comparators Table 10.1. Comparator Electrical Characteristics1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 126 |

| 11  | .CIP-51 Microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20  |

|     | Table 11.1. CIP-51 Instruction Set Summary 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 120 |

|     | Table 11.2. Special Function Register (SFR) Memory Map       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|     | Table 11.2. Special Function Register (SFR) Memory Map         11.3. Special Function Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|     | Table 11.4. Interrupt Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 12  | .Multiply And Accumulate (MAC0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 100 |

|     | Table 12.1. MAC0 Rounding (MAC0SAT = 0) $\dots$ 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 168 |

| 13  | Reset Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00  |

|     | Table 13.1. Reset Electrical Characteristics       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 83  |

| 14. | .Oscillators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|     | Table 14.1. Oscillator Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85  |

|     | Table 14.2. PLL Frequency Characteristics    1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 95  |

|     | Table 14.3. PLL Lock Timing Characteristics 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 15. | . Flash Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|     | Table 15.1. Flash Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 200 |

| 16. | . Branch Target Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 17. | External Data Memory Interface and On-Chip XRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|     | Table 17.1. AC Parameters for External Memory Interface    2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 233 |

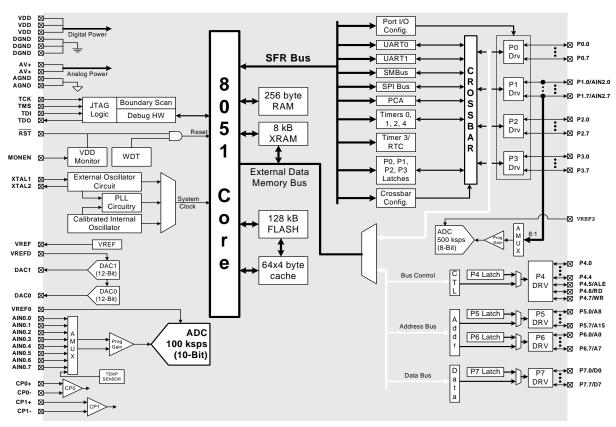

Figure 1.3. C8051F122/126 Block Diagram

### 1.1. CIP-51<sup>™</sup> Microcontroller Core

#### 1.1.1. Fully 8051 Compatible

The C8051F12x and C8051F13x utilize Silicon Labs' proprietary CIP-51 microcontroller core. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The core has all the peripherals included with a standard 8052, including five 16-bit counter/timers, two full-duplex UARTs, 256 bytes of internal RAM, 128 byte Special Function Register (SFR) address space, and 8/4 byte-wide I/O Ports.

#### 1.1.2. Improved Throughput

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute with a maximum system clock of 12-to-24 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with only four instructions taking more than four system clock cycles.

The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

With the CIP-51's maximum system clock at 100 MHz, the C8051F120/1/2/3 and C8051F130/1/2/3 have a peak throughput of 100 MIPS (the C8051F124/5/6/7 have a peak throughput of 50 MIPS).

### Table 5.1. 12-Bit ADC0 Electrical Characteristics (C8051F120/1/4/5)

$V_{DD}$  = 3.0 V, AV+ = 3.0 V, VREF = 2.40 V (REFBE = 0), PGA Gain = 1, -40 to +85 °C unless otherwise specified.

| — — — — — — — — — — — — — — — — — — — | 12<br>                                | ±1<br>±1<br>—<br>=<br>cale, 100<br>—<br>2.5<br>—<br>— | dB<br>dB<br>dB<br>MHz<br>clocks<br>µs                                                            |

|---------------------------------------|---------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| 66<br>—                               |                                       | ±1<br>—<br>—<br>cale, 100<br>—<br>2.5<br>—<br>—       | LSB<br>LSB<br>LSB<br>ppm/°C<br><b>D ksps</b><br>dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>clocks<br>µs |

| 66<br>—                               | -7±3<br>±0.25<br>7 Full Sc<br><br>-75 | ±1<br>—<br>—<br>cale, 100<br>—<br>2.5<br>—<br>—       | LSB<br>LSB<br>ppm/°C<br><b>D ksps</b><br>dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>clocks              |

| 66<br>—                               | -7±3<br>±0.25<br>7 Full Sc<br><br>-75 |                                                       | LSB<br>LSB<br>ppm/°C<br><b>0 ksps</b><br>dB<br>dB<br>dB<br>dB<br>MHz<br>clocks<br>µs             |

| 66<br>—                               | -7±3<br>±0.25<br>7 Full Sc<br><br>-75 | —<br>—<br>2.5<br>—                                    | LSB<br>ppm/°C<br><b>0 ksps</b><br>dB<br>dB<br>dB<br>dB<br>MHz<br>clocks<br>µs                    |

| 66<br>—                               | ±0.25<br>7 Full Sc<br>                | —<br>—<br>2.5<br>—                                    | ppm/°C<br>D ksps<br>dB<br>dB<br>dB<br>MHz<br>clocks<br>µs                                        |

| 66<br>—                               | <b>Full So</b><br>—<br>—75            | —<br>—<br>2.5<br>—                                    | O ksps<br>dB<br>dB<br>dB<br>dB<br>MHz<br>clocks<br>μs                                            |

| 66<br>—                               | —<br>–75                              | —<br>—<br>2.5<br>—                                    | dB<br>dB<br>dB<br>MHz<br>clocks<br>µs                                                            |

| —<br>—<br>—<br>16                     |                                       |                                                       | dB<br>dB<br>MHz<br>clocks<br>µs                                                                  |

|                                       |                                       |                                                       | dB<br>MHz<br>clocks<br>µs                                                                        |

|                                       | 80<br>—<br>—<br>—                     |                                                       | MHz<br>clocks<br>µs                                                                              |

|                                       | -                                     |                                                       | clocks<br>µs                                                                                     |

|                                       |                                       |                                                       | clocks<br>µs                                                                                     |

|                                       |                                       |                                                       | μs                                                                                               |

| 1.5                                   | —                                     | _                                                     | -                                                                                                |

| _                                     |                                       |                                                       |                                                                                                  |

|                                       | _                                     | 100                                                   | ksps                                                                                             |

|                                       |                                       | •                                                     |                                                                                                  |

| 0                                     | _                                     | VREF                                                  | V                                                                                                |

| GND                                   | _                                     | AV+                                                   | V                                                                                                |

| _                                     | 10                                    | —                                                     | pF                                                                                               |

|                                       |                                       | •                                                     |                                                                                                  |

| —                                     | ±0.2                                  | —                                                     | °C                                                                                               |

| —                                     | 776                                   | —                                                     | mV                                                                                               |

| _                                     | ±8.5                                  | —                                                     | mV                                                                                               |

| —                                     | 2.86                                  | —                                                     | mV / °C                                                                                          |

| —                                     | ±0.034                                | —                                                     | mV / °C                                                                                          |

|                                       |                                       | 1                                                     |                                                                                                  |

| _                                     | 450                                   | 900                                                   | μA                                                                                               |

|                                       | .0.2                                  | —                                                     | mV/V                                                                                             |

| _                                     | -                                     | - 2.86<br>- ±0.034                                    | - 2.86<br>- ±0.034<br>- 450 900                                                                  |

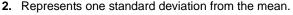

### 6. ADC0 (10-Bit ADC, C8051F122/3/6/7 and C8051F13x Only)

The ADC0 subsystem for the C8051F122/3/6/7 and C8051F13x consists of a 9-channel, configurable analog multiplexer (AMUX0), a programmable gain amplifier (PGA0), and a 100 ksps, 10-bit successiveapproximation-register ADC with integrated track-and-hold and Programmable Window Detector (see block diagram in Figure 6.1). The AMUX0, PGA0, Data Conversion Modes, and Window Detector are all configurable under software control via the Special Function Registers shown in Figure 6.1. The voltage reference used by ADC0 is selected as described in **Section "9. Voltage Reference" on page 113**. The ADC0 subsystem (ADC0, track-and-hold and PGA0) is enabled only when the AD0EN bit in the ADC0 Control register (ADC0CN) is set to logic 1. The ADC0 subsystem is in low power shutdown when this bit is logic 0.

Figure 6.1. 10-Bit ADC0 Functional Block Diagram

### 6.1. Analog Multiplexer and PGA

Eight of the AMUX channels are available for external measurements while the ninth channel is internally connected to an on-chip temperature sensor (temperature transfer function is shown in Figure 6.2). AMUX input pairs can be programmed to operate in either differential or single-ended mode. This allows the user to select the best measurement technique for each input channel, and even accommodates mode changes "on-the-fly". The AMUX defaults to all single-ended inputs upon reset. There are two registers associated with the AMUX: the Channel Selection register AMX0SL (SFR Definition 6.2), and the Configuration register AMX0CF (SFR Definition 6.1). The table in SFR Definition 6.2 shows AMUX functionality by channel, for each possible configuration. The PGA amplifies the AMUX output signal by an amount determined by the states of the AMP0GN2-0 bits in the ADC0 Configuration register, ADC0CF (SFR Definition 6.3). The PGA can be software-programmed for gains of 0.5, 2, 4, 8 or 16. Gain defaults to unity on reset.

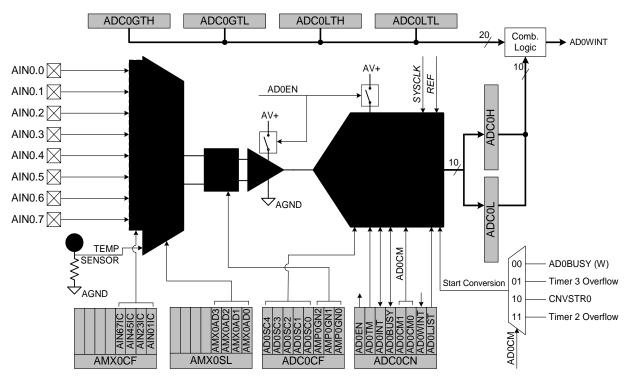

## 8. DACs, 12-Bit Voltage Mode (C8051F12x Only)

The C8051F12x devices include two on-chip 12-bit voltage-mode Digital-to-Analog Converters (DACs). Each DAC has an output swing of 0 V to (VREF-1LSB) for a corresponding input code range of 0x000 to 0xFFF. The DACs may be enabled/disabled via their corresponding control registers, DAC0CN and DAC1CN. While disabled, the DAC output is maintained in a high-impedance state, and the DAC supply current falls to 1  $\mu$ A or less. The voltage reference for each DAC is supplied at the VREFD pin (C8051F120/2/4/6 devices) or the VREF pin (C8051F121/3/5/7 devices). Note that the VREF pin on C8051F121/3/5/7 devices may be driven by the internal voltage reference or an external source. If the internal voltage reference is used it must be enabled in order for the DAC outputs to be valid. See **Section** "9. Voltage Reference" on page 113 for more information on configuring the voltage reference for the DACs.

### 8.1. DAC Output Scheduling

Each DAC features a flexible output update mechanism which allows for seamless full-scale changes and supports jitter-free updates for waveform generation. The following examples are written in terms of DAC0, but DAC1 operation is identical.

Figure 8.1. DAC Functional Block Diagram

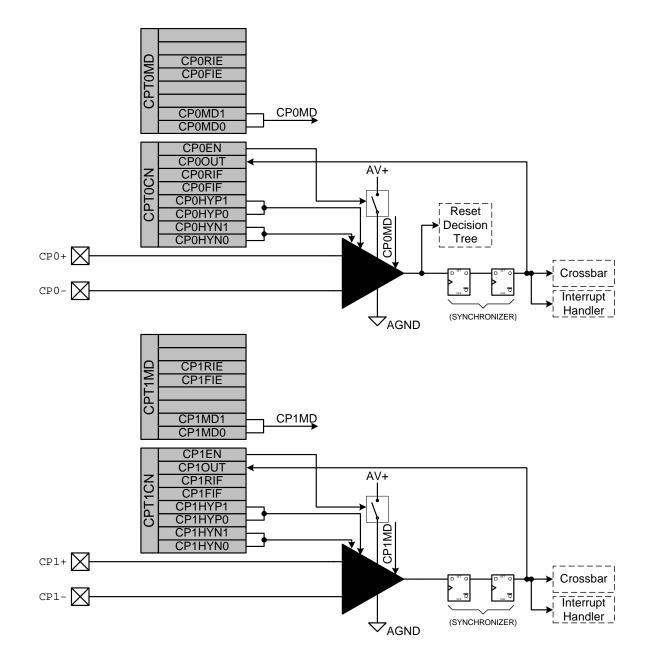

### **10. Comparators**

Two on-chip programmable voltage comparators are included, as shown in Figure 10.1. The inputs of each comparator are available at dedicated pins. The output of each comparator is optionally available at the package pins via the I/O crossbar. When assigned to package pins, each comparator output can be programmed to operate in open drain or push-pull modes. See Section "18.1. Ports 0 through 3 and the Priority Crossbar Decoder" on page 238 for Crossbar and port initialization details.

Figure 10.1. Comparator Functional Block Diagram

### Table 11.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

| Register Address                                                                                     |                   | SFR<br>Page                                              | Description                                                                                                              | Page No. |

|------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------|

| TMR4L 0xCC 2                                                                                         |                   | 2                                                        | Timer/Counter 4 Low Byte                                                                                                 | page 323 |

| WDTCN                                                                                                | 0xFF              | All Pages                                                | Watchdog Timer Control                                                                                                   | page 181 |

| XBR0                                                                                                 | 0xE1              | F                                                        | Port I/O Crossbar Control 0                                                                                              | page 245 |

| XBR1 0xE2 I                                                                                          |                   | F                                                        | Port I/O Crossbar Control 1                                                                                              | page 246 |

| XBR2 0xE3                                                                                            |                   | F                                                        | Port I/O Crossbar Control 2                                                                                              | page 247 |

| <ol> <li>Refers t</li> <li>Refers t</li> <li>Refers t</li> <li>Refers t</li> <li>Refers t</li> </ol> | o a register in t | the C8051F1<br>the C8051F1<br>the C8051F1<br>the C8051F1 | 122/3/6/7 and C8051F130/1/2/3 only.<br>120/1/2/3/4/5/6/7 only.<br>120/1/2/3 and C8051F130/1/2/3 only.<br>120/2/4/6 only. |          |

7. Refers to a register in the C8051F130/1/2/3 only.

| R/W      | R/W                          | R/W        | R/W              | R/W           | R/W           | R/W           | R                       | Reset Value           |

|----------|------------------------------|------------|------------------|---------------|---------------|---------------|-------------------------|-----------------------|

| CY       | AC                           | F0         | RS1              | RS0           | OV            | F1            | PARITY                  | 0000000               |

| Bit7     | Bit6                         | Bit5       | Bit4             | Bit3          | Bit2          | Bit1          | Bit0                    | Bit<br>Addressable    |

|          |                              |            |                  |               |               |               | SFR Address<br>SFR Page | : 0xD0<br>: All Pages |

| Bit7:    | CY: Carry I<br>This bit is s | •          | ne last arithmet | tic operatio  | n resulted    | in a carry (a | addition) or            | a borrow              |

|          |                              |            | ared to 0 by all |               |               |               | , -                     |                       |

| Bit6:    | AC: Auxilia                  |            |                  |               |               |               |                         |                       |

|          |                              |            | e last arithmeti |               |               |               |                         |                       |

| Bit5:    | from (subtr<br>F0: User F    |            | high order nib   | ble. It is cl | eared to 0    | by all other  | arithmetic of           | operations.           |

| Dito.    |                              | •          | able, general pu | urpose flac   | ı for use uı  | nder softwar  | e control.              |                       |

| Bits4–3: |                              |            | Bank Select.     |               |               |               |                         |                       |

|          | These bits                   | select whi | ch register ban  | k is used o   | during regi   | ster accesse  | es.                     |                       |

|          |                              |            |                  |               |               |               |                         |                       |

|          | RS1                          | RS0        | Register Bank    | Add           | ress          |               |                         |                       |

|          | 0                            | 0          | 0                | 0x00-         | -0x07         |               |                         |                       |

|          | 0                            | 1          | 1                | 0x08-         | -0x0F         |               |                         |                       |

|          | 1                            | 0          | 2                | 0x10-         | -0x17         |               |                         |                       |

|          | 1                            | 1          | 3                | 0x18-         | -0x1F         |               |                         |                       |

| Bit2:    | OV: Overflo                  | ow Flag.   |                  |               |               |               |                         |                       |

| Ditt.    |                              | •          | der the followin | g circumst    | ances:        |               |                         |                       |

|          |                              |            | SUBB instructi   |               |               | ange overflo  | W.                      |                       |

|          |                              |            | esults in an ove | · ·           | •             | er than 255)  |                         |                       |

|          |                              |            | uses a divide-l  |               |               |               |                         |                       |

|          |                              | is cleared | to 0 by the AD   | D, ADDC,      | SUBB, MI      | JL, and DIV   | instructions            | s in all other        |

| Bit1:    | cases.<br>F1: User F         |            |                  |               |               |               |                         |                       |

| DILT.    |                              |            | able, general pu | Irnose flag   | I for Use III | nder softwar  | e control               |                       |

| Bit0:    | PARITY: P                    |            | sio, general pr  |               |               |               | 0.0011101.              |                       |

|          |                              |            | e sum of the ei  | ight bits in  | the accum     | ulator is odd | and cleare              | d if the sum          |

|          | is even.                     |            |                  | -             |               |               |                         |                       |

|          |                              |            |                  |               |               |               |                         |                       |

|          |                              |            |                  |               |               |               |                         |                       |

### SFR Definition 11.9. PSW: Program Status Word

| R/W   | R/W                                                                                                                  | R/W        | R/W           | R/W            | R/W       | R/W        | R/W        | Reset Value             |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------|------------|---------------|----------------|-----------|------------|------------|-------------------------|--|--|--|

| -     | ES1                                                                                                                  | -          | EADC2         | EWADC2         | ET4       | EADC0      | ET3        | 00000000                |  |  |  |

| Bit7  | Bit6                                                                                                                 | Bit5       | Bit4          | Bit3           | Bit2      | Bit1       | Bit0       |                         |  |  |  |

|       |                                                                                                                      |            |               |                |           |            | SFR Addres | s: 0xE7<br>e: All Pages |  |  |  |

|       |                                                                                                                      |            |               |                |           |            | or ren ag  | o. / all l'agoo         |  |  |  |

| Bit7: | UNUSED. R                                                                                                            |            |               | 't care.       |           |            |            |                         |  |  |  |

| Bit6: | ES1: Enable                                                                                                          |            |               |                |           |            |            |                         |  |  |  |

|       | This bit sets the masking of the UART1 interrupt.                                                                    |            |               |                |           |            |            |                         |  |  |  |

|       | 0: Disable U                                                                                                         |            | •             |                |           |            |            |                         |  |  |  |

| D     | 1: Enable U/                                                                                                         |            |               |                |           |            |            |                         |  |  |  |

| Bit5: | UNUSED. R                                                                                                            |            |               |                |           |            |            |                         |  |  |  |

| Bit4: | This bit sets                                                                                                        |            |               | nversion Inte  | •         | intorrunt  |            |                         |  |  |  |

|       |                                                                                                                      |            | •             |                | onversion | interrupt. |            |                         |  |  |  |

|       | <ul><li>0: Disable ADC2 End of Conversion interrupts.</li><li>1: Enable ADC2 End of Conversion Interrupts.</li></ul> |            |               |                |           |            |            |                         |  |  |  |

| Bit3: | EWADC2: Enable Window Comparison ADC2 Interrupt.                                                                     |            |               |                |           |            |            |                         |  |  |  |

|       | This bit sets the masking of ADC2 Window Comparison interrupt.                                                       |            |               |                |           |            |            |                         |  |  |  |

|       | 0: Disable A                                                                                                         |            |               |                |           | •          |            |                         |  |  |  |

|       | 1: Enable A[                                                                                                         | C2 Windo   | w Compari     | son Interrupt  | S.        |            |            |                         |  |  |  |

| Bit2: | ET4: Enable                                                                                                          | Timer 4 In | terrupt       |                |           |            |            |                         |  |  |  |

|       | This bit sets                                                                                                        | the maskir | ng of the Tir | mer 4 interrup | ot.       |            |            |                         |  |  |  |

|       | 0: Disable Ti                                                                                                        |            | •             |                |           |            |            |                         |  |  |  |

|       | 1: Enable Tir                                                                                                        |            |               |                |           |            |            |                         |  |  |  |

| Bit1: | EADC0: Ena                                                                                                           |            |               |                |           | •          |            |                         |  |  |  |

|       | This bit sets                                                                                                        |            | •             |                | onversion | Interrupt. |            |                         |  |  |  |

|       | 0: Disable A                                                                                                         |            |               |                |           |            |            |                         |  |  |  |

| Bit0: | 1: Enable AE<br>ET3: Enable                                                                                          |            |               | n interrupts.  |           |            |            |                         |  |  |  |

| DILU. | This bit sets                                                                                                        |            | •             | nor 3 interrur | ht.       |            |            |                         |  |  |  |

|       | 0: Disable Ti                                                                                                        |            |               |                |           |            |            |                         |  |  |  |

|       | 1: Enable Tir                                                                                                        |            | •             |                |           |            |            |                         |  |  |  |

|       |                                                                                                                      |            |               |                |           |            |            |                         |  |  |  |

|       |                                                                                                                      |            |               |                |           |            |            |                         |  |  |  |

### SFR Definition 11.15. EIE2: Extended Interrupt Enable 2

Electrical specifications for the precision internal oscillator are given in Table 14.1. Note that the system clock may be derived from the programmed internal oscillator divided by 1, 2, 4, or 8, as defined by the IFCN bits in register OSCICN.

### SFR Definition 14.1. OSCICL: Internal Oscillator Calibration.

### SFR Definition 14.2. OSCICN: Internal Oscillator Control

| R/W       | R                                                                                                                                                                                                                       | R/W           | R           | R/W         | R/W   | R/W   | R/W                       | Reset Value |  |  |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|-------------|-------|-------|---------------------------|-------------|--|--|--|

| IOSCEN    | I IFRDY                                                                                                                                                                                                                 | -             | -           | -           | -     | IFCN1 | IFCN0                     | 11000000    |  |  |  |

| Bit7      | Bit6                                                                                                                                                                                                                    | Bit5          | Bit4        | Bit3        | Bit2  | Bit1  | Bit0                      | -           |  |  |  |

|           |                                                                                                                                                                                                                         |               |             |             |       |       | SFR Address:<br>SFR Page: |             |  |  |  |

| Bit 7:    | IOSCEN: Int<br>0: Internal O<br>1: Internal O                                                                                                                                                                           | scillator Dis | abled.      | Bit.        |       |       |                           |             |  |  |  |

| Bit 6:    | 1: Internal Oscillator Enabled.     Bit 6: IFRDY: Internal Oscillator Frequency Ready Flag.     0: Internal Oscillator not running at programmed frequency.     1: Internal Oscillator running at programmed frequency. |               |             |             |       |       |                           |             |  |  |  |

| Bits 5-2: | Reserved.                                                                                                                                                                                                               |               |             | -           |       |       |                           |             |  |  |  |

| Bits 1–0: | IFCN1-0: Int                                                                                                                                                                                                            | ernal Oscilla | ator Freque | ncy Control | Bits. |       |                           |             |  |  |  |

|           | 00: Internal (                                                                                                                                                                                                          | Oscillator is | divided by  | 8.          |       |       |                           |             |  |  |  |

|           | 01: Internal (                                                                                                                                                                                                          | Oscillator is | divided by  | 4.          |       |       |                           |             |  |  |  |

|           | 10: Internal (                                                                                                                                                                                                          | Oscillator is | divided by  | 2.          |       |       |                           |             |  |  |  |

|           | 11: Internal (                                                                                                                                                                                                          | Oscillator is | divided by  | 1.          |       |       |                           |             |  |  |  |

# page 199). Important Note: Cache reads, cache writes, and the prefetch engine should be disabled whenever the FLRT bits are changed to a lower setting.

To shut down the PLL, the system clock should be switched to the internal oscillator or a stable external clock source, using the CLKSEL register. Next, disable the PLL by setting PLLEN (PLL0CN.1) to '0'. Finally, the PLL can be powered off, by setting PLLPWR (PLL0CN.0) to '0'. Note that the PLLEN and PLL-PWR bits can be cleared at the same time.

| R/W       | R/W                                                                                | R/W          | R            | R/W           | R/W          | R/W     | R/W                       | Reset Value |  |  |  |

|-----------|------------------------------------------------------------------------------------|--------------|--------------|---------------|--------------|---------|---------------------------|-------------|--|--|--|

| -         | -                                                                                  | -            | PLLLCK       | 0             | PLLSRC       | PLLEN   | PLLPWR                    | 00000000    |  |  |  |

| Bit7      | Bit6                                                                               | Bit5         | Bit4         | Bit3          | Bit2         | Bit1    | Bit0                      | -           |  |  |  |

|           |                                                                                    |              |              |               |              |         | SFR Address:<br>SFR Page: |             |  |  |  |

| Bits 7–5: | UNUSED: R                                                                          | ead = 000b   | ; Write = do | on't care.    |              |         |                           |             |  |  |  |

| Bit 4:    | Bits 7–5: UNUSED: Read = 000b; Write = don't care.<br>Bit 4: PLLCK: PLL Lock Flag. |              |              |               |              |         |                           |             |  |  |  |

|           | 0: PLL Frequ                                                                       |              |              |               |              |         |                           |             |  |  |  |

|           | 1: PLL Frequ                                                                       | lency is loc | ked.         |               |              |         |                           |             |  |  |  |

| Bit 3:    | RESERVED                                                                           |              |              |               |              |         |                           |             |  |  |  |

| Bit 2:    | PLLSRC: PL                                                                         |              |              |               |              |         |                           |             |  |  |  |

|           | 0: PLL Refer                                                                       |              |              |               |              |         |                           |             |  |  |  |

| D:4.4.    | 1: PLL Refer                                                                       |              |              | External Os   | cillator.    |         |                           |             |  |  |  |

| Bit 1:    | PLLEN: PLL<br>0: PLL is hel                                                        |              |              |               |              |         |                           |             |  |  |  |

|           | 1: PLL is nei                                                                      |              | N/P must h   | o '1'         |              |         |                           |             |  |  |  |

| Bit 0:    | PLLPWR: PL                                                                         |              |              |               |              |         |                           |             |  |  |  |

| Dit U.    | 0: PLL bias g                                                                      |              |              | ed. No statio | c power is c | onsumed |                           |             |  |  |  |

|           | 1: PLL bias                                                                        |              |              |               | •            |         |                           |             |  |  |  |

|           |                                                                                    | ,            |              |               |              |         |                           |             |  |  |  |

|           |                                                                                    |              |              |               |              |         |                           |             |  |  |  |

### SFR Definition 14.5. PLL0CN: PLL Control

|                         |        |         | Lock Status |

|-------------------------|--------|---------|-------------|

|                         | TAG 0  | SLOT 0  | UNLOCKED    |

|                         | TAG 1  | SLOT 1  | UNLOCKED    |

| Cache Push              | TAG 2  | SLOT 2  | UNLOCKED    |

| Operations<br>Decrement |        |         | UNLOCKED    |

| CHSLOT                  |        |         | 1           |

| <b>A</b>                |        |         |             |

|                         | TAG 57 | SLOT 57 | UNLOCKED    |

| CHSLOT = 58             | TAG 58 | SLOT 58 | UNLOCKED    |

| $\perp$                 | TAG 59 | SLOT 59 | LOCKED      |

| Cache Pop               | TAG 60 | SLOT 60 | LOCKED      |

| Operations              | TAG 61 | SLOT 61 | LOCKED      |

| Increment               | TAG 62 | SLOT 62 | LOCKED      |

| CHSLOT                  |        |         | •           |

Figure 16.3. Cache Lock Operation

### **19.4. SMBus Special Function Registers**

The SMBus0 serial interface is accessed and controlled through five SFR's: SMB0CN Control Register, SMB0CR Clock Rate Register, SMB0ADR Address Register, SMB0DAT Data Register and SMB0STA Status Register. The five special function registers related to the operation of the SMBus0 interface are described in the following sections.

#### 19.4.1. Control Register

The SMBus0 Control register SMB0CN is used to configure and control the SMBus0 interface. All of the bits in the register can be read or written by software. Two of the control bits are also affected by the SMBus0 hardware. The Serial Interrupt flag (SI, SMB0CN.3) is set to logic 1 by the hardware when a valid serial interrupt condition occurs. It can only be cleared by software. The Stop flag (STO, SMB0CN.4) is set to logic 1 by software. It is cleared to logic 0 by hardware when a STOP condition is detected on the bus.

Setting the ENSMB flag to logic 1 enables the SMBus0 interface. Clearing the ENSMB flag to logic 0 disables the SMBus0 interface and removes it from the bus. Momentarily clearing the ENSMB flag and then resetting it to logic 1 will reset SMBus0 communication. However, ENSMB should not be used to temporarily remove a device from the bus since the bus state information will be lost. Instead, the Assert Acknowledge (AA) flag should be used to temporarily remove the device from the bus (see description of AA flag below).

Setting the Start flag (STA, SMB0CN.5) to logic 1 will put SMBus0 in a master mode. If the bus is free, SMBus0 will generate a START condition. If the bus is not free, SMBus0 waits for a STOP condition to free the bus and then generates a START condition after a 5 µs delay per the SMB0CR value (In accordance with the SMBus protocol, the SMBus0 interface also considers the bus free if the bus is idle for 50 µs and no STOP condition was recognized). If STA is set to logic 1 while SMBus0 is in master mode and one or more bytes have been transferred, a repeated START condition will be generated.

When the Stop flag (STO, SMB0CN.4) is set to logic 1 while the SMBus0 interface is in master mode, the interface generates a STOP condition. In a slave mode, the STO flag may be used to recover from an error condition. In this case, a STOP condition is not generated on the bus, but the SMBus hardware behaves as if a STOP condition has been received and enters the "not addressed" slave receiver mode. Note that this simulated STOP will not cause the bus to appear free to SMBus0. The bus will remain occupied until a STOP appears on the bus or a Bus Free Timeout occurs. Hardware automatically clears the STO flag to logic 0 when a STOP condition is detected on the bus.

The Serial Interrupt flag (SI, SMB0CN.3) is set to logic 1 by hardware when the SMBus0 interface enters one of 27 possible states. If interrupts are enabled for the SMBus0 interface, an interrupt request is generated when the SI flag is set. The SI flag must be cleared by software.

**Important Note:** If SI is set to logic 1 while the SCL line is low, the clock-low period of the serial clock will be stretched and the serial transfer is suspended until SI is cleared to logic 0. A high level on SCL is not affected by the setting of the SI flag.

The Assert Acknowledge flag (AA, SMB0CN.2) is used to set the level of the SDA line during the acknowledge clock cycle on the SCL line. Setting the AA flag to logic 1 will cause an ACK (low level on SDA) to be sent during the acknowledge cycle if the device has been addressed. Setting the AA flag to logic 0 will cause a NACK (high level on SDA) to be sent during acknowledge cycle. After the transmission of a byte in slave mode, the slave can be temporarily removed from the bus by clearing the AA flag. The slave's own address and general call address will be ignored. To resume operation on the bus, the AA flag must be reset to logic 1 to allow the slave's address to be recognized.

| R/W      | R/W                                                                                                                                                                   | R/W                                                                                                               | R/W          | R/W          | R/W          | R/W         | R/W                | Reset Value                   |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|-------------|--------------------|-------------------------------|--|--|--|

| SM00     | SM10                                                                                                                                                                  | SM20                                                                                                              | REN0         | TB80         | RB80         | TI0         | RI0                | 0000000                       |  |  |  |