Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | 8051                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 100MHz                                                       |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT           |

| Number of I/O              | 32                                                           |

| Program Memory Size        | 128KB (128K x 8)                                             |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 8.25K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                    |

| Data Converters            | A/D 8x8b, 8x10b; D/A 2x12b                                   |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 64-TQFP                                                      |

| Supplier Device Package    | 64-TQFP (10x10)                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f123r |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

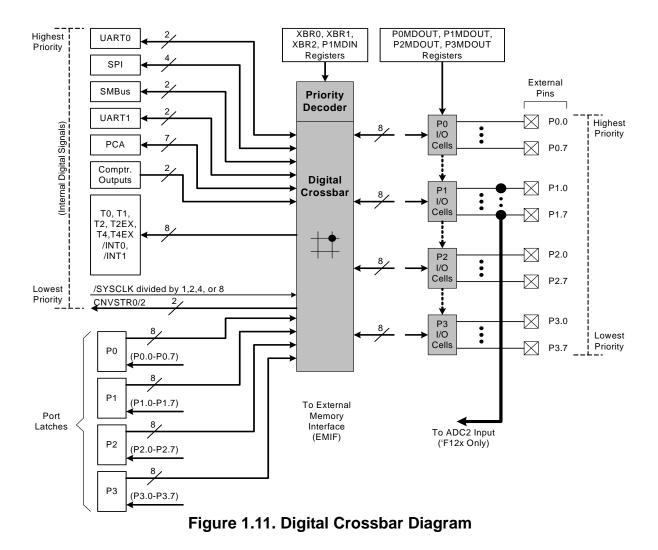

## 1.5. Programmable Digital I/O and Crossbar

The standard 8051 8-bit Ports (0, 1, 2, and 3) are available on the MCUs. The devices in the larger (100pin TQFP) packaging have 4 additional ports (4, 5, 6, and 7) for a total of 64 general-purpose port I/O. The Port I/O behave like the standard 8051 with a few enhancements.

Each Port I/O pin can be configured as either a push-pull or open-drain output. Also, the "weak pullups" which are normally fixed on an 8051 can be globally disabled, providing additional power saving capabilities for low-power applications.

Perhaps the most unique enhancement is the Digital Crossbar. This is a large digital switching network that allows mapping of internal digital system resources to Port I/O pins on P0, P1, P2, and P3. (See Figure 1.11) Unlike microcontrollers with standard multiplexed digital I/O, all combinations of functions are supported.

The on-chip counter/timers, serial buses, HW interrupts, ADC Start of Conversion inputs, comparator outputs, and other digital signals in the controller can be configured to appear on the Port I/O pins specified in the Crossbar Control registers. This allows the user to select the exact mix of general purpose Port I/O and digital resources needed for the particular application.

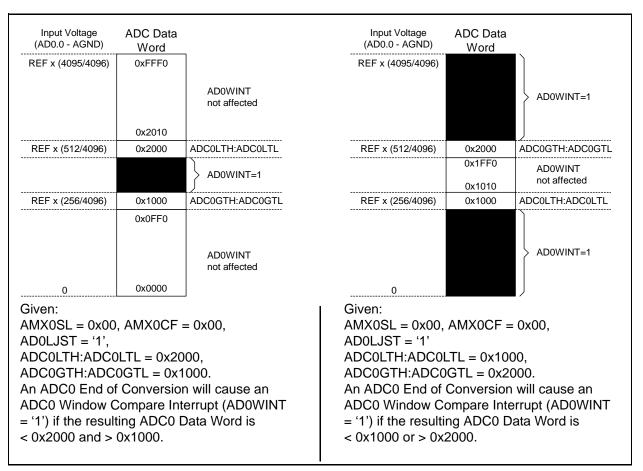

Figure 5.8. 12-Bit ADC0 Window Interrupt Example: Left Justified Single-Ended Data

| SFR Page:<br>SFR Addre                                                                                                                                                                                                                                                                                                                                                          |                                                                          |        |        |        |         |         |            |             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------|--------|--------|---------|---------|------------|-------------|

| R/W                                                                                                                                                                                                                                                                                                                                                                             | R/W                                                                      | R/W    | R/W    | R/W    | R/W     | R/W     | R/W        | Reset Value |

| AD0SC                                                                                                                                                                                                                                                                                                                                                                           | 4 AD0SC3                                                                 | AD0SC2 | AD0SC1 | AD0SC0 | AMP0GN2 | AMP0GN1 | AMP0GN     | 0 11111000  |

| Bit7                                                                                                                                                                                                                                                                                                                                                                            | Bit6                                                                     | Bit5   | Bit4   | Bit3   | Bit2    | Bit1    | Bit0       |             |

| <ul> <li>Bits7–3: AD0SC4–0: ADC0 SAR Conversion Clock Period Bits.</li> <li>SAR Conversion clock is derived from system clock by the following equation, where AD0SC refers to the 5-bit value held in AD0SC4-0, and CLK<sub>SAR0</sub> refers to the desired ADC0</li> <li>SAR clock (Note: the ADC0 SAR Conversion Clock should be less than or equal to 2.5 MHz).</li> </ul> |                                                                          |        |        |        |         |         |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                 | $AD0SC = \frac{SYSCLK}{2 \times CLK_{SAR0}} - 1 \qquad (AD0SC > 00000b)$ |        |        |        |         |         |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                 | When the AD to facilitate fa                                             |        | •      |        |         |         | is equal t | to SYSCLK   |

| Bits2–0: AMP0GN2–0: ADC0 Internal Amplifier Gain (PGA).                                                                                                                                                                                                                                                                                                                         |                                                                          |        |        |        |         |         |            |             |

| BROL OF                                                                                                                                                                                                                                                                                                                                                                         | 000: Gain = 1                                                            |        |        |        |         |         |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                 | 001: Gain = 2                                                            |        |        |        |         |         |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                 | 010: Gain = 4                                                            |        |        |        |         |         |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                 | 011: Gain = 8                                                            |        |        |        |         |         |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                 | 10x: Gain = 1                                                            | •      |        |        |         |         |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                 | 11x: Gain = 0.5                                                          |        |        |        |         |         |            |             |

### SFR Definition 6.3. ADC0CF: ADC0 Configuration

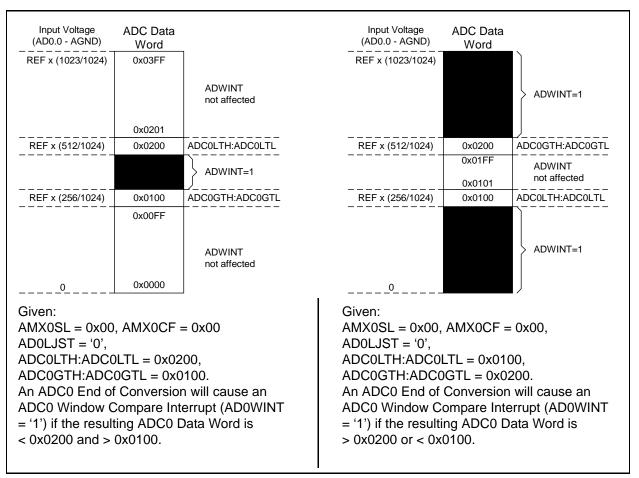

Figure 6.6. 10-Bit ADC0 Window Interrupt Example: Right Justified Single-Ended Data

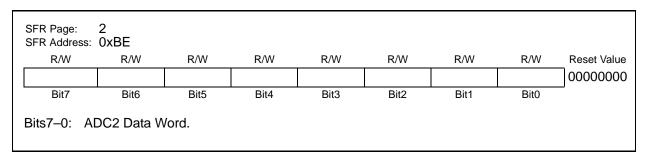

#### SFR Definition 7.5. ADC2: ADC2 Data Word

|                                                                                                                                                  |                                                                                                | 00)                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| AIN2.0–AGND<br>(Volts)                                                                                                                           | ADC2                                                                                           | 1                                                                                         |

| VREF * (255/256)                                                                                                                                 | 0xFF                                                                                           | 1                                                                                         |

| VREF * (128/256)                                                                                                                                 | 0x80                                                                                           | -                                                                                         |

| VREF * (64/256)                                                                                                                                  | 0x40                                                                                           | 7                                                                                         |

| 0                                                                                                                                                | 0x00                                                                                           | 7                                                                                         |

| Example: ADC2 Data                                                                                                                               | e:<br>d appears in the AD                                                                      | <b>DC2 Data Word Register as follows:</b><br>1ap, Differential AIN2.0-AIN2.1 Input<br>00) |

| Differential Example<br>8-bit ADC Data Wor<br>Example: ADC2 Data<br>(AMX2CF =<br>AIN2.0-AIN2.1                                                   | e:<br>d appears in the AD<br>a Word Conversion M                                               | 1ap, Differential AIN2.0-AIN2.1 Input                                                     |

| Differential Example<br>8-bit ADC Data Wor<br>Example: ADC2 Data<br>(AMX2CF =<br>AIN2.0-AIN2.1<br>(Volts)                                        | e:<br>d appears in the AD<br>a Word Conversion M<br>0x01; AMX2SL = 0x0                         | 1ap, Differential AIN2.0-AIN2.1 Input                                                     |

| Differential Example<br>8-bit ADC Data Wor<br>Example: ADC2 Data<br>(AMX2CF =<br>AIN2.0-AIN2.1<br>(Volts)                                        | e:<br>d appears in the AD<br>a Word Conversion M<br>0x01; AMX2SL = 0x0<br>ADC2                 | 1ap, Differential AIN2.0-AIN2.1 Input                                                     |

| Differential Example<br>8-bit ADC Data Wor<br>Example: ADC2 Data<br>(AMX2CF =<br>AIN2.0–AIN2.1<br>(Volts)<br>VREF * (127/128)                    | e:<br>d appears in the AD<br>a Word Conversion M<br>0x01; AMX2SL = 0x0<br>ADC2<br>0x7F         | 1ap, Differential AIN2.0-AIN2.1 Input                                                     |

| Differential Example<br>8-bit ADC Data Wor<br>Example: ADC2 Data<br>(AMX2CF =<br>AIN2.0–AIN2.1<br>(Volts)<br>VREF * (127/128)<br>VREF * (64/128) | e:<br>d appears in the AD<br>a Word Conversion M<br>0x01; AMX2SL = 0x0<br>ADC2<br>0x7F<br>0x40 | 1ap, Differential AIN2.0-AIN2.1 Input                                                     |

#### Figure 7.4. ADC2 Data Word Example

### Table 7.1. ADC2 Electrical Characteristics

$V_{DD}$  = 3.0 V, AV+ = 3.0 V, VREF2 = 2.40 V (REFBE = 0), PGA gain = 1, -40 to +85 °C unless otherwise specified.

| Parameter                                      | Conditions                         | Min     | Тур       | Max       | Units  |  |  |

|------------------------------------------------|------------------------------------|---------|-----------|-----------|--------|--|--|

| DC Accuracy                                    |                                    |         |           |           |        |  |  |

| Resolution                                     |                                    |         | 8         |           | bits   |  |  |

| Integral Nonlinearity                          |                                    | -       |           | ±1        | LSB    |  |  |

| Differential Nonlinearity                      | Guaranteed Monotonic               |         | _         | ±1        | LSB    |  |  |

| Offset Error                                   |                                    |         | 0.5±0.3   | -         | LSB    |  |  |

| Full Scale Error                               | Differential mode                  | -       | -1±0.2    | —         | LSB    |  |  |

| Offset Temperature Coefficient                 |                                    | —       | 10        | —         | ppm/°C |  |  |

| Dynamic Performance                            | (10 kHz sine-wave input, 1 dB      | below F | ull Scale | , 500 ksp | os     |  |  |

| Signal-to-Noise Plus Distortion                |                                    | 45      | 47        | —         | dB     |  |  |

| Total Harmonic Distortion                      | Up to the 5 <sup>th</sup> harmonic | _       | -51       | _         | dB     |  |  |

| Spurious-Free Dynamic Range                    |                                    | _       | 52        | _         | dB     |  |  |

|                                                | Conversion Rate                    | 1       | 1         |           |        |  |  |

| SAR Clock Frequency                            |                                    |         |           | 6         | MHz    |  |  |

| Conversion Time in SAR Clocks                  |                                    | 8       |           |           | clocks |  |  |

| Track/Hold Acquisition Time                    |                                    | 300     |           |           | ns     |  |  |

| Throughput Rate                                |                                    | _       |           | 500       | ksps   |  |  |

| Analog Inputs                                  |                                    |         |           |           |        |  |  |

| Input Voltage Range                            |                                    | 0       |           | VREF      | V      |  |  |

| Input Capacitance                              |                                    | -       | 5         | —         | pF     |  |  |

| Power Specifications                           |                                    |         |           |           |        |  |  |

| Power Supply Current<br>(AV+ supplied to ADC2) | Operating Mode, 500 ksps           | —       | 420       | 900       | μA     |  |  |

| Power Supply Rejection                         |                                    | -       | ±0.3      | —         | mV/V   |  |  |

### 8.1.1. Update Output On-Demand

In its default mode (DAC0CN.[4:3] = '00') the DAC0 output is updated "on-demand" on a write to the highbyte of the DAC0 data register (DAC0H). It is important to note that writes to DAC0L are held, and have no effect on the DAC0 output until a write to DAC0H takes place. If writing a full 12-bit word to the DAC data registers, the 12-bit data word is written to the low byte (DAC0L) and high byte (DAC0H) data registers. Data is latched into DAC0 after a write to the corresponding DAC0H register, **so the write sequence should be DAC0L followed by DAC0H** if the full 12-bit resolution is required. The DAC can be used in 8bit mode by initializing DAC0L to the desired value (typically 0x00), and writing data to only DAC0H (also see **Section 8.2** for information on formatting the 12-bit DAC data word within the 16-bit SFR space).

#### 8.1.2. Update Output Based on Timer Overflow

Similar to the ADC operation, in which an ADC conversion can be initiated by a timer overflow independently of the processor, the DAC outputs can use a Timer overflow to schedule an output update event. This feature is useful in systems where the DAC is used to generate a waveform of a defined sampling rate by eliminating the effects of variable interrupt latency and instruction execution on the timing of the DAC output. When the DACOMD bits (DACOCN.[4:3]) are set to '01', '10', or '11', writes to both DAC data registers (DACOL and DACOH) are held until an associated Timer overflow event (Timer 3, Timer 4, or Timer 2, respectively) occurs, at which time the DACOH:DACOL contents are copied to the DAC input latches allowing the DAC output to change to the new value.

### 8.2. DAC Output Scaling/Justification

In some instances, input data should be shifted prior to a DAC0 write operation to properly justify data within the DAC input registers. This action would typically require one or more load and shift operations, adding software overhead and slowing DAC throughput. To alleviate this problem, the data-formatting feature provides a means for the user to program the orientation of the DAC0 data word within data registers DAC0H and DAC0L. The three DAC0DF bits (DAC0CN.[2:0]) allow the user to specify one of five data word orientations as shown in the DAC0CN register definition.

DAC1 is functionally the same as DAC0 described above. The electrical specifications for both DAC0 and DAC1 are given in Table 8.1.

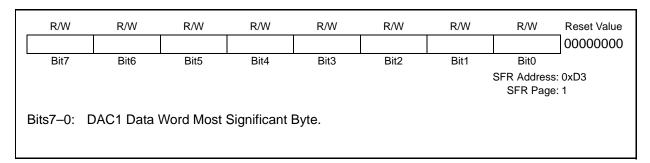

## SFR Definition 8.4. DAC1H: DAC1 High Byte

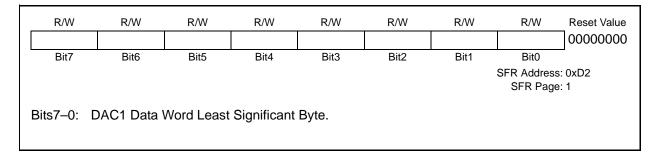

## SFR Definition 8.5. DAC1L: DAC1 Low Byte

# 9. Voltage Reference

The voltage reference options available on the C8051F12x and C8051F13x device families vary according to the device capabilities.

All devices include an internal voltage reference circuit, consisting of a 1.2 V, 15 ppm/°C (typical) bandgap voltage reference generator and a gain-of-two output buffer amplifier. The internal reference may be routed via the VREF pin to external system components or to the voltage reference input pins. The maximum load seen by the VREF pin must be less than 200  $\mu$ A to AGND. Bypass capacitors of 0.1  $\mu$ F and 4.7  $\mu$ F are recommended from the VREF pin to AGND.

The Reference Control Register, REF0CN enables/disables the internal reference generator and the internal temperature sensor on all devices. The BIASE bit in REF0CN enables the on-board reference generator while the REFBE bit enables the gain-of-two buffer amplifier which drives the VREF pin. When disabled, the supply current drawn by the bandgap and buffer amplifier falls to less than 1  $\mu$ A (typical) and the output of the buffer amplifier enters a high impedance state. If the internal bandgap is used as the reference voltage generator, BIASE and REFBE must both be set to logic 1. If the internal reference is not used, REFBE may be set to logic 0. Note that the BIASE bit must be set to logic 1 if any DACs or ADCs are used, regardless of whether the voltage reference is derived from the on-chip reference or supplied by an off-chip source. If no ADCs or DACs are being used, both of these bits can be set to logic 0 to conserve power.

When enabled, the temperature sensor connects to the highest order input of the ADC0 input multiplexer. The TEMPE bit within REF0CN enables and disables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state. Any ADC measurements performed on the sensor while disabled will result in undefined data.

The electrical specifications for the internal voltage reference are given in Table 9.1.

#### 9.1. Reference Configuration on the C8051F120/2/4/6

On the C8051F120/2/4/6 devices, the REF0CN register also allows selection of the voltage reference source for ADC0 and ADC2, as shown in SFR Definition 9.1. Bits AD0VRS and AD2VRS in the REF0CN register select the ADC0 and ADC2 voltage reference sources, respectively. Three voltage reference input pins allow each ADC and the two DACs to reference an external voltage reference or the on-chip voltage reference output (with an external connection). ADC0 may also reference the DAC0 output internally, and ADC2 may reference the analog power supply voltage, via the VREF multiplexers shown in Figure 9.1.

| Mnemonic             | Description                                                                                                 | Bytes | Clock<br>Cycles |

|----------------------|-------------------------------------------------------------------------------------------------------------|-------|-----------------|

| JZ rel               | Jump if A equals zero                                                                                       | 2     | 2/3*            |

| JNZ rel              | Jump if A does not equal zero                                                                               | 2     | 2/3*            |

| CJNE A, direct, rel  | Compare direct byte to A and jump if not equal                                                              | 3     | 3/4*            |

| CJNE A, #data, rel   | Compare immediate to A and jump if not equal                                                                | 3     | 3/4*            |

| CJNE Rn, #data, rel  | Compare immediate to Register and jump if not equal                                                         | 3     | 3/4*            |

| CJNE @Ri, #data, rel | Compare immediate to indirect and jump if not equal                                                         | 3     | 4/5*            |

| DJNZ Rn, rel         | Decrement Register and jump if not zero                                                                     | 2     | 2/3*            |

| DJNZ direct, rel     | Decrement direct byte and jump if not zero                                                                  | 3     | 3/4*            |

| NOP                  | No operation                                                                                                | 1     | 1               |

|                      | incur a cache-miss penalty if the branch target location<br>See Section "16. Branch Target Cache" on page 2 |       |                 |

### Table 11.1. CIP-51 Instruction Set Summary (Continued)

#### Notes on Registers, Operands and Addressing Modes:

Rn - Register R0-R7 of the currently selected register bank.

**@Ri** - Data RAM location addressed indirectly through R0 or R1.

**rel** - 8-bit, signed (2s complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct** - 8-bit internal data location's address. This could be a direct-access Data RAM location (0x00-0x7F) or an SFR (0x80-0xFF).

#data - 8-bit constant

#data16 - 16-bit constant

bit - Direct-accessed bit in Data RAM or SFR

**addr11** - 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2K-byte page of program memory as the first byte of the following instruction.

**addr16** - 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 64K-byte program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

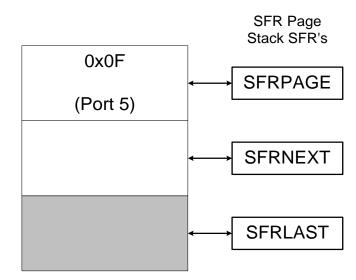

#### 11.2.6.3.SFR Page Stack Example

The following is an example that shows the operation of the SFR Page Stack during interrupts.

In this example, the SFR Page Control is left in the default enabled state (i.e., SFRPGEN = 1), and the CIP-51 is executing in-line code that is writing values to Port 5 (SFR "P5", located at address 0xD8 on SFR Page 0x0F). The device is also using the Programmable Counter Array (PCA) and the 10-bit ADC (ADC2) window comparator to monitor a voltage. The PCA is timing a critical control function in its interrupt service routine (ISR), so its interrupt is enabled and is set to *high* priority. The ADC2 is monitoring a voltage that is less important, but to minimize the software overhead its window comparator is being used with an associated ISR that is set to *low* priority. At this point, the SFR page is set to access the Port 5 SFR (SFRPAGE = 0x0F). See Figure 11.5 below.

### Figure 11.5. SFR Page Stack While Using SFR Page 0x0F To Access Port 5

While CIP-51 executes in-line code (writing values to Port 5 in this example), ADC2 Window Comparator Interrupt occurs. The CIP-51 vectors to the ADC2 Window Comparator ISR and pushes the current SFR Page value (SFR Page 0x0F) into SFRNEXT in the SFR Page Stack. The SFR page needed to access ADC2's SFR's is then automatically placed in the SFRPAGE register (SFR Page 0x02). SFRPAGE is considered the "top" of the SFR Page Stack. Software can now access the ADC2 SFR's. Software may switch to any SFR Page by writing a new value to the SFRPAGE register at any time during the ADC2 ISR to access SFR's that are not on SFR Page 0x02. See Figure 11.6 below.

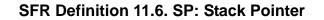

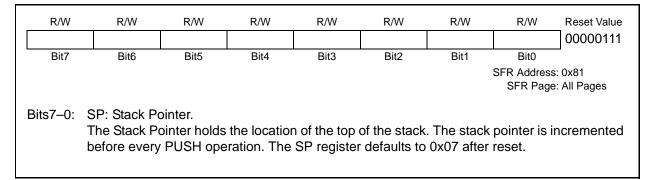

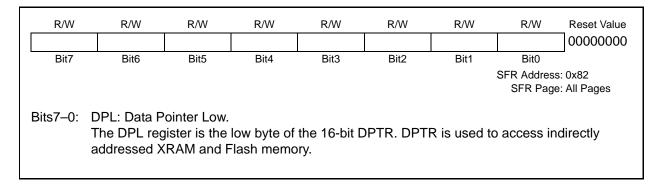

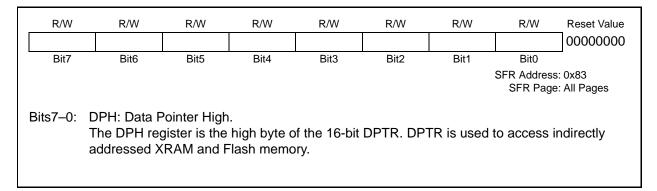

#### 11.2.7. Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should not be set to logic I. Future product versions may use these bits to implement new features in which case the reset value of the bit will be logic 0, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the datasheet associated with their corresponding system function.

## SFR Definition 11.7. DPL: Data Pointer Low Byte

### SFR Definition 11.8. DPH: Data Pointer High Byte

Certain types of instruction data or certain blocks of code can also be excluded from caching. The destinations of RETI instructions are, by default, excluded from caching. To enable caching of RETI destinations, the CHRETI bit (CCH0CN.3) can be set to '1'. It is generally not beneficial to cache RETI destinations unless the same instruction is likely to be interrupted repeatedly (such as a code loop that is waiting for an interrupt to happen). Instructions that are part of an interrupt service routine (ISR) can also be excluded from caching. By default, ISR instructions are cached, but this can be disabled by clearing the CHISR bit (CCH0CN.2) to '0'. The other information that can be explicitly excluded from caching are the data returned by MOVC instructions. Clearing the CHMOV bit (CCH0CN.1) to '0' will disable caching of MOVC data. If MOVC caching is allowed, it can be restricted to only use slot 0 for the MOVC information (excluding cache push operations). The CHFIXM bit (CCH0TN.2) controls this behavior.

Further cache control can be implemented by disabling all cache writes. Cache writes can be disabled by clearing the CHWREN bit (CCH0CN.7) to '0'. Although normal cache writes (such as those after a cache miss) are disabled, data can still be written to the cache with a cache push operation. Disabling cache writes can be used to prevent a non-critical section of code from changing the cache contents. Note that regardless of the value of CHWREN, a Flash write or erase operation automatically removes the affected bytes from the cache. Cache reads and the prefetch engine can also be individually disabled. Disabling cache reads forces all instructions data to execute from Flash memory or from the prefetch engine. To disable cache reads, the CHRDEN bit (CCH0CN.6) can be cleared to '0'. Note that when cache reads are disabled, cache writes will still occur (if CHWREN is set to '1'). Disabling the prefetch engine is accomplished using the CHPFEN bit (CCH0CN.5). When this bit is cleared to '0', the prefetch engine will be disabled. If both CHPFEN and CHRDEN are '0', code will execute at a fixed rate, as instructions become available from the Flash memory.

Cache locations can also be pre-loaded and locked with time-critical branch destinations. For example, in a system with an ISR that must respond as fast as possible, the entry point for the ISR can be locked into a cache location to minimize the response latency of the ISR. Up to 61 locations can be locked into the cache at one time. Instructions are locked into cache by enabling cache push operations with the CHPUSH bit (CCH0LC.7). When CHPUSH is set to '1', a MOVC instruction will cause the four-byte segment containing the data byte to be written to the cache slot location indicated by CHSLOT (CCH0LC.5-0). CHSLOT is them decremented to point to the next lockable cache location. This process is called a cache push operation. Cache locations that are above CHSLOT are "locked", and cannot be changed by the processor core, as shown in Figure 16.3. Cache locations can be unlocked by using a cache pop operation. A cache pop is performed by writing a '1' to the CHPOP bit (CCH0LC.6). When a cache pop is initiated, the value of CHSLOT is incremented. This unlocks the most recently locked cache location, but does not remove the information from the cache. Note that a cache pop should not be initiated if CHSLOT is equal to 111110b. Doing so may have an adverse effect on cache performance. Important: Although locking cache location 1 is not explicitly disabled by hardware, the entire cache will be unlocked when CHSLOT is equal to 000000b. Therefore, cache locations 1 and 0 must remain unlocked at all times.

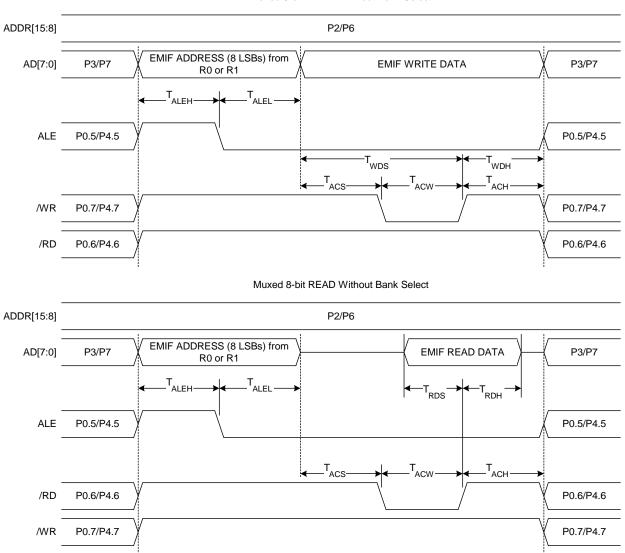

#### 17.6.2.2.8-bit MOVX without Bank Select: EMI0CF[4:2] = '001' or '011'.

Muxed 8-bit WRITE Without Bank Select

Figure 17.8. Multiplexed 8-bit MOVX without Bank Select Timing

ple, to assign TX0 to a Port pin without assigning RX0 as well. Each combination of enabled peripherals results in a unique device pinout.

All Port pins on Ports 0 through 3 that are not allocated by the Crossbar can be accessed as General-Purpose I/O (GPIO) pins by reading and writing the associated Port Data registers (See SFR Definition 18.4, SFR Definition 18.6, SFR Definition 18.9, and SFR Definition 18.11), a set of SFR's which are both byteand bit-addressable. The output states of Port pins that are allocated by the Crossbar are controlled by the digital peripheral that is mapped to those pins. Writes to the Port Data registers (or associated Port bits) will have no effect on the states of these pins.

A Read of a Port Data register (or Port bit) will always return the logic state present at the pin itself, regardless of whether the Crossbar has allocated the pin for peripheral use or not. An exception to this occurs during the execution of a *read-modify-write* instruction (ANL, ORL, XRL, CPL, INC, DEC, DJNZ, JBC, CLR, SETB, and the bitwise MOV write operation). During the *read* cycle of the *read-modify-write* instruction, it is the contents of the Port Data register, not the state of the Port pins themselves, which is read. Note that at clock rates above 50 MHz, when a pin is written and then immediately read (i.e. a write instruction followed immediately by a read instruction), the propagation delay of the port drivers may cause the read instruction to return the previous logic level of the pin.

Because the Crossbar registers affect the pinout of the peripherals of the device, they are typically configured in the initialization code of the system before the peripherals themselves are configured. Once configured, the Crossbar registers are typically left alone.

Once the Crossbar registers have been properly configured, the Crossbar is enabled by setting XBARE (XBR2.4) to a logic 1. Until XBARE is set to a logic 1, the output drivers on Ports 0 through 3 are explicitly disabled in order to prevent possible contention on the Port pins while the Crossbar registers and other registers which can affect the device pinout are being written.

The output drivers on Crossbar-assigned input signals (like RX0, for example) are explicitly disabled; thus the values of the Port Data registers and the PnMDOUT registers have no effect on the states of these pins.

#### **18.1.2. Configuring the Output Modes of the Port Pins**

The output drivers on Ports 0 through 3 remain disabled until the Crossbar is enabled by setting XBARE (XBR2.4) to a logic 1.

The output mode of each port pin can be configured to be either Open-Drain or Push-Pull. In the Push-Pull configuration, writing a logic 0 to the associated bit in the Port Data register will cause the Port pin to be driven to GND, and writing a logic 1 will cause the Port pin to be driven to  $V_{DD}$ . In the Open-Drain configuration, writing a logic 0 to the associated bit in the Port Data register will cause the Port pin to be driven to GND, and a logic 1 will cause the Port pin to assume a high-impedance state. The Open-Drain configuration is useful to prevent contention between devices in systems where the Port pin participates in a shared interconnection in which multiple outputs are connected to the same physical wire (like the SDA signal on an SMBus connection).

The output modes of the Port pins on Ports 0 through 3 are determined by the bits in the associated PnMDOUT registers (See SFR Definition 18.5, SFR Definition 18.8, SFR Definition 18.10, and SFR Definition 18.12). For example, a logic 1 in P3MDOUT.7 will configure the output mode of P3.7 to Push-Pull; a logic 0 in P3MDOUT.7 will configure the output mode of P3.7 to Open-Drain. All Port pins default to Open-Drain output.

|      |                                                                                                            | · ·                                                                               |

|------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

|      |                                                                                                            |                                                                                   |

| 0x60 | Own slave address + W received. ACK trans-<br>mitted.                                                      | Wait for data.                                                                    |

| 0x68 | Arbitration lost in sending SLA + R/W as mas-<br>ter. Own address + W received. ACK transmit-<br>ted.      | Save current data for retry when bus is free. Wait for data.                      |

| 0x70 | General call address received. ACK transmit-<br>ted.                                                       | Wait for data.                                                                    |

| 0x78 | Arbitration lost in sending SLA + R/W as mas-<br>ter. General call address received. ACK trans-<br>mitted. | Save current data for retry when bus is free.                                     |

| 0x80 | Data byte received. ACK transmitted.                                                                       | Read SMB0DAT. Wait for next byte or STOP.                                         |

| 0x88 | Data byte received. NACK transmitted.                                                                      | Set STO to reset SMBus.                                                           |

| 0x90 | Data byte received after general call address.<br>ACK transmitted.                                         | Read SMB0DAT. Wait for next byte or STOP.                                         |

| 0x98 | Data byte received after general call address.<br>NACK transmitted.                                        | Set STO to reset SMBus.                                                           |

| 0xA0 | STOP or repeated START received.                                                                           | No action necessary.                                                              |

| 0xA8 | Own address + R received. ACK transmitted.                                                                 | Load SMB0DAT with data to transmit.                                               |

| 0xB0 | Arbitration lost in transmitting SLA + R/W as<br>master. Own address + R received. ACK<br>transmitted.     | Save current data for retry when bus is free. Load SMB0DAT with data to transmit. |

| 0xB8 | Data byte transmitted. ACK received.                                                                       | Load SMB0DAT with data to transmit.                                               |

| 0xC0 | Data byte transmitted. NACK received.                                                                      | Wait for STOP.                                                                    |

| 0xC8 | Last data byte transmitted (AA=0). ACK received.                                                           | Set STO to reset SMBus.                                                           |

| 0xD0 | SCL Clock High Timer per SMB0CR timed out                                                                  | Set STO to reset SMBus.                                                           |

| 0x00 | Bus Error (illegal START or STOP)                                                                          | Set STO to reset SMBus.                                                           |

| 0xF8 | Idle                                                                                                       | State does not set SI.                                                            |

|      |                                                                                                            |                                                                                   |

## Table 19.1. SMB0STA Status Codes and States (Continued)

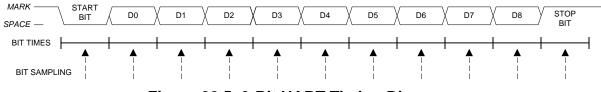

#### 22.2.2. 9-Bit UART

9-bit UART mode uses a total of eleven bits per data byte: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. The state of the ninth transmit data bit is determined by the value in TB81 (SCON1.3), which is assigned by user software. It can be assigned the value of the parity flag (bit P in register PSW) for error detection, or used in multiprocessor communications. On receive, the ninth data bit goes into RB81 (SCON1.2) and the stop bit is ignored.

Data transmission begins when an instruction writes a data byte to the SBUF1 register. The TI1 Transmit Interrupt Flag (SCON1.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN1 Receive Enable bit (SCON1.4) is set to '1'. After the stop bit is received, the data byte will be loaded into the SBUF1 receive register if the following conditions are met: (1) RI1 must be logic 0, and (2) if MCE1 is logic 1, the 9th bit must be logic 1 (when MCE1 is logic 0, the state of the ninth data bit is unimportant). If these conditions are met, the eight bits of data are stored in SBUF1, the ninth bit is stored in RB81, and the RI1 flag is set to '1'. A UART1 interrupt will occur if enabled when either TI1 or RI1 is set to '1'.

Figure 22.5. 9-Bit UART Timing Diagram

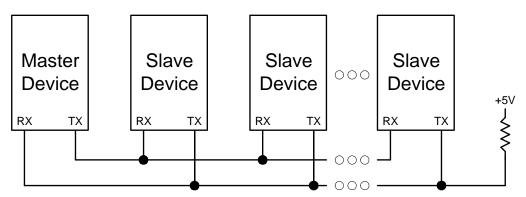

#### 22.3. Multiprocessor Communications

9-Bit UART mode supports multiprocessor communication between a master processor and one or more slave processors by special use of the ninth data bit. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its ninth bit is logic 1; in a data byte, the ninth bit is always set to logic 0.

Setting the MCE1 bit (SCON.5) of a slave processor configures its UART such that when a stop bit is received, the UART will generate an interrupt only if the ninth bit is logic one (RB81 = 1) signifying an address byte has been received. In the UART interrupt handler, software should compare the received address with the slave's own assigned 8-bit address. If the addresses match, the slave should clear its MCE1 bit to enable interrupts on the reception of the following data byte(s). Slaves that weren't addressed leave their MCE1 bits set and do not generate interrupts on the reception of the following data bytes, thereby ignoring the data. Once the entire message is received, the addressed slave should reset its MCE1 bit to ignore all transmissions until it receives the next address byte.

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s).

Figure 22.6. UART Multi-Processor Mode Interconnect Diagram

# 23. Timers

Each MCU includes 5 counter/timers: Timer 0 and Timer 1 are 16-bit counter/timers compatible with those found in the standard 8051. Timer 2, Timer 3, and Timer 4 are 16-bit auto-reload and capture counter/timers for use with the ADCs, DACs, square-wave generation, or for general-purpose use. These timers can be used to measure time intervals, count external events and generate periodic interrupt requests. Timer 0 and Timer 1 are nearly identical and have four primary modes of operation. Timer 3 offers 16-bit auto-reload and capture. Timers 2 and 4 are identical, and offer not only 16-bit auto-reload and capture, but have the ability to produce a 50% duty-cycle square-wave (toggle output) at an external port pin.

| Timer 0 and Timer 1 Modes:              | Timer 2, 3 and 4 Modes:               |

|-----------------------------------------|---------------------------------------|

| 13-bit counter/timer                    | 16-bit counter/timer with auto-reload |

| 16-bit counter/timer                    | 16-bit counter/timer with capture     |

| 8-bit counter/timer with auto-reload    | Toggle Output (Timer 2 and 4 only)    |

| Two 8-bit counter/timers (Timer 0 only) |                                       |

Timers 0 and 1 may be clocked by one of five sources, determined by the Timer Mode Select bits (T1M-T0M) and the Clock Scale bits (SCA1-SCA0). The Clock Scale bits define a pre-scaled clock by which Timer 0 and/or Timer 1 may be clocked (See SFR Definition 23.3 for pre-scaled clock selection). Timers 0 and 1 can be configured to use either the pre-scaled clock signal or the system clock directly. Timers 2, 3, and 4 may be clocked by the system clock, the system clock divided by 12, or the external oscillator clock source divided by 8.

Timer 0 and Timer 1 may also be operated as counters. When functioning as a counter, a counter/timer register is incremented on each high-to-low transition at the selected input pin. Events with a frequency of up to one-fourth the system clock's frequency can be counted. The input signal need not be periodic, but it should be held at a given logic level for at least two full system clock cycles to ensure the level is properly sampled.

### 23.1. Timer 0 and Timer 1

Each timer is implemented as a 16-bit register accessed as two separate 8-bit SFRs: a low byte (TL0 or TL1) and a high byte (TH0 or TH1). The Counter/Timer Control register (TCON) is used to enable Timer 0 and Timer 1 as well as indicate their status. Timer 0 interrupts can be enabled by setting the ET0 bit in the IE register (Section "11.3.5. Interrupt Register Descriptions" on page 157); Timer 1 interrupts can be enabled by setting the ET1 bit in the IE register (Section 11.3.5). Both counter/timers operate in one of four primary modes selected by setting the Mode Select bits T1M1–T0M0 in the Counter/Timer Mode register (TMOD). Both timers can be configured independently.

#### 23.1.1. Mode 0: 13-bit Counter/Timer

Timer 0 and Timer 1 operate as 13-bit counter/timers in Mode 0. The following describes the configuration and operation of Timer 0. However, both timers operate identically, and Timer 1 is configured in the same manner as described for Timer 0.

The TH0 register holds the eight MSBs of the 13-bit counter/timer. TL0 holds the five LSBs in bit positions TL0.4–TL0.0. The three upper bits of TL0 (TL0.7–TL0.5) are indeterminate and should be masked out or ignored when reading the TL0 register. As the 13-bit timer register increments and overflows from 0x1FFF (all ones) to 0x0000, the timer overflow flag TF0 (TCON.5) is set and an interrupt will occur if Timer 0 interrupts are enabled.