# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 64                                                             |

| Program Memory Size        | 128KB (128K x 8)                                               |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 8.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 8x8b, 8x12b; D/A 2x12b                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 100-TQFP                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f124-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 17.5.3.Split Mode with Bank Select                       | 225 |

|----------------------------------------------------------|-----|

| 17.5.4.External Only                                     |     |

| 17.6.EMIF Timing                                         |     |

| 17.6.1.Non-multiplexed Mode                              |     |

| 17.6.2.Multiplexed Mode                                  |     |

| 18. Port Input/Output                                    | 235 |

| 18.1.Ports 0 through 3 and the Priority Crossbar Decoder | 238 |

| 18.1.1.Crossbar Pin Assignment and Allocation            |     |

| 18.1.2.Configuring the Output Modes of the Port Pins     | 239 |

| 18.1.3.Configuring Port Pins as Digital Inputs           | 240 |

| 18.1.4.Weak Pullups                                      | 240 |

| 18.1.5.Configuring Port 1 Pins as Analog Inputs          | 240 |

| 18.1.6.External Memory Interface Pin Assignments         | 241 |

| 18.1.7.Crossbar Pin Assignment Example                   | 243 |

| 18.2.Ports 4 through 7 (100-pin TQFP devices only)       | 252 |

| 18.2.1.Configuring Ports which are not Pinned Out        | 252 |

| 18.2.2.Configuring the Output Modes of the Port Pins     | 252 |

| 18.2.3.Configuring Port Pins as Digital Inputs           |     |

| 18.2.4.Weak Pullups                                      | 253 |

| 18.2.5.External Memory Interface                         |     |

| 19. System Management Bus / I2C Bus (SMBus0)             |     |

| 19.1.Supporting Documents                                |     |

| 19.2.SMBus Protocol                                      |     |

| 19.2.1.Arbitration                                       |     |

| 19.2.2.Clock Low Extension                               |     |

| 19.2.3.SCL Low Timeout                                   |     |

| 19.2.4.SCL High (SMBus Free) Timeout                     | 261 |

| 19.3.SMBus Transfer Modes                                |     |

| 19.3.1.Master Transmitter Mode                           |     |

| 19.3.2.Master Receiver Mode                              |     |

| 19.3.3.Slave Transmitter Mode                            |     |

| 19.3.4.Slave Receiver Mode                               |     |

| 19.4.SMBus Special Function Registers                    |     |

| 19.4.1.Control Register                                  |     |

| 19.4.2.Clock Rate Register                               |     |

| 19.4.3.Data Register                                     |     |

| 19.4.4.Address Register                                  |     |

| 19.4.5.Status Register                                   |     |

| 20. Enhanced Serial Peripheral Interface (SPI0)          |     |

| 20.1.Signal Descriptions                                 | 274 |

| 20.1.1.Master Out, Slave In (MOSI)                       |     |

| 20.1.2.Master In, Slave Out (MISO)                       |     |

| 20.1.3.Serial Clock (SCK)                                |     |

| 20.1.4.Slave Select (NSS)                                | 2/4 |

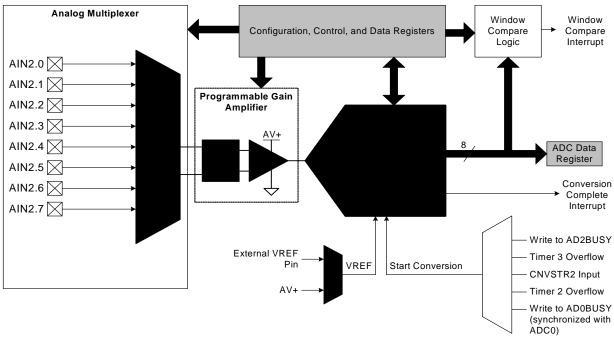

#### 1.9. 8-Bit Analog to Digital Converter

The C8051F12x devices have an on-board 8-bit SAR ADC (ADC2) with an 8-channel input multiplexer and programmable gain amplifier. This ADC features a 500 ksps maximum throughput and true 8-bit linearity with an INL of ±1LSB. Eight input pins are available for measurement. The ADC is under full control of the CIP-51 microcontroller via the Special Function Registers. The ADC2 voltage reference is selected between the analog power supply (AV+) and an external VREF pin. On the 100-pin TQFP devices, ADC2 has its own dedicated Voltage Reference input pin; on the 64-pin TQFP devices, ADC2 shares a Voltage Reference input pin with ADC0. User software may put ADC2 into shutdown mode to save power.

A programmable gain amplifier follows the analog multiplexer. The gain stage can be especially useful when different ADC input channels have widely varied input voltage signals, or when it is necessary to "zoom in" on a signal with a large DC offset (in differential mode, a DAC could be used to provide the DC offset). The PGA gain can be set in software to 0.5, 1, 2, or 4.

A flexible conversion scheduling system allows ADC2 conversions to be initiated by software commands, timer overflows, or an external input signal. ADC2 conversions may also be synchronized with ADC0 software-commanded conversions. Conversion completions are indicated by a status bit and an interrupt (if enabled), and the resulting 8-bit data word is latched into an SFR upon completion.

Figure 1.14. 8-Bit ADC Diagram

### 4. Pinout and Package Definitions

|                 |                                                                                  | Pin Nu        | mbers          |                |       |                                                                                                                                                                                                                                                                                                      |

|-----------------|----------------------------------------------------------------------------------|---------------|----------------|----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name            | <sup>·</sup> F120<br><sup>·</sup> F122<br><sup>·</sup> F124<br><sup>·</sup> F126 | 'F125         | 'F130<br>'F132 | 'F131<br>'F133 | Туре  | Description                                                                                                                                                                                                                                                                                          |

| V <sub>DD</sub> | 37,<br>64, 90                                                                    | 24,<br>41, 57 | 37,<br>64, 90  | 24,<br>41, 57  |       | Digital Supply Voltage. Must be tied to +2.7 to +3.6 V.                                                                                                                                                                                                                                              |

| DGND            | 38,<br>63, 89                                                                    | 25,<br>40, 56 | 38,<br>63, 89  | 25,<br>40, 56  |       | Digital Ground. Must be tied to Ground.                                                                                                                                                                                                                                                              |

| AV+             | 11, 14                                                                           | 6             | 11, 14         | 6              |       | Analog Supply Voltage. Must be tied to +2.7 to +3.6 V.                                                                                                                                                                                                                                               |

| AGND            | 10, 13                                                                           | 5             | 10, 13         | 5              |       | Analog Ground. Must be tied to Ground.                                                                                                                                                                                                                                                               |

| TMS             | 1                                                                                | 58            | 1              | 58             | D In  | JTAG Test Mode Select with internal pullup.                                                                                                                                                                                                                                                          |

| тск             | 2                                                                                | 59            | 2              | 59             | D In  | JTAG Test Clock with internal pullup.                                                                                                                                                                                                                                                                |

| TDI             | 3                                                                                | 60            | 3              | 60             | D In  | JTAG Test Data Input with internal pullup. TDI is latched on the rising edge of TCK.                                                                                                                                                                                                                 |

| TDO             | 4                                                                                | 61            | 4              | 61             | D Out | JTAG Test Data Output with internal pullup. Data<br>is shifted out on TDO on the falling edge of TCK.<br>TDO output is a tri-state driver.                                                                                                                                                           |

| RST             | 5                                                                                | 62            | 5              | 62             | D I/O | Device Reset. Open-drain output of internal $V_{DD}$ monitor. Is driven low when $V_{DD}$ is $< V_{RST}$ and MONEN is high. An external source can initiate a system reset by driving this pin low.                                                                                                  |

| XTAL1           | 26                                                                               | 17            | 26             | 17             | A In  | Crystal Input. This pin is the return for the inter-<br>nal oscillator circuit for a crystal or ceramic reso-<br>nator. For a precision internal clock, connect a<br>crystal or ceramic resonator from XTAL1 to<br>XTAL2. If overdriven by an external CMOS<br>clock, this becomes the system clock. |

| XTAL2           | 27                                                                               | 18            | 27             | 18             | A Out | Crystal Output. This pin is the excitation driver for a crystal or ceramic resonator.                                                                                                                                                                                                                |

| MONEN           | 28                                                                               | 19            | 28             | 19             | D In  | $V_{DD}$ Monitor Enable. When tied high, this pin<br>enables the internal $V_{DD}$ monitor, which forces a<br>system reset when $V_{DD}$ is < $V_{RST}$ . When tied<br>low, the internal $V_{DD}$ monitor is disabled.<br><b>This pin must be tied high or low.</b>                                  |

#### Table 4.1. Pin Definitions

|          |                                                                                  | Pin Nu | mbers          |                |       |                                                                                                                                            |

|----------|----------------------------------------------------------------------------------|--------|----------------|----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Name     | <sup>•</sup> F120<br><sup>•</sup> F122<br><sup>•</sup> F124<br><sup>•</sup> F126 | _      | 'F130<br>'F132 | 'F131<br>'F133 | Туре  | Description                                                                                                                                |

| ALE/P4.5 | 93                                                                               |        | 93             |                | D I/O | ALE Strobe for External Memory Address bus<br>(multiplexed mode)<br>Port 4.5<br>See Port Input/Output section for complete<br>description. |

| RD/P4.6  | 92                                                                               |        | 92             |                | D I/O | /RD Strobe for External Memory Address bus<br>Port 4.6<br>See Port Input/Output section for complete<br>description.                       |

| WR/P4.7  | 91                                                                               |        | 91             |                | D I/O | /WR Strobe for External Memory Address bus<br>Port 4.7<br>See Port Input/Output section for complete<br>description.                       |

| A8/P5.0  | 88                                                                               |        | 88             |                | D I/O | Bit 8 External Memory Address bus (Non-multi-<br>plexed mode)<br>Port 5.0<br>See Port Input/Output section for complete<br>description.    |

| A9/P5.1  | 87                                                                               |        | 87             |                | D I/O | Port 5.1. See Port Input/Output section for complete description.                                                                          |

| A10/P5.2 | 86                                                                               |        | 86             |                | D I/O | Port 5.2. See Port Input/Output section for complete description.                                                                          |

| A11/P5.3 | 85                                                                               |        | 85             |                | D I/O | Port 5.3. See Port Input/Output section for complete description.                                                                          |

| A12/P5.4 | 84                                                                               |        | 84             |                | D I/O | Port 5.4. See Port Input/Output section for complete description.                                                                          |

| A13/P5.5 | 83                                                                               |        | 83             |                | D I/O | Port 5.5. See Port Input/Output section for complete description.                                                                          |

| A14/P5.6 | 82                                                                               |        | 82             |                | D I/O | Port 5.6. See Port Input/Output section for complete description.                                                                          |

| A15/P5.7 | 81                                                                               |        | 81             |                | D I/O | Port 5.7. See Port Input/Output section for complete description.                                                                          |

#### Table 4.1. Pin Definitions (Continued)

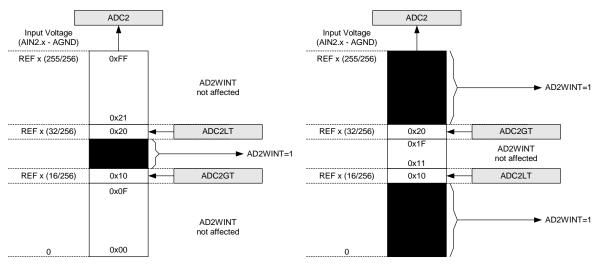

### 7.3. ADC2 Programmable Window Detector

The ADC2 Programmable Window Detector continuously compares the ADC2 output to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD2WINT in register ADC2CN) can also be used in polled mode. The ADC2 Greater-Than (ADC2GT) and Less-Than (ADC2LT) registers hold the comparison values. Example comparisons for Differential and Single-ended modes are shown in Figure 7.6 and Figure 7.5, respectively. Notice that the window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC2LT and ADC2GT registers.

#### 7.3.1. Window Detector In Single-Ended Mode

Figure 7.5 shows two example window comparisons for Single-ended mode, with ADC2LT = 0x20 and ADC2GT = 0x10. Notice that in Single-ended mode, the codes vary from 0 to VREF\*(255/256) and are represented as 8-bit unsigned integers. In the left example, an AD2WINT interrupt will be generated if the ADC2 conversion word (ADC2) is within the range defined by ADC2GT and ADC2LT (if 0x10 < ADC2 < 0x20). In the right example, and AD2WINT interrupt will be generated if ADC2 is outside of the range defined by ADC2GT and ADC2LT (if ADC2 < 0x10 or ADC2 > 0x20).

Figure 7.5. ADC2 Window Compare Examples, Single-Ended Mode

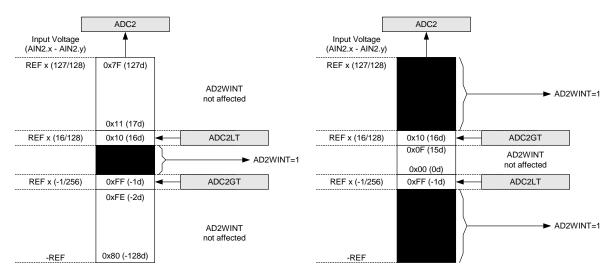

#### 7.3.2. Window Detector In Differential Mode

Figure 7.6 shows two example window comparisons for differential mode, with ADC2LT = 0x10 (+16d) and ADC2GT = 0xFF (-1d). Notice that in Differential mode, the codes vary from -VREF to VREF\*(127/128) and are represented as 8-bit 2's complement signed integers. In the left example, an AD2WINT interrupt will be generated if the ADC2 conversion word (ADC2L) is within the range defined by ADC2GT and ADC2LT (if 0xFF (-1d) < ADC2 < 0x0F (16d)). In the right example, an AD2WINT interrupt will be generated if ADC2 is outside of the range defined by ADC2GT and ADC2LT (if ADC2 < 0xFF (-1d) or ADC2 > 0x10 (+16d)).

Figure 7.6. ADC2 Window Compare Examples, Differential Mode

|          |                                                       | SFR Det                                                                                         | finition 8.                     | 3. DAC0C                          | N: DAC0     | Control             |                                              |             |  |  |  |

|----------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------|-------------|---------------------|----------------------------------------------|-------------|--|--|--|

| R/W      | R/W                                                   | R/W                                                                                             | R/W                             | R/W                               | R/W         | R/W                 | R/W                                          | Reset Valu  |  |  |  |

| DAC0EN   | - ۱                                                   | -                                                                                               | DAC0MD'                         | 1 DAC0MD0                         | DAC0DF2     | DAC0DF1             | DAC0DF0                                      | 0000000     |  |  |  |

| Bit7     | Bit6                                                  | Bit5                                                                                            | Bit4                            | Bit3                              | Bit2        | Bit1                | Bit0                                         | ,           |  |  |  |

|          |                                                       |                                                                                                 |                                 |                                   |             |                     | SFR Address:<br>SFR Page:                    | -           |  |  |  |

| Bit7:    |                                                       | isabled. DA                                                                                     | C0 Output p                     | oin is disable<br>in is active; [ |             |                     | er shutdowr                                  | n mode.     |  |  |  |

| Bits6–5: |                                                       | UNUSED. Read = 00b; Write = don't care.                                                         |                                 |                                   |             |                     |                                              |             |  |  |  |

| Bits4–3: |                                                       |                                                                                                 |                                 |                                   |             |                     |                                              |             |  |  |  |

|          | 00: DAC ou                                            | utput update                                                                                    | es occur on                     | a write to DA                     | C0H.        |                     |                                              |             |  |  |  |

|          | 01: DAC ou                                            | utput update                                                                                    | es occur on                     | Timer 3 over                      | flow.       |                     |                                              |             |  |  |  |

|          | 10: DAC οι                                            | utput update                                                                                    | es occur on                     | Timer 4 over                      | flow.       |                     |                                              |             |  |  |  |

|          | 11: DAC ou                                            | itput update                                                                                    | es occur on                     | Timer 2 over                      | flow.       |                     |                                              |             |  |  |  |

| Bits2–0: | DAC0DF2-                                              | -0: DAC0 D                                                                                      | ata Format                      | Bits:                             |             |                     |                                              |             |  |  |  |

|          |                                                       | -                                                                                               | ificant nibble<br>e is in DAC0  | e of the DAC                      | 0 Data Word | d is in DAC         | 0H[3:0], wh                                  | ile the lea |  |  |  |

|          |                                                       | DAC0H                                                                                           |                                 |                                   | DACOL       |                     |                                              |             |  |  |  |

|          |                                                       | MSB                                                                                             |                                 |                                   |             |                     |                                              | LSE         |  |  |  |

|          | sig                                                   | -                                                                                               | its are in DA                   | s of the DAC(<br>COL[7:1].        |             | DAC                 |                                              |             |  |  |  |

|          | N                                                     | ISB                                                                                             |                                 | Ī                                 |             |                     |                                              | LSB         |  |  |  |

|          | 010: The                                              | e most sian                                                                                     | ificant 6-bits                  | s of the DAC                      | ) Data Word | d is in DAC         | 0H[5:0], wh                                  | ile the lea |  |  |  |

|          |                                                       |                                                                                                 | its are in DA                   | C0L[7:2].                         |             |                     |                                              |             |  |  |  |

|          |                                                       |                                                                                                 | its are in DA                   | C0L[7:2].                         |             | DAC0                | L                                            |             |  |  |  |

|          |                                                       | nificant 6-bi                                                                                   | its are in DA                   | C0L[7:2].                         |             | DACO                | L<br>LSB                                     |             |  |  |  |

|          | sig<br>MSB<br>011: The                                | nificant 6-bi<br>DAC0H                                                                          | ificant 7-bits                  | s of the DAC                      | ) Data Word |                     | LSB                                          |             |  |  |  |

|          | sig<br>MSB<br>011: The                                | nificant 6-bi<br>DAC0H                                                                          |                                 | s of the DAC                      | ) Data Word |                     | LSB<br>0H[6:0], wh                           |             |  |  |  |

|          | sig<br>MSB<br>011: The                                | nificant 6-bi<br>DACOH                                                                          | ificant 7-bits                  | s of the DAC                      | ) Data Word | d is in DAC         | LSB<br>0H[6:0], wh                           |             |  |  |  |

| M        | sig<br>MSB  <br>011: The<br>sig<br>SB    <br>1xx: The | nificant 6-bi<br>DACOH<br>e most sign<br>nificant 5-bi<br>DACOH<br>e most sign                  | ificant 7-bits<br>its are in DA | s of the DAC(<br>COL[7:3].        |             | d is in DAC DAC0    | LSB<br>0H[6:0], wh<br>L<br>SB                | ile the lea |  |  |  |

| M        | SB   1xx: The sig                                     | nificant 6-bi<br>DACOH<br>e most sign<br>nificant 5-bi<br>DACOH<br>e most sign                  | ificant 7-bits<br>its are in DA | s of the DAC(<br>COL[7:3].        |             | d is in DAC<br>DACO | LSB<br>0H[6:0], wh<br>L<br>SB<br>0H[7:0], wh | ile the lea |  |  |  |

|          | SB   1xx: The sig                                     | nificant 6-bi<br>DACOH<br>e most sign<br>nificant 5-bi<br>DACOH<br>e most sign<br>nificant 4-bi | ificant 7-bits<br>its are in DA | s of the DAC(<br>COL[7:3].        |             | d is in DAC<br>DACO | LSB<br>0H[6:0], wh<br>L<br>SB<br>0H[7:0], wh | ile the lea |  |  |  |

| MSB      | SB   1xx: The sig                                     | nificant 6-bi<br>DACOH<br>e most sign<br>nificant 5-bi<br>DACOH<br>e most sign<br>nificant 4-bi | ificant 7-bits<br>its are in DA | s of the DAC(<br>COL[7:3].        |             | d is in DAC<br>DACO | LSB<br>0H[6:0], wh<br>L<br>SB<br>0H[7:0], wh | ile the lea |  |  |  |

|          | SB   1xx: The sig                                     | nificant 6-bi<br>DACOH<br>e most sign<br>nificant 5-bi<br>DACOH<br>e most sign<br>nificant 4-bi | ificant 7-bits<br>its are in DA | s of the DAC(<br>COL[7:3].        |             | d is in DAC<br>DACO | LSB<br>0H[6:0], wh<br>L<br>SB<br>0H[7:0], wh | ile the lea |  |  |  |

|                   | ss: 0xD1                                                                                                                    | 544  | <b>D</b> 444 | 544          | <b>D</b> 444   | 5.44        | 544        | <b>D</b> (1)(1)                         |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------|------|--------------|--------------|----------------|-------------|------------|-----------------------------------------|--|

| R/W               | R/W                                                                                                                         | R/W  | R/W          | R/W          | R/W            | R/W         | R/W        | Reset Value                             |  |

| -                 | -                                                                                                                           | -    | AD0VRS       | AD2VRS       | TEMPE          | BIASE       | REFBE      | 00000000                                |  |

| Bit7              | Bit6                                                                                                                        | Bit5 | Bit4         | Bit3         | Bit2           | Bit1        | Bit0       |                                         |  |

| Bits7–5:<br>Bit4: | Bits7–5: UNUSED. Read = 000b; Write = don't care.<br>Bit4: AD0VRS: ADC0 Voltage Reference Select.                           |      |              |              |                |             |            |                                         |  |

| Bitti             | 0: ADC0 volta                                                                                                               | •    |              |              |                |             |            |                                         |  |

|                   | 1: ADC0 volta                                                                                                               | •    |              | •            |                |             |            |                                         |  |

| Bit3:             | AD2VRS: AD                                                                                                                  | •    |              | •            |                |             |            |                                         |  |

| Bito.             | 0: ADC2 volta                                                                                                               |      |              |              |                |             |            |                                         |  |

|                   | 1: ADC2 volta                                                                                                               | •    |              | •            |                |             |            |                                         |  |

| Bit2:             | TEMPE: Tem                                                                                                                  | •    |              |              |                |             |            |                                         |  |

| DRE.              | 0: Internal Ter                                                                                                             |      |              | o Biti       |                |             |            |                                         |  |

|                   | 1: Internal Ter                                                                                                             |      |              |              |                |             |            |                                         |  |

| Bit1:             | BIASE: ADC/                                                                                                                 | •    |              | nable Bit (N | /lust be '1' i | f using AD  | C DAC or   | VRFF)                                   |  |

| Bitti             | 0: Internal Bia                                                                                                             |      |              |              |                | i donig / D | 0, 27.0, 0 | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |  |

|                   | 1: Internal Bia                                                                                                             |      |              |              |                |             |            |                                         |  |

| Bit0:             | REFBE: Inter                                                                                                                |      | •••••        | nable Bit    |                |             |            |                                         |  |

| Bito.             |                                                                                                                             |      |              |              |                |             |            |                                         |  |

|                   | 0: Internal Reference Buffer Off.<br>1: Internal Reference Buffer On. Internal voltage reference is driven on the VREF pin. |      |              |              |                |             |            |                                         |  |

#### SFR Definition 9.2. REF0CN: Reference Control (C8051F121/3/5/7)

and a RET pops two record bits, also.) The stack record circuitry can also detect an overflow or underflow on the 32-bit shift register, and can notify the debug software even with the MCU running at speed.

#### 11.2.6. Special Function Registers

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFR's). The SFR's provide control and data exchange with the CIP-51's resources and peripherals. The CIP-51 duplicates the SFR's found in a typical 8051 implementation as well as implementing additional SFR's used to configure and access the sub-systems unique to the MCU. This allows the addition of new functionality while retaining compatibility with the MCS-51<sup>™</sup> instruction set. Table 11.2 lists the SFR's implemented in the CIP-51 System Controller.

The SFR registers are accessed whenever the direct addressing mode is used to access memory locations from 0x80 to 0xFF. SFR's with addresses ending in 0x0 or 0x8 (e.g. P0, TCON, P1, SCON, IE, etc.) are bit-addressable as well as byte-addressable. All other SFR's are byte-addressable only. Unoccupied addresses in the SFR space are reserved for future use. Accessing these areas will have an indeterminate effect and should be avoided. Refer to the corresponding pages of the datasheet, as indicated in Table 11.3, for a detailed description of each register.

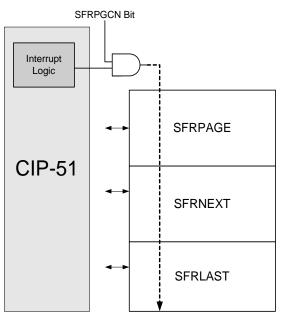

#### 11.2.6.1.SFR Paging

The CIP-51 features *SFR paging*, allowing the device to map many SFR's into the 0x80 to 0xFF memory address space. The SFR memory space has 256 *pages*. In this way, each memory location from 0x80 to 0xFF can access up to 256 SFR's. The C8051F12x family of devices utilizes five SFR pages: 0, 1, 2, 3, and F. SFR pages are selected using the Special Function Register Page Selection register, SFRPAGE (see SFR Definition 11.3). The procedure for reading and writing an SFR is as follows:

- 1. Select the appropriate SFR page number using the SFRPAGE register.

- 2. Use direct accessing mode to read or write the special function register (MOV instruction).

#### 11.2.6.2.Interrupts and SFR Paging

When an interrupt occurs, the SFR Page Register will automatically switch to the SFR page containing the flag bit that caused the interrupt. The automatic SFR Page switch function conveniently removes the burden of switching SFR pages from the interrupt service routine. Upon execution of the RETI instruction, the SFR page is automatically restored to the SFR Page in use prior to the interrupt. This is accomplished via a three-byte *SFR Page Stack*. The top byte of the stack is SFRPAGE, the current SFR Page. The second byte of the SFR Page Stack is SFRNEXT. The third, or bottom byte of the SFR Page Stack is SFRLAST. On interrupt, the current SFRPAGE value is pushed to the SFR Page containing the flag bit associated with the interrupt. On a return from interrupt, the SFR Page Stack is popped resulting in the value of SFRNEXT returning to the SFRPAGE register, thereby restoring the SFR page context without software intervention. The value in SFRLAST (0x00 if there is no SFR Page value in the bottom of the stack) of the stack is placed in SFRNEXT register. If desired, the values stored in SFRNEXT and SFRLAST may be modified during an interrupt, enabling the CPU to return to a different SFR Page upon execution of the RETI instruction (on interrupt exit). Modifying registers in the SFR Page Stack does not cause a push or pop of the stack. Only interrupt calls and returns will cause push/pop operations on the SFR Page Stack.

Figure 11.4. SFR Page Stack

Automatic hardware switching of the SFR Page on interrupts may be enabled or disabled as desired using the SFR Automatic Page Control Enable Bit located in the SFR Page Control Register (SFRPGCN). This function defaults to 'enabled' upon reset. In this way, the autoswitching function will be enabled unless disabled in software.

A summary of the SFR locations (address and SFR page) is provided in Table 11.2. in the form of an SFR memory map. Each memory location in the map has an SFR page row, denoting the page in which that SFR resides. Note that certain SFR's are accessible from ALL SFR pages, and are denoted by the "(ALL PAGES)" designation. For example, the Port I/O registers P0, P1, P2, and P3 all have the "(ALL PAGES)" designation, indicating these SFR's are accessible from all SFR pages regardless of the SFRPAGE register value.

| R/W      | R/W                          | R/W                                                                                                                                                                | R/W              | R/W           | R/W           | R/W           | R                       | Reset Value           |  |  |  |

|----------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|---------------|---------------|-------------------------|-----------------------|--|--|--|

| CY       | AC                           | F0                                                                                                                                                                 | RS1              | RS0           | OV            | F1            | PARITY                  | 0000000               |  |  |  |

| Bit7     | Bit6                         | Bit5                                                                                                                                                               | Bit4             | Bit3          | Bit2          | Bit1          | Bit0                    | Bit<br>Addressable    |  |  |  |

|          |                              |                                                                                                                                                                    |                  |               |               |               | SFR Address<br>SFR Page | : 0xD0<br>: All Pages |  |  |  |

| Bit7:    | CY: Carry I<br>This bit is s | •                                                                                                                                                                  | ne last arithmet | tic operatio  | n resulted    | in a carry (a | addition) or            | a borrow              |  |  |  |

|          |                              | This bit is set when the last arithmetic operation resulted in a carry (addition) or a borrow subtraction). It is cleared to 0 by all other arithmetic operations. |                  |               |               |               |                         |                       |  |  |  |

| Bit6:    | AC: Auxilia                  |                                                                                                                                                                    |                  |               |               |               |                         |                       |  |  |  |

|          |                              |                                                                                                                                                                    | e last arithmeti |               |               |               |                         |                       |  |  |  |

| Bit5:    | from (subtr<br>F0: User F    |                                                                                                                                                                    | high order nib   | ble. It is cl | eared to 0    | by all other  | arithmetic of           | operations.           |  |  |  |

| Dito.    |                              | •                                                                                                                                                                  | able, general pu | urpose flac   | ı for use uı  | nder softwar  | e control.              |                       |  |  |  |

| Bits4–3: |                              |                                                                                                                                                                    | Bank Select.     |               |               |               |                         |                       |  |  |  |

|          | These bits                   | select whi                                                                                                                                                         | ch register ban  | k is used o   | during regi   | ster accesse  | es.                     |                       |  |  |  |

|          |                              |                                                                                                                                                                    |                  |               |               |               |                         |                       |  |  |  |

|          | RS1                          | RS0                                                                                                                                                                | Register Bank    | Add           | ress          |               |                         |                       |  |  |  |

|          | 0                            | 0                                                                                                                                                                  | 0                | 0x00-         | -0x07         |               |                         |                       |  |  |  |

|          | 0                            | 1                                                                                                                                                                  | 1                | 0x08-         | -0x0F         |               |                         |                       |  |  |  |

|          | 1                            | 0                                                                                                                                                                  | 2                | 0x10-         | -0x17         |               |                         |                       |  |  |  |

|          | 1                            | 1                                                                                                                                                                  | 3                | 0x18-         | -0x1F         |               |                         |                       |  |  |  |

| Bit2:    | OV: Overflo                  | ow Flag.                                                                                                                                                           |                  |               |               |               |                         |                       |  |  |  |

| Ditt.    |                              | •                                                                                                                                                                  | der the followin | g circumst    | ances:        |               |                         |                       |  |  |  |

|          |                              |                                                                                                                                                                    | SUBB instructi   |               |               | ange overflo  | W.                      |                       |  |  |  |

|          |                              |                                                                                                                                                                    | esults in an ove | · ·           | •             | er than 255)  |                         |                       |  |  |  |

|          |                              |                                                                                                                                                                    | uses a divide-l  |               |               |               |                         |                       |  |  |  |

|          |                              | is cleared                                                                                                                                                         | to 0 by the AD   | D, ADDC,      | SUBB, MI      | JL, and DIV   | instructions            | s in all other        |  |  |  |

| Bit1:    | cases.<br>F1: User F         |                                                                                                                                                                    |                  |               |               |               |                         |                       |  |  |  |

| DILT.    |                              |                                                                                                                                                                    | able, general pu | Irnose flag   | I for Use III | nder softwar  | e control               |                       |  |  |  |

| Bit0:    | PARITY: P                    |                                                                                                                                                                    | sio, general pr  |               |               |               | 0.0011101.              |                       |  |  |  |

|          |                              |                                                                                                                                                                    | e sum of the ei  | ight bits in  | the accum     | ulator is odd | and cleare              | d if the sum          |  |  |  |

|          | is even.                     |                                                                                                                                                                    |                  | -             |               |               |                         |                       |  |  |  |

|          |                              |                                                                                                                                                                    |                  |               |               |               |                         |                       |  |  |  |

|          |                              |                                                                                                                                                                    |                  |               |               |               |                         |                       |  |  |  |

#### SFR Definition 11.9. PSW: Program Status Word

| R/W   | R/W                            | R/W                                               | R/W         | R/W            | R/W       | R/W        | R/W                                      | Reset Value  |  |  |  |  |  |

|-------|--------------------------------|---------------------------------------------------|-------------|----------------|-----------|------------|------------------------------------------|--------------|--|--|--|--|--|

| -     | ES1                            | -                                                 | EADC2       | EWADC2         | ET4       | EADC0      | ET3                                      | 0000000      |  |  |  |  |  |

| Bit7  | Bit6                           | Bit5                                              | Bit4        | Bit3           | Bit2      | Bit1       | Bit0                                     | _            |  |  |  |  |  |

|       |                                |                                                   |             |                |           |            | SFR Address: 0xE7<br>SFR Page: All Pages |              |  |  |  |  |  |

|       |                                |                                                   |             |                |           |            | SFR Pag                                  | e: All Pages |  |  |  |  |  |

| Bit7: | UNUSED. R                      | ead = 0b, V                                       | Vrite = don | 't care.       |           |            |                                          |              |  |  |  |  |  |

| Bit6: | ES1: Enable UART1 Interrupt.   |                                                   |             |                |           |            |                                          |              |  |  |  |  |  |

|       | This bit sets                  | This bit sets the masking of the UART1 interrupt. |             |                |           |            |                                          |              |  |  |  |  |  |

|       | 0: Disable U                   |                                                   | •           |                |           |            |                                          |              |  |  |  |  |  |

|       | 1: Enable UA                   |                                                   | •           |                |           |            |                                          |              |  |  |  |  |  |

| Bit5: | UNUSED. R                      |                                                   |             |                |           |            |                                          |              |  |  |  |  |  |

| Bit4: | EADC2: Ena                     |                                                   |             |                |           |            |                                          |              |  |  |  |  |  |

|       | This bit sets<br>0: Disable Al |                                                   |             |                | onversion | interrupt. |                                          |              |  |  |  |  |  |

|       | 1: Enable A                    |                                                   |             |                |           |            |                                          |              |  |  |  |  |  |

| Bit3: | EWADC2: E                      |                                                   |             | •              | nterrupt  |            |                                          |              |  |  |  |  |  |

| Dito: | This bit sets                  |                                                   |             |                | •         | nterrupt.  |                                          |              |  |  |  |  |  |

|       | 0: Disable Al                  |                                                   | •           |                | •         |            |                                          |              |  |  |  |  |  |

|       | 1: Enable AD                   |                                                   |             |                |           |            |                                          |              |  |  |  |  |  |

| Bit2: | ET4: Enable                    | Timer 4 In                                        | terrupt     |                |           |            |                                          |              |  |  |  |  |  |

|       | This bit sets                  |                                                   |             | ner 4 interrup | ot.       |            |                                          |              |  |  |  |  |  |

|       | 0: Disable Ti                  |                                                   | •           |                |           |            |                                          |              |  |  |  |  |  |

| Dire  | 1: Enable Tir                  |                                                   | •           |                |           |            |                                          |              |  |  |  |  |  |

| Bit1: | EADC0: Ena                     |                                                   |             |                | •         | Interview  |                                          |              |  |  |  |  |  |

|       | This bit sets<br>0: Disable Al |                                                   |             |                | onversion | interrupt. |                                          |              |  |  |  |  |  |

|       | 1: Enable A                    |                                                   |             |                |           |            |                                          |              |  |  |  |  |  |

| Bit0: | ET3: Enable                    |                                                   |             |                |           |            |                                          |              |  |  |  |  |  |

| 2.101 | This bit sets                  |                                                   |             | ner 3 interru  | ot.       |            |                                          |              |  |  |  |  |  |

|       | 0: Disable Ti                  |                                                   |             |                |           |            |                                          |              |  |  |  |  |  |

|       | 1: Enable Tir                  | mer 3 interr                                      | upts.       |                |           |            |                                          |              |  |  |  |  |  |

|       |                                |                                                   |             |                |           |            |                                          |              |  |  |  |  |  |

|       |                                |                                                   |             |                |           |            |                                          |              |  |  |  |  |  |

#### SFR Definition 11.15. EIE2: Extended Interrupt Enable 2

#### SFR Definition 13.1. WDTCN: Watchdog Timer Control

| R/W      | R/W                                                                                                                                                                                                             | R/W                                 | R/W          | R/W         | R/W        | R/W                  | R/W                       | Reset Value                             |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------|-------------|------------|----------------------|---------------------------|-----------------------------------------|--|

| Bit7     | Bit6                                                                                                                                                                                                            | Bit5                                | Bit4         | Bit3        | Bit2       | Bit1                 | Bit0                      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |  |

| Ditt     | Dito                                                                                                                                                                                                            | Dito                                | Ditt         | Dito        | DIL        |                      | SFR Address:<br>SFR Page: | -                                       |  |

| Bits7–0: | WDT Contro<br>Writing 0xA5<br>Writing 0xDE<br>Writing 0xFF                                                                                                                                                      | both enable<br>followed w           | ithin 4 syst | em clocks b |            | ables the V          | VDT.                      |                                         |  |

| Bit4:    | Watchdog Si<br>Reading the<br>0: WDT is in<br>1: WDT is ac                                                                                                                                                      | tatus Bit (wl<br>WDTCN.[4<br>active | nen Read)    |             | hdog Timer | <sup>-</sup> Status. |                           |                                         |  |

| Bits2–0: | <ul> <li>WDT is active</li> <li>Bits2–0: Watchdog Timeout Interval Bits</li> <li>The WDTCN.[2:0] bits set the Watchdog Timeout Interval. When writing these bits,</li> <li>WDTCN.7 must be set to 0.</li> </ul> |                                     |              |             |            |                      |                           |                                         |  |

|          |                                                                                                                                                                                                                 |                                     |              |             |            |                      |                           |                                         |  |

Electrical specifications for the precision internal oscillator are given in Table 14.1. Note that the system clock may be derived from the programmed internal oscillator divided by 1, 2, 4, or 8, as defined by the IFCN bits in register OSCICN.

#### SFR Definition 14.1. OSCICL: Internal Oscillator Calibration.

### SFR Definition 14.2. OSCICN: Internal Oscillator Control

| R/W       | R                                              | R/W                                | R           | R/W         | R/W         | R/W | R/W                       | Reset Value |  |  |  |

|-----------|------------------------------------------------|------------------------------------|-------------|-------------|-------------|-----|---------------------------|-------------|--|--|--|

| IOSCEN    | I IFRDY                                        | -                                  | 11000000    |             |             |     |                           |             |  |  |  |

| Bit7      | Bit6                                           | Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 |             |             |             |     |                           |             |  |  |  |

|           |                                                |                                    |             |             |             |     | SFR Address:<br>SFR Page: |             |  |  |  |

| Bit 7:    | IOSCEN: Int<br>0: Internal O<br>1: Internal O  | scillator Dis                      | abled.      | Bit.        |             |     |                           |             |  |  |  |

| Bit 6:    | IFRDY: Inter<br>0: Internal O<br>1: Internal O | scillator not                      | running at  | programme   | d frequency | /.  |                           |             |  |  |  |

| Bits 5-2: | Reserved.                                      |                                    |             | -           |             |     |                           |             |  |  |  |

| Bits 1–0: | IFCN1-0: Int                                   | ernal Oscilla                      | ator Freque | ncy Control | Bits.       |     |                           |             |  |  |  |

|           | 00: Internal (                                 | Oscillator is                      | divided by  | 8.          |             |     |                           |             |  |  |  |

|           | 01: Internal (                                 | Oscillator is                      | divided by  | 4.          |             |     |                           |             |  |  |  |

|           | 10: Internal (                                 | Oscillator is                      | divided by  | 2.          |             |     |                           |             |  |  |  |

|           | 11: Internal (                                 | Oscillator is                      | divided by  | 1.          |             |     |                           |             |  |  |  |

#### 15.1.3. Writing Flash Memory From Software

Bytes in Flash memory can be written one byte at a time, or in small blocks. The CHBLKW bit in register CCH0CN (SFR Definition 16.1) controls whether a single byte or a block of bytes is written to Flash during a write operation. When CHBLKW is cleared to '0', the Flash will be written one byte at a time. When CHBLKW is set to '1', the Flash will be written in blocks of four bytes for addresses in code space, or blocks of two bytes for addresses in the Scratchpad area. Block writes are performed in the same amount of time as single byte writes, which can save time when storing large amounts of data to Flash memory.

For single-byte writes to Flash, bytes are written individually, and the Flash write is performed after each MOVX write instruction. The recommended procedure for writing Flash in single bytes is as follows:

- Step 1. Disable interrupts.

- Step 2. Clear CHBLKW (CCH0CN.0) to select single-byte write mode.

- Step 3. If writing to bytes in Bank 1, Bank 2, or Bank 3, set the COBANK bits (PSBANK.5-4) for the appropriate bank.

- Step 4. If writing to bytes in the Scratchpad area, set the SFLE bit (PSCTL.2).

- Step 5. Set FLWE (FLSCL.0) to enable Flash writes/erases via user software.

- Step 6. Set PSWE (PSCTL.0) to redirect MOVX commands to write to Flash.

- Step 7. Use the MOVX instruction to write a data byte to the desired location (repeat as necessary).

- Step 8. Clear the PSWE bit to redirect MOVX commands to the XRAM data space.

- Step 9. Clear the FLWE bit, to disable Flash writes/erases.

- Step 10. If writing to bytes in the Scratchpad area, clear the SFLE bit.

- Step 11. Re-enable interrupts.

For block Flash writes, the Flash write procedure is only performed after the last byte of each block is written with the MOVX write instruction. When writing to addresses located in any of the four code banks, a Flash write block is four bytes long, from addresses ending in 00b to addresses ending in 11b. Writes must be performed sequentially (i.e. addresses ending in 00b, 01b, 10b, and 11b must be written in order). The Flash write will be performed following the MOVX write that targets the address ending in 11b. When writing to addresses located in the Flash Scratchpad area, a Flash block is two bytes long, from addresses ending in 0b to addresses ending in 1b. The Flash write will be performed following the MOVX write that targets the address ending in 1b. If any bytes in the block do not need to be updated in Flash, they should be written to 0xFF. The recommended procedure for writing Flash in blocks is as follows:

- Step 1. Disable interrupts.

- Step 2. Set CHBLKW (CCH0CN.0) to select block write mode.

- Step 3. If writing to bytes in Bank 1, Bank 2, or Bank 3, set the COBANK bits (PSBANK.5-4) for the appropriate bank.

- Step 4. If writing to bytes in the Scratchpad area, set the SFLE bit (PSCTL.2).

- Step 5. Set FLWE (FLSCL.0) to enable Flash writes/erases via user software.

- Step 6. Set PSWE (PSCTL.0) to redirect MOVX commands to write to Flash.

- Step 7. Use the MOVX instruction to write data bytes to the desired block. The data bytes must be written sequentially, and the last byte written must be the high byte of the block (see text for details, repeat as necessary).

- Step 8. Clear the PSWE bit to redirect MOVX commands to the XRAM data space.

- Step 9. Clear the FLWE bit, to disable Flash writes/erases.

- Step 10. If writing to bytes in the Scratchpad area, clear the SFLE bit.

- Step 11. Re-enable interrupts.

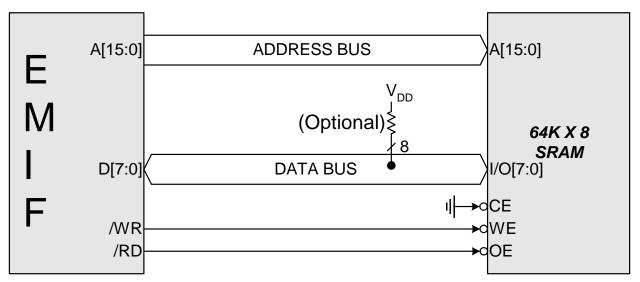

#### 17.4.2. Non-multiplexed Configuration

In Non-multiplexed mode, the Data Bus and the Address Bus pins are not shared. An example of a Nonmultiplexed Configuration is shown in Figure 17.2. See **Section "17.6.1. Non-multiplexed Mode" on page 227** for more information about Non-multiplexed operation.

Figure 17.2. Non-multiplexed Configuration Example

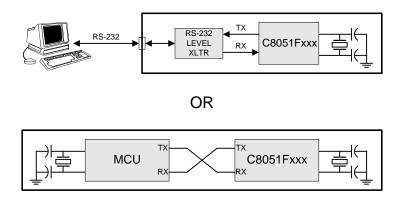

#### Figure 21.6. UART0 Modes 1, 2, and 3 Interconnect Diagram

#### 21.1.4. Mode 3: 9-Bit UART, Variable Baud Rate

Mode 3 uses the Mode 2 transmission protocol with the Mode 1 baud rate generation. Mode 3 operation transmits 11 bits: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. The baud rate is derived from Timer 1 or Timer 2, 3, or 4 overflows, as defined by Equation 21.1 and Equation 21.3. Multiprocessor communications and hardware address recognition are supported, as described in **Section 21.2**.

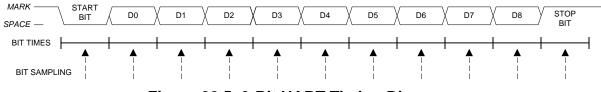

#### 22.2.2. 9-Bit UART

9-bit UART mode uses a total of eleven bits per data byte: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. The state of the ninth transmit data bit is determined by the value in TB81 (SCON1.3), which is assigned by user software. It can be assigned the value of the parity flag (bit P in register PSW) for error detection, or used in multiprocessor communications. On receive, the ninth data bit goes into RB81 (SCON1.2) and the stop bit is ignored.

Data transmission begins when an instruction writes a data byte to the SBUF1 register. The TI1 Transmit Interrupt Flag (SCON1.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN1 Receive Enable bit (SCON1.4) is set to '1'. After the stop bit is received, the data byte will be loaded into the SBUF1 receive register if the following conditions are met: (1) RI1 must be logic 0, and (2) if MCE1 is logic 1, the 9th bit must be logic 1 (when MCE1 is logic 0, the state of the ninth data bit is unimportant). If these conditions are met, the eight bits of data are stored in SBUF1, the ninth bit is stored in RB81, and the RI1 flag is set to '1'. A UART1 interrupt will occur if enabled when either TI1 or RI1 is set to '1'.

Figure 22.5. 9-Bit UART Timing Diagram

| R/W      | R/W                           | R/W          | R/W                                         | R/W                          | R/W          | R/W         | R/W                     | Reset Value |  |  |  |

|----------|-------------------------------|--------------|---------------------------------------------|------------------------------|--------------|-------------|-------------------------|-------------|--|--|--|

| GATE1    | C/T1                          | T1M1         | T1M0                                        | GATE0                        | C/T0         | T0M1        | T0M0                    | 00000000    |  |  |  |

| Bit7     | Bit6                          | Bit5         | Bit4                                        | Bit3                         | Bit2         | Bit1        | Bit0                    | _           |  |  |  |

|          |                               |              |                                             |                              |              |             | SFR Address<br>SFR Page |             |  |  |  |

| Bit7:    |                               | enabled w    | e Control.<br>hen TR1 = 1 i<br>nly when TR1 | •                            |              | •           |                         |             |  |  |  |

| Bit6:    | C/T1: Counter/Timer 1 Select. |              |                                             |                              |              |             |                         |             |  |  |  |

|          | 0: Timer F                    | unction: Tir | mer 1 increme                               | ented by clo                 | k defined    | by T1M bit  | (CKCON.4)               | ).          |  |  |  |

|          | 1: Counter                    | Function:    | Timer 1 increi                              | mented by h                  | igh-to-low   | transitions | on external             | input pin   |  |  |  |

|          | (T1).                         |              |                                             |                              |              |             |                         |             |  |  |  |

| Bits5–4: |                               |              | Mode Select                                 |                              |              |             |                         |             |  |  |  |

|          | These bits                    | select the   | Timer 1 opera                               | ation mode.                  |              |             |                         |             |  |  |  |

|          | T1M1                          | T1M0         |                                             | Mod                          | е            |             | 7                       |             |  |  |  |

|          | 0                             | 0            | Мос                                         | Mode 0: 13-bit counter/timer |              |             |                         |             |  |  |  |

|          | 0                             | 1            | Мос                                         | le 1: 16-bit o               | counter/tim  | er          |                         |             |  |  |  |

|          | 1                             | 0            | Mode 2: 8-b                                 |                              |              |             |                         |             |  |  |  |

|          | 1                             | 1            | M                                           | ode 3: Time                  | r 1 inactive |             |                         |             |  |  |  |

| Bit3:    | GATE0: Ti                     | mar 0 Cat    | Control                                     |                              |              |             |                         |             |  |  |  |

| DILJ.    |                               |              | hen TR0 = 1 i                               | rrespective                  | of /INITO Io | aic loval   |                         |             |  |  |  |

|          |                               |              | nly when TR0                                |                              |              |             |                         |             |  |  |  |

| Bit2:    | C/T0: Cou                     |              |                                             | - 170070                     |              |             |                         |             |  |  |  |

|          |                               |              | ner 0 increme                               | ented by clo                 | ck defined   | by T0M bit  | (CKCON.3                | ).          |  |  |  |

|          |                               |              | Timer 0 increi                              |                              |              |             |                         |             |  |  |  |

|          | (T0).                         |              |                                             | ·                            | -            |             |                         |             |  |  |  |

| Bits1–0: |                               |              | Mode Select                                 |                              |              |             |                         |             |  |  |  |

|          | These bits                    | select the   | Timer 0 opera                               | ation mode.                  |              |             |                         |             |  |  |  |

|          | T0M1                          | T0M0         |                                             | Mod                          | 9            |             | ]                       |             |  |  |  |

|          | 0                             | 0            | Mod                                         | e 0: 13-bit c                | ounter/time  | er          | 1                       |             |  |  |  |

|          | 0                             | 1            | Mod                                         | e 1: 16-bit c                | ounter/time  | er          | 1                       |             |  |  |  |

|          | 1                             | 0            | Mode 2: 8-b                                 | it counter/tir               | ner with au  | to-reload   | 1                       |             |  |  |  |

|          | 1                             | 1            | Mode                                        | 3: Two 8-bit                 | counter/tin  | ners        | 1                       |             |  |  |  |