#### Silicon Labs - C8051F124 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | 8051                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 50MHz                                                       |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT          |

| Number of I/O              | 64                                                          |

| Program Memory Size        | 128KB (128K x 8)                                            |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 8.25K x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                 |

| Data Converters            | A/D 8x8b, 8x12b; D/A 2x12b                                  |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 100-TQFP                                                    |

| Supplier Device Package    | 100-TQFP (14x14)                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f124 |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1. | System Overview                                       | 19 |

|----|-------------------------------------------------------|----|

|    | 1.1. CIP-51 <sup>™</sup> Microcontroller Core         | 27 |

|    | 1.1.1. Fully 8051 Compatible                          | 27 |

|    | 1.1.2. Improved Throughput                            | 27 |

|    | 1.1.3. Additional Features                            | 28 |

|    | 1.2. On-Chip Memory                                   | 29 |

|    | 1.3. JTAG Debug and Boundary Scan                     | 30 |

|    | 1.4. 16 x 16 MAC (Multiply and Accumulate) Engine     | 31 |

|    | 1.5. Programmable Digital I/O and Crossbar            | 32 |

|    | 1.6. Programmable Counter Array                       |    |

|    | 1.7. Serial Ports                                     |    |

|    | 1.8. 12 or 10-Bit Analog to Digital Converter         | 34 |

|    | 1.9. 8-Bit Analog to Digital Converter                |    |

|    | 1.10.12-bit Digital to Analog Converters              |    |

|    | 1.11.Analog Comparators                               |    |

|    | Absolute Maximum Ratings                              |    |

| 3. |                                                       |    |

| 4. | · · · · · · · · · · · · · · · · · · ·                 |    |

| 5. | ADC0 (12-Bit ADC, C8051F120/1/4/5 Only)               |    |

|    | 5.1. Analog Multiplexer and PGA                       |    |

|    | 5.2. ADC Modes of Operation                           |    |

|    | 5.2.1. Starting a Conversion                          |    |

|    | 5.2.2. Tracking Modes                                 |    |

|    | 5.2.3. Settling Time Requirements                     |    |

|    | 5.3. ADC0 Programmable Window Detector                |    |

| 6. | ADC0 (10-Bit ADC, C8051F122/3/6/7 and C8051F13x Only) |    |

|    | 6.1. Analog Multiplexer and PGA                       |    |

|    | 6.2. ADC Modes of Operation                           |    |

|    | 6.2.1. Starting a Conversion                          |    |

|    | 6.2.2. Tracking Modes                                 |    |

|    | 6.2.3. Settling Time Requirements                     |    |

|    | 6.3. ADC0 Programmable Window Detector                |    |

| 7. | ADC2 (8-Bit ADC, C8051F12x Only)                      |    |

|    | 7.1. Analog Multiplexer and PGA                       |    |

|    | 7.2. ADC2 Modes of Operation                          |    |

|    | 7.2.1. Starting a Conversion                          |    |

|    | 7.2.2. Tracking Modes                                 |    |

|    | 7.2.3. Settling Time Requirements                     |    |

|    | 7.3. ADC2 Programmable Window Detector 1              |    |

|    | 7.3.1. Window Detector In Single-Ended Mode 1         | 00 |

|    | 7.3.2. Window Detector In Differential Mode 1         | 01 |

### List of Registers

| SFR | Definition 5.1. AMX0CF: AMUX0 Configuration                 | . 60 |

|-----|-------------------------------------------------------------|------|

|     | Definition 5.2. AMX0SL: AMUX0 Channel Select                |      |

|     | Definition 5.3. ADC0CF: ADC0 Configuration                  |      |

|     | Definition 5.4. ADC0CN: ADC0 Control                        |      |

| SFR | Definition 5.5. ADC0H: ADC0 Data Word MSB                   | . 64 |

|     | Definition 5.6. ADC0L: ADC0 Data Word LSB                   |      |

|     | Definition 5.7. ADC0GTH: ADC0 Greater-Than Data High Byte   |      |

|     | Definition 5.8. ADC0GTL: ADC0 Greater-Than Data Low Byte    |      |

|     | Definition 5.9. ADC0LTH: ADC0 Less-Than Data High Byte      |      |

|     | Definition 5.10. ADC0LTL: ADC0 Less-Than Data Low Byte      |      |

|     | Definition 6.1. AMX0CF: AMUX0 Configuration                 |      |

|     | Definition 6.2. AMX0SL: AMUX0 Channel Select                |      |

|     | Definition 6.3. ADC0CF: ADC0 Configuration                  |      |

|     | Definition 6.4. ADC0CN: ADC0 Control                        |      |

|     | Definition 6.5. ADC0H: ADC0 Data Word MSB                   |      |

|     | Definition 6.6. ADC0L: ADC0 Data Word LSB                   |      |

|     | Definition 6.7. ADC0GTH: ADC0 Greater-Than Data High Byte   |      |

|     | Definition 6.8. ADC0GTL: ADC0 Greater-Than Data Low Byte    |      |

|     | Definition 6.9. ADC0LTH: ADC0 Less-Than Data High Byte      |      |

|     | Definition 6.10. ADC0LTL: ADC0 Less-Than Data Low Byte      |      |

|     | Definition 7.1. AMX2CF: AMUX2 Configuration                 |      |

|     | Definition 7.2. AMX2SL: AMUX2 Channel Select                |      |

| SFR | Definition 7.3. ADC2CF: ADC2 Configuration                  | . 97 |

|     | Definition 7.4. ADC2CN: ADC2 Control                        |      |

|     | Definition 7.5. ADC2: ADC2 Data Word                        |      |

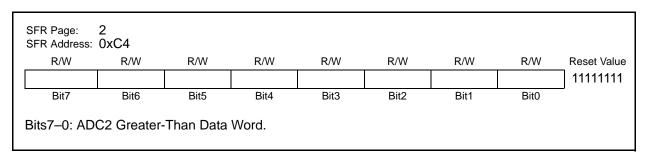

| SFR | Definition 7.6. ADC2GT: ADC2 Greater-Than Data Byte         | 102  |

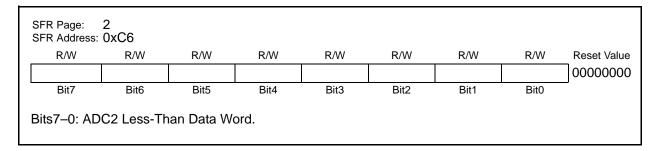

| SFR | Definition 7.7. ADC2LT: ADC2 Less-Than Data Byte            | 102  |

|     | Definition 8.1. DAC0H: DAC0 High Byte                       |      |

|     | Definition 8.2. DAC0L: DAC0 Low Byte                        |      |

|     | Definition 8.3. DAC0CN: DAC0 Control                        |      |

|     | Definition 8.4. DAC1H: DAC1 High Byte                       |      |

| SFR | Definition 8.5. DAC1L: DAC1 Low Byte                        | 109  |

|     | Definition 8.6. DAC1CN: DAC1 Control                        |      |

|     | Definition 9.1. REF0CN: Reference Control (C8051F120/2/4/6) |      |

|     | Definition 9.2. REF0CN: Reference Control (C8051F121/3/5/7) |      |

|     | Definition 9.3. REF0CN: Reference Control (C8051F130/1/2/3) |      |

| SFR | Definition 10.1. CPT0CN: Comparator0 Control                | 122  |

|     | Definition 10.2. CPT0MD: Comparator0 Mode Selection         |      |

|     | Definition 10.3. CPT1CN: Comparator1 Control                |      |

|     | Definition 10.4. CPT1MD: Comparator1 Mode Selection         |      |

|     | Definition 11.1. PSBANK: Program Space Bank Select          |      |

|     | Definition 11.2. SFRPGCN: SFR Page Control                  |      |

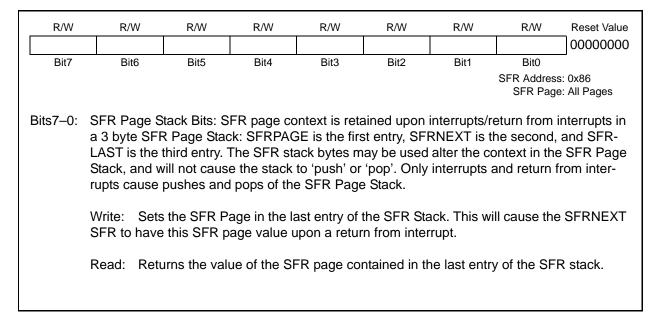

| SFR | Definition 11.3. SFRPAGE: SFR Page                          | 142  |

### 2. Absolute Maximum Ratings

| Parameter                                                                                                                                                                                                                             | Conditions          | Min      | Тур       | Мах                      | Units    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------|-----------|--------------------------|----------|

| Ambient temperature under bias                                                                                                                                                                                                        |                     | -55      |           | 125                      | °C       |

| Storage Temperature                                                                                                                                                                                                                   |                     | -65      | —         | 150                      | °C       |

| Voltage on any Pin (except V <sub>DD</sub> and Port I/O) with Respect to DGND                                                                                                                                                         |                     | -0.3     | _         | V <sub>DD</sub> +<br>0.3 | V        |

| Voltage on any Port I/O Pin or RST with Respect to DGND                                                                                                                                                                               |                     | -0.3     | _         | 5.8                      | V        |

| Voltage on V <sub>DD</sub> with Respect to DGND                                                                                                                                                                                       |                     | -0.3     | _         | 4.2                      | V        |

| Maximum Total Current through V <sub>DD</sub> , AV+, DGND,<br>and AGND                                                                                                                                                                |                     | _        | _         | 800                      | mA       |

| Maximum Output Current Sunk by any Port pin                                                                                                                                                                                           |                     |          |           | 100                      | mA       |

| Maximum Output Current Sunk by any other I/O pin                                                                                                                                                                                      |                     |          |           | 50                       | mA       |

| Maximum Output Current Sourced by any Port pin                                                                                                                                                                                        |                     |          |           | 100                      | mA       |

| Maximum Output Current Sourced by any other I/O<br>Pin                                                                                                                                                                                |                     |          |           | 50                       | mA       |

| *Note: Stresses above those listed under "Absolute Maximu<br>This is a stress rating only and functional operation of<br>indicated in the operation listings of this specification<br>extended periods may affect device reliability. | the devices at thos | e or any | other con | ditions abo              | ve those |

### Table 2.1. Absolute Maximum Ratings<sup>\*</sup>

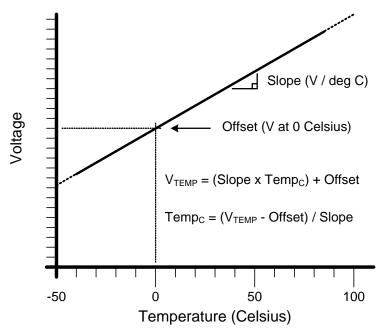

The Temperature Sensor transfer function is shown in Figure 5.2. The output voltage ( $V_{TEMP}$ ) is the PGA input when the Temperature Sensor is selected by bits AMX0AD3-0 in register AMX0SL; this voltage will be amplified by the PGA according to the user-programmed PGA settings. Typical values for the Slope and Offset parameters can be found in Table 5.1.

Figure 5.2. Typical Temperature Sensor Transfer Function

#### SFR Definition 5.4. ADC0CN: ADC0 Control

| ADOEN<br>Bit7<br>Bit7:<br>Bit6:<br>Bit5:<br>Bit4:<br>Bit4: | Bit6<br>AD0EN: AD0<br>0: ADC0 Dis<br>1: ADC0 Ena<br>AD0TM: AD0<br>0: When the<br>1: Tracking I<br>AD0INT: AD0<br>This flag mus<br>0: ADC0 has<br>1: ADC0 has<br>AD0BUSY: A<br>Read:<br>0: ADC0 Cor | Bit5<br>C0 Enable<br>abled. ADC<br>abled. ADC<br>Track Mc<br>ADC is en<br>ADC is en<br>C0 Conver<br>st be cleare<br>not completed | C0 is in low<br>C0 is active<br>ode Bit.<br>abled, tracl<br>ADCM1-0<br>sion Comp<br>ed by softw<br>leted a data         | and ready<br>king is cont<br>bits.<br>lete Interru<br>vare.                       | for data con<br>inuous unles            |               | R/W<br>ADOLJST<br>Bit0 | _           |  |  |  |  |  |  |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------|---------------|------------------------|-------------|--|--|--|--|--|--|

| Bit7:<br>Bit6:<br>Bit5:<br>Bit4:                           | AD0EN: AD0<br>0: ADC0 Dis<br>1: ADC0 Ena<br>AD0TM: AD0<br>0: When the<br>1: Tracking E<br>AD0INT: AD0<br>This flag mus<br>0: ADC0 has<br>1: ADC0 has<br>AD0BUSY: A<br>Read:<br>0: ADC0 Cor         | C0 Enable<br>abled. ADC<br>abled. ADC<br>C Track Mc<br>ADC is en<br>Oefined by<br>C0 Conver<br>st be cleare<br>not completed      | Bit.<br>C0 is in low<br>C0 is active<br>ode Bit.<br>abled, tracl<br>ADCM1-0<br>sion Comp<br>ed by softw<br>leted a data | Bit3<br>-power shu<br>and ready<br>king is cont<br>bits.<br>lete Interru<br>vare. | itdown.<br>for data con<br>inuous unles | versions.     | BitO                   | _           |  |  |  |  |  |  |

| Bit6:<br>Bit5:<br>Bit4:                                    | 0: ADC0 Dis.<br>1: ADC0 Ena<br>AD0TM: ADC<br>0: When the<br>1: Tracking E<br>AD0INT: ADC<br>This flag mu:<br>0: ADC0 has<br>1: ADC0 has<br>AD0BUSY: A<br>Read:<br>0: ADC0 Cor                      | abled. ADC<br>abled. ADC<br>C Track Mc<br>ADC is en<br>Defined by<br>C0 Conver<br>st be cleare<br>not completed                   | C0 is in low<br>C0 is active<br>ode Bit.<br>abled, tracl<br>ADCM1-0<br>sion Comp<br>ed by softw<br>leted a data         | and ready<br>king is cont<br>bits.<br>lete Interru<br>vare.                       | for data con<br>inuous unles            |               | ion is in pro          | ocess.      |  |  |  |  |  |  |

| Bit6:<br>Bit5:<br>Bit4:                                    | 0: ADC0 Dis.<br>1: ADC0 Ena<br>AD0TM: ADC<br>0: When the<br>1: Tracking E<br>AD0INT: ADC<br>This flag mu:<br>0: ADC0 has<br>1: ADC0 has<br>AD0BUSY: A<br>Read:<br>0: ADC0 Cor                      | abled. ADC<br>abled. ADC<br>C Track Mc<br>ADC is en<br>Defined by<br>C0 Conver<br>st be cleare<br>not completed                   | C0 is in low<br>C0 is active<br>ode Bit.<br>abled, tracl<br>ADCM1-0<br>sion Comp<br>ed by softw<br>leted a data         | and ready<br>king is cont<br>bits.<br>lete Interru<br>vare.                       | for data con<br>inuous unles            |               | ion is in pro          | ocess.      |  |  |  |  |  |  |

| Bit5:<br>Bit4:                                             | 1: ADC0 Ena<br>AD0TM: AD0<br>0: When the<br>1: Tracking I<br>AD0INT: AD0<br>This flag mus<br>0: ADC0 has<br>1: ADC0 has<br>AD0BUSY: A<br>Read:<br>0: ADC0 Cor                                      | abled. ADC<br>C Track Mc<br>ADC is en<br>Defined by<br>C0 Conver<br>st be cleare<br>not comple                                    | C0 is active<br>ode Bit.<br>abled, tracl<br>ADCM1-0<br>sion Comp<br>ed by softw<br>leted a data                         | and ready<br>king is cont<br>bits.<br>lete Interru<br>vare.                       | for data con<br>inuous unles            |               | ion is in pro          | ocess.      |  |  |  |  |  |  |

| Bit5:<br>Bit4:                                             | ADOTM: ADO<br>0: When the<br>1: Tracking I<br>ADOINT: ADO<br>This flag mus<br>0: ADC0 has<br>1: ADC0 has<br>AD0BUSY: A<br>Read:<br>0: ADC0 Cor                                                     | C Track Mo<br>ADC is en<br>Defined by<br>C0 Conver<br>st be cleare<br>not comple<br>completed                                     | ode Bit.<br>abled, tracl<br>ADCM1-0<br>sion Comp<br>ed by softw<br>leted a data                                         | king is cont<br>bits.<br>lete Interru<br>vare.                                    | inuous unles                            |               | ion is in pro          | ocess.      |  |  |  |  |  |  |

| Bit5:<br>Bit4:                                             | 0: When the<br>1: Tracking I<br>ADOINT: ADO<br>This flag mus<br>0: ADC0 has<br>1: ADC0 has<br>AD0BUSY: A<br>Read:<br>0: ADC0 Cor                                                                   | ADC is en<br>Defined by<br>C0 Conver<br>st be cleare<br>not completed                                                             | abled, tracl<br>ADCM1-0<br>sion Comp<br>ed by softw<br>leted a data                                                     | bits.<br>lete Interru<br>vare.                                                    |                                         | ss a convers  | ion is in pro          | cess.       |  |  |  |  |  |  |

| Bit4:                                                      | 1: Tracking E<br>ADOINT: ADO<br>This flag mus<br>0: ADC0 has<br>1: ADC0 has<br>AD0BUSY: A<br>Read:<br>0: ADC0 Cor                                                                                  | Defined by<br>C0 Conver<br>st be cleare<br>not completed<br>completed                                                             | ADCM1-0<br>sion Comp<br>ed by softw<br>leted a data                                                                     | bits.<br>lete Interru<br>vare.                                                    |                                         |               |                        |             |  |  |  |  |  |  |

| Bit4:                                                      | ADOINT: ADO<br>This flag mus<br>0: ADC0 has<br>1: ADC0 has<br>AD0BUSY: A<br>Read:<br>0: ADC0 Cor                                                                                                   | C0 Conver<br>st be cleare<br>not completed                                                                                        | sion Comp<br>ed by softw<br>leted a data                                                                                | lete Interru<br>are.                                                              | pt Flag.                                |               |                        |             |  |  |  |  |  |  |

| Bit4:                                                      | This flag mus<br>0: ADC0 has<br>1: ADC0 has<br>AD0BUSY: A<br>Read:<br>0: ADC0 Cor                                                                                                                  | st be cleare<br>not compl<br>completee                                                                                            | ed by softw<br>leted a data                                                                                             | vare.                                                                             | p                                       |               |                        |             |  |  |  |  |  |  |

|                                                            | 0: ADC0 has<br>1: ADC0 has<br>AD0BUSY: A<br>Read:<br>0: ADC0 Cor                                                                                                                                   | not completed                                                                                                                     | leted a data                                                                                                            |                                                                                   |                                         |               |                        |             |  |  |  |  |  |  |

|                                                            | 1: ADC0 has<br>AD0BUSY: A<br>Read:<br>0: ADC0 Cor                                                                                                                                                  | completed                                                                                                                         |                                                                                                                         | a conversio                                                                       | n since the l                           | ast time this | flag was cl            | eared.      |  |  |  |  |  |  |

|                                                            | AD0BUSY: A<br>Read:<br>0: ADC0 Cor                                                                                                                                                                 | •                                                                                                                                 | u a uala UU                                                                                                             |                                                                                   |                                         |               | U U                    |             |  |  |  |  |  |  |

| Bits3–2:                                                   | 0: ADC0 Cor                                                                                                                                                                                        |                                                                                                                                   |                                                                                                                         |                                                                                   |                                         |               |                        |             |  |  |  |  |  |  |

| Bits3–2:                                                   |                                                                                                                                                                                                    |                                                                                                                                   |                                                                                                                         |                                                                                   |                                         |               |                        |             |  |  |  |  |  |  |

| Bits3–2:                                                   | to logic 1 on                                                                                                                                                                                      | 0: ADC0 Conversion is complete or a conversion is not currently in progress. AD0INT is set                                        |                                                                                                                         |                                                                                   |                                         |               |                        |             |  |  |  |  |  |  |

| Bits3–2:                                                   |                                                                                                                                                                                                    | to logic 1 on the falling edge of AD0BUSY.                                                                                        |                                                                                                                         |                                                                                   |                                         |               |                        |             |  |  |  |  |  |  |

| Bits3–2:                                                   | 1: ADC0 Conversion is in progress.                                                                                                                                                                 |                                                                                                                                   |                                                                                                                         |                                                                                   |                                         |               |                        |             |  |  |  |  |  |  |

| Bits3–2:                                                   | Write:                                                                                                                                                                                             |                                                                                                                                   |                                                                                                                         |                                                                                   |                                         |               |                        |             |  |  |  |  |  |  |

| Bits3–2:                                                   | 0: No Effect.<br>1: Initiates ADC0 Conversion if AD0CM1-0 = 00b.                                                                                                                                   |                                                                                                                                   |                                                                                                                         |                                                                                   |                                         |               |                        |             |  |  |  |  |  |  |

| Bits3-2:                                                   |                                                                                                                                                                                                    |                                                                                                                                   |                                                                                                                         |                                                                                   |                                         |               |                        |             |  |  |  |  |  |  |

|                                                            | AD0CM1 $-0$ :<br>If AD0TM = 0                                                                                                                                                                      |                                                                                                                                   | rt of Conve                                                                                                             | rsion wode                                                                        | e Select.                               |               |                        |             |  |  |  |  |  |  |

|                                                            | 00: ADC0 co                                                                                                                                                                                        |                                                                                                                                   | aitiated on (                                                                                                           | ovory write                                                                       |                                         | BUSY          |                        |             |  |  |  |  |  |  |

|                                                            | 00. ADC0 co                                                                                                                                                                                        |                                                                                                                                   |                                                                                                                         |                                                                                   |                                         | 0001.         |                        |             |  |  |  |  |  |  |

|                                                            | 10: ADC0 co                                                                                                                                                                                        |                                                                                                                                   |                                                                                                                         |                                                                                   |                                         |               |                        |             |  |  |  |  |  |  |

|                                                            | 11: ADC0 co                                                                                                                                                                                        |                                                                                                                                   |                                                                                                                         |                                                                                   |                                         |               |                        |             |  |  |  |  |  |  |

|                                                            | If AD0TM = $^{-1}$                                                                                                                                                                                 |                                                                                                                                   |                                                                                                                         |                                                                                   | 111101 2.                               |               |                        |             |  |  |  |  |  |  |

|                                                            | 00: Tracking starts with the write of '1' to AD0BUSY and lasts for 3 SAR clocks, followed by                                                                                                       |                                                                                                                                   |                                                                                                                         |                                                                                   |                                         |               |                        |             |  |  |  |  |  |  |

|                                                            | conversion.                                                                                                                                                                                        |                                                                                                                                   |                                                                                                                         |                                                                                   |                                         |               |                        |             |  |  |  |  |  |  |

|                                                            | 01: Tracking                                                                                                                                                                                       | started by                                                                                                                        | the overflo                                                                                                             | w of Timer                                                                        | 3 and lasts                             | for 3 SAR cl  | ocks, follow           | ed by con-  |  |  |  |  |  |  |

|                                                            | 01: Tracking started by the overflow of Timer 3 and lasts for 3 SAR clocks, followed by conversion.                                                                                                |                                                                                                                                   |                                                                                                                         |                                                                                   |                                         |               |                        |             |  |  |  |  |  |  |

|                                                            | 10: ADC0 tra                                                                                                                                                                                       |                                                                                                                                   | hen CNVS                                                                                                                | TR0 input                                                                         | is logic low;                           | conversion s  | starts on risi         | ing         |  |  |  |  |  |  |

|                                                            | CNVSTR0 e                                                                                                                                                                                          |                                                                                                                                   |                                                                                                                         |                                                                                   |                                         |               |                        |             |  |  |  |  |  |  |

|                                                            | 11: Tracking                                                                                                                                                                                       | started by                                                                                                                        | the overflo                                                                                                             | w of Timer                                                                        | 2 and lasts                             | for 3 SAR clo | ocks, follow           | ed by con-  |  |  |  |  |  |  |

|                                                            | version.                                                                                                                                                                                           |                                                                                                                                   | -                                                                                                                       |                                                                                   |                                         |               |                        |             |  |  |  |  |  |  |

| Bit1:                                                      | ADOWINT: A                                                                                                                                                                                         |                                                                                                                                   |                                                                                                                         |                                                                                   | Flag.                                   |               |                        |             |  |  |  |  |  |  |

|                                                            | This bit must                                                                                                                                                                                      |                                                                                                                                   | •                                                                                                                       |                                                                                   |                                         |               |                        |             |  |  |  |  |  |  |

|                                                            | 0: ADC0 Wir                                                                                                                                                                                        |                                                                                                                                   |                                                                                                                         |                                                                                   |                                         | ed since this | s flag was la          | ast cleared |  |  |  |  |  |  |

| BitO.                                                      | 1: ADC0 Wir                                                                                                                                                                                        |                                                                                                                                   |                                                                                                                         |                                                                                   | as occurred.                            |               |                        |             |  |  |  |  |  |  |

| Bit0:                                                      | AD0LJST: Al<br>0: Data in Al                                                                                                                                                                       |                                                                                                                                   |                                                                                                                         |                                                                                   | instified                               |               |                        |             |  |  |  |  |  |  |

|                                                            |                                                                                                                                                                                                    |                                                                                                                                   | OL register                                                                                                             | -                                                                                 | •                                       |               |                        |             |  |  |  |  |  |  |

#### SFR Definition 7.6. ADC2GT: ADC2 Greater-Than Data Byte

### SFR Definition 7.7. ADC2LT: ADC2 Less-Than Data Byte

#### SFR Definition 11.4. SFRNEXT: SFR Next Register

| R/W      | R/W                                                                                                                                       | R/W                                                                                                                 | R/W                                                                                                   | R/W                                                                                                         | R/W                                                                                                | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W                                                                                      | Reset Value                                                        |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|          |                                                                                                                                           |                                                                                                                     |                                                                                                       |                                                                                                             |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                          | 0000000                                                            |

| Bit7     | Bit6                                                                                                                                      | Bit5                                                                                                                | Bit4                                                                                                  | Bit3                                                                                                        | Bit2                                                                                               | Bit1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Bit0                                                                                     | _                                                                  |

|          |                                                                                                                                           |                                                                                                                     |                                                                                                       |                                                                                                             |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SFR Address                                                                              | : 0x85                                                             |

|          |                                                                                                                                           |                                                                                                                     |                                                                                                       |                                                                                                             |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SFR Page                                                                                 | : All Pages                                                        |

| Bits7–0: | SFR Page S<br>a 3 byte SFR<br>LAST is the t<br>Stack, and w<br>rupts cause p<br>Write: Sets<br>the SFRPAG<br>Read: Retu<br>This is the va | R Page Stac<br>third entry. <sup>-</sup><br>ill not cause<br>pushes and<br>the SFR P<br>E SFR to h<br>urns the valu | ck: SFRPAG<br>The SFR sta<br>e the stack<br>pops of the<br>age contain<br>ave this SF<br>ue of the SF | GE is the firs<br>ack bytes m<br>to 'push' or<br>e SFR Page<br>ned in the se<br>R page value<br>FR page cou | at entry, SFI<br>ay be used<br>'pop'. Only<br>Stack.<br>econd byte<br>ue upon a r<br>ntained in th | RNEXT is the alter the contribution interrupts a of the SFR eturn from it is second by the second by | ne second,<br>ontext in the<br>and return f<br>Stack. This<br>nterrupt.<br>byte of the s | and SFR-<br>e SFR Page<br>rom inter-<br>s will cause<br>SFR stack. |

### SFR Definition 11.5. SFRLAST: SFR Last Register

| Register | Page |           | Page No.                        |                                             |

|----------|------|-----------|---------------------------------|---------------------------------------------|

| ACC      | 0xE0 | All Pages | Accumulator                     | page 153                                    |

| ADC0CF   | 0xBC | 0         | ADC0 Configuration              | page 62 <sup>1</sup> , page 80 <sup>2</sup> |

| ADC0CN   | 0xE8 | 0         | ADC0 Control                    | page 63 <sup>1</sup> , page 81 <sup>2</sup> |

| ADC0GTH  | 0xC5 | 0         | ADC0 Greater-Than High Byte     | page 66 <sup>1</sup> , page 84 <sup>2</sup> |

| ADC0GTL  | 0xC4 | 0         | ADC0 Greater-Than Low Byte      | page 66 <sup>1</sup> , page 84 <sup>2</sup> |

| ADC0H    | 0xBF | 0         | ADC0 Data Word High Byte        | page 64 <sup>1</sup> , page 82 <sup>2</sup> |

| ADC0L    | 0xBE | 0         | ADC0 Data Word Low Byte         | page 64 <sup>1</sup> , page 82 <sup>2</sup> |

| ADC0LTH  | 0xC7 | 0         | ADC0 Less-Than High Byte        | page 67 <sup>1</sup> , page 85 <sup>2</sup> |

| ADC0LTL  | 0xC6 | 0         | ADC0 Less-Than Low Byte         | page 67 <sup>1</sup> , page 85 <sup>2</sup> |

| ADC2     | 0xBE | 2         | ADC2 Data Word                  | page 99 <sup>3</sup>                        |

| ADC2CF   | 0xBC | 2         | ADC2 Configuration              | page 97 <sup>3</sup>                        |

| ADC2CN   | 0xE8 | 2         | ADC2 Control                    | page 98 <sup>3</sup>                        |

| ADC2GT   | 0xC4 | 2         | ADC2 Greater-Than               | page 102 <sup>3</sup>                       |

| ADC2LT   | 0xC6 | 2         | ADC2 Less-Than                  | page 102 <sup>3</sup>                       |

| AMX0CF   | 0xBA | 0         | ADC0 Multiplexer Configuration  | page 60 <sup>1</sup> , page 78 <sup>2</sup> |

| AMX0SL   | 0xBB | 0         | ADC0 Multiplexer Channel Select | page 61 <sup>1</sup> , page 79 <sup>2</sup> |

| AMX2CF   | 0xBA | 2         | ADC2 Multiplexer Configuration  | page 95 <sup>3</sup>                        |

| AMX2SL   | 0xBB | 2         | ADC2 Multiplexer Channel Select | page 96 <sup>3</sup>                        |

| В        | 0xF0 | All Pages | •                               | page 153                                    |

| CCH0CN   | 0xA1 | F         | Cache Control                   | page 215                                    |

| CCH0LC   | 0xA3 | F         | Cache Lock                      | page 216                                    |

| CCH0MA   | 0x9A | F         | Cache Miss Accumulator          | page 217                                    |

| CCH0TN   | 0xA2 | F         | Cache Tuning                    | page 216                                    |

| CKCON    | 0x8E | 0         | Clock Control                   | page 315                                    |

| CLKSEL   | 0x97 | F         | System Clock Select             | page 188                                    |

| CPT0CN   | 0x88 | 1         | Comparator 0 Control            | page 123                                    |

| CPT0MD   | 0x89 | 1         | Comparator 0 Configuration      | page 123                                    |

| CPT1CN   | 0x88 | 2         | Comparator 1 Control            | page 124                                    |

| CPT1MD   | 0x89 | 2         | Comparator 1 Configuration      | page 125                                    |

| DAC0CN   | 0xD4 | 0         | DAC0 Control                    | page 108 <sup>3</sup>                       |

| DAC0H    | 0xD3 | 0         | DAC0 High Byte                  | page 107 <sup>3</sup>                       |

| DAC0L    | 0xD2 | 0         | DAC0 Low Byte                   | page 107 <sup>3</sup>                       |

| DAC1CN   | 0xD4 | 1         | DAC1 Control                    | page 110 <sup>3</sup>                       |

| DAC1H    | 0xD3 | 1         | DAC1 High Byte                  | page 109 <sup>3</sup>                       |

| DAC1L    | 0xD2 | 1         | DAC1 Low Byte                   | page 109 <sup>3</sup>                       |

| DPH      | 0x83 | All Pages |                                 | page 151                                    |

| DPL      | 0x82 | All Pages |                                 | page 151                                    |

### Table 11.3. Special Function Registers

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

| R/W   | R/W                         | R/W        | R/W           | R/W            | R/W       | R/W        | R/W        | Reset Value             |

|-------|-----------------------------|------------|---------------|----------------|-----------|------------|------------|-------------------------|

| -     | ES1                         | -          | EADC2         | EWADC2         | ET4       | EADC0      | ET3        | 00000000                |

| Bit7  | Bit6                        | Bit5       | Bit4          | Bit3           | Bit2      | Bit1       | Bit0       |                         |

|       |                             |            |               |                |           |            | SFR Addres | s: 0xE7<br>e: All Pages |

|       |                             |            |               |                |           |            | or ren ag  | o. / all l'agoo         |

| Bit7: | UNUSED. R                   |            |               | 't care.       |           |            |            |                         |

| Bit6: | ES1: Enable                 |            |               |                |           |            |            |                         |

|       | This bit sets               |            |               | ART1 interrup  | ot.       |            |            |                         |

|       | 0: Disable U                |            | •             |                |           |            |            |                         |

| D     | 1: Enable U/                |            |               |                |           |            |            |                         |

| Bit5: | UNUSED. R                   |            |               |                |           |            |            |                         |

| Bit4: | This bit sets               |            |               | nversion Inter | •         | intorrunt  |            |                         |

|       | 0: Disable A                |            | •             |                | onversion | interrupt. |            |                         |

|       | 1: Enable A                 |            |               |                |           |            |            |                         |

| Bit3: | EWADC2: E                   |            |               |                | nterrupt. |            |            |                         |

|       |                             |            |               | Window Cor     | •         | nterrupt.  |            |                         |

|       | 0: Disable A                |            |               |                |           | •          |            |                         |

|       | 1: Enable A[                | C2 Windo   | w Compari     | son Interrupt  | S.        |            |            |                         |

| Bit2: | ET4: Enable                 | Timer 4 In | terrupt       |                |           |            |            |                         |

|       | This bit sets               | the maskir | ng of the Tir | mer 4 interrup | ot.       |            |            |                         |

|       | 0: Disable Ti               |            | •             |                |           |            |            |                         |

|       | 1: Enable Tir               |            | •             |                |           |            |            |                         |

| Bit1: | EADC0: Ena                  |            |               |                |           | •          |            |                         |

|       | This bit sets               |            | •             |                | onversion | Interrupt. |            |                         |

|       | 0: Disable A                |            |               |                |           |            |            |                         |

| Bit0: | 1: Enable AE<br>ET3: Enable |            |               | n interrupts.  |           |            |            |                         |

| DILU. | This bit sets               |            | •             | nor 3 interrur | ht.       |            |            |                         |

|       | 0: Disable Ti               |            |               |                |           |            |            |                         |

|       | 1: Enable Tir               |            | •             |                |           |            |            |                         |

|       |                             |            |               |                |           |            |            |                         |

|       |                             |            |               |                |           |            |            |                         |

### SFR Definition 11.15. EIE2: Extended Interrupt Enable 2

#### 12.6. Rounding and Saturation

A Rounding Engine is included, which can be used to provide a rounded result when operating on fractional numbers. MAC0 uses an unbiased rounding algorithm to round the data stored in bits 31–16 of the accumulator, as shown in Table 12.1. Rounding occurs during the third stage of the MAC0 pipeline, after any shift operation, or on a write to the LSB of the accumulator. The rounded results are stored in the rounding registers: MAC0RNDH (SFR Definition 12.12) and MAC0RNDL (SFR Definition 12.13). The accumulator registers are not affected by the rounding engine. Although rounding is primarily used for fractional data, the data in the rounding registers is updated in the same way when operating in integer mode.

| Accumulator Bits 15–0<br>(MAC0ACC1:MAC0ACC0) | Accumulator Bits 31–16<br>(MAC0ACC3:MAC0ACC2) |      | Rounded Results<br>(MAC0RNDH:MAC0RNDL) |

|----------------------------------------------|-----------------------------------------------|------|----------------------------------------|

| Greater Than 0x8000                          | Anything                                      | Up   | (MAC0ACC3:MAC0ACC2) + 1                |

| Less Than 0x8000                             | Anything                                      | Down | (MAC0ACC3:MAC0ACC2)                    |

| Equal To 0x8000                              | Odd (LSB = 1)                                 | Up   | (MAC0ACC3:MAC0ACC2) + 1                |

| Equal To 0x8000                              | Even (LSB = 0)                                | Down | (MAC0ACC3:MAC0ACC2)                    |

Table 12.1. MAC0 Rounding (MAC0SAT = 0)

The rounding engine can also be used to saturate the results stored in the rounding registers. If the MACOSAT bit is set to '1' and the rounding register overflows, the rounding registers will saturate. When a positive overflow occurs, the rounding registers will show a value of 0x7FFF when saturated. For a negative overflow, the rounding registers will show a value of 0x8000 when saturated. If the MACOSAT bit is cleared to '0', the rounding registers will not saturate.

### 12.7. Usage Examples

This section details some software examples for using MAC0. **Section 12.7.1** shows a series of two MAC operations using fractional numbers. **Section 12.7.2** shows a single operation in Multiply Only mode with integer numbers. The last example, shown in **Section 12.7.3**, demonstrates how the left-shift and right-shift operations can be used to modify the accumulator. All of the examples assume that all of the flags in the MAC0STA register are initially set to '0'.

#### 12.7.1. Multiply and Accumulate Example

The example below implements the equation:

```

(0.5 \times 0.25) + (0.5 \times -0.25) = 0.125 - 0.125 = 0.0

```

| MOV | MACOCF, | #0Ah |   | Set to Clear Accumulator, Use fractional numbers              |

|-----|---------|------|---|---------------------------------------------------------------|

| MOV | МАСОАН, | #40h | ; | Load MACOA register with 4000 hex = 0.5 decimal               |

| MOV | MACOAL, | #00h |   |                                                               |

| MOV | MACOBH, | #20h | ; | Load MACOB register with 2000 hex = 0.25 decimal              |

| MOV | MACOBL, | #00h | ; | This line initiates the first MAC operation                   |

| MOV | MACOBH, | #E0h | ; | Load MACOB register with E000 hex = $-0.25$ decimal           |

| MOV | MACOBL, | #00h | ; | This line initiates the second MAC operation                  |

| NOP |         |      |   |                                                               |

| NOP |         |      | ; | After this instruction, the Accumulator should be equal to 0, |

|     |         |      | ; | and the MACOSTA register should be 0x04, indicating a zero    |

| NOP |         |      | ; | After this instruction, the Rounding register is updated      |

#### 13.3. External Reset

The external RST pin provides a means for external circuitry to force the MCU into a reset state. Asserting the RST pin low will cause the MCU to enter the reset state. It may be desirable to provide an external pullup and/or decoupling of the RST pin to avoid erroneous noise-induced resets. The MCU will remain in reset until at least 12 clock cycles after the active-low RST signal is removed. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

#### 13.4. Missing Clock Detector Reset

The Missing Clock Detector is essentially a one-shot circuit that is triggered by the MCU system clock. If the system clock goes away for more than 100  $\mu$ s, the one-shot will time out and generate a reset. After a Missing Clock Detector reset, the MCDRSF flag (RSTSRC.2) will be set, signifying the MSD as the reset source; otherwise, this bit reads '0'. The state of the RST pin is unaffected by this reset. Setting the MCDRSF bit, RSTSRC.2 (see Section "14. Oscillators" on page 185) enables the Missing Clock Detector.

#### 13.5. Comparator0 Reset

Comparator0 can be configured as a reset input by writing a '1' to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled using CPT0CN.7 (see Section "**10. Comparators**" on page **119**) prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (CP0+ pin) is less than the inverting input voltage (CP0- pin), the MCU is put into the reset state. After a Comparator0 Reset, the CORSEF flag (RSTSRC.5) will read '1' signifying Comparator0 as the reset source; otherwise, this bit reads '0'. The state of the RST pin is unaffected by this reset.

#### 13.6. External CNVSTR0 Pin Reset

The external CNVSTR0 signal can be configured as a reset input by writing a '1' to the CNVRSEF flag (RSTSRC.6). The CNVSTR0 signal can appear on any of the P0, P1, P2 or P3 I/O pins as described in Section "**18.1. Ports 0 through 3 and the Priority Crossbar Decoder**" on page **238**. Note that the Crossbar must be configured for the CNVSTR0 signal to be routed to the appropriate Port I/O. The Crossbar should be configured and enabled before the CNVRSEF is set. When configured as a reset, CNVSTR0 is active-low and level sensitive. CNVSTR0 cannot be used to start ADC0 conversions when it is configured as a reset source. After a CNVSTR0 reset, the CNVRSEF flag (RSTSRC.6) will read '1' signifying CNVSTR0 as the reset source; otherwise, this bit reads '0'. The state of the /RST pin is unaffected by this reset.

#### 13.7. Watchdog Timer Reset

The MCU includes a programmable Watchdog Timer (WDT) running off the system clock. A WDT overflow will force the MCU into the reset state. To prevent the reset, the WDT must be restarted by application software before overflow. If the system experiences a software or hardware malfunction preventing the software from restarting the WDT, the WDT will overflow and cause a reset. This should prevent the system from running out of control.

Following a reset the WDT is automatically enabled and running with the default maximum time interval. If desired the WDT can be disabled by system software or locked on to prevent accidental disabling. Once locked, the WDT cannot be disabled until the next system reset. The state of the RST pin is unaffected by this reset.