# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 50MHz                                                           |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 64                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 8.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 8x8b, 8x10b; D/A 2x12b                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 100-TQFP                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f126-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| SFR Definition 16.5. FLSTAT: Flash Status                      | 217 |

|----------------------------------------------------------------|-----|

| SFR Definition 17.1. EMIOCN: External Memory Interface Control | 220 |

| SFR Definition 17.2. EMI0CF: External Memory Configuration     |     |

| SFR Definition 17.3. EMIOTC: External Memory Timing Control    |     |

| SFR Definition 18.1. XBR0: Port I/O Crossbar Register 0        |     |

| SFR Definition 18.2. XBR1: Port I/O Crossbar Register 1        |     |

| SFR Definition 18.3. XBR2: Port I/O Crossbar Register 2        |     |

| SFR Definition 18.4. P0: Port0 Data                            |     |

| SFR Definition 18.5. P0MDOUT: Port0 Output Mode                | 248 |

| SFR Definition 18.6. P1: Port1 Data                            | 249 |

| SFR Definition 18.7. P1MDIN: Port1 Input Mode                  | 249 |

| SFR Definition 18.8. P1MDOUT: Port1 Output Mode                | 250 |

| SFR Definition 18.9. P2: Port2 Data                            | 250 |

| SFR Definition 18.10. P2MDOUT: Port2 Output Mode               | 251 |

| SFR Definition 18.11. P3: Port3 Data                           | 251 |

| SFR Definition 18.12. P3MDOUT: Port3 Output Mode               | 252 |

| SFR Definition 18.13. P4: Port4 Data                           |     |

| SFR Definition 18.14. P4MDOUT: Port4 Output Mode               | 254 |

| SFR Definition 18.15. P5: Port5 Data                           | 255 |

| SFR Definition 18.16. P5MDOUT: Port5 Output Mode               | 255 |

| SFR Definition 18.17. P6: Port6 Data                           |     |

| SFR Definition 18.18. P6MDOUT: Port6 Output Mode               |     |

| SFR Definition 18.19. P7: Port7 Data                           |     |

| SFR Definition 18.20. P7MDOUT: Port7 Output Mode               | 257 |

| SFR Definition 19.1. SMB0CN: SMBus0 Control                    | 266 |

| SFR Definition 19.2. SMB0CR: SMBus0 Clock Rate                 | 267 |

| SFR Definition 19.3. SMB0DAT: SMBus0 Data                      |     |

| SFR Definition 19.4. SMB0ADR: SMBus0 Address                   | 269 |

| SFR Definition 19.5. SMB0STA: SMBus0 Status                    |     |

| SFR Definition 20.1. SPI0CFG: SPI0 Configuration               |     |

| SFR Definition 20.2. SPI0CN: SPI0 Control                      |     |

| SFR Definition 20.3. SPI0CKR: SPI0 Clock Rate                  |     |

| SFR Definition 20.4. SPI0DAT: SPI0 Data                        |     |

| SFR Definition 21.1. SCON0: UART0 Control                      |     |

| SFR Definition 21.2. SSTA0: UART0 Status and Clock Selection   |     |

| SFR Definition 21.3. SBUF0: UART0 Data Buffer                  |     |

| SFR Definition 21.4. SADDR0: UART0 Slave Address               |     |

| SFR Definition 21.5. SADEN0: UARTO Slave Address Enable        | 298 |

| SFR Definition 22.1. SCON1: Serial Port 1 Control              |     |

| SFR Definition 22.2. SBUF1: Serial (UART1) Port Data Buffer    |     |

| SFR Definition 23.1. TCON: Timer Control                       |     |

| SFR Definition 23.2. TMOD: Timer Mode                          |     |

| SFR Definition 23.3. CKCON: Clock Control                      |     |

| SFR Definition 23.4. TL0: Timer 0 Low Byte                     |     |

| SFR Definition 23.5. TL1: Timer 1 Low Byte                     | 316 |

|                                                                |     |

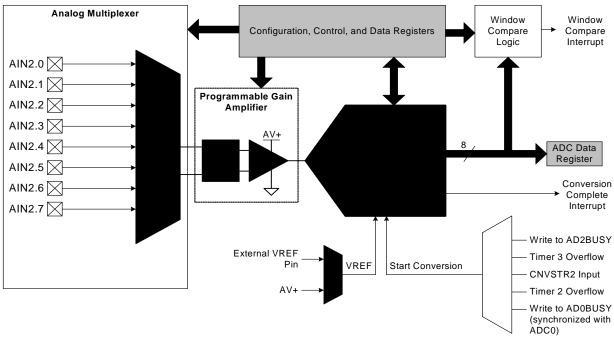

#### 1.9. 8-Bit Analog to Digital Converter

The C8051F12x devices have an on-board 8-bit SAR ADC (ADC2) with an 8-channel input multiplexer and programmable gain amplifier. This ADC features a 500 ksps maximum throughput and true 8-bit linearity with an INL of ±1LSB. Eight input pins are available for measurement. The ADC is under full control of the CIP-51 microcontroller via the Special Function Registers. The ADC2 voltage reference is selected between the analog power supply (AV+) and an external VREF pin. On the 100-pin TQFP devices, ADC2 has its own dedicated Voltage Reference input pin; on the 64-pin TQFP devices, ADC2 shares a Voltage Reference input pin with ADC0. User software may put ADC2 into shutdown mode to save power.

A programmable gain amplifier follows the analog multiplexer. The gain stage can be especially useful when different ADC input channels have widely varied input voltage signals, or when it is necessary to "zoom in" on a signal with a large DC offset (in differential mode, a DAC could be used to provide the DC offset). The PGA gain can be set in software to 0.5, 1, 2, or 4.

A flexible conversion scheduling system allows ADC2 conversions to be initiated by software commands, timer overflows, or an external input signal. ADC2 conversions may also be synchronized with ADC0 software-commanded conversions. Conversion completions are indicated by a status bit and an interrupt (if enabled), and the resulting 8-bit data word is latched into an SFR upon completion.

Figure 1.14. 8-Bit ADC Diagram

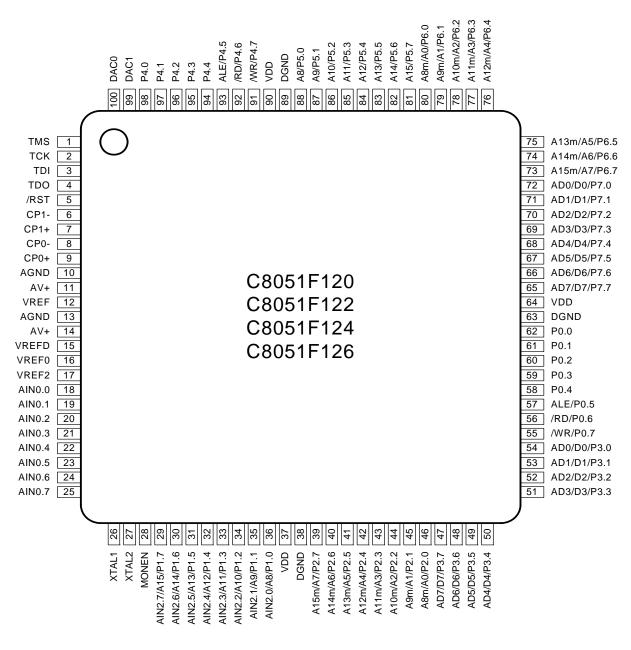

Figure 4.1. C8051F120/2/4/6 Pinout Diagram (TQFP-100)

#### SFR Definition 5.4. ADC0CN: ADC0 Control

| SFR Addre<br>R/W | R/W                                                                                                                      | (bit addre<br>R/W | R/W           | R/W          | R/W           | R/W            | R/W            | Reset Value |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------|---------------|--------------|---------------|----------------|----------------|-------------|--|--|--|

| ADOE             | AD0TM                                                                                                                    | <b>AD0INT</b>     | AD0BUSY       | AD0CM1       | AD0CM0        | <b>ADOWINT</b> | AD0LJST        | 00000000    |  |  |  |

| Bit7             | Bit6                                                                                                                     | Bit5              | Bit4          | Bit3         | Bit2          | Bit1           | Bit0           | _           |  |  |  |

| D:47.            |                                                                                                                          | CO Enchia         | D:4           |              |               |                |                |             |  |  |  |

| Bit7:            | AD0EN: AD                                                                                                                |                   |               | nowor ob     | tdown         |                |                |             |  |  |  |

|                  | 0: ADC0 Dis<br>1: ADC0 En                                                                                                |                   |               |              |               | versions       |                |             |  |  |  |

| Bit6:            | ADOTM: AD                                                                                                                |                   |               | anu reauy    |               | versions.      |                |             |  |  |  |

| Dito.            |                                                                                                                          |                   |               | kina is cont | inuous unles  | ss a convers   | ion is in pro  | Cess        |  |  |  |

|                  | 1: Tracking                                                                                                              |                   |               |              |               |                |                | 0000.       |  |  |  |

| Bit5:            | AD0INT: AD                                                                                                               |                   |               |              | ot Flag.      |                |                |             |  |  |  |

|                  | This flag mu                                                                                                             |                   |               |              |               |                |                |             |  |  |  |

|                  |                                                                                                                          |                   |               |              | n since the l | ast time this  | flag was clo   | eared.      |  |  |  |

|                  | 1: ADC0 has                                                                                                              |                   |               |              |               |                | U              |             |  |  |  |

| Bit4:            | AD0BUSY:                                                                                                                 | ADC0 Bus          | y Bit.        |              |               |                |                |             |  |  |  |

|                  | Read:                                                                                                                    |                   |               |              |               |                |                |             |  |  |  |

|                  | 0: ADC0 Conversion is complete or a conversion is not currently in progress. AD0INT is set                               |                   |               |              |               |                |                |             |  |  |  |

|                  | to logic 1 on the falling edge of AD0BUSY.                                                                               |                   |               |              |               |                |                |             |  |  |  |

|                  | 1: ADC0 Conversion is in progress.                                                                                       |                   |               |              |               |                |                |             |  |  |  |

|                  | Write:                                                                                                                   |                   |               |              |               |                |                |             |  |  |  |

|                  | 0: No Effect                                                                                                             |                   |               |              | 0.01          |                |                |             |  |  |  |

| Dite? 2          | 1: Initiates A<br>AD0CM1–0                                                                                               |                   |               |              |               |                |                |             |  |  |  |

| Bits3–2:         | If AD0CMT=0                                                                                                              |                   | an of Conve   |              | Select.       |                |                |             |  |  |  |

|                  |                                                                                                                          |                   | nitiated on ( | ovorv writo  | of '1' to AD( | BUSY           |                |             |  |  |  |

|                  | 00: ADC0 conversion initiated on every write of '1' to AD0BUSY.<br>01: ADC0 conversion initiated on overflow of Timer 3. |                   |               |              |               |                |                |             |  |  |  |

|                  | 10: ADC0 conversion initiated on overnow of nimer 3.                                                                     |                   |               |              |               |                |                |             |  |  |  |

|                  | 11: ADC0 conversion initiated on overflow of Timer 2.                                                                    |                   |               |              |               |                |                |             |  |  |  |

|                  | If $ADOTM = 1$ :                                                                                                         |                   |               |              |               |                |                |             |  |  |  |

|                  | 00: Tracking starts with the write of '1' to AD0BUSY and lasts for 3 SAR clocks, followed by                             |                   |               |              |               |                |                |             |  |  |  |

|                  | conversion.                                                                                                              |                   |               |              |               |                |                |             |  |  |  |

|                  | -                                                                                                                        | started by        | the overflo   | w of Timer   | 3 and lasts   | for 3 SAR cl   | ocks, follow   | ed by con-  |  |  |  |

|                  | version.                                                                                                                 |                   |               |              |               |                |                |             |  |  |  |

|                  |                                                                                                                          |                   | when CNVS     | TR0 input    | is logic low; | conversion s   | starts on risi | ng          |  |  |  |

|                  | CNVSTR0 e                                                                                                                |                   | (I            |              |               |                |                |             |  |  |  |

|                  |                                                                                                                          | started by        | the overflo   | w of Timer   | 2 and lasts   | for 3 SAR clo  | DCKS, TOIIOW   | ed by con-  |  |  |  |

| Di+1.            | version.<br>AD0WINT: A                                                                                                   |                   | low Compo     | ro Intorrunt | Flog          |                |                |             |  |  |  |

| Bit1:            | This bit mus                                                                                                             |                   |               |              | Flag.         |                |                |             |  |  |  |

|                  |                                                                                                                          |                   |               |              | s not occur   | ed since this  | s flag was la  | est cleared |  |  |  |

|                  | 1: ADC0 Wi                                                                                                               |                   |               |              |               |                | s nay was lo   |             |  |  |  |

| Bit0:            | ADOLJST: A                                                                                                               |                   | •             |              |               |                |                |             |  |  |  |

| 2.00.            | 0: Data in A                                                                                                             |                   |               |              | iustified.    |                |                |             |  |  |  |

|                  |                                                                                                                          |                   |               |              |               |                |                |             |  |  |  |

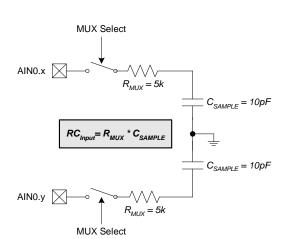

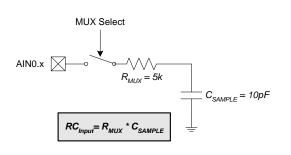

#### 6.2.3. Settling Time Requirements

A minimum tracking time is required before an accurate conversion can be performed. This tracking time is determined by the ADC0 MUX resistance, the ADC0 sampling capacitance, any external source resistance, and the accuracy required for the conversion. Figure 6.4 shows the equivalent ADC0 input circuits for both Differential and Single-ended modes. Notice that the equivalent time constant for both input circuits is the same. The required settling time for a given settling accuracy (*SA*) may be approximated by Equation 6.1. When measuring the Temperature Sensor output,  $R_{TOTAL}$  reduces to  $R_{MUX}$ . An absolute minimum settling time of 1.5 µs is required after any MUX or PGA selection. Note that in low-power tracking mode, three SAR clocks are used for tracking at the start of every conversion. For most applications, these three SAR clocks will meet the tracking requirements.

$$t = \ln\left(\frac{2^n}{SA}\right) \times R_{TOTAL} C_{SAMPLE}$$

### Equation 6.1. ADC0 Settling Time Requirements

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the ADC0 MUX resistance and any external source resistance. *n* is the ADC resolution in bits (10).

**Differential Mode**

Single-Ended Mode

#### Figure 6.4. ADC0 Equivalent Input Circuits

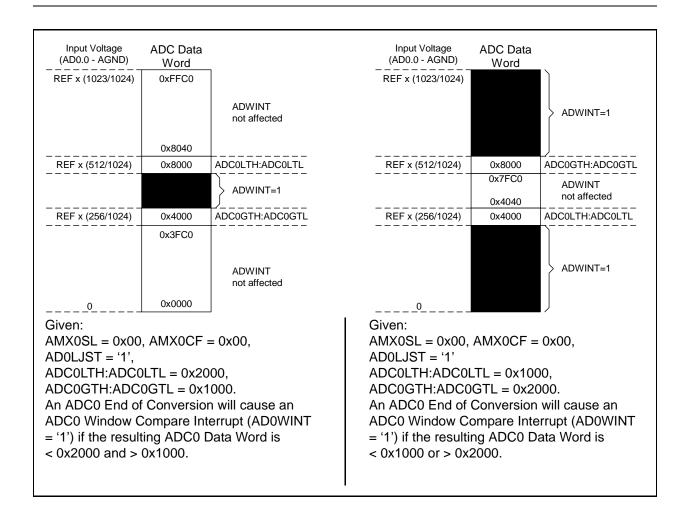

# Figure 6.8. 10-Bit ADC0 Window Interrupt Example: Left Justified Single-Ended Data

#### 7.2. ADC2 Modes of Operation

ADC2 has a maximum conversion speed of 500 ksps. The ADC2 conversion clock (SAR2 clock) is a divided version of the system clock, determined by the AD2SC bits in the ADC2CF register. The maximum ADC2 conversion clock is 6 MHz.

#### 7.2.1. Starting a Conversion

A conversion can be initiated in one of five ways, depending on the programmed states of the ADC2 Start of Conversion Mode bits (AD2CM2-0) in ADC2CN. Conversions may be initiated by:

- 1. Writing a '1' to the AD2BUSY bit of ADC2CN;

- 2. A Timer 3 overflow (i.e. timed continuous conversions);

- 3. A rising edge detected on the external ADC convert start signal, CNVSTR2;

- 4. A Timer 2 overflow (i.e. timed continuous conversions);

- 5. Writing a '1' to the AD0BUSY of register ADC0CN (initiate conversion of ADC2 and ADC0 with a single software command).

During conversion, the AD2BUSY bit is set to logic 1 and restored to 0 when conversion is complete. The falling edge of AD2BUSY triggers an interrupt (when enabled) and sets the interrupt flag in ADC2CN. Converted data is available in the ADC2 data word, ADC2.

When a conversion is initiated by writing a '1' to AD2BUSY, it is recommended to poll AD2INT to determine when the conversion is complete. The recommended procedure is:

Step 1. Write a '0' to AD2INT; Step 2. Write a '1' to AD2BUSY; Step 3. Poll AD2INT for '1'; Step 4. Process ADC2 data.

When CNVSTR2 is used as a conversion start source, it must be enabled in the crossbar, and the corresponding pin must be set to open-drain, high-impedance mode (see **Section "18. Port Input/Output" on page 235** for more details on Port I/O configuration).

#### 7.2.2. Tracking Modes

The AD2TM bit in register ADC2CN controls the ADC2 track-and-hold mode. In its default state, the ADC2 input is continuously tracked, except when a conversion is in progress. When the AD2TM bit is logic 1, ADC2 operates in low-power track-and-hold mode. In this mode, each conversion is preceded by a track-ing period of 3 SAR clocks (after the start-of-conversion signal). When the CNVSTR2 signal is used to initiate conversions in low-power tracking mode, ADC2 tracks only when CNVSTR2 is low; conversion begins on the rising edge of CNVSTR2 (see Figure 7.2). Tracking can also be disabled (shutdown) when the entire chip is in low power standby or sleep modes. Low-power Track-and-Hold mode is also useful when AMUX or PGA settings are frequently changed, due to the settling time requirements described in **Section "7.2.3. Settling Time Requirements" on page 94**.

#### SFR Definition 10.4. CPT1MD: Comparator1 Mode Selection

| R/W      | R/W                                              | R/W            | R/W           | R/W         | R/W                   | R/W    | R/W    | Reset Value |  |  |

|----------|--------------------------------------------------|----------------|---------------|-------------|-----------------------|--------|--------|-------------|--|--|

| -        | -                                                | CP1RIE         | CP1FIE        | -           | -                     | CP1MD1 | CP1MD0 | 00000010    |  |  |

| Bit7     | Bit6                                             | Bit5           | Bit4          | Bit3        | Bit2                  | Bit1   | Bit0   | 1           |  |  |

| Bits7–6: | UNUSED. Re                                       | ad = 00b. V    | /rite = don't | care.       |                       |        |        |             |  |  |

| Bit 5:   | CP1RIE: Con                                      |                |               |             | nable Bit.            |        |        |             |  |  |

|          | 0: Comparato                                     |                |               |             |                       |        |        |             |  |  |

|          | 1: Comparato                                     | •              | •             |             |                       |        |        |             |  |  |

| Bit 4:   | CP1FIE: Con                                      | nparator 0 F   | alling-Edge   | Interrupt E | nable Bit.            |        |        |             |  |  |

|          | 0: Comparator 1 falling-edge interrupt disabled. |                |               |             |                       |        |        |             |  |  |

|          | 1: Comparato                                     | or 1 falling-e | dge interrup  | t enabled.  |                       |        |        |             |  |  |

| Bits3–2: | UNUSED. Re                                       | ad = 00b, V    | /rite = don't | care.       |                       |        |        |             |  |  |

| Bits1–0: | CP1MD1–CF                                        | 1MD0: Com      | nparator1 M   | ode Select  |                       |        |        |             |  |  |

|          | These bits se                                    | lect the resp  | oonse time    | for Compar  | ator1.                |        |        |             |  |  |

|          | Mode                                             | CP0MD1         | CP0MD0        |             | Notes                 |        |        |             |  |  |

|          | 0                                                | 0              | 0             | Faste       | Fastest Response Time |        |        |             |  |  |

|          | 1                                                | 0              | 1             |             | _                     |        |        |             |  |  |

|          | 2                                                | 1              | 0             |             | _                     |        |        |             |  |  |

|          | 3                                                | 1              | 1             | 1           | Power Con             |        |        |             |  |  |

| Mnemonic          | Description                                | Bytes | Ciock    |  |  |  |  |  |  |  |

|-------------------|--------------------------------------------|-------|----------|--|--|--|--|--|--|--|

| MOV direct, @Ri   | Move indirect RAM to direct byte           | 2     | 2        |  |  |  |  |  |  |  |

| MOV direct, #data | Move immediate to direct byte              | 3     | 3        |  |  |  |  |  |  |  |

| MOV @Ri, A        | Move A to indirect RAM                     | 1     | 2        |  |  |  |  |  |  |  |

| MOV @Ri, direct   | Move direct byte to indirect RAM           | 2     | 2        |  |  |  |  |  |  |  |

| MOV @Ri, #data    | Move immediate to indirect RAM             | 2     | 2        |  |  |  |  |  |  |  |

| MOV DPTR, #data16 | Load DPTR with 16-bit constant             | 3     | 3        |  |  |  |  |  |  |  |

| MOVC A, @A+DPTR   | Move code byte relative DPTR to A          | 1     | 3        |  |  |  |  |  |  |  |

| MOVC A, @A+PC     | Move code byte relative PC to A            | 1     | 3        |  |  |  |  |  |  |  |

| MOVX A, @Ri       | Move external data (8-bit address) to A    | 1     | 3        |  |  |  |  |  |  |  |

| MOVX @Ri, A       | Move A to external data (8-bit address)    | 1     | 3        |  |  |  |  |  |  |  |

| MOVX A, @DPTR     | Move external data (16-bit address) to A   | 1     | 3        |  |  |  |  |  |  |  |

| MOVX @DPTR, A     | Move A to external data (16-bit address)   | 1     | 3        |  |  |  |  |  |  |  |

| PUSH direct       | Push direct byte onto stack                | 2     | 2        |  |  |  |  |  |  |  |

| POP direct        | Pop direct byte from stack                 | 2     | 2        |  |  |  |  |  |  |  |

| XCH A, Rn         | Exchange Register with A                   | 1     | 1        |  |  |  |  |  |  |  |

| XCH A, direct     | Exchange direct byte with A                | 2     | 2        |  |  |  |  |  |  |  |

| XCH A, @Ri        | Exchange indirect RAM with A               | 1     | 2        |  |  |  |  |  |  |  |

| XCHD A, @Ri       | Exchange low nibble of indirect RAM with A | 1     | 2        |  |  |  |  |  |  |  |

| - , -             | Boolean Manipulation                       |       |          |  |  |  |  |  |  |  |

| CLR C             | Clear Carry                                | 1     | 1        |  |  |  |  |  |  |  |

| CLR bit           | Clear direct bit                           | 2     | 2        |  |  |  |  |  |  |  |

| SETB C            | Set Carry                                  | 1     | 1        |  |  |  |  |  |  |  |

| SETB bit          | Set direct bit                             | 2     | 2        |  |  |  |  |  |  |  |

| CPL C             | Complement Carry                           | 1     | 1        |  |  |  |  |  |  |  |

| CPL bit           | Complement direct bit                      | 2     | 2        |  |  |  |  |  |  |  |

| ANL C, bit        | AND direct bit to Carry                    | 2     | 2        |  |  |  |  |  |  |  |

| ANL C, /bit       | AND complement of direct bit to Carry      | 2     | 2        |  |  |  |  |  |  |  |

| ORL C, bit        | OR direct bit to carry                     | 2     | 2        |  |  |  |  |  |  |  |

| ORL C, /bit       | OR complement of direct bit to Carry       | 2     | 2        |  |  |  |  |  |  |  |

| MOV C, bit        | Move direct bit to Carry                   | 2     | 2        |  |  |  |  |  |  |  |

| MOV bit, C        | Move Carry to direct bit                   | 2     | 2        |  |  |  |  |  |  |  |

| JC rel            | Jump if Carry is set                       | 2     | 2/3*     |  |  |  |  |  |  |  |

| JNC rel           | Jump if Carry is not set                   | 2     | 2/3*     |  |  |  |  |  |  |  |

| JB bit, rel       | Jump if direct bit is set                  | 3     | 3/4*     |  |  |  |  |  |  |  |

| JNB bit, rel      | Jump if direct bit is not set              | 3     | 3/4*     |  |  |  |  |  |  |  |

| JBC bit, rel      | Jump if direct bit is set and clear bit    | 3     | 3/4*     |  |  |  |  |  |  |  |

|                   | Program Branching                          | 5     | 0/7      |  |  |  |  |  |  |  |

| ACALL addr11      | Absolute subroutine call                   | 2     | 3*       |  |  |  |  |  |  |  |

| LCALL addr16      | Long subroutine call                       | 3     | 3<br>4*  |  |  |  |  |  |  |  |

| RET               | Return from subroutine                     | 1     | 4<br>5*  |  |  |  |  |  |  |  |

| RETI              | Return from interrupt                      | 1     | 5<br>5*  |  |  |  |  |  |  |  |

| AJMP addr11       | Absolute jump                              | 2     | 3*       |  |  |  |  |  |  |  |

| LJMP addr16       |                                            | 3     | 3*<br>4* |  |  |  |  |  |  |  |

| SJMP rel          | Long jump                                  | 2     | 4^<br>3* |  |  |  |  |  |  |  |

|                   | Short jump (relative address)              |       | -        |  |  |  |  |  |  |  |

| JMP @A+DPTR       | Jump indirect relative to DPTR             | 1     | 3*       |  |  |  |  |  |  |  |

#### Table 11.1. CIP-51 Instruction Set Summary (Continued)

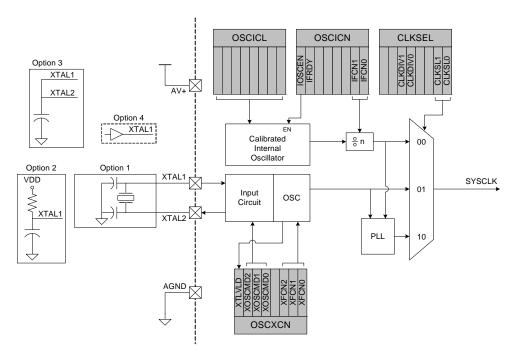

### 14. Oscillators

The devices include a programmable internal oscillator and an external oscillator drive circuit. The internal oscillator can be enabled, disabled, and calibrated using the OSCICN and OSCICL registers, as shown in Figure 14.1. The system clock can be sourced by the external oscillator circuit, the internal oscillator, or the on-chip phase-locked loop (PLL). The internal oscillator's electrical specifications are given in Table 14.1 on page 185.

Figure 14.1. Oscillator Diagram

### Table 14.1. Oscillator Electrical Characteristics

-40°C to +85°C unless otherwise specified.

| Parameter                                                     | Conditions   | Min | Тур  | Max | Units |

|---------------------------------------------------------------|--------------|-----|------|-----|-------|

| Calibrated Internal Oscillator<br>Frequency                   |              | 24  | 24.5 | 25  | MHz   |

| Internal Oscillator Supply<br>Current (from V <sub>DD</sub> ) | OSCICN.7 = 1 | _   | 400  | _   | μA    |

| External Clock Frequency                                      |              | 0   |      | 30  | MHz   |

| T <sub>XCH</sub> (External Clock High Time)                   |              | 15  | _    | _   | ns    |

| T <sub>XCL</sub> (External Clock Low Time)                    |              | 15  | —    | _   | ns    |

#### 14.1. Internal Calibrated Oscillator

All devices include a calibrated internal oscillator that defaults as the system clock after a system reset. The internal oscillator period can be adjusted via the OSCICL register as defined by SFR Definition 14.1. OSCICL is factory calibrated to obtain a 24.5 MHz frequency.

| R/W                 | R/W                                         | R/W          | R/W       | R/W          | R/W          | R/W           | R/W                     | Reset Value  |

|---------------------|---------------------------------------------|--------------|-----------|--------------|--------------|---------------|-------------------------|--------------|

| -                   | -                                           | FLF          | RT        | Reserved     | Reserved     | Reserved      | FLWE                    | 10000000     |

| Bit7                | Bit6                                        | Bit5         | Bit4      | Bit3         | Bit2         | Bit1          | Bit0                    | SFR Address: |

|                     |                                             |              |           |              |              | S             | SFR Address<br>SFR Page |              |

| Bits 7-6:           | Unused.                                     |              |           |              |              |               |                         |              |

| Bits 5-4:           | FLRT: Flash                                 | Read Time.   |           |              |              |               |                         |              |

|                     | These bits sh                               | nould be pro | grammed   | to the small | est allowed  | l value, acco | ording to th            | ie system    |

|                     | clock speed.                                |              |           |              |              |               |                         |              |

|                     | 00: SYSCLK                                  |              |           |              |              |               |                         |              |

|                     | 01: SYSCLK                                  |              |           |              |              |               |                         |              |

|                     | 10: SYSCLK                                  |              |           |              |              |               |                         |              |

|                     | 11: SYSCLK                                  | _            |           |              |              |               |                         |              |

| Bits 3–1:<br>Bit 0: | RESERVED.<br>FLWE: Flash                    |              |           | vrite uuud.  |              |               |                         |              |

| BILU.               | This bit must                               |              |           | writes/erasi | ires from us | sor software  |                         |              |

|                     | 0: Flash write                              |              |           | writes/crast |              | Ser Sonware.  | •                       |              |

|                     | 1: Flash write                              |              |           |              |              |               |                         |              |

|                     |                                             |              |           |              |              |               |                         |              |

| Importan            | t Note: Wher<br>value of 11b<br>disabled us | to 00b), ca  | che reads | s, cache wr  | ites, and th | ne prefetch   | -                       | -            |

|                     |                                             |              |           |              |              |               |                         |              |

|                     |                                             |              |           |              |              |               |                         |              |

#### SFR Definition 15.2. FLSCL: Flash Memory Control

| Parameter                           | Description                                            | Min                     | Max                      | Units |

|-------------------------------------|--------------------------------------------------------|-------------------------|--------------------------|-------|

| T <sub>ACS</sub>                    | Address/Control Setup Time                             | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ACW</sub>                    | Address/Control Pulse Width                            | 1 x T <sub>SYSCLK</sub> | 16 x T <sub>SYSCLK</sub> | ns    |

| T <sub>ACH</sub>                    | Address/Control Hold Time                              | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ALEH</sub>                   | Address Latch Enable High Time                         | 1 x T <sub>SYSCLK</sub> | 4 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ALEL</sub>                   | Address Latch Enable Low Time                          | 1 x T <sub>SYSCLK</sub> | 4 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>WDS</sub>                    | Write Data Setup Time                                  | 1 x T <sub>SYSCLK</sub> | 19 x T <sub>SYSCLK</sub> | ns    |

| T <sub>WDH</sub>                    | Write Data Hold Time                                   | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>RDS</sub>                    | Read Data Setup Time                                   | 20                      | —                        | ns    |

| T <sub>RDH</sub>                    | Read Data Hold Time                                    | 0                       | —                        | ns    |

| <b>√ote:</b> T <sub>SYSCLK</sub> is | s equal to one period of the device system clock (SYSC | CLK).                   |                          |       |

#### Table 17.1. AC Parameters for External Memory Interface

#### 19.3. SMBus Transfer Modes

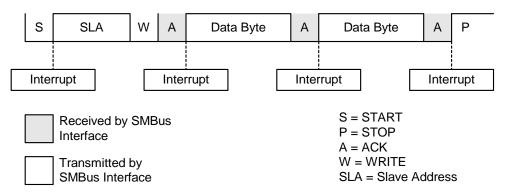

The SMBus0 interface may be configured to operate as a master and/or a slave. At any particular time, the interface will be operating in one of the following modes: Master Transmitter, Master Receiver, Slave Transmitter, or Slave Receiver. See Table 19.1 for transfer mode status decoding using the SMB0STA status register. The following mode descriptions illustrate an interrupt-driven SMBus0 application; SMBus0 may alternatively be operated in polled mode.

#### 19.3.1. Master Transmitter Mode

Serial data is transmitted on SDA while the serial clock is output on SCL. SMBus0 generates a START condition and then transmits the first byte containing the address of the target slave device and the data direction bit. In this case the data direction bit (R/W) will be logic 0 to indicate a "WRITE" operation. The SMBus0 interface transmits one or more bytes of serial data, waiting for an acknowledge (ACK) from the slave after each byte. To indicate the end of the serial transfer, SMBus0 generates a STOP condition.

Figure 19.4. Typical Master Transmitter Sequence

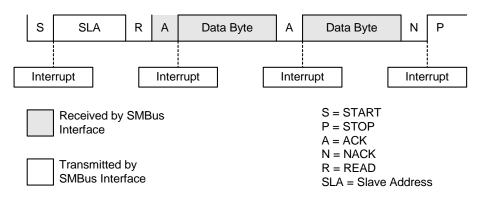

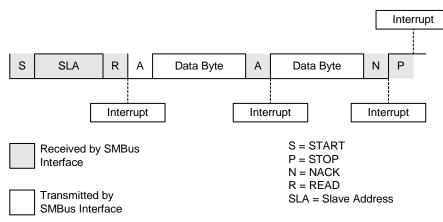

#### 19.3.2. Master Receiver Mode

Serial data is received on SDA while the serial clock is output on SCL. The SMBus0 interface generates a START followed by the first data byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 1 to indicate a "READ" operation. The SMBus0 interface receives serial data from the slave and generates the clock on SCL. After each byte is received, SMBus0 generates an ACK or NACK depending on the state of the AA bit in register SMB0CN. SMBus0 generates a STOP condition to indicate the end of the serial transfer.

#### Figure 19.5. Typical Master Receiver Sequence

#### 19.3.3. Slave Transmitter Mode

Serial data is transmitted on SDA while the serial clock is received on SCL. The SMBus0 interface receives a START followed by data byte containing the slave address and direction bit. If the received slave address matches the address held in register SMB0ADR, the SMBus0 interface generates an ACK. SMBus0 will also ACK if the general call address (0x00) is received and the General Call Address Enable bit (SMB0ADR.0) is set to logic 1. In this case the data direction bit (R/W) will be logic 1 to indicate a "READ" operation. The SMBus0 interface receives the clock on SCL and transmits one or more bytes of serial data, waiting for an ACK from the master after each byte. SMBus0 exits slave mode after receiving a STOP condition from the master.

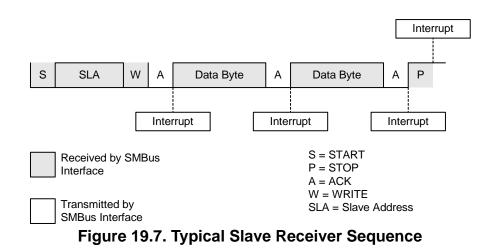

#### 19.3.4. Slave Receiver Mode

Serial data is received on SDA while the serial clock is received on SCL. The SMBus0 interface receives a START followed by data byte containing the slave address and direction bit. If the received slave address matches the address held in register SMB0ADR, the interface generates an ACK. SMBus0 will also ACK if the general call address (0x00) is received and the General Call Address Enable bit (SMB0ADR.0) is set to logic 1. In this case the data direction bit (R/W) will be logic 0 to indicate a "WRITE" operation. The SMBus0 interface receives one or more bytes of serial data; after each byte is received, the interface transmits an ACK or NACK depending on the state of the AA bit in SMB0CN. SMBus0 exits Slave Receiver Mode after receiving a STOP condition from the master.

#### 21.1. UART0 Operational Modes

UART0 provides four operating modes (one synchronous and three asynchronous) selected by setting configuration bits in the SCON0 register. These four modes offer different baud rates and communication protocols. The four modes are summarized in Table 21.1.

| Mode | Synchronization | Baud Clock                   | Data Bits | Start/Stop Bits |

|------|-----------------|------------------------------|-----------|-----------------|

| 0    | Synchronous     | SYSCLK / 12                  | 8         | None            |

| 1    | Asynchronous    | Timer 1, 2, 3, or 4 Overflow | 8         | 1 Start, 1 Stop |

| 2    | Asynchronous    | SYSCLK / 32 or SYSCLK / 64   | 9         | 1 Start, 1 Stop |

| 3    | Asynchronous    | Timer 1, 2, 3, or 4 Overflow | 9         | 1 Start, 1 Stop |

#### Table 21.1. UART0 Modes

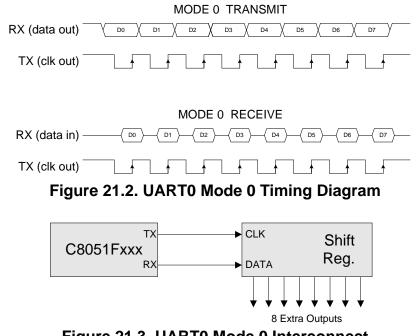

#### 21.1.1. Mode 0: Synchronous Mode

Mode 0 provides synchronous, half-duplex communication. Serial data is transmitted and received on the RX0 pin. The TX0 pin provides the shift clock for both transmit and receive. The MCU must be the master since it generates the shift clock for transmission in both directions (see the interconnect diagram in Figure 21.3).

Data transmission begins when an instruction writes a data byte to the SBUF0 register. Eight data bits are transferred LSB first (see the timing diagram in Figure 21.2), and the TIO Transmit Interrupt Flag (SCON0.1) is set at the end of the eighth bit time. Data reception begins when the REN0 Receive Enable bit (SCON0.4) is set to logic 1 and the RI0 Receive Interrupt Flag (SCON0.0) is cleared. One cycle after the eighth bit is shifted in, the RI0 flag is set and reception stops until software clears the RI0 bit. An interrupt will occur if enabled when either TI0 or RI0 are set.

The Mode 0 baud rate is SYSCLK / 12. RX0 is forced to open-drain in Mode 0, and an external pullup will typically be required.

| R/W      | R/W                                                                                       | R/W                                                                           | R/W                                         | R/W            | R/W          | R/W         | R/W                     | Reset Value |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------|----------------|--------------|-------------|-------------------------|-------------|--|--|--|--|

| GATE1    | C/T1                                                                                      | T1M1                                                                          | T1M0                                        | GATE0          | C/T0         | T0M1        | T0M0                    | 00000000    |  |  |  |  |

| Bit7     | Bit6                                                                                      | Bit5                                                                          | Bit4                                        | Bit3           | Bit2         | Bit1        | Bit0                    |             |  |  |  |  |

|          |                                                                                           |                                                                               |                                             |                |              |             | SFR Address<br>SFR Page |             |  |  |  |  |

| Bit7:    |                                                                                           | enabled w                                                                     | e Control.<br>hen TR1 = 1 i<br>nly when TR1 |                |              | •           |                         |             |  |  |  |  |

| Bit6:    | C/T1: Counter/Timer 1 Select.                                                             |                                                                               |                                             |                |              |             |                         |             |  |  |  |  |

|          | 0: Timer F                                                                                | unction: Tir                                                                  | ner 1 increme                               | ented by cloo  | ck defined   | by T1M bit  | (CKCON.4                | ).          |  |  |  |  |

|          |                                                                                           | Function:                                                                     | Timer 1 increi                              | mented by h    | igh-to-low   | transitions | on external             | input pin   |  |  |  |  |

|          | (T1).                                                                                     |                                                                               |                                             |                |              |             |                         |             |  |  |  |  |

| Bits5–4: |                                                                                           |                                                                               | Mode Select                                 |                |              |             |                         |             |  |  |  |  |

|          | These bits select the Timer 1 operation mode.                                             |                                                                               |                                             |                |              |             |                         |             |  |  |  |  |

|          | T1M1                                                                                      | T1M0                                                                          |                                             | Mod            | е            |             | 7                       |             |  |  |  |  |

|          | 0                                                                                         | 0                                                                             | Мос                                         | le 0: 13-bit o | counter/tim  | er          |                         |             |  |  |  |  |

|          | 0                                                                                         | 1                                                                             | Mode 1: 16-bit counter/timer                |                |              |             |                         |             |  |  |  |  |

|          | 1                                                                                         | 0                                                                             | Mode 2: 8-b                                 |                |              |             |                         |             |  |  |  |  |

|          | 1                                                                                         | 1                                                                             | M                                           | ode 3: Time    | r 1 inactive |             |                         |             |  |  |  |  |

| Bit3:    | GATE0: Ti                                                                                 | mor 0 Cate                                                                    | Control                                     |                |              |             |                         |             |  |  |  |  |

| DIIJ.    |                                                                                           |                                                                               | hen TR0 = 1 i                               | rrespective    | of /INTO Io  | nic level   |                         |             |  |  |  |  |

|          |                                                                                           |                                                                               | nly when TR0                                |                |              |             |                         |             |  |  |  |  |

| Bit2:    | C/T0: Cou                                                                                 |                                                                               |                                             |                |              |             |                         |             |  |  |  |  |

|          | 0: Timer F                                                                                | 0: Timer Function: Timer 0 incremented by clock defined by T0M bit (CKCON.3). |                                             |                |              |             |                         |             |  |  |  |  |

|          | 1: Counter Function: Timer 0 incremented by high-to-low transitions on external input pin |                                                                               |                                             |                |              |             |                         |             |  |  |  |  |

|          | (T0).                                                                                     |                                                                               |                                             |                |              |             |                         |             |  |  |  |  |

| Bits1–0: |                                                                                           |                                                                               | Mode Select                                 |                |              |             |                         |             |  |  |  |  |

|          | These bits                                                                                | select the                                                                    | Timer 0 opera                               | ation mode.    |              |             |                         |             |  |  |  |  |

|          | T0M1                                                                                      | T0M0                                                                          |                                             | Mod            | е            |             | ]                       |             |  |  |  |  |

|          | 0                                                                                         | 0                                                                             | Mod                                         | le 0: 13-bit c | ounter/time  | er          |                         |             |  |  |  |  |

|          | 0                                                                                         | 1                                                                             |                                             | le 1: 16-bit c |              |             | ]                       |             |  |  |  |  |

|          | 1                                                                                         | 0                                                                             | Mode 2: 8-b                                 |                |              |             |                         |             |  |  |  |  |

|          | 1                                                                                         | 1                                                                             | Mode                                        | 3: Two 8-bit   | counter/tin  | ners        |                         |             |  |  |  |  |

|          |                                                                                           |                                                                               |                                             |                |              |             |                         |             |  |  |  |  |

|          |                                                                                           |                                                                               |                                             |                |              |             |                         |             |  |  |  |  |

#### SFR Definition 23.2. TMOD: Timer Mode

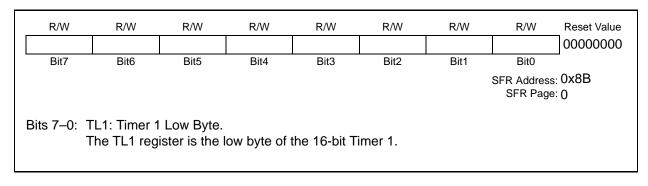

#### SFR Definition 23.5. TL1: Timer 1 Low Byte

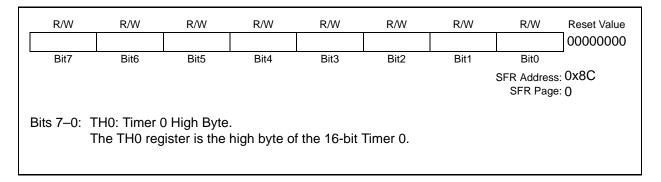

#### SFR Definition 23.6. TH0: Timer 0 High Byte

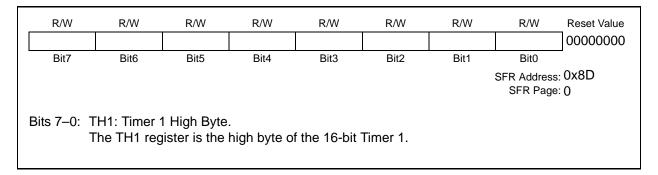

### SFR Definition 23.7. TH1: Timer 1 High Byte

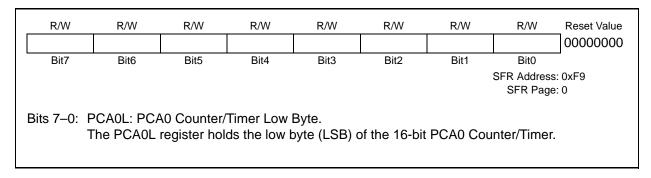

#### SFR Definition 24.4. PCA0L: PCA0 Counter/Timer Low Byte

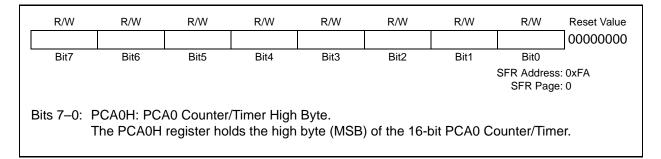

#### SFR Definition 24.5. PCA0H: PCA0 Counter/Timer High Byte

#### SFR Definition 24.6. PCA0CPLn: PCA0 Capture Module Low Byte

| R/W       | R/W                            | R/W                   | R/W           | R/W          | R/W          | R/W            | R/W         | Reset Value |

|-----------|--------------------------------|-----------------------|---------------|--------------|--------------|----------------|-------------|-------------|

|           |                                |                       |               |              |              |                |             | 0000000     |

| Bit7      | Bit6                           | Bit5                  | Bit4          | Bit3         | Bit2         | Bit1           | Bit0        | _           |

| SFR Addre | ess: PCA0CPL0: 0<br>0xE1       | XFB, PCA0CF           | PL1: 0xFD, PC | A0CPL2: 0xE9 | , PCA0CPL3:  | 0xEB, PCA0C    | PL4: 0xED,  | PCA0CPL5:   |

| SFR Pa    | ge: PCA0CPL0: p<br>PCA0CPL5: p | age 0, PCA00<br>age 0 | CPL1: page 0, | PCA0CPL2: pa | age 0, PCA0C | PL3: page 0, F | PCA0CPL4: p | bage 0,     |

| Bits7–0:  | PCA0CPLn: I<br>The PCA0CP      |                       |               |              | B) of the 16 | -bit capture   | module n    |             |