Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 50MHz                                                           |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 32                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 8.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 8x8b, 8x10b; D/A 2x12b                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 64-TQFP                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f127-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1. | System Overview                                       | 19 |

|----|-------------------------------------------------------|----|

|    | 1.1. CIP-51 <sup>™</sup> Microcontroller Core         | 27 |

|    | 1.1.1. Fully 8051 Compatible                          | 27 |

|    | 1.1.2. Improved Throughput                            | 27 |

|    | 1.1.3. Additional Features                            | 28 |

|    | 1.2. On-Chip Memory                                   | 29 |

|    | 1.3. JTAG Debug and Boundary Scan                     | 30 |

|    | 1.4. 16 x 16 MAC (Multiply and Accumulate) Engine     | 31 |

|    | 1.5. Programmable Digital I/O and Crossbar            | 32 |

|    | 1.6. Programmable Counter Array                       |    |

|    | 1.7. Serial Ports                                     |    |

|    | 1.8. 12 or 10-Bit Analog to Digital Converter         | 34 |

|    | 1.9. 8-Bit Analog to Digital Converter                |    |

|    | 1.10.12-bit Digital to Analog Converters              |    |

|    | 1.11.Analog Comparators                               |    |

|    | Absolute Maximum Ratings                              |    |

| 3. |                                                       |    |

| 4. | · · · · · · · · · · · · · · · · · · ·                 |    |

| 5. | ADC0 (12-Bit ADC, C8051F120/1/4/5 Only)               |    |

|    | 5.1. Analog Multiplexer and PGA                       |    |

|    | 5.2. ADC Modes of Operation                           |    |

|    | 5.2.1. Starting a Conversion                          |    |

|    | 5.2.2. Tracking Modes                                 |    |

|    | 5.2.3. Settling Time Requirements                     |    |

|    | 5.3. ADC0 Programmable Window Detector                |    |

| 6. | ADC0 (10-Bit ADC, C8051F122/3/6/7 and C8051F13x Only) |    |

|    | 6.1. Analog Multiplexer and PGA                       |    |

|    | 6.2. ADC Modes of Operation                           |    |

|    | 6.2.1. Starting a Conversion                          |    |

|    | 6.2.2. Tracking Modes                                 |    |

|    | 6.2.3. Settling Time Requirements                     |    |

|    | 6.3. ADC0 Programmable Window Detector                |    |

| 7. | ADC2 (8-Bit ADC, C8051F12x Only)                      |    |

|    | 7.1. Analog Multiplexer and PGA                       |    |

|    | 7.2. ADC2 Modes of Operation                          |    |

|    | 7.2.1. Starting a Conversion                          |    |

|    | 7.2.2. Tracking Modes                                 |    |

|    | 7.2.3. Settling Time Requirements                     |    |

|    | 7.3. ADC2 Programmable Window Detector 1              |    |

|    | 7.3.1. Window Detector In Single-Ended Mode 1         | 00 |

|    | 7.3.2. Window Detector In Differential Mode 1         | 01 |

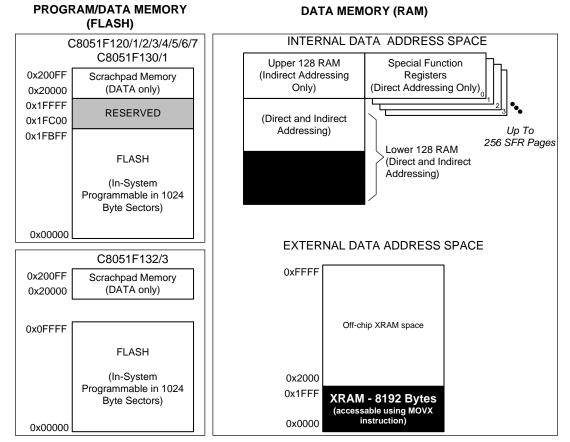

#### 1.2. On-Chip Memory

The CIP-51 has a standard 8051 program and data address configuration. It includes 256 bytes of data RAM, with the upper 128 bytes dual-mapped. Indirect addressing accesses the upper 128 bytes of general purpose RAM, and direct addressing accesses the 128 byte SFR address space. The lower 128 bytes of RAM are accessible via direct and indirect addressing. The first 32 bytes are addressable as four banks of general purpose registers, and the next 16 bytes can be byte addressable or bit addressable.

The devices include an on-chip 8k byte RAM block and an external memory interface (EMIF) for accessing off-chip data memory. The on-chip 8k byte block can be addressed over the entire 64k external data memory address range (overlapping 8k boundaries). External data memory address space can be mapped to on-chip memory only, off-chip memory only, or a combination of the two (addresses up to 8k directed to on-chip, above 8k directed to EMIF). The EMIF is also configurable for multiplexed or non-multiplexed address/data lines.

On the C8051F12x and C8051F130/1, the MCU's program memory consists of 128 k bytes of banked Flash memory. The 1024 bytes from addresses 0x1FC00 to 0x1FFFF are reserved. On the C8051F132/3, the MCU's program memory consists of 64 k bytes of Flash memory. This memory may be reprogrammed in-system in 1024 byte sectors, and requires no special off-chip programming voltage.

On all devices, there are also two 128 byte sectors at addresses 0x20000 to 0x200FF, which may be used by software for data storage. See Figure 1.8 for the MCU system memory map.

Figure 1.8. On-Chip Memory Map

| (ADC0H[7:0]:ADC0L[<br>(ADC0L[3:0]                                                                                     | [7:4], if AD0LJST = 1<br>  = 0000b).                                                                                |                                                                                                    |                        |

|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------|

| •                                                                                                                     | a Word Conversion Ma<br>0x00, AMX0SL = 0x00                                                                         | • •                                                                                                | ingle-Ended Mode       |

| AIN0.0–AGND<br>(Volts)                                                                                                | ADC0H:ADC0L<br>(AD0LJST = 0)                                                                                        | ADC0H:ADC0L<br>(AD0LJST = 1)                                                                       | ]                      |

| VREF x (4095/4096)                                                                                                    | 0x0FFF                                                                                                              | 0xFFF0                                                                                             |                        |

| VREF / 2                                                                                                              | 0x0800                                                                                                              | 0x8000                                                                                             |                        |

| VREF x (2047/4096)                                                                                                    | 0x07FF                                                                                                              | 0x7FF0                                                                                             |                        |

|                                                                                                                       |                                                                                                                     |                                                                                                    |                        |

| 0<br>Example: ADC0 Data                                                                                               | 0x0000<br>a Word Conversion Ma                                                                                      | 0x0000<br>ap, AIN0.0-AIN0.1 Di                                                                     | fferential Input Pair  |

| Example: ADC0 Data                                                                                                    | 0x0000<br>a Word Conversion Ma<br>0x01, AMX0SL = 0x00<br>ADC0H:ADC0L<br>(AD0LJST = 0)                               | ap, AIN0.0-AIN0.1 Di                                                                               | ifferential Input Pair |

| Example: ADC0 Data<br>(AMX0CF =<br>AIN0.0–AIN0.1<br>(Volts)                                                           | a Word Conversion Ma<br>0x01, AMX0SL = 0x00<br><b>ADC0H:ADC0L</b>                                                   | ap, AIN0.0-AIN0.1 Di<br>D)<br>ADC0H:ADC0L                                                          | ifferential Input Pair |

| Example: ADC0 Data<br>(AMX0CF =<br>AIN0.0–AIN0.1<br>(Volts)                                                           | a Word Conversion Ma<br>0x01, AMX0SL = 0x00<br><b>ADC0H:ADC0L</b><br>(AD0LJST = 0)                                  | ap, AIN0.0-AIN0.1 Di<br>0)<br><b>ADC0H:ADC0L</b><br>(AD0LJST = 1)                                  | ifferential Input Pair |

| Example: ADC0 Data<br>(AMX0CF =<br>AIN0.0–AIN0.1<br>(Volts)<br>VREF x (2047/2048)                                     | a Word Conversion Ma<br>0x01, AMX0SL = 0x00<br><b>ADC0H:ADC0L</b><br>(AD0LJST = 0)<br>0x07FF                        | ap, AIN0.0-AIN0.1 Di<br>D)<br>ADC0H:ADC0L<br>(AD0LJST = 1)<br>0x7FF0                               | ifferential Input Pair |

| Example: ADC0 Data<br>(AMX0CF =<br>AIN0.0–AIN0.1<br>(Volts)<br>VREF x (2047/2048)<br>VREF / 2                         | a Word Conversion Ma<br>0x01, AMX0SL = 0x00<br>ADC0H:ADC0L<br>(AD0LJST = 0)<br>0x07FF<br>0x0400                     | ap, AIN0.0-AIN0.1 Di<br>0)<br>ADC0H:ADC0L<br>(AD0LJST = 1)<br>0x7FF0<br>0x4000                     | ifferential Input Pair |

| Example: ADC0 Data<br>(AMX0CF =<br>AIN0.0–AIN0.1<br>(Volts)<br>VREF x (2047/2048)<br>VREF / 2<br>VREF x (1/2048)      | a Word Conversion Ma<br>0x01, AMX0SL = 0x00<br><b>ADC0H:ADC0L</b><br>(AD0LJST = 0)<br>0x07FF<br>0x0400<br>0x0001    | ap, AIN0.0-AIN0.1 Di<br>D)<br>ADC0H:ADC0L<br>(AD0LJST = 1)<br>0x7FF0<br>0x4000<br>0x0010           | ifferential Input Pair |

| Example: ADC0 Data<br>(AMX0CF =<br>AIN0.0–AIN0.1<br>(Volts)<br>VREF x (2047/2048)<br>VREF / 2<br>VREF x (1/2048)<br>0 | a Word Conversion Ma<br>0x01, AMX0SL = 0x00<br>ADC0H:ADC0L<br>(AD0LJST = 0)<br>0x07FF<br>0x0400<br>0x0001<br>0x0000 | ap, AIN0.0-AIN0.1 Di<br>D)<br>ADC0H:ADC0L<br>(AD0LJST = 1)<br>0x7FF0<br>0x4000<br>0x0010<br>0x0000 | ifferential Input Pair |

#### Figure 5.5. ADC0 Data Word Example

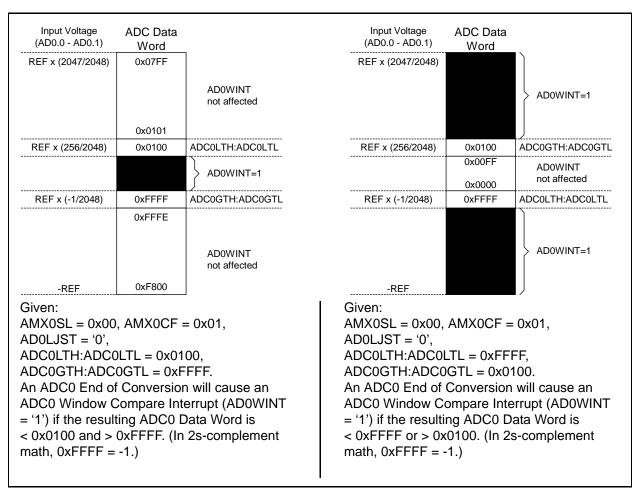

Figure 5.7. 12-Bit ADC0 Window Interrupt Example: Right Justified Differential Data

Figure 5.9. 12-Bit ADC0 Window Interrupt Example: Left Justified Differential Data

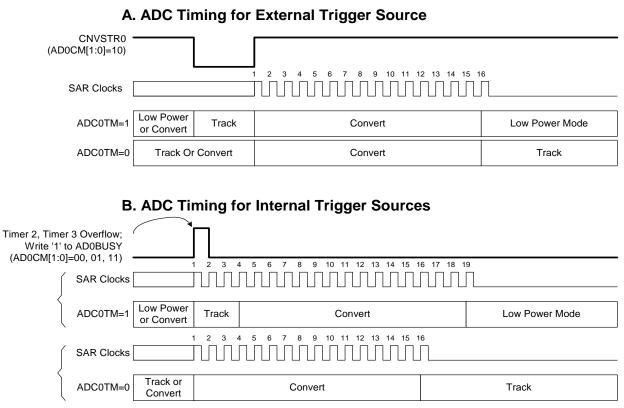

#### 6.2.2. Tracking Modes

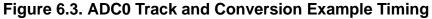

The AD0TM bit in register ADC0CN controls the ADC0 track-and-hold mode. In its default state, the ADC0 input is continuously tracked when a conversion is not in progress. When the AD0TM bit is logic 1, ADC0 operates in low-power track-and-hold mode. In this mode, each conversion is preceded by a tracking period of 3 SAR clocks (after the start-of-conversion signal). When the CNVSTR0 signal is used to initiate conversions in low-power tracking mode, ADC0 tracks only when CNVSTR0 is low; conversion begins on the rising edge of CNVSTR0 (see Figure 6.3). Tracking can also be disabled (shutdown) when the entire chip is in low power standby or sleep modes. Low-power track-and-hold mode is also useful when AMUX or PGA settings are frequently changed, to ensure that settling time requirements are met (see **Section "6.2.3. Settling Time Requirements" on page 77**).

| 000000b).                                                                                                               |                                                                                                                               |                                                                                                               |  |

|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                         |                                                                                                                               |                                                                                                               |  |

| ADC0H[7:0]:ADC0L[<br>(ADC0L[5:0]                                                                                        | [7:6], if AD0LJST = 1<br>  = 00b).                                                                                            |                                                                                                               |  |

|                                                                                                                         | a Word Conversion Ma<br>0x00, AMX0SL = 0x00                                                                                   |                                                                                                               |  |

| AIN0.0–AGND<br>(Volts)                                                                                                  | ADC0H:ADC0L<br>(AD0LJST = 0)                                                                                                  | ADC0H:ADC0L<br>(AD0LJST = 1)                                                                                  |  |

| /REF x (1023/1024)                                                                                                      | 0x03FF                                                                                                                        | 0xFFC0                                                                                                        |  |

| VREF / 2                                                                                                                | 0x0200                                                                                                                        | 0x8000                                                                                                        |  |

|                                                                                                                         | 0x01FF                                                                                                                        | 0x7FC0                                                                                                        |  |

| VREF x (511/1024)                                                                                                       | UXUIFF                                                                                                                        | 0x7FC0                                                                                                        |  |

| 0                                                                                                                       | 0x0000<br>0x0000<br>a Word Conversion Ma                                                                                      | 0x0000                                                                                                        |  |

| 0<br>Example: ADC0 Data<br>(AMX0CF =<br>AIN0.0–AIN0.1<br>(Volts)                                                        | 0x0000<br>a Word Conversion Ma<br>0x01, AMX0SL = 0x00<br>ADC0H:ADC0L<br>(AD0LJST = 0)                                         | 0x0000<br>ap, AIN0.0-AIN0.1 Di<br>0)<br>ADC0H:ADC0L<br>(AD0LJST = 1)                                          |  |

| 0<br>Example: ADC0 Data<br>(AMX0CF =<br>AIN0.0–AIN0.1<br>(Volts)<br>VREF x (511/512)                                    | 0x0000<br>a Word Conversion Ma<br>0x01, AMX0SL = 0x00<br>ADC0H:ADC0L<br>(AD0LJST = 0)<br>0x01FF                               | 0x0000<br>ap, AIN0.0-AIN0.1 Dir<br>0)<br>ADC0H:ADC0L<br>(AD0LJST = 1)<br>0x7FC0                               |  |

| 0<br>Example: ADC0 Dat<br>(AMX0CF =<br>AIN0.0–AIN0.1<br>(Volts)<br>VREF x (511/512)<br>VREF / 2                         | 0x0000<br>a Word Conversion Ma<br>0x01, AMX0SL = 0x00<br>ADC0H:ADC0L<br>(AD0LJST = 0)                                         | 0x0000<br>ap, AIN0.0-AIN0.1 Di<br>0)<br>ADC0H:ADC0L<br>(AD0LJST = 1)                                          |  |

| 0<br>Example: ADC0 Data<br>(AMX0CF =<br>AIN0.0–AIN0.1<br>(Volts)<br>VREF x (511/512)                                    | 0x0000<br>a Word Conversion Ma<br>0x01, AMX0SL = 0x00<br>ADC0H:ADC0L<br>(AD0LJST = 0)<br>0x01FF                               | 0x0000<br>ap, AIN0.0-AIN0.1 Dir<br>0)<br>ADC0H:ADC0L<br>(AD0LJST = 1)<br>0x7FC0                               |  |

| 0<br>Example: ADC0 Dat<br>(AMX0CF =<br>AIN0.0–AIN0.1<br>(Volts)<br>VREF x (511/512)<br>VREF / 2                         | 0x0000<br>a Word Conversion Ma<br>0x01, AMX0SL = 0x00<br>ADC0H:ADC0L<br>(AD0LJST = 0)<br>0x01FF<br>0x0100                     | 0x0000<br>ap, AIN0.0-AIN0.1 Di<br>0)<br>ADC0H:ADC0L<br>(AD0LJST = 1)<br>0x7FC0<br>0x4000                      |  |

| 0<br>Example: ADC0 Data<br>(AMX0CF =<br>AIN0.0–AIN0.1<br>(Volts)<br>VREF x (511/512)<br>VREF / 2<br>VREF x (1/512)      | 0x0000<br>a Word Conversion Ma<br>0x01, AMX0SL = 0x00<br>ADC0H:ADC0L<br>(AD0LJST = 0)<br>0x01FF<br>0x0100<br>0x0001           | 0x0000<br>ap, AIN0.0-AIN0.1 Dir<br>0)<br>ADC0H:ADC0L<br>(AD0LJST = 1)<br>0x7FC0<br>0x4000<br>0x0040           |  |

| 0<br>Example: ADC0 Data<br>(AMX0CF =<br>AIN0.0–AIN0.1<br>(Volts)<br>VREF x (511/512)<br>VREF / 2<br>VREF x (1/512)<br>0 | 0x0000<br>a Word Conversion Ma<br>0x01, AMX0SL = 0x00<br>ADC0H:ADC0L<br>(AD0LJST = 0)<br>0x01FF<br>0x0100<br>0x0001<br>0x0000 | 0x0000<br>ap, AIN0.0-AIN0.1 Dir<br>0)<br>ADC0H:ADC0L<br>(AD0LJST = 1)<br>0x7FC0<br>0x4000<br>0x0040<br>0x0000 |  |

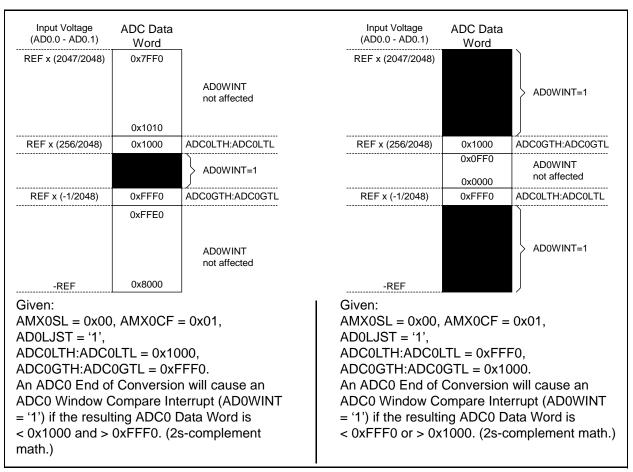

### Figure 6.5. ADC0 Data Word Example

| R/W      | R/W                                                                                                  | R/W         | R/W          | R/W            | R/W           | R/W      | R/W  | Reset Value |  |  |

|----------|------------------------------------------------------------------------------------------------------|-------------|--------------|----------------|---------------|----------|------|-------------|--|--|

| -        | PIN67IC PIN45IC PIN23                                                                                |             | PIN23IC      | PIN01IC        | 00000000      |          |      |             |  |  |

| Bit7     | Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1                                                                   |             |              |                |               | Bit1     | Bit0 | -           |  |  |

| Bits7–4: | Bits7–4: UNUSED. Read = 0000b; Write = don't care.                                                   |             |              |                |               |          |      |             |  |  |

| Bit3:    | PIN67IC: AIN                                                                                         |             |              |                | on Bit        |          |      |             |  |  |

| Dito.    | 0: AIN2.6 and                                                                                        |             |              | •              |               |          |      |             |  |  |

|          | 1: AIN2.6 and                                                                                        |             |              | •              |               |          |      |             |  |  |

| Bit2:    | PIN45IC: AIN                                                                                         |             | · ·          | • • •          |               |          |      |             |  |  |

|          | 0: AIN2.4 and                                                                                        |             |              | •              |               |          |      |             |  |  |

|          | 1: AIN2.4 and                                                                                        |             |              | •              |               |          |      |             |  |  |

| Bit1:    | PIN23IC: AIN                                                                                         |             |              |                |               | •        |      |             |  |  |

|          | 0: AIN2.2 and                                                                                        |             |              |                |               |          |      |             |  |  |

|          | 1: AIN2.2 and                                                                                        | d AIN2.3 ar | e (respectiv | ely) +, – dif  | ferential inp | ut pair. |      |             |  |  |

| Bit0:    | PIN01IC: AIN                                                                                         | 2.0, AIN2.1 | I Input Pair | Configuratio   | on Bit.       |          |      |             |  |  |

|          | 0: AIN2.0 and                                                                                        | d AIN2.1 ar | e independe  | ent single-e   | nded inputs   |          |      |             |  |  |

|          | 1: AIN2.0 and                                                                                        | d AIN2.1 ar | e (respectiv | rely) +, – dif | ferential inp | ut pair. |      |             |  |  |

|          |                                                                                                      |             |              |                |               |          |      |             |  |  |

| NI. 4    | <b>Note:</b> The ADC2 Data Word is in 2's complement format for channels configured as differential. |             |              |                |               |          |      |             |  |  |

#### SFR Definition 7.1. AMX2CF: AMUX2 Configuration

### 9. Voltage Reference

The voltage reference options available on the C8051F12x and C8051F13x device families vary according to the device capabilities.

All devices include an internal voltage reference circuit, consisting of a 1.2 V, 15 ppm/°C (typical) bandgap voltage reference generator and a gain-of-two output buffer amplifier. The internal reference may be routed via the VREF pin to external system components or to the voltage reference input pins. The maximum load seen by the VREF pin must be less than 200  $\mu$ A to AGND. Bypass capacitors of 0.1  $\mu$ F and 4.7  $\mu$ F are recommended from the VREF pin to AGND.

The Reference Control Register, REF0CN enables/disables the internal reference generator and the internal temperature sensor on all devices. The BIASE bit in REF0CN enables the on-board reference generator while the REFBE bit enables the gain-of-two buffer amplifier which drives the VREF pin. When disabled, the supply current drawn by the bandgap and buffer amplifier falls to less than 1  $\mu$ A (typical) and the output of the buffer amplifier enters a high impedance state. If the internal bandgap is used as the reference voltage generator, BIASE and REFBE must both be set to logic 1. If the internal reference is not used, REFBE may be set to logic 0. Note that the BIASE bit must be set to logic 1 if any DACs or ADCs are used, regardless of whether the voltage reference is derived from the on-chip reference or supplied by an off-chip source. If no ADCs or DACs are being used, both of these bits can be set to logic 0 to conserve power.

When enabled, the temperature sensor connects to the highest order input of the ADC0 input multiplexer. The TEMPE bit within REF0CN enables and disables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state. Any ADC measurements performed on the sensor while disabled will result in undefined data.

The electrical specifications for the internal voltage reference are given in Table 9.1.

#### 9.1. Reference Configuration on the C8051F120/2/4/6

On the C8051F120/2/4/6 devices, the REF0CN register also allows selection of the voltage reference source for ADC0 and ADC2, as shown in SFR Definition 9.1. Bits AD0VRS and AD2VRS in the REF0CN register select the ADC0 and ADC2 voltage reference sources, respectively. Three voltage reference input pins allow each ADC and the two DACs to reference an external voltage reference or the on-chip voltage reference output (with an external connection). ADC0 may also reference the DAC0 output internally, and ADC2 may reference the analog power supply voltage, via the VREF multiplexers shown in Figure 9.1.

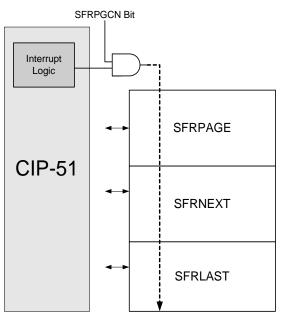

Figure 11.4. SFR Page Stack

Automatic hardware switching of the SFR Page on interrupts may be enabled or disabled as desired using the SFR Automatic Page Control Enable Bit located in the SFR Page Control Register (SFRPGCN). This function defaults to 'enabled' upon reset. In this way, the autoswitching function will be enabled unless disabled in software.

A summary of the SFR locations (address and SFR page) is provided in Table 11.2. in the form of an SFR memory map. Each memory location in the map has an SFR page row, denoting the page in which that SFR resides. Note that certain SFR's are accessible from ALL SFR pages, and are denoted by the "(ALL PAGES)" designation. For example, the Port I/O registers P0, P1, P2, and P3 all have the "(ALL PAGES)" designation, indicating these SFR's are accessible from all SFR pages regardless of the SFRPAGE register value.

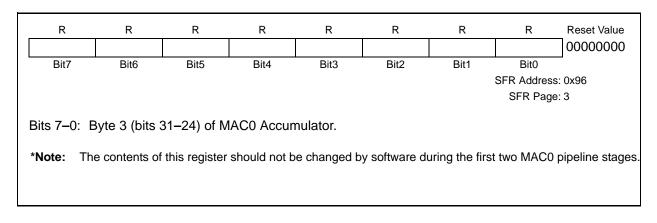

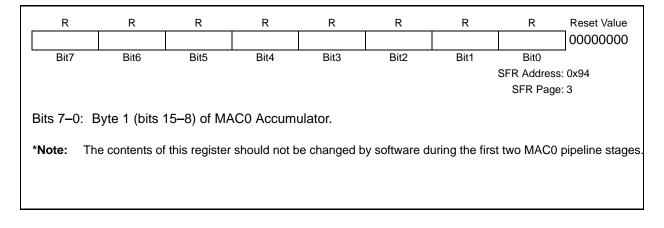

#### SFR Definition 12.7. MAC0ACC3: MAC0 Accumulator Byte 3

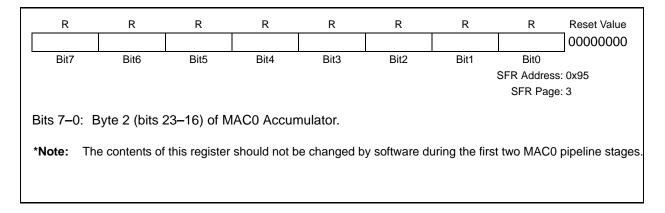

#### SFR Definition 12.8. MAC0ACC2: MAC0 Accumulator Byte 2

#### SFR Definition 12.9. MAC0ACC1: MAC0 Accumulator Byte 1

#### 15.1.3. Writing Flash Memory From Software

Bytes in Flash memory can be written one byte at a time, or in small blocks. The CHBLKW bit in register CCH0CN (SFR Definition 16.1) controls whether a single byte or a block of bytes is written to Flash during a write operation. When CHBLKW is cleared to '0', the Flash will be written one byte at a time. When CHBLKW is set to '1', the Flash will be written in blocks of four bytes for addresses in code space, or blocks of two bytes for addresses in the Scratchpad area. Block writes are performed in the same amount of time as single byte writes, which can save time when storing large amounts of data to Flash memory.

For single-byte writes to Flash, bytes are written individually, and the Flash write is performed after each MOVX write instruction. The recommended procedure for writing Flash in single bytes is as follows:

- Step 1. Disable interrupts.

- Step 2. Clear CHBLKW (CCH0CN.0) to select single-byte write mode.

- Step 3. If writing to bytes in Bank 1, Bank 2, or Bank 3, set the COBANK bits (PSBANK.5-4) for the appropriate bank.

- Step 4. If writing to bytes in the Scratchpad area, set the SFLE bit (PSCTL.2).

- Step 5. Set FLWE (FLSCL.0) to enable Flash writes/erases via user software.

- Step 6. Set PSWE (PSCTL.0) to redirect MOVX commands to write to Flash.

- Step 7. Use the MOVX instruction to write a data byte to the desired location (repeat as necessary).

- Step 8. Clear the PSWE bit to redirect MOVX commands to the XRAM data space.

- Step 9. Clear the FLWE bit, to disable Flash writes/erases.

- Step 10. If writing to bytes in the Scratchpad area, clear the SFLE bit.

- Step 11. Re-enable interrupts.

For block Flash writes, the Flash write procedure is only performed after the last byte of each block is written with the MOVX write instruction. When writing to addresses located in any of the four code banks, a Flash write block is four bytes long, from addresses ending in 00b to addresses ending in 11b. Writes must be performed sequentially (i.e. addresses ending in 00b, 01b, 10b, and 11b must be written in order). The Flash write will be performed following the MOVX write that targets the address ending in 11b. When writing to addresses located in the Flash Scratchpad area, a Flash block is two bytes long, from addresses ending in 0b to addresses ending in 1b. The Flash write will be performed following the MOVX write that targets the address ending in 1b. If any bytes in the block do not need to be updated in Flash, they should be written to 0xFF. The recommended procedure for writing Flash in blocks is as follows:

- Step 1. Disable interrupts.

- Step 2. Set CHBLKW (CCH0CN.0) to select block write mode.

- Step 3. If writing to bytes in Bank 1, Bank 2, or Bank 3, set the COBANK bits (PSBANK.5-4) for the appropriate bank.

- Step 4. If writing to bytes in the Scratchpad area, set the SFLE bit (PSCTL.2).

- Step 5. Set FLWE (FLSCL.0) to enable Flash writes/erases via user software.

- Step 6. Set PSWE (PSCTL.0) to redirect MOVX commands to write to Flash.

- Step 7. Use the MOVX instruction to write data bytes to the desired block. The data bytes must be written sequentially, and the last byte written must be the high byte of the block (see text for details, repeat as necessary).

- Step 8. Clear the PSWE bit to redirect MOVX commands to the XRAM data space.

- Step 9. Clear the FLWE bit, to disable Flash writes/erases.

- Step 10. If writing to bytes in the Scratchpad area, clear the SFLE bit.

- Step 11. Re-enable interrupts.

| R         | R/W                                | R/W           | R/W          | R/W           | R/W          | R/W          | R/W                     | Reset Value     |

|-----------|------------------------------------|---------------|--------------|---------------|--------------|--------------|-------------------------|-----------------|

| CHMSC     | V                                  |               |              | CHMSCTH       |              |              |                         | 0000000         |

| Bit7      | Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 |               |              |               |              |              |                         |                 |

|           |                                    |               |              |               |              |              | SFR Address<br>SFR Page |                 |

| Bit 7:    | CHMSOV: C                          | ache Miss     | Penalty Ov   | erflow        |              |              |                         |                 |

|           | This bit indic                     |               |              |               | v Accumula   | tor has ove  | erflowed si             | nce it was      |

|           | last written.                      |               |              |               | ,            |              |                         |                 |

|           | 0: The Cach                        | e Miss Pen    | alty Accum   | ulator has n  | ot overflowe | ed since it  | was last w              | ritten.         |

|           | 1: An overflo                      | w of the Ca   | iche Miss P  | enalty Accu   | mulator has  | s occurred   | since it was            | s last writte   |

| Bits 6–0: | CHMSCTH:                           | Cache Mis     | s Penalty A  | ccumulator    | (bits 11–5)  |              |                         |                 |

|           | These are bi                       | ts 11-5 of th | ne Cache M   | iss Penalty   | Accumulato   | or. The nex  | t four bits (           | bits 4-1) ar    |

|           | stored in CH                       |               |              | •             |              |              |                         |                 |

|           | The Cache N                        |               |              |               |              |              |                         |                 |

|           | delayed due code for exe           |               |              | is primarily  | used as a di | iagnostic fe | eature, whe             | n optimizin     |

|           | Writing to CH                      | HMSCTH c      | ears the lov | wer 5 bits of | the Cache    | Miss Pena    | Ity Accum               | ulator.         |

|           | Reading fror                       | n CHMSCT      | H returns t  | he current v  | alue of CHN  | MSTCH. ar    | nd latches l            | hite $A_1$ into |

|           |                                    |               |              |               |              | ,            |                         | JIIS 4- I IIIIC |

|           | CHMSTCL s                          | o that they   | can be rea   | d. Because    |              |              |                         |                 |

#### SFR Definition 16.5. FLSTAT: Flash Status

| R<br>-   | R/W<br>-                                                                       | R/W<br>-                   | R/W<br>- | R/W<br>- | R/W<br>- | R/W<br>- | R/W<br>FLBUSY                   | Reset Value        |

|----------|--------------------------------------------------------------------------------|----------------------------|----------|----------|----------|----------|---------------------------------|--------------------|

| Bit7     | Bit6                                                                           | Bit5                       | Bit4     | Bit3     | Bit2     | Bit1     | Bit0                            | Bit<br>Addressable |

| Bit 0: I | Reserved.<br>FLBUSY: Fla<br>This bit indic<br>D: Flash is id<br>1: Flash write | ates when<br>lle or readir | ıg.      |          |          |          | SFR Address:<br>SFR Page:<br>S. |                    |

|         |       |   |   | p | 0 |           | P1          |       | P2  |       |     | P3    |       | Crossbar Registe |

|---------|-------|---|---|---|---|-----------|-------------|-------|-----|-------|-----|-------|-------|------------------|

| PIN I/O | 0     | 1 | 2 | 3 | 4 | 5 6 7 0 1 | 2 3 4 5 6 7 | 0 1 2 | 3 4 | 5 6 7 | 0 1 | 2 3 4 | 5 6 7 | Crossbar registe |

| X0      | ۲     |   |   |   |   |           |             |       |     |       |     |       |       |                  |

| exo 🛛   |       | ۲ |   |   |   |           |             |       |     |       |     |       |       |                  |

| ск      | ۲     |   | ۲ |   |   |           |             |       |     |       |     |       |       |                  |

| niso 🛛  |       |   |   | ۲ |   |           |             |       |     |       |     |       |       |                  |

| nosi 🛛  |       |   |   |   | • |           |             |       |     |       |     |       |       |                  |

| iss     |       |   |   |   |   |           |             |       |     |       |     |       |       |                  |

| DA      | ۲     |   | ۲ | ۲ | 0 |           |             |       |     |       |     |       |       |                  |

| ICL     |       | ۲ |   | ۲ | • |           |             |       |     |       |     |       |       |                  |

| TX1     | ۲     |   | ۲ | ۲ | ۲ |           |             |       |     |       |     |       |       |                  |

| X1      |       | ۲ |   | ۲ | • |           |             |       |     |       |     |       |       |                  |

| CEXO    | ۲     |   | ۲ | ۲ | ۲ |           |             |       |     |       |     |       |       |                  |

| CEX1    |       | ۲ |   | ۲ | • |           |             |       |     |       |     |       |       |                  |

| CEX2    |       |   |   |   |   |           |             |       |     |       |     |       |       |                  |

| EX3     |       |   |   | ۲ |   |           |             |       |     |       |     |       |       |                  |

| EX4     |       |   |   |   | • |           |             |       |     |       |     |       |       |                  |

| EX5     |       |   |   |   |   |           |             |       |     |       |     |       |       |                  |

| CI      | ۲     | ۲ | ۲ | ۲ |   |           |             |       |     |       |     |       |       |                  |

| CP0     | ۲     | ۲ | ۲ | ۲ | 0 |           |             |       |     |       |     |       |       |                  |

| CP1     | ۲     | ۲ | ۲ | ۲ |   |           |             |       |     |       |     |       |       |                  |

| 0       | ۲     | ۲ | ۲ | ۲ | ۲ |           |             |       |     |       |     |       |       |                  |

| NTO     | ۲     | ۲ | ۲ | ۲ | ۲ |           |             |       |     |       |     |       |       |                  |

| 1       | ۲     | ۲ | ۲ | ۲ | ۲ |           |             |       |     |       |     |       |       |                  |

| INT1    | ۲     | ۲ | ۲ | ۲ | 0 |           |             |       |     |       |     |       |       |                  |

| 2       | ۲     | ۲ | ۲ | ۲ |   |           |             |       |     |       |     |       |       |                  |

| 2EX     | ۲     | ۲ | ۲ | ۲ |   |           |             |       |     |       |     |       |       |                  |

| 4       | ۲     | ۲ | ۲ | ۲ | ۲ |           |             |       |     |       |     |       |       |                  |

| '4EX    | ۲     | ۲ | ۲ | ۲ |   | 6.6       |             |       |     |       |     |       |       |                  |

| SYSCLK  | ۲     | ۲ | ۲ | ۲ | 0 |           |             |       |     |       |     |       |       |                  |

| humanna | ette. |   | ۲ | ۲ | 0 |           |             |       |     |       |     |       |       |                  |

| NVSTRO  | an    |   |   |   |   |           |             |       |     |       |     |       |       |                  |

(EMIFLE = 1; EMIF in Multiplexed Mode; P1MDIN = 0xE3; XBR0 = 0x05; XBR1 = 0x14; XBR2 = 0x42)

Figure 18.6. Crossbar Example

#### Figure 21.6. UART0 Modes 1, 2, and 3 Interconnect Diagram

#### 21.1.4. Mode 3: 9-Bit UART, Variable Baud Rate

Mode 3 uses the Mode 2 transmission protocol with the Mode 1 baud rate generation. Mode 3 operation transmits 11 bits: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. The baud rate is derived from Timer 1 or Timer 2, 3, or 4 overflows, as defined by Equation 21.1 and Equation 21.3. Multiprocessor communications and hardware address recognition are supported, as described in **Section 21.2**.

#### 23.2.4. Toggle Output Mode (Timer 2 and Timer 4 Only)

Timers 2 and 4 have the capability to toggle the state of their respective output port pins (T2 or T4) to produce a 50% duty cycle waveform output. The port pin state will change upon the overflow or underflow of the respective timer (depending on whether the timer is counting *up* or *down*). The toggle frequency is determined by the clock source of the timer and the values loaded into RCAPnH and RCAPnL. When counting DOWN, the auto-reload value for the timer is 0xFFFF, and underflow will occur when the value in the timer matches the value stored in RCAPnH:RCAPnL. When counting UP, the auto-reload value for the timer is RCAPnH:RCAPnL, and overflow will occur when the value in the timer transitions from 0xFFFF to the reload value.

To output a square wave, the timer is placed in reload mode (the Capture/Reload Select Bit in TMRnCN and the Timer/Counter Select Bit in TMRnCN are cleared to '0'). The timer output is enabled by setting the Timer Output Enable Bit in TMRnCF to '1'. The timer should be configured via the timer clock source and reload/underflow values such that the timer overflow/underflows at 1/2 the desired output frequency. The port pin assigned by the crossbar as the timer's output pin should be configured as a digital output (see **Section "18. Port Input/Output" on page 235**). Setting the timer's Run Bit (TRn) to '1' will start the toggle of the pin. A Read/Write of the Timer's Toggle Output State Bit (TMRnCF.2) is used to read the state of the toggle output, or to force a value of the output. This is useful when it is desired to start the toggle of a pin in a known state, or to force the pin into a desired state when the toggle mode is halted.

#### Equation 23.1. Square Wave Frequency (Timer 2 and Timer 4 Only)

$$F_{sq} = \frac{F_{TCLK}}{2 \times (65536 - RCAPn)}$$

Rev. 1.4

#### SFR Definition 24.3. PCA0CPMn: PCA0 Capture/Compare Mode

| R/W     | R/W                                                                                                         | R/W                    | R/W          | R/W             | R/W           | R/W           | R/W           | Reset Value |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------|------------------------|--------------|-----------------|---------------|---------------|---------------|-------------|--|--|--|

| PWM16   | n ECOMn                                                                                                     | CAPPn                  | CAPNn        | MATn            | TOGn          | PWMn          | ECCFn         | 00000000    |  |  |  |

| Bit7    | Bit6                                                                                                        | Bit5                   | Bit4         | Bit3            | Bit2          | Bit1          | Bit0          | -           |  |  |  |

|         | SFR PCA0CPM0: 0xDA, PCA0CPM1: 0xDB, PCA0CPM2: 0xDC, PCA0CPM3: 0xDD, PCA0CPM4: 0xDE, Address: PCA0CPM5: 0xDF |                        |              |                 |               |               |               |             |  |  |  |

|         |                                                                                                             |                        |              |                 |               |               |               | <b>~</b> 0  |  |  |  |

| SFR Pag | PCAUCPMU:                                                                                                   | page 0, PCAU<br>page 0 | CPMT: page 0 | , PCA0CPM2:     | page 0, PCA   | JCPM3: 0, PC/ | AUCPINI4: pag | e 0,        |  |  |  |

|         |                                                                                                             |                        |              |                 |               |               |               |             |  |  |  |

| Bit7:   | PWM16n: 16                                                                                                  |                        |              |                 | -             |               |               |             |  |  |  |

|         | This bit sele                                                                                               |                        | ode when I   | Pulse Width     | Modulatior    | n mode is er  | nabled (PW    | /Mn = 1).   |  |  |  |

|         | 0: 8-bit PWN                                                                                                |                        |              |                 |               |               |               |             |  |  |  |

| Bit6:   | 1: 16-bit PW<br>ECOMn: Co                                                                                   |                        |              | blo             |               |               |               |             |  |  |  |

| DILO.   | This bit enab                                                                                               | •                      |              |                 | on for PCA    | 0 module n    |               |             |  |  |  |

|         | 0: Disabled.                                                                                                |                        | s the comp   |                 |               |               | •             |             |  |  |  |

|         | 1: Enabled.                                                                                                 |                        |              |                 |               |               |               |             |  |  |  |

| Bit5:   | CAPPn: Cap                                                                                                  | oture Positiv          | e Function   | Enable.         |               |               |               |             |  |  |  |

|         | This bit enat                                                                                               |                        |              |                 | ture for PC   | A0 module     | n.            |             |  |  |  |

|         | 0: Disabled.                                                                                                |                        |              |                 |               |               |               |             |  |  |  |

|         | 1: Enabled.                                                                                                 |                        |              |                 |               |               |               |             |  |  |  |

| Bit4:   | CAPNn: Cap                                                                                                  | -                      |              |                 |               |               |               |             |  |  |  |

|         | This bit enab                                                                                               | oles/disable           | s the negat  | ive edge ca     | pture for P   | CA0 module    | en.           |             |  |  |  |

|         | 0: Disabled.                                                                                                |                        |              |                 |               |               |               |             |  |  |  |

| Bit3:   | 1: Enabled.<br>MATn: Matcl                                                                                  | h Eurotion             | Enabla       |                 |               |               |               |             |  |  |  |

| DILJ.   | This bit enab                                                                                               |                        |              | function fo     |               | dule n Whe    | n enabled     | matches of  |  |  |  |

|         | the PCA0 co                                                                                                 |                        |              |                 |               |               |               |             |  |  |  |

|         | register to be                                                                                              |                        |              |                 | pareregier    |               |               |             |  |  |  |

|         | 0: Disabled.                                                                                                | 0                      |              |                 |               |               |               |             |  |  |  |

|         | 1: Enabled.                                                                                                 |                        |              |                 |               |               |               |             |  |  |  |

| Bit2:   | TOGn: Togg                                                                                                  |                        |              |                 |               |               |               |             |  |  |  |

|         | This bit enab                                                                                               |                        |              |                 |               |               |               |             |  |  |  |

|         | the PCA0 co                                                                                                 |                        |              | •               |               |               | •             |             |  |  |  |

|         | CEXn pin to                                                                                                 |                        | e Pvvivin bi | t is also set   | to logic 1, t | ne module     | operates in   | Frequency   |  |  |  |

|         | Output Mode<br>0: Disabled.                                                                                 | 5.                     |              |                 |               |               |               |             |  |  |  |

|         | 1: Enabled.                                                                                                 |                        |              |                 |               |               |               |             |  |  |  |

| Bit1:   | PWMn: Puls                                                                                                  | e Width Mo             | dulation Mo  | ode Enable.     |               |               |               |             |  |  |  |

|         | This bit enab                                                                                               |                        |              |                 | PCA0 mod      | dule n. Whe   | n enabled,    | a pulse     |  |  |  |

|         | width modula                                                                                                |                        |              |                 |               |               |               |             |  |  |  |

|         | 16-bit mode                                                                                                 | is used if P           | WM16n log    | jic 1. If the T | OGn bit is    | also set, the | e module o    | perates in  |  |  |  |

|         | Frequency C                                                                                                 | Dutput Mode            | e.           |                 |               |               |               |             |  |  |  |

|         | 0: Disabled.                                                                                                |                        |              |                 |               |               |               |             |  |  |  |

| D:40    | 1: Enabled.                                                                                                 |                        | <b>F</b> l   |                 | 1.            |               |               |             |  |  |  |

| Bit0:   | ECCFn: Cap                                                                                                  |                        |              |                 |               | CEn) intorr   | upt           |             |  |  |  |

|         | This bit sets<br>0: Disable C                                                                               |                        |              | prore/Comp      | are riag (C   |               | սբւ.          |             |  |  |  |

|         | 1: Enable a                                                                                                 |                        | •            | interrunt re    | quest when    | n CCFn is s   | et            |             |  |  |  |

|         |                                                                                                             | Captaro, OU            | pais ridg    | ,               | 99000 00101   |               |               |             |  |  |  |

#### 25.2. Flash Programming Commands

The Flash memory can be programmed directly over the JTAG interface using the Flash Control, Flash Data, Flash Address, and Flash Scale registers. These Indirect Data Registers are accessed via the JTAG Instruction Register. Read and write operations on indirect data registers are performed by first setting the appropriate DR address in the IR register. Each read or write is then initiated by writing the appropriate Indirect Operation Code (IndOpCode) to the selected data register. Incoming commands to this register have the following format:

| 19:18     | 17:0      |

|-----------|-----------|

| IndOpCode | WriteData |

IndOpCode: These bit set the operation to perform according to the following table:

| IndOpCode | Operation |

|-----------|-----------|

| 0x        | Poll      |

| 10        | Read      |

| 11        | Write     |

The Poll operation is used to check the Busy bit as described below. Although a Capture-DR is performed, no Update-DR is allowed for the Poll operation. Since updates are disabled, polling can be accomplished by shifting in/out a single bit.

The Read operation initiates a read from the register addressed by the DRAddress. Reads can be initiated by shifting only 2 bits into the indirect register. After the read operation is initiated, polling of the Busy bit must be performed to determine when the operation is complete.

The write operation initiates a write of WriteData to the register addressed by DRAddress. Registers of any width up to 18 bits can be written. If the register to be written contains fewer than 18 bits, the data in Write-Data should be left-justified, i.e. its MSB should occupy bit 17 above. This allows shorter registers to be written in fewer JTAG clock cycles. For example, an 8-bit register could be written by shifting only 10 bits. After a Write is initiated, the Busy bit should be polled to determine when the next operation can be initiated. The contents of the Instruction Register should not be altered while either a read or write operation is busy.

Outgoing data from the indirect Data Register has the following format:

| 19 | 18:1     | 0    |

|----|----------|------|

| 0  | ReadData | Busy |

The Busy bit indicates that the current operation is not complete. It goes high when an operation is initiated and returns low when complete. Read and Write commands are ignored while Busy is high. In fact, if polling for Busy to be low will be followed by another read or write operation, JTAG writes of the next operation can be made while checking for Busy to be low. They will be ignored until Busy is read low, at which time the new operation will initiate. This bit is placed ate bit 0 to allow polling by single-bit shifts. When waiting for a Read to complete and Busy is 0, the following 18 bits can be shifted out to obtain the resulting data. ReadData is always right-justified. This allows registers shorter than 18 bits to be read using a reduced number of shifts. For example, the results from a byte-read requires 9 bit shifts (Busy + 8 bits).

### DOCUMENT CHANGE LIST

#### Revision 1.3 to Revision 1.4

- Added new paragraph tags: SFR Definition and JTAG Register Definition.

- Product Selection Guide Table 1.1: Added RoHS-compliant ordering information.

- Overview Chapter, Figure 1.8, "On-Chip Memory Map": Corrected on-chip XRAM size to "8192 Bytes".

- SAR8 Chapter: Table 7.1, "ADC2 Electrical Characteristics": Track/Hold minimum spec corrected to "300 ns".

- SAR8 Chapter: Table 7.1, "ADC2 Electrical Characteristics": Total Harmonic Distortion typical spec corrected to "-51 dB".

- Oscillators Chapter, Figure 14.1, "Oscillator Diagram": Corrected location of IOSCEN arrow.

- CIP51 Chapter, **Section 11.3**: Added note describing EA change behavior when followed by singlecycle instruction.

- CIP51 Chapter, Interrupt Summary Table: Added "SFRPAGE" column and SFRPAGE value for each interrupt source.

- CIP-51 Chapter, Figure 11.2, "Memory Map": Corrected on-chip XRAM size to "8192 Bytes".

- Port I/O Chapter, Crossbar Priority Figures: Character formatting problem corrected.

- Port I/O Chapter, P7MDOUT Register Description: Removed references to UART and SMBus peripherals.

- Port I/O Chapter, P3MDOUT Register Description: Corrected text to read "P3MDOUT.[7:0]".

- Timers Chapter: References to "TnCON" corrected to read "TMRnCN".

- PCA0 Chapter, Section 24.1: Added note about PCA0CN Register and effects of read-modify-write instructions on the CF bit.