Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                 |

|----------------------------|-----------------------------------------------------------------|

| Product Status             | Not For New Designs                                             |

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 100MHz                                                          |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 64                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 8.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                       |

| Data Converters            | A/D 8x10b                                                       |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 100-TQFP                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f132-gqr |

| SFR Definition 16.5. FLSTAT: Flash Status                      | 217 |

|----------------------------------------------------------------|-----|

| SFR Definition 17.1. EMIOCN: External Memory Interface Control | 220 |

| SFR Definition 17.2. EMIOCF: External Memory Configuration     |     |

| SFR Definition 17.3. EMIOTC: External Memory Timing Control    |     |

| SFR Definition 18.1. XBR0: Port I/O Crossbar Register 0        | 245 |

| SFR Definition 18.2. XBR1: Port I/O Crossbar Register 1        |     |

| SFR Definition 18.3. XBR2: Port I/O Crossbar Register 2        | 247 |

| SFR Definition 18.4. P0: Port0 Data                            |     |

| SFR Definition 18.5. P0MDOUT: Port0 Output Mode                |     |

| SFR Definition 18.6. P1: Port1 Data                            |     |

| SFR Definition 18.7. P1MDIN: Port1 Input Mode                  |     |

| SFR Definition 18.8. P1MDOUT: Port1 Output Mode                |     |

| SFR Definition 18.9. P2: Port2 Data                            |     |

| SFR Definition 18.10. P2MDOUT: Port2 Output Mode               |     |

| SFR Definition 18.11. P3: Port3 Data                           |     |

| SFR Definition 18.12. P3MDOUT: Port3 Output Mode               |     |

| SFR Definition 18.13. P4: Port4 Data                           |     |

| SFR Definition 18.14. P4MDOUT: Port4 Output Mode               |     |

| SFR Definition 18.15. P5: Port5 Data                           | 255 |

| SFR Definition 18.16. P5MDOUT: Port5 Output Mode               | 255 |

| SFR Definition 18.17. P6: Port6 Data                           |     |

| SFR Definition 18.18. P6MDOUT: Port6 Output Mode               |     |

| SFR Definition 18.19. P7: Port7 Data                           |     |

| SFR Definition 18.20. P7MDOUT: Port7 Output Mode               |     |

| SFR Definition 19.1. SMB0CN: SMBus0 Control                    |     |

| SFR Definition 19.2. SMB0CR: SMBus0 Clock Rate                 |     |

| SFR Definition 19.3. SMB0DAT: SMBus0 Data                      |     |

| SFR Definition 19.4. SMB0ADR: SMBus0 Address                   |     |

| SFR Definition 19.5. SMB0STA: SMBus0 Status                    |     |

| SFR Definition 20.1. SPI0CFG: SPI0 Configuration               |     |

| SFR Definition 20.2. SPI0CN: SPI0 Control                      |     |

| SFR Definition 20.3. SPI0CKR: SPI0 Clock Rate                  | 202 |

| SFR Definition 20.4. SPI0DAT: SPI0 Data                        |     |

| SFR Definition 21.1. SCON0: UART0 Control                      |     |

| SFR Definition 21.2. SSTA0: UART0 Status and Clock Selection   |     |

| SFR Definition 21.3. SBUF0: UART0 Data Buffer                  |     |

| SFR Definition 21.4. SADDR0: UART0 Slave Address               |     |

| SFR Definition 21.5. SADEN0: UARTO Slave Address Enable        |     |

| SFR Definition 22.1. SCON1: Serial Port 1 Control              |     |

| SFR Definition 22.2. SBUF1: Serial (UART1) Port Data Buffer    | 305 |

| SFR Definition 23.1. TCON: Timer Control                       |     |

| SFR Definition 23.2. TMOD: Timer Mode                          |     |

| SFR Definition 23.3. CKCON: Clock Control                      |     |

| SFR Definition 23.4. TL0: Timer 0 Low Byte                     |     |

| SFR Definition 23.5. TL1: Timer 1 Low Byte                     | 316 |

#### 1.5. Programmable Digital I/O and Crossbar

The standard 8051 8-bit Ports (0, 1, 2, and 3) are available on the MCUs. The devices in the larger (100pin TQFP) packaging have 4 additional ports (4, 5, 6, and 7) for a total of 64 general-purpose port I/O. The Port I/O behave like the standard 8051 with a few enhancements.

Each Port I/O pin can be configured as either a push-pull or open-drain output. Also, the "weak pullups" which are normally fixed on an 8051 can be globally disabled, providing additional power saving capabilities for low-power applications.

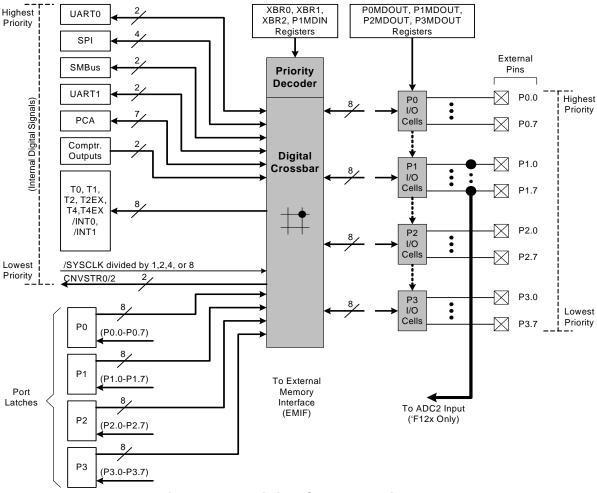

Perhaps the most unique enhancement is the Digital Crossbar. This is a large digital switching network that allows mapping of internal digital system resources to Port I/O pins on P0, P1, P2, and P3. (See Figure 1.11) Unlike microcontrollers with standard multiplexed digital I/O, all combinations of functions are supported.

The on-chip counter/timers, serial buses, HW interrupts, ADC Start of Conversion inputs, comparator outputs, and other digital signals in the controller can be configured to appear on the Port I/O pins specified in the Crossbar Control registers. This allows the user to select the exact mix of general purpose Port I/O and digital resources needed for the particular application.

Figure 1.11. Digital Crossbar Diagram

#### SFR Definition 5.3. ADC0CF: ADC0 Configuration

SFR Page: 0 SFR Address: 0xBC

| R/W    | R/W    | R/W    | R/W    | R/W    | R/W     | R/W     | R/W     | Reset Value |

|--------|--------|--------|--------|--------|---------|---------|---------|-------------|

| AD0SC4 | AD0SC3 | AD0SC2 | AD0SC1 | AD0SC0 | AMP0GN2 | AMP0GN1 | AMP0GN0 | 11111000    |

| Bit7   | Bit6   | Bit5   | Bit4   | Bit3   | Bit2    | Bit1    | Bit0    |             |

Bits7-3: AD0SC4-0: ADC0 SAR Conversion Clock Period Bits.

The SAR Conversion clock is derived from system clock by the following equation, where ADOSC refers to the 5-bit value held in ADOSC4-0, and  $CLK_{SAR0}$  refers to the desired ADC0 SAR clock (Note: the ADC0 SAR Conversion Clock should be less than or equal to 2.5 MHz).

$$AD0SC = \frac{SYSCLK}{2 \times CLK_{SAR0}} - 1 \qquad (AD0SC > 00000b)$$

When the ADOSC bits are equal to 00000b, the SAR Conversion clock is equal to SYSCLK to facilitate faster ADC conversions at slower SYSCLK speeds.

Bits2-0: AMP0GN2-0: ADC0 Internal Amplifier Gain (PGA).

000: Gain = 1 001: Gain = 2 010: Gain = 4 011: Gain = 8 10x: Gain = 16 11x: Gain = 0.5

#### 7.3. ADC2 Programmable Window Detector

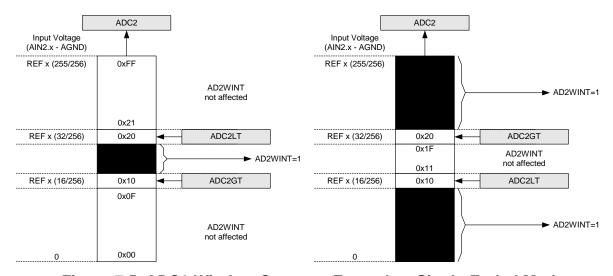

The ADC2 Programmable Window Detector continuously compares the ADC2 output to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD2WINT in register ADC2CN) can also be used in polled mode. The ADC2 Greater-Than (ADC2GT) and Less-Than (ADC2LT) registers hold the comparison values. Example comparisons for Differential and Single-ended modes are shown in Figure 7.6 and Figure 7.5, respectively. Notice that the window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC2LT and ADC2GT registers.

#### 7.3.1. Window Detector In Single-Ended Mode

Figure 7.5 shows two example window comparisons for Single-ended mode, with ADC2LT = 0x20 and ADC2GT = 0x10. Notice that in Single-ended mode, the codes vary from 0 to VREF\*(255/256) and are represented as 8-bit unsigned integers. In the left example, an AD2WINT interrupt will be generated if the ADC2 conversion word (ADC2) is within the range defined by ADC2GT and ADC2LT (if 0x10 < ADC2 < 0x20). In the right example, and AD2WINT interrupt will be generated if ADC2 is outside of the range defined by ADC2GT and ADC2LT (if ADC2 < 0x10 or ADC2 > 0x20).

Figure 7.5. ADC2 Window Compare Examples, Single-Ended Mode

SILICON LABS

### **Table 7.1. ADC2 Electrical Characteristics**

$V_{DD}$  = 3.0 V, AV+ = 3.0 V, VREF2 = 2.40 V (REFBE = 0), PGA gain = 1, -40 to +85 °C unless otherwise specified.

| Parameter                                   | Conditions                         | Min                                   | Тур       | Max       | Units  |

|---------------------------------------------|------------------------------------|---------------------------------------|-----------|-----------|--------|

|                                             | DC Accuracy                        |                                       |           |           |        |

| Resolution                                  |                                    |                                       | 8         |           | bits   |

| Integral Nonlinearity                       |                                    | _                                     | _         | ±1        | LSB    |

| Differential Nonlinearity                   | Guaranteed Monotonic               |                                       | _         | ±1        | LSB    |

| Offset Error                                |                                    |                                       | 0.5±0.3   | _         | LSB    |

| Full Scale Error                            | Differential mode                  | _                                     | -1±0.2    | _         | LSB    |

| Offset Temperature Coefficient              |                                    | _                                     | 10        | _         | ppm/°C |

| Dynamic Performance                         | (10 kHz sine-wave input, 1 dB      | below F                               | ull Scale | , 500 ksp | os     |

| Signal-to-Noise Plus Distortion             |                                    | 45                                    | 47        | _         | dB     |

| Total Harmonic Distortion                   | Up to the 5 <sup>th</sup> harmonic | _                                     | -51       | _         | dB     |

| Spurious-Free Dynamic Range                 |                                    | _                                     | 52        | _         | dB     |

|                                             | Conversion Rate                    | ·                                     |           |           |        |

| SAR Clock Frequency                         |                                    |                                       | _         | 6         | MHz    |

| Conversion Time in SAR Clocks               |                                    | 8                                     | _         | _         | clocks |

| Track/Hold Acquisition Time                 |                                    | 300                                   | _         | _         | ns     |

| Throughput Rate                             |                                    | _                                     | _         | 500       | ksps   |

|                                             | Analog Inputs                      | · · · · · · · · · · · · · · · · · · · |           |           |        |

| Input Voltage Range                         |                                    | 0                                     | _         | VREF      | V      |

| Input Capacitance                           |                                    | _                                     | 5         | _         | pF     |

|                                             | Power Specifications               |                                       |           |           |        |

| Power Supply Current (AV+ supplied to ADC2) | Operating Mode, 500 ksps           | _                                     | 420       | 900       | μΑ     |

| Power Supply Rejection                      |                                    |                                       | ±0.3      | _         | mV/V   |

**Notes:**

#### 9. Voltage Reference

The voltage reference options available on the C8051F12x and C8051F13x device families vary according to the device capabilities.

All devices include an internal voltage reference circuit, consisting of a 1.2 V, 15 ppm/°C (typical) bandgap voltage reference generator and a gain-of-two output buffer amplifier. The internal reference may be routed via the VREF pin to external system components or to the voltage reference input pins. The maximum load seen by the VREF pin must be less than 200  $\mu$ A to AGND. Bypass capacitors of 0.1  $\mu$ F and 4.7  $\mu$ F are recommended from the VREF pin to AGND.

The Reference Control Register, REF0CN enables/disables the internal reference generator and the internal temperature sensor on all devices. The BIASE bit in REF0CN enables the on-board reference generator while the REFBE bit enables the gain-of-two buffer amplifier which drives the VREF pin. When disabled, the supply current drawn by the bandgap and buffer amplifier falls to less than 1  $\mu$ A (typical) and the output of the buffer amplifier enters a high impedance state. If the internal bandgap is used as the reference voltage generator, BIASE and REFBE must both be set to logic 1. If the internal reference is not used, REFBE may be set to logic 0. Note that the BIASE bit must be set to logic 1 if any DACs or ADCs are used, regardless of whether the voltage reference is derived from the on-chip reference or supplied by an off-chip source. If no ADCs or DACs are being used, both of these bits can be set to logic 0 to conserve power.

When enabled, the temperature sensor connects to the highest order input of the ADC0 input multiplexer. The TEMPE bit within REF0CN enables and disables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state. Any ADC measurements performed on the sensor while disabled will result in undefined data.

The electrical specifications for the internal voltage reference are given in Table 9.1.

#### 9.1. Reference Configuration on the C8051F120/2/4/6

On the C8051F120/2/4/6 devices, the REF0CN register also allows selection of the voltage reference source for ADC0 and ADC2, as shown in SFR Definition 9.1. Bits AD0VRS and AD2VRS in the REF0CN register select the ADC0 and ADC2 voltage reference sources, respectively. Three voltage reference input pins allow each ADC and the two DACs to reference an external voltage reference or the on-chip voltage reference output (with an external connection). ADC0 may also reference the DAC0 output internally, and ADC2 may reference the analog power supply voltage, via the VREF multiplexers shown in Figure 9.1.

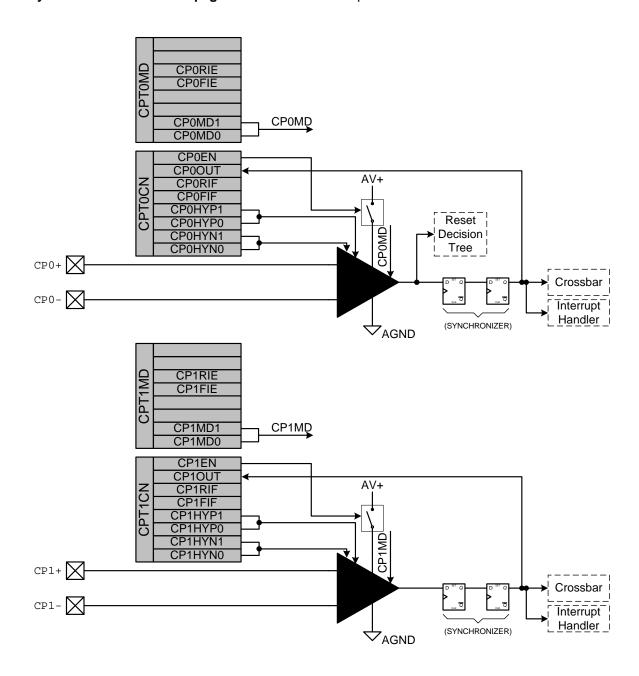

### 10. Comparators

Two on-chip programmable voltage comparators are included, as shown in Figure 10.1. The inputs of each comparator are available at dedicated pins. The output of each comparator is optionally available at the package pins via the I/O crossbar. When assigned to package pins, each comparator output can be programmed to operate in open drain or push-pull modes. See **Section "18.1. Ports 0 through 3 and the Priority Crossbar Decoder" on page 238** for Crossbar and port initialization details.

Figure 10.1. Comparator Functional Block Diagram

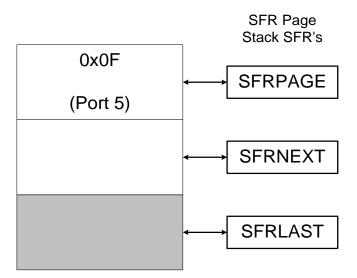

#### 11.2.6.3.SFR Page Stack Example

The following is an example that shows the operation of the SFR Page Stack during interrupts.

In this example, the SFR Page Control is left in the default enabled state (i.e., SFRPGEN = 1), and the CIP-51 is executing in-line code that is writing values to Port 5 (SFR "P5", located at address 0xD8 on SFR Page 0x0F). The device is also using the Programmable Counter Array (PCA) and the 10-bit ADC (ADC2) window comparator to monitor a voltage. The PCA is timing a critical control function in its interrupt service routine (ISR), so its interrupt is enabled and is set to *high* priority. The ADC2 is monitoring a voltage that is less important, but to minimize the software overhead its window comparator is being used with an associated ISR that is set to *low* priority. At this point, the SFR page is set to access the Port 5 SFR (SFRPAGE = 0x0F). See Figure 11.5 below.

Figure 11.5. SFR Page Stack While Using SFR Page 0x0F To Access Port 5

While CIP-51 executes in-line code (writing values to Port 5 in this example), ADC2 Window Comparator Interrupt occurs. The CIP-51 vectors to the ADC2 Window Comparator ISR and pushes the current SFR Page value (SFR Page 0x0F) into SFRNEXT in the SFR Page Stack. The SFR page needed to access ADC2's SFR's is then automatically placed in the SFRPAGE register (SFR Page 0x02). SFRPAGE is considered the "top" of the SFR Page Stack. Software can now access the ADC2 SFR's. Software may switch to any SFR Page by writing a new value to the SFRPAGE register at any time during the ADC2 ISR to access SFR's that are not on SFR Page 0x02. See Figure 11.6 below.

SILICON LABS

#### **Table 11.3. Special Function Registers (Continued)**

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

| Register         | Address | SFR<br>Page | Description                                  | Page No.                |

|------------------|---------|-------------|----------------------------------------------|-------------------------|

|                  |         | 1 age       |                                              | page 114 <sup>5</sup> , |

| REF0CN           | 0xD1    | 0           | Voltage Reference Control                    | page 116 <sup>6</sup> , |

| KEI OOK          | OXD I   |             | voltago recionolo control                    | page 117 <sup>7</sup>   |

| RSTSRC           | 0xEF    | 0           | Reset Source                                 |                         |

| SADDR0           | 0xEF    | 0           | UART 0 Slave Address                         | page 182                |

| SADDRU<br>SADENO |         |             |                                              | page 298                |

| SBUF0            | 0xB9    | 0           | UART 0 Slave Address Mask UART 0 Data Buffer | page 298                |

| SBUF1            | 0x99    |             | UART 1 Data Buffer                           | page 298                |

|                  | 0x99    | 1           |                                              | page 305                |

| SCON0            | 0x98    | 0           | UART 0 Control                               | page 296                |

| SCON1            | 0x98    | 1           | UART 1 Control                               | page 304                |

| SFRLAST          | 0x86    |             | SFR Stack Last Page                          | page 143                |

| SFRNEXT          | 0x85    |             | SFR Stack Next Page                          | page 143                |

| SFRPAGE          | 0x84    | _           | SFR Page Select                              | page 142                |

| SFRPGCN          | 0x96    | F           | SFR Page Control                             | page 142                |

| SMB0ADR          | 0xC3    | 0           | SMBus Slave Address                          | page 269                |

| SMB0CN           | 0xC0    | 0           | SMBus Control                                | page 266                |

| SMB0CR           | 0xCF    | 0           | SMBus Clock Rate                             | page 267                |

| SMB0DAT          | 0xC2    | 0           | SMBus Data                                   | page 268                |

| SMB0STA          | 0xC1    | 0           | SMBus Status                                 | page 269                |

| SP               | 0x81    | All Pages   |                                              | page 151                |

| SPI0CFG          | 0x9A    | 0           | SPI Configuration                            | page 280                |

| SPI0CKR          | 0x9D    | 0           | SPI Clock Rate Control                       | page 282                |

| SPI0CN           | 0xF8    | 0           | SPI Control                                  | page 281                |

| SPI0DAT          | 0x9B    | 0           | SPI Data                                     | page 282                |

| SSTA0            | 0x91    | 0           | UART 0 Status                                | page 297                |

| TCON             | 0x88    | 0           | Timer/Counter Control                        | page 313                |

| TH0              | 0x8C    | 0           | Timer/Counter 0 High Byte                    | page 316                |

| TH1              | 0x8D    | 0           | Timer/Counter 1 High Byte                    | page 316                |

| TL0              | 0x8A    | 0           | Timer/Counter 0 Low Byte                     | page 315                |

| TL1              | 0x8B    | 0           | Timer/Counter 1 Low Byte                     | page 316                |

| TMOD             | 0x89    | 0           | Timer/Counter Mode                           | page 314                |

| TMR2CF           | 0xC9    | 0           | Timer/Counter 2 Configuration                | page 324                |

| TMR2CN           | 0xC8    | 0           | Timer/Counter 2 Control                      | page 324                |

| TMR2H            | 0xCD    | 0           | Timer/Counter 2 High Byte                    | page 324                |

| TMR2L            | 0xCC    | 0           | Timer/Counter 2 Low Byte                     | page 323                |

| TMR3CF           | 0xC9    | 1           | Timer 3 Configuration                        | page 324                |

| TMR3CN           | 0xC8    | 1           | Timer 3 Control                              | page 324                |

| TMR3H            | 0xCD    | 1           | Timer 3 High Byte                            | page 324                |

| TMR3L            | 0xCC    | 1           | Timer 3 Low Byte                             | page 323                |

| TMR4CF           | 0xC9    | 2           | Timer/Counter 4 Configuration                | page 324                |

| TMR4CN           | 0xC8    | 2           | Timer/Counter 4 Control                      | page 324                |

| TMR4H            | 0xCD    | 2           | Timer/Counter 4 High Byte                    | page 324                |

#### 12.6. Rounding and Saturation

A Rounding Engine is included, which can be used to provide a rounded result when operating on fractional numbers. MACO uses an unbiased rounding algorithm to round the data stored in bits 31–16 of the accumulator, as shown in Table 12.1. Rounding occurs during the third stage of the MACO pipeline, after any shift operation, or on a write to the LSB of the accumulator. The rounded results are stored in the rounding registers: MACORNDH (SFR Definition 12.12) and MACORNDL (SFR Definition 12.13). The accumulator registers are not affected by the rounding engine. Although rounding is primarily used for fractional data, the data in the rounding registers is updated in the same way when operating in integer mode.

| Accumulator Bits 15–0 (MAC0ACC1:MAC0ACC0) | Accumulator Bits 31–16 (MAC0ACC3:MAC0ACC2) |      | Rounded Results<br>(MAC0RNDH:MAC0RNDL) |

|-------------------------------------------|--------------------------------------------|------|----------------------------------------|

| Greater Than 0x8000                       | Anything                                   | Up   | (MAC0ACC3:MAC0ACC2) + 1                |

| Less Than 0x8000                          | Anything                                   | Down | (MAC0ACC3:MAC0ACC2)                    |

| Equal To 0x8000                           | Odd (LSB = 1)                              | Up   | (MAC0ACC3:MAC0ACC2) + 1                |

| Equal To 0x8000                           | Even (LSB = 0)                             | Down | (MAC0ACC3:MAC0ACC2)                    |

Table 12.1. MAC0 Rounding (MAC0SAT = 0)

The rounding engine can also be used to saturate the results stored in the rounding registers. If the MACOSAT bit is set to '1' and the rounding register overflows, the rounding registers will saturate. When a positive overflow occurs, the rounding registers will show a value of 0x7FFF when saturated. For a negative overflow, the rounding registers will show a value of 0x8000 when saturated. If the MACOSAT bit is cleared to '0', the rounding registers will not saturate.

#### 12.7. Usage Examples

168

This section details some software examples for using MAC0. **Section 12.7.1** shows a series of two MAC operations using fractional numbers. **Section 12.7.2** shows a single operation in Multiply Only mode with integer numbers. The last example, shown in **Section 12.7.3**, demonstrates how the left-shift and right-shift operations can be used to modify the accumulator. All of the examples assume that all of the flags in the MAC0STA register are initially set to '0'.

#### 12.7.1. Multiply and Accumulate Example

The example below implements the equation:

```

(0.5 \times 0.25) + (0.5 \times -0.25) = 0.125 - 0.125 = 0.0

```

```

MACOCF, #0Ah

; Set to Clear Accumulator, Use fractional numbers

MOV

VOM

MACOAH, #40h

; Load MACOA register with 4000 hex = 0.5 decimal

MOV

MACOAL, #00h

MACOBH, #20h

; Load MACOB register with 2000 hex = 0.25 decimal

VOM

; This line initiates the first MAC operation

VOM

MACOBL, #00h

MACOBH, #E0h

; Load MACOB register with E000 hex = -0.25 decimal

MOV

MACOBL, #00h

; This line initiates the second MAC operation

MOV

NOP

; After this instruction, the Accumulator should be equal to 0,

; and the MACOSTA register should be 0x04, indicating a zero

NOP

; After this instruction, the Rounding register is updated

```

Rev. 1.4

SILICON LABS

| Not | ES: |

|-----|-----|

|-----|-----|

#### SFR Definition 16.1. CCH0CN: Cache Control

| R/W    | R/W    | R/W    | R/W    | R/W    | R/W   | R/W    | R/W    | Reset Value |

|--------|--------|--------|--------|--------|-------|--------|--------|-------------|

| CHWREN | CHRDEN | CHPFEN | CHFLSH | CHRETI | CHISR | CHMOVC | CHBLKW | 11100110    |

| Bit7   | Bit6   | Bit5   | Bit4   | Bit3   | Bit2  | Bit1   | Bit0   | •           |

SFR Address: 0xA1 SFR Page: F

Bit 7: CHWREN: Cache Write Enable.

This bit enables the processor to write to the cache memory.

0: Cache contents are not allowed to change, except during Flash writes/erasures or cache locks.

1: Writes to cache memory are allowed.

Bit 6: CHRDEN: Cache Read Enable.

This bit enables the processor to read instructions from the cache memory.

0: All instruction data comes from Flash memory or the prefetch engine.

1: Instruction data is obtained from cache (when available).

Bit 5: CHPFEN: Cache Prefetch Enable.

This bit enables the prefetch engine.

0: Prefetch engine is disabled.

1: Prefetch engine is enabled.

Bit 4: CHFLSH: Cache Flush.

When written to a '1', this bit clears the cache contents. This bit always reads '0'.

Bit 3: CHRETI: Cache RETI Destination Enable.

This bit enables the destination of a RETI address to be cached.

0: Destinations of RETI instructions will not be cached.

1: RETI destinations will be cached.

Bit 2: CHISR: Cache ISR Enable.

This bit allows instructions which are part of an Interrupt Service Rountine (ISR) to be cached.

0: Instructions in ISRs will not be loaded into cache memory.

1: Instructions in ISRs can be cached.

Bit 1: CHMOVC: Cache MOVC Enable.

This bit allows data requested by a MOVC instruction to be loaded into the cache memory.

0: Data requested by MOVC instructions will not be cached.

1: Data requested by MOVC instructions will be loaded into cache memory.

Bit 0: CHBLKW: Block Write Enable.

This bit allows block writes to Flash memory from software.

0: Each byte of a software Flash write is written individually.

1: Flash bytes are written in groups of four (for code space writes) or two (for scratchpad writes).

### **SFR Definition 17.3. EMIOTC: External Memory Timing Control**

| R/W      | R/W                                                                                                                                                                                                              | R/W                                       | R/W                              | R/W                             | R/W  | R/W  | R/W  | Reset Value |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------|---------------------------------|------|------|------|-------------|--|

| EAS1     | EAS0                                                                                                                                                                                                             | ERW3                                      | EWR2                             | EWR1                            | EWR0 | EAH1 | EAH0 | 11111111    |  |

| Bit7     | Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0  SFR Address: 0xA1  SFR Page: 0                                                                                                                                               |                                           |                                  |                                 |      |      |      |             |  |

| Bits7–6: | EAS1-0: EMIF Address Setup Time Bits.  00: Address setup time = 0 SYSCLK cycles.  01: Address setup time = 1 SYSCLK cycle.  10: Address setup time = 2 SYSCLK cycles.  11: Address setup time = 3 SYSCLK cycles. |                                           |                                  |                                 |      |      |      |             |  |

| Bits5-2: | <ul><li>10: Address setup time = 2 SYSCLK cycles.</li><li>11: Address setup time = 3 SYSCLK cycles.</li></ul>                                                                                                    |                                           |                                  |                                 |      |      |      |             |  |

| Bits1–0: | EAH1-0: EM<br>00: Address<br>01: Address<br>10: Address<br>11: Address                                                                                                                                           | hold time =<br>hold time =<br>hold time = | 0 SYSCLK<br>1 SYSCLK<br>2 SYSCLK | Ccycles.<br>Ccycle.<br>Ccycles. |      |      |      |             |  |

**Table 19.1. SMB0STA Status Codes and States**

| 0x08 | START condition transmitted.                  | Load SMB0DAT with Slave Address + R/W. Clear STA.                                                       |

|------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------|

| 0x10 | Repeated START condition transmitted.         | Load SMB0DAT with Slave Address + R/W. Clear STA.                                                       |

| 0x18 | Slave Address + W transmitted. ACK received.  | Load SMB0DAT with data to be transmitted.                                                               |

| 0x20 | Slave Address + W transmitted. NACK received. | Acknowledge poll to retry. Set STO + STA.                                                               |

| 0x28 | Data byte transmitted. ACK received.          | 1) Load SMB0DAT with next byte, OR     2) Set STO, OR     3) Clear STO then set STA for repeated START. |

| 0x30 | Data byte transmitted. NACK received.         | 1) Retry transfer OR<br>2) Set STO.                                                                     |

| 0x38 | Arbitration Lost.                             | Save current data.                                                                                      |

| 0x40 | Slave Address + R transmitted. ACK received.  | If only receiving one byte, clear AA (send NACK after received byte). Wait for received data.           |

| 0x48 | Slave Address + R transmitted. NACK received. | Acknowledge poll to retry. Set STO + STA.                                                               |

| 0x50 | Data byte received. ACK transmitted.          | Read SMB0DAT. Wait for next byte. If next byte is last byte, clear AA.                                  |

| 0x58 | Data byte received. NACK transmitted.         | Set STO.                                                                                                |

#### 20.2. SPI0 Master Mode Operation

A SPI master device initiates all data transfers on a SPI bus. SPI0 is placed in master mode by setting the Master Enable flag (MSTEN, SPI0CN.6). Writing a byte of data to the SPI0 data register (SPI0DAT) when in master mode writes to the transmit buffer. If the SPI shift register is empty, the byte in the transmit buffer is moved to the shift register, and a data transfer begins. The SPI0 master immediately shifts out the data serially on the MOSI line while providing the serial clock on SCK. The SPIF (SPI0CN.7) flag is set to logic 1 at the end of the transfer. If interrupts are enabled, an interrupt request is generated when the SPIF flag is set. While the SPI0 master transfers data to a slave on the MOSI line, the addressed SPI slave device simultaneously transfers the contents of its shift register to the SPI master on the MISO line in a full-duplex operation. Therefore, the SPIF flag serves as both a transmit-complete and receive-data-ready flag. The data byte received from the slave is transferred MSB-first into the master's shift register. When a byte is fully shifted into the register, it is moved to the receive buffer where it can be read by the processor by reading SPI0DAT.

When configured as a master, SPI0 can operate in one of three different modes: multi-master mode, 3-wire single-master mode, and 4-wire single-master mode. The default, multi-master mode is active when NSS-MD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In this mode, NSS is an input to the device, and is used to disable the master SPI0 when another master is accessing the bus. When NSS is pulled low in this mode, MSTEN (SPI0CN.6) and SPIEN (SPI0CN.0) are set to 0 to disable the SPI master device, and a Mode Fault is generated (MODF, SPI0CN.5 = 1). Mode Fault will generate an interrupt if enabled. SPI0 must be manually re-enabled in software under these circumstances. In multi-master systems, devices will typically default to being slave devices while they are not acting as the system master device. In multi-master mode, slave devices can be addressed individually (if needed) using general-purpose I/O pins. Figure 20.2 shows a connection diagram between two master devices in multiple-master mode.

3-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. In this mode, NSS is not used, and is not mapped to an external port pin through the crossbar. Any slave devices that must be addressed in this mode should be selected using general-purpose I/O pins. Figure 20.3 shows a connection diagram between a master device in 3-wire master mode and a slave device.

4-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 1. In this mode, NSS is configured as an output pin, and can be used as a slave-select signal for a single SPI device. In this mode, the output value of NSS is controlled (in software) with the bit NSSMD0 (SPI0CN.2). Additional slave devices can be addressed using general-purpose I/O pins. Figure 20.4 shows a connection diagram for a master device in 4-wire master mode and two slave devices.

#### SFR Definition 21.2. SSTA0: UARTO Status and Clock Selection

| R/W  | R/W   | R/W    | R/W   | R/W     | R/W     | R/W     | R/W     | Reset Value |

|------|-------|--------|-------|---------|---------|---------|---------|-------------|

| FE0  | RXOV0 | TXCOL0 | SMOD0 | S0TCLK1 | S0TCLK0 | S0RCLK1 | S0RCLK0 | 00000000    |

| Rit7 | Rit6  | Bit5   | Rit4  | Rit3    | Rit2    | Rit1    | Rit∩    | •           |

SFR Address: 0x91 SFR Page: 0

Bit7: FE0: Frame Error Flag.\*

This flag indicates if an invalid (low) STOP bit is detected.

0: Frame Error has not been detected

1: Frame Error has been detected.

Bit6: RXOV0: Receive Overrun Flag.\*

This flag indicates new data has been latched into the receive buffer before software has read the previous byte.

0: Receive overrun has not been detected.

1: Receive Overrun has been detected.

Bit5: TXCOL0: Transmit Collision Flag.\*

This flag indicates user software has written to the SBUF0 register while a transmission is in progress.

0: Transmission Collision has not been detected.

1: Transmission Collision has been detected.

Bit4: SMOD0: UART0 Baud Rate Doubler Enable.

This bit enables/disables the divide-by-two function of the UART0 baud rate logic for configurations described in the UART0 section.

0: UART0 baud rate divide-by-two enabled.

1: UART0 baud rate divide-by-two disabled.

Bits3-2: UART0 Transmit Baud Rate Clock Selection Bits

| S0TCLK1 | S0TCLK0 | Serial Transmit Baud Rate Clock Source        |

|---------|---------|-----------------------------------------------|

| 0       | 0       | Timer 1 generates UART0 TX Baud Rate          |

| 0       | 1       | Timer 2 Overflow generates UART0 TX baud rate |

| 1       | 0       | Timer 3 Overflow generates UART0 TX baud rate |

| 1       | 1       | Timer 4 Overflow generates UART0 TX baud rate |

#### Bits1-0: UARTO Receive Baud Rate Clock Selection Bits

| S0RCLK1 | S0RCLK0 | Serial Receive Baud Rate Clock Source         |

|---------|---------|-----------------------------------------------|

| 0       | 0       | Timer 1 generates UART0 RX Baud Rate          |

| 0       | 1       | Timer 2 Overflow generates UART0 RX baud rate |

| 1       | 0       | Timer 3 Overflow generates UART0 RX baud rate |

| 1       | 1       | Timer 4 Overflow generates UART0 RX baud rate |

\*Note: FE0, RXOV0, and TXCOL0 are flags only, and no interrupt is generated by these conditions.

Table 22.2. Timer Settings for Standard Baud Rates Using an External 25.0 MHz Oscillator

|                              | Frequency: 25.0 MHz          |                      |                                  |                       |                                     |      |                                  |  |

|------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------|------|----------------------------------|--|

|                              | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload<br>Value (hex) |  |

| SYSCLK from<br>External Osc. | 230400                       | -0.47%               | 108                              | SYSCLK                | XX                                  | 1    | 0xCA                             |  |

|                              | 115200                       | 115200 0.45% 218     |                                  | SYSCLK                | XX                                  | 1    | 0x93                             |  |

|                              | 57600                        | -0.01%               | 434                              | SYSCLK                | XX                                  | 1    | 0x27                             |  |

|                              | 28800                        | 0.45%                | 872                              | SYSCLK / 4            | 01                                  | 0    | 0x93                             |  |

|                              | 14400                        | -0.01%               | 1736                             | SYSCLK / 4            | 01                                  | 0    | 0x27                             |  |

|                              | 9600                         | 0.15%                | 2608                             | EXTCLK / 8            | 11                                  | 0    | 0x5D                             |  |

|                              | 2400                         | 0.45%                | 10464                            | SYSCLK / 48           | 10                                  | 0    | 0x93                             |  |

|                              | 1200                         | -0.01%               | 20832                            | SYSCLK / 48           | 10                                  | 0    | 0x27                             |  |

| SYSCLK from Internal Osc.    | 57600                        | -0.47%               | 432                              | EXTCLK / 8            | 11                                  | 0    | 0xE5                             |  |

|                              | 28800                        | -0.47%               | 864                              | EXTCLK / 8            | 11                                  | 0    | 0xCA                             |  |

|                              | 14400                        | 0.45%                | 1744                             | EXTCLK / 8            | 11                                  | 0    | 0x93                             |  |

|                              | 9600                         | 0.15%                | 2608                             | EXTCLK / 8            | 11                                  | 0    | 0x5D                             |  |

X = Don't care

\*Note: SCA1-SCA0 and T1M bit definitions can be found in Section 23.1.

Table 22.3. Timer Settings for Standard Baud Rates Using an External 22.1184 MHz

Oscillator

|                              | Frequency: 22.1184 MHz       |                      |                                  |                       |                                     |      |                                  |

|------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------|------|----------------------------------|

|                              | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload<br>Value (hex) |

|                              | 230400                       | 0.00%                | 96                               | SYSCLK                | XX                                  | 1    | 0xD0                             |

| SYSCLK from<br>External Osc. | 115200                       | 0.00%                | 192                              | SYSCLK                | XX                                  | 1    | 0xA0                             |

|                              | 57600                        | 0.00%                | 384                              | SYSCLK                | XX                                  | 1    | 0x40                             |

|                              | 28800                        | 0.00%                | 768                              | SYSCLK / 12           | 00                                  | 0    | 0xE0                             |

|                              | 14400                        | 0.00%                | 1536                             | SYSCLK / 12           | 00                                  | 0    | 0xC0                             |

|                              | 9600                         | 0.00%                | 2304                             | SYSCLK / 12           | 00                                  | 0    | 0xA0                             |

|                              | 2400                         | 0.00%                | 9216                             | SYSCLK / 48           | 10                                  | 0    | 0xA0                             |

|                              | 1200                         | 0.00%                | 18432                            | SYSCLK / 48           | 10                                  | 0    | 0x40                             |

| SYSCLK from Internal Osc.    | 230400                       | 0.00%                | 96                               | EXTCLK / 8            | 11                                  | 0    | 0xFA                             |

|                              | 115200                       | 0.00%                | 192                              | EXTCLK / 8            | 11                                  | 0    | 0xF4                             |

|                              | 57600                        | 0.00%                | 384                              | EXTCLK / 8            | 11                                  | 0    | 0xE8                             |

|                              | 28800                        | 0.00%                | 768                              | EXTCLK / 8            | 11                                  | 0    | 0xD0                             |

|                              | 14400                        | 0.00%                | 1536                             | EXTCLK / 8            | 11                                  | 0    | 0xA0                             |

|                              | 9600                         | 0.00%                | 2304                             | EXTCLK / 8            | 11                                  | 0    | 0x70                             |

X = Don't care

\*Note: SCA1-SCA0 and T1M bit definitions can be found in Section 23.1.

SILICON LABS

**Important Note About the PCA0CN Register:** If the main PCA counter (PCA0H: PCA0L) overflows during the execution phase of a read-modify-write instruction (bit-wise SETB or CLR, ANL, ORL, XRL) that targets the PCA0CN register, the CF (Counter Overflow) bit will not be set. If the CF flag is used by software to keep track of counter overflows, the following steps should be taken when performing a bit-wise operation on the PCA0CN register:

- Step 1. Disable global interrupts.

- Step 2. Read PCA0L. This will latch the value of PCA0H.

- Step 3. Read PCA0H, saving the value.

- Step 4. Execute the bit-wise operation on CCFn (for example, CLR CCF0, or CCF0 = 0;).

- Step 5. Read PCA0L.

- Step 6. Read PCA0H, saving the value.

- Step 7. If the value of PCA0H read in Step 3 is 0xFF and the value for PCA0H read in Step 6 is 0x00, then manually set the CF bit in software (for example, SETB CF, or CF = 1;).

- Step 8. Re-enable interrupts.

#### 24.3. Register Descriptions for PCA0

Following are detailed descriptions of the special function registers related to the operation of PCA0.

#### SFR Definition 24.1. PCA0CN: PCA Control

| R/W  | Reset Value |

|------|------|------|------|------|------|------|------|-------------|

| CF   | CR   | CCF5 | CCF4 | CCF3 | CCF2 | CCF1 | CCF0 | 00000000    |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | <u> </u>    |

SFR Address: 0xD8 SFR Page: 0

Bit7: CF: PCA Counter/Timer Overflow Flag.

Set by hardware when the PCA0 Counter/Timer overflows from 0xFFFF to 0x0000. When the Counter/Timer Overflow (CF) interrupt is enabled, setting this bit causes the CPU to vector to the CF interrupt service routine. This bit is not automatically cleared by hardware and

must be cleared by software.

CR: PCA0 Counter/Timer Run Control.

Bit6:

This bit enables/disables the PCA0 Counter/Timer.

0: PCA0 Counter/Timer disabled.1: PCA0 Counter/Timer enabled.

Bit5: CCF5: PCA0 Module 5 Capture/Compare Flag.

This bit is set by hardware when a match or capture occurs. When the CCF interrupt is enabled, setting this bit causes the CPU to vector to the CCF interrupt service routine. This

bit is not automatically cleared by hardware and must be cleared by software.

Bit4: CCF4: PCA0 Module 4 Capture/Compare Flag.

This bit is set by hardware when a match or capture occurs. When the CCF interrupt is enabled, setting this bit causes the CPU to vector to the CCF interrupt service routine. This

bit is not automatically cleared by hardware and must be cleared by software.

Bit3: CCF3: PCA0 Module 3 Capture/Compare Flag.

This bit is set by hardware when a match or capture occurs. When the CCF interrupt is enabled, setting this bit causes the CPU to vector to the CCF interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software.

Bit2: CCF2: PCA0 Module 2 Capture/Compare Flag.

This bit is set by hardware when a match or capture occurs. When the CCF interrupt is enabled, setting this bit causes the CPU to vector to the CCF interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software.

Bit1: CCF1: PCA0 Module 1 Capture/Compare Flag.

This bit is set by hardware when a match or capture occurs. When the CCF interrupt is enabled, setting this bit causes the CPU to vector to the CCF interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software.

CCF0: PCA0 Module 0 Capture/Compare Flag.

This bit is set by hardware when a match or capture occurs. When the CCF interrupt is enabled, setting this bit causes the CPU to vector to the CCF interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software.

Bit0: