#### Silicon Labs - C8051F132 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | 8051                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 100MHz                                                      |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT          |

| Number of I/O              | 64                                                          |

| Program Memory Size        | 64KB (64K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 8.25K x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                   |

| Data Converters            | A/D 8x10b                                                   |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 100-TQFP                                                    |

| Supplier Device Package    | 100-TQFP (14x14)                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f132 |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1. | System Overview                                       | 19 |

|----|-------------------------------------------------------|----|

|    | 1.1. CIP-51 <sup>™</sup> Microcontroller Core         | 27 |

|    | 1.1.1. Fully 8051 Compatible                          | 27 |

|    | 1.1.2. Improved Throughput                            | 27 |

|    | 1.1.3. Additional Features                            | 28 |

|    | 1.2. On-Chip Memory                                   | 29 |

|    | 1.3. JTAG Debug and Boundary Scan                     | 30 |

|    | 1.4. 16 x 16 MAC (Multiply and Accumulate) Engine     | 31 |

|    | 1.5. Programmable Digital I/O and Crossbar            | 32 |

|    | 1.6. Programmable Counter Array                       |    |

|    | 1.7. Serial Ports                                     |    |

|    | 1.8. 12 or 10-Bit Analog to Digital Converter         | 34 |

|    | 1.9. 8-Bit Analog to Digital Converter                |    |

|    | 1.10.12-bit Digital to Analog Converters              |    |

|    | 1.11.Analog Comparators                               |    |

|    | Absolute Maximum Ratings                              |    |

| 3. |                                                       |    |

| 4. | · · · · · · · · · · · · · · · · · · ·                 |    |

| 5. | ADC0 (12-Bit ADC, C8051F120/1/4/5 Only)               |    |

|    | 5.1. Analog Multiplexer and PGA                       |    |

|    | 5.2. ADC Modes of Operation                           |    |

|    | 5.2.1. Starting a Conversion                          |    |

|    | 5.2.2. Tracking Modes                                 |    |

|    | 5.2.3. Settling Time Requirements                     |    |

|    | 5.3. ADC0 Programmable Window Detector                |    |

| 6. | ADC0 (10-Bit ADC, C8051F122/3/6/7 and C8051F13x Only) |    |

|    | 6.1. Analog Multiplexer and PGA                       |    |

|    | 6.2. ADC Modes of Operation                           |    |

|    | 6.2.1. Starting a Conversion                          |    |

|    | 6.2.2. Tracking Modes                                 |    |

|    | 6.2.3. Settling Time Requirements                     |    |

|    | 6.3. ADC0 Programmable Window Detector                |    |

| 7. | ADC2 (8-Bit ADC, C8051F12x Only)                      |    |

|    | 7.1. Analog Multiplexer and PGA                       |    |

|    | 7.2. ADC2 Modes of Operation                          |    |

|    | 7.2.1. Starting a Conversion                          |    |

|    | 7.2.2. Tracking Modes                                 |    |

|    | 7.2.3. Settling Time Requirements                     |    |

|    | 7.3. ADC2 Programmable Window Detector 1              |    |

|    | 7.3.1. Window Detector In Single-Ended Mode 1         | 00 |

|    | 7.3.2. Window Detector In Differential Mode 1         | 01 |

|                 |                                             | Pin Nu                           | mbers |      |               |                                                                                                                                                                                                    |

|-----------------|---------------------------------------------|----------------------------------|-------|------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name            | <sup>'F120</sup><br>'F122<br>'F124<br>'F126 | 22 'F123 'F132 'F133<br>24 'F125 |       | Туре | Description   |                                                                                                                                                                                                    |

| AIN2.2/A10/P1.2 | 34                                          | 27                               | 34    | 27   | A In<br>D I/O | Port 1.2. See Port Input/Output section for complete description.                                                                                                                                  |

| AIN2.3/A11/P1.3 | 33                                          | 26                               | 33    | 26   | A In<br>D I/O | Port 1.3. See Port Input/Output section for complete description.                                                                                                                                  |

| AIN2.4/A12/P1.4 | 32                                          | 23                               | 32    | 23   | A In<br>D I/O | Port 1.4. See Port Input/Output section for complete description.                                                                                                                                  |

| AIN2.5/A13/P1.5 | 31                                          | 22                               | 31    | 22   | A In<br>D I/O | Port 1.5. See Port Input/Output section for complete description.                                                                                                                                  |

| AIN2.6/A14/P1.6 | 30                                          | 21                               | 30    | 21   | A In<br>D I/O | Port 1.6. See Port Input/Output section for complete description.                                                                                                                                  |

| AIN2.7/A15/P1.7 | 29                                          | 20                               | 29    | 20   | A In<br>D I/O | Port 1.7. See Port Input/Output section for complete description.                                                                                                                                  |

| A8m/A0/P2.0     | 46                                          | 37                               | 46    | 37   | D I/O         | Bit 8 External Memory Address bus (Multiplexed<br>mode)<br>Bit 0 External Memory Address bus (Non-multi-<br>plexed mode)<br>Port 2.0<br>See Port Input/Output section for complete<br>description. |

| A9m/A1/P2.1     | 45                                          | 36                               | 45    | 36   | D I/O         | Port 2.1. See Port Input/Output section for complete description.                                                                                                                                  |

| A10m/A2/P2.2    | 44                                          | 35                               | 44    | 35   | D I/O         | Port 2.2. See Port Input/Output section for complete description.                                                                                                                                  |

| A11m/A3/P2.3    | 43                                          | 34                               | 43    | 34   | D I/O         | Port 2.3. See Port Input/Output section for complete description.                                                                                                                                  |

| A12m/A4/P2.4    | 42                                          | 33                               | 42    | 33   | D I/O         | Port 2.4. See Port Input/Output section for complete description.                                                                                                                                  |

| A13m/A5/P2.5    | 41                                          | 32                               | 41    | 32   | D I/O         | Port 2.5. See Port Input/Output section for complete description.                                                                                                                                  |

| A14m/A6/P2.6    | 40                                          | 31                               | 40    | 31   | D I/O         | Port 2.6. See Port Input/Output section for complete description.                                                                                                                                  |

| A15m/A7/P2.7    | 39                                          | 30                               | 39    | 30   | D I/O         | Port 2.7. See Port Input/Output section for complete description.                                                                                                                                  |

Table 4.1. Pin Definitions (Continued)

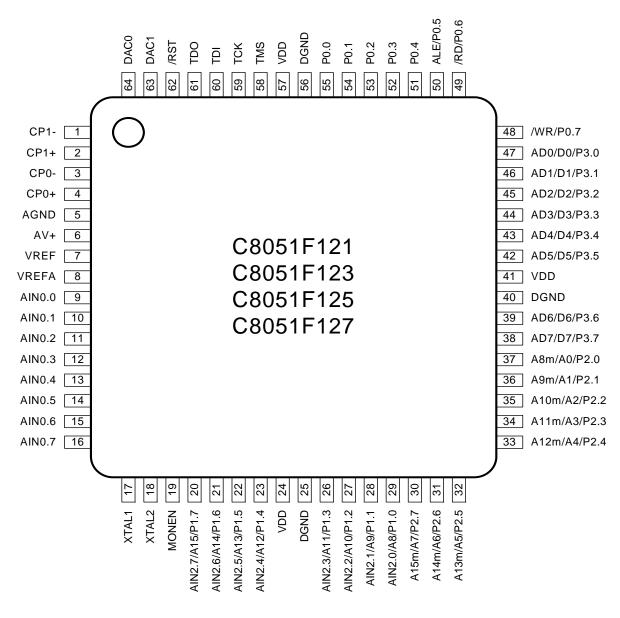

Figure 4.4. C8051F121/3/5/7 Pinout Diagram (TQFP-64)

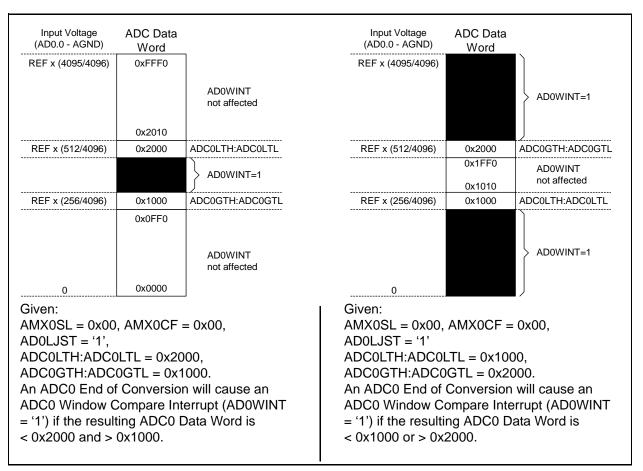

Figure 5.8. 12-Bit ADC0 Window Interrupt Example: Left Justified Single-Ended Data

### SFR Definition 6.4. ADC0CN: ADC0 Control

| R/W      | R/W                                                                                                                                          | R/W           | R/W           | R/W          | R/W                                     | R/W            | R/W           | Reset Value  |  |  |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|--------------|-----------------------------------------|----------------|---------------|--------------|--|--|--|--|--|

| ADOEN    | AD0TM                                                                                                                                        | <b>AD0INT</b> | AD0BUSY       | AD0CM1       | AD0CM0                                  | ADOWINT        | AD0LJST       | 00000000     |  |  |  |  |  |

| Bit7     | Bit6                                                                                                                                         | Bit5          | Bit4          | Bit3         | Bit2                                    | Bit1           | Bit0          |              |  |  |  |  |  |

| Bit7:    |                                                                                                                                              | 20 Enchla     | D:+           |              |                                         |                |               |              |  |  |  |  |  |

| DIL7.    | AD0EN: AD0                                                                                                                                   |               |               | nowor chi    | tdown                                   |                |               |              |  |  |  |  |  |

|          | <ul><li>0: ADC0 Disabled. ADC0 is in low-power shutdown.</li><li>1: ADC0 Enabled. ADC0 is active and ready for data conversions.</li></ul>   |               |               |              |                                         |                |               |              |  |  |  |  |  |

| Bit6:    | AD0TM: AD0                                                                                                                                   |               |               | anu reauy    |                                         | versions.      |               |              |  |  |  |  |  |

| Bito.    |                                                                                                                                              |               |               | cina is cont | inuous unle                             | ss a conversi  | on is in pro  | Cess         |  |  |  |  |  |

|          | 1: Tracking [                                                                                                                                |               |               | •            |                                         |                |               |              |  |  |  |  |  |

| Bit5:    | ADOINT: AD                                                                                                                                   |               |               |              | ot Flag.                                |                |               |              |  |  |  |  |  |

|          | This flag mu                                                                                                                                 |               |               |              | - · · · · · · · · · · · · · · · · · · · |                |               |              |  |  |  |  |  |

|          |                                                                                                                                              |               |               |              | n since the                             | last time this | flag was cl   | eared.       |  |  |  |  |  |

|          | 1: ADC0 has                                                                                                                                  |               |               |              |                                         |                | •             |              |  |  |  |  |  |

| Bit4:    | AD0BUSY: A                                                                                                                                   | ADC0 Busy     | y Bit.        |              |                                         |                |               |              |  |  |  |  |  |

|          | Read:                                                                                                                                        |               |               |              |                                         |                |               |              |  |  |  |  |  |

|          | 0: ADC0 Conversion is complete or a conversion is not currently in progress. AD0INT is set                                                   |               |               |              |                                         |                |               |              |  |  |  |  |  |

|          | to logic 1 on the falling edge of AD0BUSY.                                                                                                   |               |               |              |                                         |                |               |              |  |  |  |  |  |

|          | 1: ADC0 Conversion is in progress.                                                                                                           |               |               |              |                                         |                |               |              |  |  |  |  |  |

|          | Write:                                                                                                                                       |               |               |              |                                         |                |               |              |  |  |  |  |  |

|          | 0: No Effect.<br>1: Initiates ADC0 Conversion if AD0CM1-0 = 00b.                                                                             |               |               |              |                                         |                |               |              |  |  |  |  |  |

| D:4-2 0. |                                                                                                                                              |               |               |              |                                         |                |               |              |  |  |  |  |  |

| Bits3–2: | AD0CM1–0:<br>If AD0TM = 0                                                                                                                    |               | In or Conve   | ISION MODE   | Select.                                 |                |               |              |  |  |  |  |  |

|          | 00: ADC0 cc                                                                                                                                  |               | nitiated on a | wory writo   |                                         |                |               |              |  |  |  |  |  |

|          | 01: ADC0 cc                                                                                                                                  |               |               |              |                                         |                |               |              |  |  |  |  |  |

|          |                                                                                                                                              |               |               |              |                                         | CNVSTR0.       |               |              |  |  |  |  |  |

|          | <ol> <li>ADC0 conversion initiated on rising edge of external CNVSTR0.</li> <li>ADC0 conversion initiated on overflow of Timer 2.</li> </ol> |               |               |              |                                         |                |               |              |  |  |  |  |  |

|          | If AD0TM =                                                                                                                                   |               |               |              | -                                       |                |               |              |  |  |  |  |  |

|          | 00: Tracking                                                                                                                                 | starts with   | n the write o | f '1' to ADC | BUSY and I                              | asts for 3 SA  | R clocks, fo  | ollowed by   |  |  |  |  |  |

|          | conversion.                                                                                                                                  |               |               |              |                                         |                |               |              |  |  |  |  |  |

|          |                                                                                                                                              | started by    | the overflo   | w of Timer   | 3 and lasts                             | for 3 SAR clo  | ocks, follow  | ed by con-   |  |  |  |  |  |

|          | version.                                                                                                                                     |               |               |              |                                         |                |               |              |  |  |  |  |  |

|          |                                                                                                                                              |               | when CNVS     | TR0 input    | is logic low;                           | conversion s   | tarts on risi | ng           |  |  |  |  |  |

|          | CNVSTR0 e                                                                                                                                    |               |               | ·            |                                         |                |               |              |  |  |  |  |  |

|          | -                                                                                                                                            | started by    | the overflor  | w of Timer   | 2 and lasts                             | for 3 SAR clo  | ocks, follow  | ed by con-   |  |  |  |  |  |

| D:44     | version.                                                                                                                                     |               |               |              |                                         |                |               |              |  |  |  |  |  |

| Bit1:    | ADOWINT: A                                                                                                                                   |               |               |              | Flag.                                   |                |               |              |  |  |  |  |  |

|          | This bit must                                                                                                                                |               |               |              | e not occur                             | ed since this  | flog woo lo   | et cloared   |  |  |  |  |  |

|          | 1: ADC0 Wir                                                                                                                                  |               | •             |              |                                         |                | nay was la    | ist cleared. |  |  |  |  |  |

| Bit0:    | ADOLJST: A                                                                                                                                   |               | •             |              |                                         |                |               |              |  |  |  |  |  |

|          | 0: Data in Al                                                                                                                                |               | •             |              |                                         |                |               |              |  |  |  |  |  |

|          | () $()$ $()$ $()$ $()$ $()$ $()$ $()$                                                                                                        | ((()))        | () redister   | s are right. | Illistitied                             |                |               |              |  |  |  |  |  |

## 7.2. ADC2 Modes of Operation

ADC2 has a maximum conversion speed of 500 ksps. The ADC2 conversion clock (SAR2 clock) is a divided version of the system clock, determined by the AD2SC bits in the ADC2CF register. The maximum ADC2 conversion clock is 6 MHz.

#### 7.2.1. Starting a Conversion

A conversion can be initiated in one of five ways, depending on the programmed states of the ADC2 Start of Conversion Mode bits (AD2CM2-0) in ADC2CN. Conversions may be initiated by:

- 1. Writing a '1' to the AD2BUSY bit of ADC2CN;

- 2. A Timer 3 overflow (i.e. timed continuous conversions);

- 3. A rising edge detected on the external ADC convert start signal, CNVSTR2;

- 4. A Timer 2 overflow (i.e. timed continuous conversions);

- 5. Writing a '1' to the AD0BUSY of register ADC0CN (initiate conversion of ADC2 and ADC0 with a single software command).

During conversion, the AD2BUSY bit is set to logic 1 and restored to 0 when conversion is complete. The falling edge of AD2BUSY triggers an interrupt (when enabled) and sets the interrupt flag in ADC2CN. Converted data is available in the ADC2 data word, ADC2.

When a conversion is initiated by writing a '1' to AD2BUSY, it is recommended to poll AD2INT to determine when the conversion is complete. The recommended procedure is:

Step 1. Write a '0' to AD2INT; Step 2. Write a '1' to AD2BUSY; Step 3. Poll AD2INT for '1'; Step 4. Process ADC2 data.

When CNVSTR2 is used as a conversion start source, it must be enabled in the crossbar, and the corresponding pin must be set to open-drain, high-impedance mode (see **Section "18. Port Input/Output" on page 235** for more details on Port I/O configuration).

#### 7.2.2. Tracking Modes

The AD2TM bit in register ADC2CN controls the ADC2 track-and-hold mode. In its default state, the ADC2 input is continuously tracked, except when a conversion is in progress. When the AD2TM bit is logic 1, ADC2 operates in low-power track-and-hold mode. In this mode, each conversion is preceded by a track-ing period of 3 SAR clocks (after the start-of-conversion signal). When the CNVSTR2 signal is used to initiate conversions in low-power tracking mode, ADC2 tracks only when CNVSTR2 is low; conversion begins on the rising edge of CNVSTR2 (see Figure 7.2). Tracking can also be disabled (shutdown) when the entire chip is in low power standby or sleep modes. Low-power Track-and-Hold mode is also useful when AMUX or PGA settings are frequently changed, due to the settling time requirements described in **Section "7.2.3. Settling Time Requirements" on page 94**.

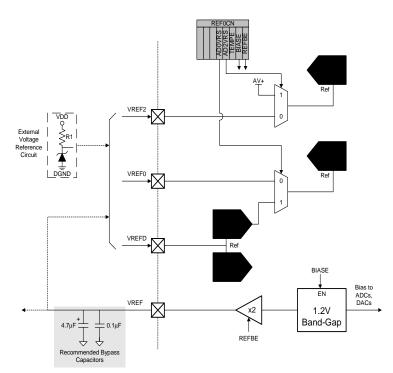

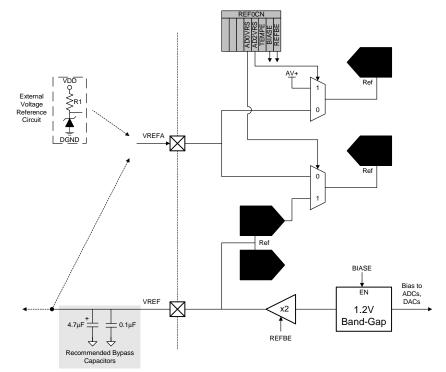

## Figure 9.1. Voltage Reference Functional Block Diagram (C8051F120/2/4/6)

| R/W      | R/W                 | R/W         | R/W           | R/W           | R/W           | R/W              | R/W        | Reset Value |

|----------|---------------------|-------------|---------------|---------------|---------------|------------------|------------|-------------|

| -        | -                   | -           | AD0VRS        | AD2VRS        | TEMPE         | BIASE            | REFBE      | 0000000     |

| Bit7     | Bit6                | Bit5        | Bit4          | Bit3          | Bit2          | Bit1             | Bit0       | <u>,</u>    |

| Bits7–5: | UNUSED. Re          | ad = 000b   | ; Write = dor | n't care.     |               |                  |            |             |

| Bit4:    | AD0VRS: AD          |             |               |               |               |                  |            |             |

|          | 0: ADC0 volta       | -           |               |               |               |                  |            |             |

|          | 1: ADC0 volta       | -           |               | •             |               |                  |            |             |

| Bit3:    | AD2VRS: AD          | •           |               |               |               |                  |            |             |

|          | 0: ADC2 volta       | ige referen | ce from VR    | EF2 pin.      |               |                  |            |             |

|          | 1: ADC2 volta       | ige referen | ce from AV-   | ۰.<br>۲.      |               |                  |            |             |

| Bit2:    | TEMPE: Tem          | perature S  | ensor Enabl   | e Bit.        |               |                  |            |             |

|          | 0: Internal Ter     | nperature   | Sensor Off.   |               |               |                  |            |             |

|          | 1: Internal Ter     | nperature   | Sensor On.    |               |               |                  |            |             |

| Bit1:    | BIASE: ADC/         | DAC Bias    | Generator E   | nable Bit. (I | Must be '1' i | if using AD      | C, DAC, or | VREF).      |

|          | 0: Internal Bia     | as Generat  | or Off.       |               |               | -                |            |             |

|          | 1: Internal Bia     | s Generat   | or On.        |               |               |                  |            |             |

| Bit0:    | <b>REFBE:</b> Inter | nal Refere  | nce Buffer E  | nable Bit.    |               |                  |            |             |

|          | 0: Internal Re      | ference Bu  | ıffer Off.    |               |               |                  |            |             |

|          |                     | , n         | (             | 1             |               | the state and an | n the VREF |             |

## 9.2. Reference Configuration on the C8051F121/3/5/7

On the C8051F121/3/5/7 devices, the REF0CN register also allows selection of the voltage reference source for ADC0 and ADC2, as shown in SFR Definition 9.2. Bits AD0VRS and AD2VRS in the REF0CN register select the ADC0 and ADC2 voltage reference sources, respectively. The VREFA pin provides a voltage reference input for ADC0 and ADC2, which can be connected to an external precision reference or the internal voltage reference. ADC0 may also reference the DAC0 output internally, and ADC2 may reference the analog power supply voltage, via the VREF multiplexers shown in Figure 9.2.

Figure 9.2. Voltage Reference Functional Block Diagram (C8051F121/3/5/7)

| R/W                   | R/W                                                                                            | R/W            | R/W          | R/W        | R/W           | R/W          | R/W             | Reset Value       |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------|----------------|--------------|------------|---------------|--------------|-----------------|-------------------|--|--|--|

| -                     | -                                                                                              | COB            | ANK          | -          | - IFBANK 00   |              | 00010001        |                   |  |  |  |

| Bit7                  | Bit6                                                                                           | Bit5           | Bit4         | Bit3       | Bit2          | Bit1         | Bit0            | _                 |  |  |  |

|                       |                                                                                                |                |              |            |               |              | SFR Address     | s: 0xB1           |  |  |  |

|                       |                                                                                                |                |              |            |               |              | SFR Page        | e: All Pages      |  |  |  |

| Bits 7–6 <sup>.</sup> | Reserved.                                                                                      |                |              |            |               |              |                 |                   |  |  |  |

|                       | COBANK: Co                                                                                     | onstant Oper   | rations Bank | Select     |               |              |                 |                   |  |  |  |

| 5100 1                | These bits se                                                                                  | •              |              |            | urina consta  | nt operatio  | ns (MOVC ar     | nd Flash          |  |  |  |

|                       | MOVX) involv                                                                                   |                |              | •          | •             | •            | •               |                   |  |  |  |

|                       | Scratchpad n                                                                                   | •              |              |            |               | •            |                 | 0                 |  |  |  |

|                       | 00: Constant                                                                                   |                |              |            |               |              |                 | x0000 to          |  |  |  |

|                       | 0x7FFF).                                                                                       |                | -            |            |               |              |                 |                   |  |  |  |

|                       | 01: Constant                                                                                   | •              | •            |            |               |              |                 |                   |  |  |  |

|                       | 10: Constant                                                                                   |                |              |            |               |              |                 |                   |  |  |  |

|                       | 11: Constant                                                                                   | Operations     | Target Bank  | 3.         |               |              |                 |                   |  |  |  |

|                       | Reserved.                                                                                      |                |              |            |               |              |                 |                   |  |  |  |

| Bits 1–0:             | IFBANK: Inst                                                                                   |                | •            |            |               |              |                 | 0.0000.0          |  |  |  |

|                       | These bits se                                                                                  |                |              |            |               |              |                 | S 0X8000 to       |  |  |  |

|                       | 0xFFFF. The                                                                                    |                |              |            |               |              |                 | 00 to             |  |  |  |

|                       | 00: Instructions Fetch From Bank 0 (note that Bank 0 is also mapped between 0x0000 to 0x7FFF). |                |              |            |               |              |                 |                   |  |  |  |

|                       | 01: Instructions Fetch From Bank 1.                                                            |                |              |            |               |              |                 |                   |  |  |  |

|                       | 10: Instructio                                                                                 |                |              |            |               |              |                 |                   |  |  |  |

|                       | 11: Instruction                                                                                | ns Fetch Fro   | om Bank 3.   |            |               |              |                 |                   |  |  |  |

|                       |                                                                                                |                |              |            |               |              |                 |                   |  |  |  |

|                       | n the C8051F1                                                                                  |                |              | FBANK bits | should both r | emain set to | o the default s | etting of '01' to |  |  |  |

| er                    | nsure proper de                                                                                | evice function | ality.       |            |               |              |                 |                   |  |  |  |

|                       |                                                                                                |                |              |            |               |              |                 |                   |  |  |  |

| Internal<br>Address | IFBANK = 0 | IFBANK = 1 | IFBANK = 2 | IFBANK = 3 |

|---------------------|------------|------------|------------|------------|

| 0xFFFF<br>0x8000    | Bank 0     | Bank 1     | Bank 2     | Bank 3     |

| 0x7FFF<br>0x0000    | Bank 0     | Bank 0     | Bank 0     | Bank 0     |

## Figure 11.3. Address Memory Map for Instruction Fetches (128 kB Flash Only)

| R/W   | R/W                                                                                                                                          | R/W         | R/W          | R/W                 | R/W          | R/W   | R/W         | Reset Value  |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|---------------------|--------------|-------|-------------|--------------|--|--|--|--|--|

| -     | PS1                                                                                                                                          | -           | PADC2        | PWADC2              | PT4          | PADC0 | PT3         | 0000000      |  |  |  |  |  |

| Bit7  | Bit6                                                                                                                                         | Bit5        | Bit4         | Bit3                | Bit2         | Bit1  | Bit0        |              |  |  |  |  |  |

|       |                                                                                                                                              |             |              |                     |              |       | SFR Address |              |  |  |  |  |  |

|       |                                                                                                                                              |             |              |                     |              |       | SFR Page    | e: All Pages |  |  |  |  |  |

| Bit7: | UNUSED. R                                                                                                                                    | ead = 0b    | Nrite = don  | 't care             |              |       |             |              |  |  |  |  |  |

| Bit6: | ES1: UART1                                                                                                                                   |             |              |                     |              |       |             |              |  |  |  |  |  |

|       |                                                                                                                                              |             |              | RT1 interrupt.      |              |       |             |              |  |  |  |  |  |

|       | 0: UART1 in                                                                                                                                  |             |              |                     |              |       |             |              |  |  |  |  |  |

|       | 1: UART1 in                                                                                                                                  | •           |              | •                   |              |       |             |              |  |  |  |  |  |

| Bit5: | UNUSED. R                                                                                                                                    | •           | • •          |                     |              |       |             |              |  |  |  |  |  |

| Bit4: |                                                                                                                                              |             |              | Interrupt Pri       | oritv Contr  | ol.   |             |              |  |  |  |  |  |

|       |                                                                                                                                              |             |              | 2 End of Co         |              |       |             |              |  |  |  |  |  |

|       |                                                                                                                                              |             |              |                     |              |       |             |              |  |  |  |  |  |

|       | <ul><li>0: ADC2 End of Conversion interrupt set to low priority.</li><li>1: ADC2 End of Conversion interrupt set to high priority.</li></ul> |             |              |                     |              |       |             |              |  |  |  |  |  |

| Bit3: | PWADC2: ADC2 Window Compare Interrupt Priority Control.                                                                                      |             |              |                     |              |       |             |              |  |  |  |  |  |

|       | This bit sets the priority of the ADC2 Window Compare interrupt.                                                                             |             |              |                     |              |       |             |              |  |  |  |  |  |

|       | 0: ADC2 Window Compare interrupt set to low priority.                                                                                        |             |              |                     |              |       |             |              |  |  |  |  |  |

|       |                                                                                                                                              |             |              | ,<br>pt set to high |              |       |             |              |  |  |  |  |  |

| Bit2: | PT4: Timer 4                                                                                                                                 |             |              |                     | 1 2          |       |             |              |  |  |  |  |  |

|       | This bit sets the priority of the Timer 4 interrupt.                                                                                         |             |              |                     |              |       |             |              |  |  |  |  |  |

|       | 0: Timer 4 interrupt set to low priority.                                                                                                    |             |              |                     |              |       |             |              |  |  |  |  |  |

|       | 1: Timer 4 interrupt set to high priority.                                                                                                   |             |              |                     |              |       |             |              |  |  |  |  |  |

| Bit1: | PADC0: ADC                                                                                                                                   | C0 End of ( | Conversion   | Interrupt Pric      | ority Contro | ol.   |             |              |  |  |  |  |  |

|       | This bit sets the priority of the ADC0 End of Conversion Interrupt.                                                                          |             |              |                     |              |       |             |              |  |  |  |  |  |

|       | 0: ADC0 End of Conversion interrupt set to low priority.                                                                                     |             |              |                     |              |       |             |              |  |  |  |  |  |

|       | 1: ADC0 End of Conversion interrupt set to high priority.                                                                                    |             |              |                     |              |       |             |              |  |  |  |  |  |

| Bit0: | PT3: Timer 3                                                                                                                                 |             |              | •                   |              |       |             |              |  |  |  |  |  |

|       | This bit sets the priority of the Timer 3 interrupts.                                                                                        |             |              |                     |              |       |             |              |  |  |  |  |  |

|       | 0: Timer 3 in                                                                                                                                | terrupt set | to low prior | ity.                |              |       |             |              |  |  |  |  |  |

|       | 1: Timer 3 in                                                                                                                                | terrupt set | to high pric | ority.              |              |       |             |              |  |  |  |  |  |

|       |                                                                                                                                              | -           |              | -                   |              |       |             |              |  |  |  |  |  |

## SFR Definition 11.17. EIP2: Extended Interrupt Priority 2

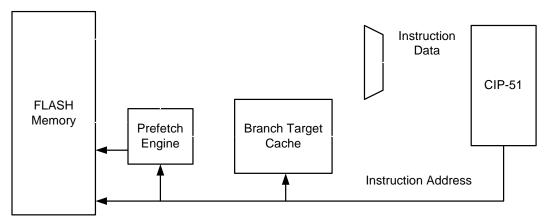

## 16. Branch Target Cache

The C8051F12x and C8051F13x device families incorporate a 63x4 byte branch target cache with a 4-byte prefetch engine. Because the access time of the Flash memory is 40 Flashns, and the minimum instruction time is 10ns (C8051F120/1/2/3 and C8051F130/1/2/3) or 20 ns (C8051F124/5/6/7), the branch target cache and prefetch engine are necessary for full-speed code execution. Instructions are read from Flash memory four bytes at a time by the prefetch engine, and given to the CIP-51 processor core to execute. When running linear code (code without any jumps or branches), the prefetch engine alone allows instructions to be executed at full speed. When a code branch occurs, a search is performed for the branch target (destination address) in the cache. If the branch target information is found in the cache (called a "cache hit"), the instruction data is read from the cache and immediately returned to the CIP-51 with no delay in code execution. If the branch target is not found in the cache (called a "cache miss"), the processor may be stalled for up to four clock cycles while the next set of four instructions is retrieved from Flash memory. Each time a cache miss occurs, the requested instruction data is written to the cache if allowed by the current cache settings. A data flow diagram of the interaction between the CIP-51 and the Branch Target Cache and Prefetch Engine is shown in Figure 16.1.

Figure 16.1. Branch Target Cache Data Flow

## 16.1. Cache and Prefetch Operation

The branch target cache maintains two sets of memory locations: "slots" and "tags". A slot is where the cached instruction data from Flash is stored. Each slot holds four consecutive code bytes. A tag contains the 15 most significant bits of the corresponding Flash address for each four-byte slot. Thus, instruction data is always cached along four-byte boundaries in code space. A tag also contains a "valid bit", which indicates whether a cache location contains valid instruction data. A special cache location (called the linear tag and slot), is reserved for use by the prefetch engine. The cache organization is shown in Figure 16.2. Each time a Flash read is requested, the address is compared with all valid cache tag locations (including the linear tag). If any of the tag locations match the requested address, the data from that slot is immediately provided to the CIP-51. If the requested address matches a location that is currently being read by the prefetch engine, the CIP-51 will be stalled until the read is complete. If a match is not found, the current prefetch operation is abandoned, and a new prefetch operation is initiated for the requested instruction data. When the prefetch engine begins reading the next four-byte word from Flash memory. If the newly-fetched data also meets the criteria necessary to be cached, it will be written to the cache in the slot indicated by the current replacement algorithm.

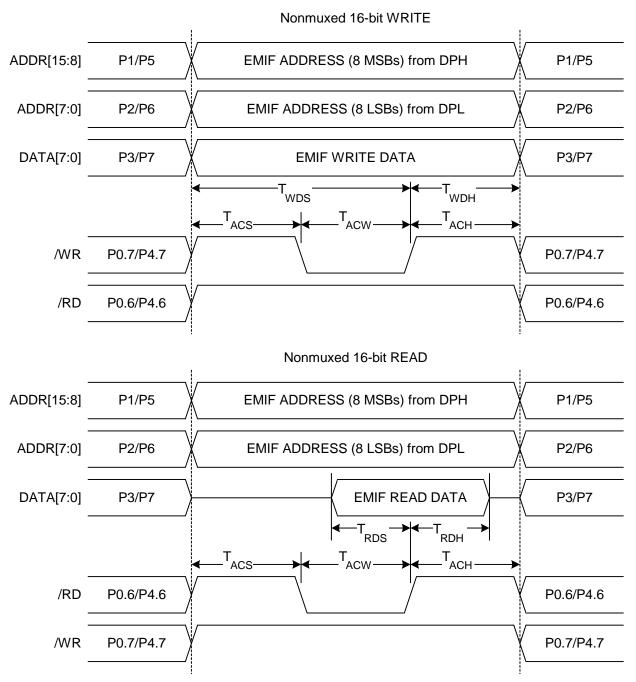

### 17.6.1. Non-multiplexed Mode

17.6.1.1.16-bit MOVX: EMI0CF[4:2] = '101', '110', or '111'

Figure 17.4. Non-multiplexed 16-bit MOVX Timing

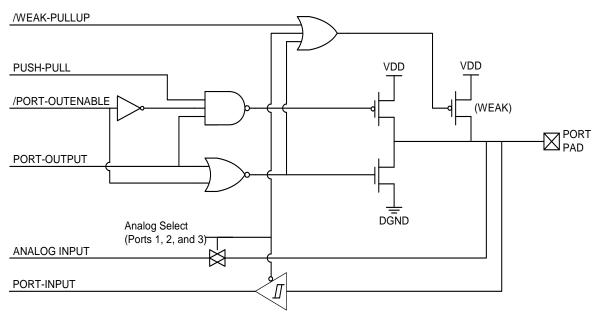

## **18. Port Input/Output**

The devices are fully integrated mixed-signal System on a Chip MCUs with 64 digital I/O pins (100-pin TQFP packaging) or 32 digital I/O pins (64-pin TQFP packaging), organized as 8-bit Ports. All ports are both bit- and byte-addressable through their corresponding Port Data registers. All Port pins are 5 V-toler- ant, and all support configurable Open-Drain or Push-Pull output modes and weak pullups. A block dia-gram of the Port I/O cell is shown in Figure 18.1. Complete Electrical Specifications for the Port I/O pins are given in Table 18.1.

Figure 18.1. Port I/O Cell Block Diagram

| R/W      | R/W                                                                                                                             | R/W                                                            | R/W                                       | R/W        | R/W         | R/W         | R/W                     | Reset Value        |

|----------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------|------------|-------------|-------------|-------------------------|--------------------|

| P7.7     | P7.6                                                                                                                            | P7.5                                                           | P7.4                                      | P7.3       | P7.2        | P7.1        | P7.0                    | 11111111           |

| Bit7     | Bit6                                                                                                                            | Bit5                                                           | Bit4                                      | Bit3       | Bit2        | Bit1        | Bit0                    | Bit<br>Addressable |

|          |                                                                                                                                 |                                                                |                                           |            |             |             | SFR Address<br>SFR Page |                    |

| Bits7–0: | P7.[7:0]: Port<br>Write - Outpu<br>0: Logic Low<br>1: Logic High<br>18.20.<br>Read - Return<br>0: P7.n pin is<br>1: P7.n pin is | t appears<br>Output.<br>Output (C<br>ns states o<br>logic low. | on I/O pins<br>Open-Drain<br>of I/O pins. |            | ding P7MD   | OUT bit = 0 | )). See SFF             | R Definition       |

| Note:    | P7.[7:0] can I<br>mode, or as I<br>Interface and<br>Interface.                                                                  | D[7:0] in N                                                    | on-multiple                               | xed mode). | See Section | on "17. Ext | ernal Data              |                    |

## SFR Definition 18.19. P7: Port7 Data

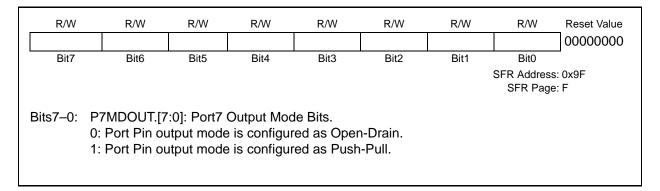

## SFR Definition 18.20. P7MDOUT: Port7 Output Mode

| R/W                                                                                                                                                                                                                                                                                                          | R/W                                                                                                                                                                                      | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|-------------|--|--|--|

| SLV6                                                                                                                                                                                                                                                                                                         | SLV5                                                                                                                                                                                     | SLV4 | SLV3 | SLV2 | SLV1 | SLV0 | GC   | 0000000     |  |  |  |

| Bit7                                                                                                                                                                                                                                                                                                         | Bit6                                                                                                                                                                                     | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |             |  |  |  |

|                                                                                                                                                                                                                                                                                                              | SFR Address: 0xC3<br>SFR Page: 0                                                                                                                                                         |      |      |      |      |      |      |             |  |  |  |

| Bits7–1: SLV6–SLV0: SMBus0 Slave Address.<br>These bits are loaded with the 7-bit slave address to which SMBus0 will respond when oper-<br>ating as a slave transmitter or slave receiver. SLV6 is the most significant bit of the address<br>and corresponds to the first bit of the address byte received. |                                                                                                                                                                                          |      |      |      |      |      |      |             |  |  |  |

| Bit0:                                                                                                                                                                                                                                                                                                        | GC: General Call Address Enable.<br>This bit is used to enable general call address (0x00) recognition.<br>0: General call address is ignored.<br>1: General call address is recognized. |      |      |      |      |      |      |             |  |  |  |

#### 19.4.5. Status Register

The SMB0STA Status register holds an 8-bit status code indicating the current state of the SMBus0 interface. There are 28 possible SMBus0 states, each with a corresponding unique status code. The five most significant bits of the status code vary while the three least-significant bits of a valid status code are fixed at zero when SI = '1'. Therefore, all possible status codes are multiples of eight. This facilitates the use of status codes in software as an index used to branch to appropriate service routines (allowing 8 bytes of code to service the state or jump to a more extensive service routine).

For the purposes of user software, the contents of the SMB0STA register is only defined when the SI flag is logic 1. Software should never write to the SMB0STA register; doing so will yield indeterminate results. The 28 SMBus0 states, along with their corresponding status codes, are given in Table 1.1.

| R/W                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W                         | R/W  | R/W           | R/W          | R/W       | R/W        | R/W                       | Reset Value |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------|---------------|--------------|-----------|------------|---------------------------|-------------|

| STA7                                                                                                                                                                                                                                                                                                                                                                                                                                    | STA6                        | STA5 | STA4          | STA3         | STA2      | STA1       | STA0                      | 11111000    |

| Bit7                                                                                                                                                                                                                                                                                                                                                                                                                                    | Bit6                        | Bit5 | Bit4          | Bit3         | Bit2      | Bit1       | Bit0                      | -           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             |      |               |              |           |            | SFR Address:<br>SFR Page: |             |

| Bits7–3: STA7–STA3: SMBus0 Status Code.<br>These bits contain the SMBus0 Status Code. There are 28 possible status codes; each sta-<br>tus code corresponds to a single SMBus state. A valid status code is present in SMB0STA<br>when the SI flag (SMB0CN.3) is set to logic 1. The content of SMB0STA is not defined when<br>the SI flag is logic 0. Writing to the SMB0STA register at any time will yield indeterminate<br>results. |                             |      |               |              |           |            |                           |             |

| Bits2–0:                                                                                                                                                                                                                                                                                                                                                                                                                                | STA2–STA0<br>the SI flag is |      | least signifi | cant bits of | SMB0STA : | are always | read as log               | ic 0 when   |

### SFR Definition 19.5. SMB0STA: SMBus0 Status

## 20.2. SPI0 Master Mode Operation

A SPI master device initiates all data transfers on a SPI bus. SPI0 is placed in master mode by setting the Master Enable flag (MSTEN, SPI0CN.6). Writing a byte of data to the SPI0 data register (SPI0DAT) when in master mode writes to the transmit buffer. If the SPI shift register is empty, the byte in the transmit buffer is moved to the shift register, and a data transfer begins. The SPI0 master immediately shifts out the data serially on the MOSI line while providing the serial clock on SCK. The SPIF (SPI0CN.7) flag is set to logic 1 at the end of the transfer. If interrupts are enabled, an interrupt request is generated when the SPIF flag is set. While the SPI0 master transfers data to a slave on the MOSI line, the addressed SPI slave device simultaneously transfers the contents of its shift register to the SPI master on the MISO line in a full-duplex operation. Therefore, the SPIF flag serves as both a transmit-complete and receive-data-ready flag. The data byte received from the slave is transferred MSB-first into the master's shift register. When a byte is fully shifted into the register, it is moved to the receive buffer where it can be read by the processor by reading SPI0DAT.

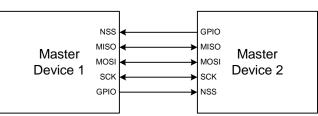

When configured as a master, SPI0 can operate in one of three different modes: multi-master mode, 3-wire single-master mode, and 4-wire single-master mode. The default, multi-master mode is active when NSS-MD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In this mode, NSS is an input to the device, and is used to disable the master SPI0 when another master is accessing the bus. When NSS is pulled low in this mode, MSTEN (SPI0CN.6) and SPIEN (SPI0CN.0) are set to 0 to disable the SPI master device, and a Mode Fault is generated (MODF, SPI0CN.5 = 1). Mode Fault will generate an interrupt if enabled. SPI0 must be manually re-enabled in software under these circumstances. In multi-master systems, devices will typically default to being slave devices while they are not acting as the system master device. In multi-master mode, slave devices can be addressed individually (if needed) using general-purpose I/O pins. Figure 20.2 shows a connection diagram between two master devices in multiple-master mode.

3-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. In this mode, NSS is not used, and is not mapped to an external port pin through the crossbar. Any slave devices that must be addressed in this mode should be selected using general-purpose I/O pins. Figure 20.3 shows a connection diagram between a master device in 3-wire master mode and a slave device.

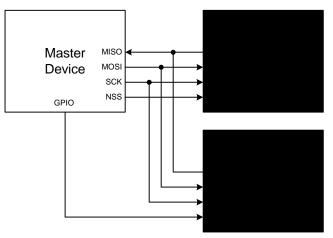

4-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 1. In this mode, NSS is configured as an output pin, and can be used as a slave-select signal for a single SPI device. In this mode, the output value of NSS is controlled (in software) with the bit NSSMD0 (SPI0CN.2). Additional slave devices can be addressed using general-purpose I/O pins. Figure 20.4 shows a connection diagram for a master device in 4-wire master mode and two slave devices.

Figure 20.2. Multiple-Master Mode Connection Diagram

Figure 20.3. 3-Wire Single Master and Slave Mode Connection Diagram

Figure 20.4. 4-Wire Single Master and Slave Mode Connection Diagram

### 21.1. UART0 Operational Modes

UART0 provides four operating modes (one synchronous and three asynchronous) selected by setting configuration bits in the SCON0 register. These four modes offer different baud rates and communication protocols. The four modes are summarized in Table 21.1.

| Mode | Synchronization | Baud Clock                   | Data Bits | Start/Stop Bits |

|------|-----------------|------------------------------|-----------|-----------------|

| 0    | Synchronous     | SYSCLK / 12                  | 8         | None            |

| 1    | Asynchronous    | Timer 1, 2, 3, or 4 Overflow | 8         | 1 Start, 1 Stop |

| 2    | Asynchronous    | SYSCLK / 32 or SYSCLK / 64   | 9         | 1 Start, 1 Stop |

| 3    | Asynchronous    | Timer 1, 2, 3, or 4 Overflow | 9         | 1 Start, 1 Stop |

### Table 21.1. UART0 Modes

#### 21.1.1. Mode 0: Synchronous Mode

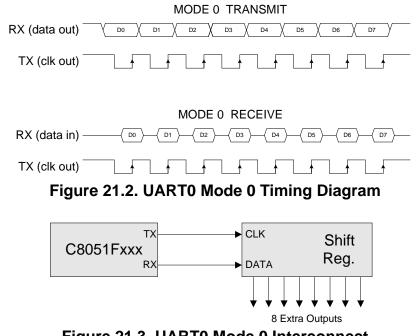

Mode 0 provides synchronous, half-duplex communication. Serial data is transmitted and received on the RX0 pin. The TX0 pin provides the shift clock for both transmit and receive. The MCU must be the master since it generates the shift clock for transmission in both directions (see the interconnect diagram in Figure 21.3).

Data transmission begins when an instruction writes a data byte to the SBUF0 register. Eight data bits are transferred LSB first (see the timing diagram in Figure 21.2), and the TIO Transmit Interrupt Flag (SCON0.1) is set at the end of the eighth bit time. Data reception begins when the REN0 Receive Enable bit (SCON0.4) is set to logic 1 and the RI0 Receive Interrupt Flag (SCON0.0) is cleared. One cycle after the eighth bit is shifted in, the RI0 flag is set and reception stops until software clears the RI0 bit. An interrupt will occur if enabled when either TI0 or RI0 are set.

The Mode 0 baud rate is SYSCLK / 12. RX0 is forced to open-drain in Mode 0, and an external pullup will typically be required.

|                              | Frequency: 50.0 MHz  |                                  |                       |                                     |      |                                  |  |  |

|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------|------|----------------------------------|--|--|

| Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload<br>Value (hex) |  |  |

| 230400                       | 0.45%                | 218                              | SYSCLK                | XX                                  | 1    | 0x93                             |  |  |

| 115200                       | -0.01%               | 434                              | SYSCLK                | XX                                  | 1    | 0x27                             |  |  |

| 57600                        | 0.45%                | 872                              | SYSCLK/4              | 01                                  | 0    | 0x93                             |  |  |

| 28800                        | -0.01%               | 1736                             | SYSCLK / 4            | 01                                  | 0    | 0x27                             |  |  |

| 14400                        | 0.22%                | 3480                             | SYSCLK / 12           | 00                                  | 0    | 0x6F                             |  |  |

| 9600                         | -0.01%               | 5208                             | SYSCLK / 12           | 00                                  | 0    | 0x27                             |  |  |

| 2400                         | -0.01%               | 20832                            | SYSCLK / 48           | 10                                  | 0    | 0x27                             |  |  |

## Table 22.4. Times Cattings for Standard David Dates Using the DL

X = Don't care

\*Note: SCA1-SCA0 and T1M bit definitions can be found in Section 23.1.

| Table 22.5. | Timer Settings for Standard Baud Rates Using the PLL |

|-------------|------------------------------------------------------|

|             | Frequency: 100.0 MHz                                 |

| Frequency: 100.0 MHz         |                      |                                  |                       |                                     |      |                                  |

|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------|------|----------------------------------|

| Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload<br>Value (hex) |

| 230400                       | -0.01%               | 434                              | SYSCLK                | XX                                  | 1    | 0x27                             |

| 115200                       | 0.45%                | 872                              | SYSCLK/4              | 01                                  | 0    | 0x93                             |

| 57600                        | -0.01%               | 1736                             | SYSCLK/4              | 01                                  | 0    | 0x27                             |

| 28800                        | 0.22%                | 3480                             | SYSCLK / 12           | 00                                  | 0    | 0x6F                             |

| 14400                        | -0.47%               | 6912                             | SYSCLK / 48           | 10                                  | 0    | 0xB8                             |

| 9600                         | 0.45%                | 10464                            | SYSCLK / 48           | 10                                  | 0    | 0x93                             |

X = Don't care

\*Note: SCA1-SCA0 and T1M bit definitions can be found in Section 23.1.

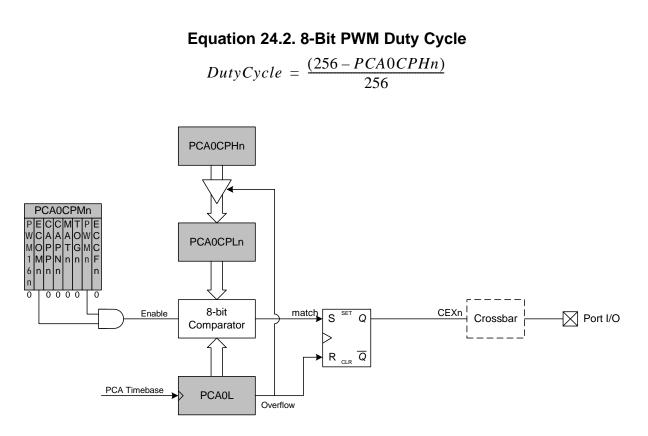

#### 24.2.5. 8-Bit Pulse Width Modulator Mode

Each module can be used independently to generate pulse width modulated (PWM) outputs on its associated CEXn pin. The frequency of the output is dependent on the timebase for the PCA0 counter/timer. The duty cycle of the PWM output signal is varied using the module's PCA0CPLn capture/compare register. When the value in the low byte of the PCA0 counter/timer (PCA0L) is equal to the value in PCA0CPLn, the output on the CEXn pin will be high. When the count value in PCA0L overflows, the CEXn output will be low (see Figure 24.8). Also, when the counter/timer low byte (PCA0L) overflows from 0xFF to 0x00, PCA0CPLn is reloaded automatically with the value stored in the counter/timer's high byte (PCA0H) without software intervention. Setting the ECOMn and PWMn bits in the PCA0CPMn register enables 8-Bit Pulse Width Modulator mode. The duty cycle for 8-Bit PWM Mode is given by Equation 24.2.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

Figure 24.8. PCA 8-Bit PWM Mode Diagram