# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | 68000                                                                   |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 16.67MHz                                                                |

| Co-Processors/DSP               | -                                                                       |

| RAM Controllers                 | -                                                                       |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | -                                                                       |

| SATA                            | -                                                                       |

| USB                             | -                                                                       |

| Voltage - I/O                   | 5.0V                                                                    |

| Operating Temperature           | -55°C ~ 125°C (TC)                                                      |

| Security Features               | -                                                                       |

| Package / Case                  | 132-BCQFP                                                               |

| Supplier Device Package         | 132-CQFP (24.13x24.13)                                                  |

| Purchase URL                    | https://www.e-xfl.com/product-detail/microchip-technology/ts68020mf1-16 |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The micromachine consists of an execution unit, nanorom and microrom storage, an instruction decoder, an instruction pipe, and associated control sections. The execution unit consists of an address section, an operand address section, and a data section. Microcode control is provided by a modified two-level store of microrom and nanorom. Programmed logical arrays (PLAs) are used to provide instruction decode and sequencing information. The instruction pipe and other individual control sections provide the secondary decode of instructions and generated the actual control signals that result in the decoding and interpretation of nanorom and micorom information.

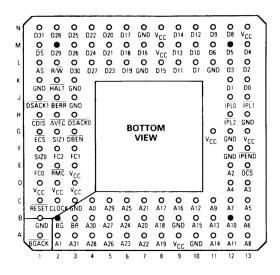

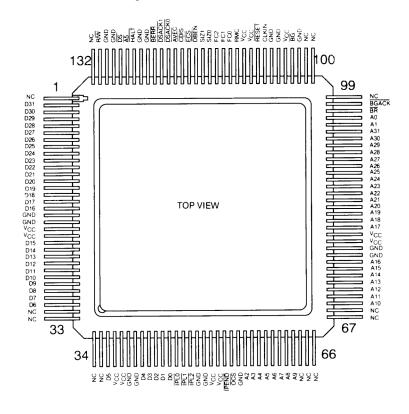

Figure 3. CQFP Terminal Designation

#### Figure 4. Functional Signal Groups

## **Signal Description**

Figure 4 illustrates the functional signal groups and Table 1 lists the signals and their function.

The  $V_{CC}$  and GND pins are separated into four groups to provide individual power supply connections for the address bus buffers, data bus buffers, and all other output buffers and internal logic.

| Group       | V <sub>cc</sub>      | GND              |

|-------------|----------------------|------------------|

| Address Bus | A9, D3               | A10, B9,C3, F12  |

| Data Bus    | M8, N8, N13          | L7, L11, N7, K3  |

| Logic       | D1, D2, E3, G11, G13 | G12, H13, J3, K1 |

| Clock       | —                    | В1               |

4

## **Electrical Characteristics**

#### Table 2. Absolute Maximum Ratings

| Symbol                                  | Parameter             | Test Conditions            | Min  | Max  | Unit |

|-----------------------------------------|-----------------------|----------------------------|------|------|------|

| V <sub>CC</sub>                         | Supply Voltage        |                            | -0.3 | +7.0 | V    |

| VI                                      | Input Voltage         |                            | -0.5 | +7.0 | V    |

| P <sub>dmax</sub> Max Power Dissipation | May Dawar Dissingtion | T <sub>case</sub> = -55°C  |      | 2.0  | W    |

|                                         | Max Power Dissipation | T <sub>case</sub> = +125°C |      | 1.9  | W    |

| T <sub>case</sub> Operating Temperature |                       | M Suffix                   | -55  | +125 | °C   |

|                                         | Operating Temperature | V Suffix                   | -40  | +85  | °C   |

| T <sub>stg</sub>                        | Storage Temperature   |                            | -55  | +150 | °C   |

| T <sub>leads</sub>                      | Lead Temperature      | Max 5 Sec. Soldering       |      | +270 | °C   |

#### Table 3. Recommended Condition of Use

#### Unless otherwise stated, all voltages are referenced to the reference terminal (see Table 1).

| Symbol                                | Parameter                             |          | Min  | Max   | Unit |

|---------------------------------------|---------------------------------------|----------|------|-------|------|

| V <sub>CC</sub>                       | Supply Voltage                        |          | 4.5  | 5.5   | V    |

| V <sub>IL</sub>                       | Low Level Input Voltage               |          | -0.3 | 0.5   | V    |

| V <sub>IH</sub>                       | High Level Input Voltage              |          | 2.4  | 5.25  | V    |

| T <sub>case</sub>                     | Operating Temperature                 |          | -55  | +125  | °C   |

| RL                                    | Value of Output Load Resistance       |          | (1)  |       | Ω    |

| CL                                    | Output Loading Capacitance            |          |      | (1)   | pF   |

|                                       |                                       | 68020-16 |      | 5     |      |

| t <sub>r</sub> (c)–t <sub>f</sub> (c) | Clock Rise Time (See Figure 5)        | 68020-20 |      | 5     | ns   |

|                                       |                                       | 68020-25 |      | 4     |      |

|                                       |                                       | 68020-16 | 8    | 16.67 |      |

| f <sub>c</sub>                        | Clock Frequency (See Figure 5)        | 68020-20 | 12.5 | 20    | MHz  |

|                                       |                                       | 68020-25 | 12.5 | 25    |      |

|                                       |                                       | 68020-16 | 60   | 125   |      |

| t <sub>cyc</sub>                      | Cycle Time (see Figure 5)             | 68020-20 | 50   | 80    | ns   |

|                                       |                                       | 68020-25 | 40   | 80    |      |

|                                       |                                       | 68020-16 | 24   | 95    |      |

| t <sub>w</sub> (CL)                   | Clock Pulse Width Low (See Figure 5)  | 68020-20 | 20   | 54    | ns   |

|                                       |                                       | 68020-25 | 19   | 61    | 1    |

|                                       |                                       | 68020-16 | 24   | 95    |      |

| t <sub>w</sub> (CH)                   | Clock Pulse Width High (See Figure 5) | 68020-20 | 20   | 50    | ns   |

|                                       |                                       | 68020-25 | 19   | 61    | 1    |

Note: 1. Load network number 1 to 4 as specified (Table 7) gives the maximum loading of the relevant output.

The total thermal resistance of a package  $(\theta_{JA})$  can be separated into two components,  $\theta_{JC}$  and  $\theta_{CA}$ , representing the barrier to heat flow from the semiconductor junction to the package (case), surface  $(\theta_{JC})$  and from the case to the outside ambient  $(\theta_{CA})$ . These terms are related by the equation:

$\theta_{JA} = \theta_{JC} = \theta_{CA}$

(4)

$\theta_{JC}$  is device related and cannot be influenced by the user. However,  $\theta_{CA}$  is user dependent and can be minimized by such thermal management techniques as heat sinks, ambient air cooling and thermal convection. Thus, good thermal management on the part of the user can significantly reduce  $\theta_{CA}$  so that  $\theta_{JA}$  approximately equals  $\theta_{JC}$ . Substitution of  $\theta_{JC}$  for  $\theta_{JA}$  in equation (1) will result in a lower semiconductor junction temperature.

Mechanical andThe microcircuits shall meet all mechanical environmental requirements of MIL-STD-<br/>883 for class B devices.

Marking

The document where are defined the marking are identified in the related reference documents. Each microcircuit are legible and permanently marked with the following information as minimum:

- ATMEL Logo

- Manufacturer's Part Number

- Class B Identification

- Date-code of Inspection Lot

- ESD Identifier if Available

- Country of Manufacturing

| Quality Conformance<br>Inspection |                                                                                                                                                                                                  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DESC/MIL-STD-883                  | Is in accordance with MIL-M-38510 and method 5005 of MIL-STD-883. Group A and B inspections are performed on each production lot. Group C and D inspections are performed on a periodical basis. |

| Electrical<br>Characteristics     |                                                                                                                                                                                                  |

| General Requirements              | All static and dynamic electrical characteristics specified and the relevant measurement conditions are given below.                                                                             |

|                                   | (last issue on request to our marketing services).                                                                                                                                               |

|                                   | Table 5: Static electrical characteristics for all electrical variants.                                                                                                                          |

|                                   | Table 6: Dynamic electrical characteristics for 68020-16 (16.67 MHz), 68020-20 (20 MHz) and 68020-25 (25 MHz).                                                                                   |

|                                   | For static characteristics, test methods refer to "Test Conditions Specific to the Device" on page 14 hereafter of this specification (Table 7).                                                 |

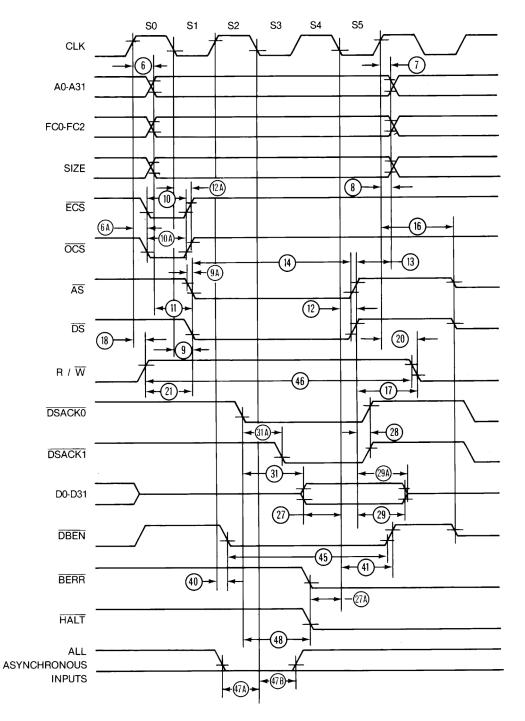

#### **Time Definitions**

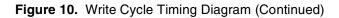

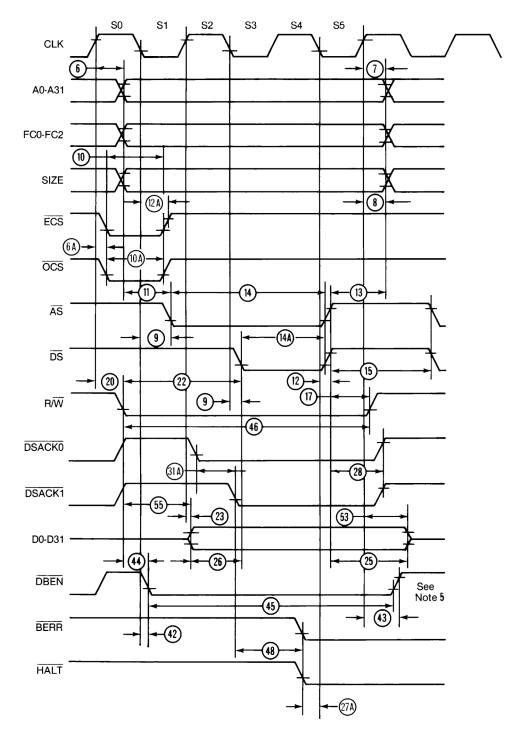

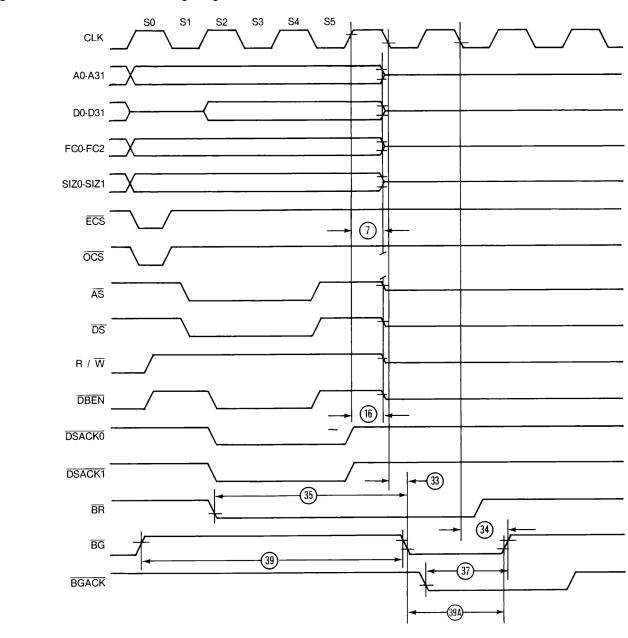

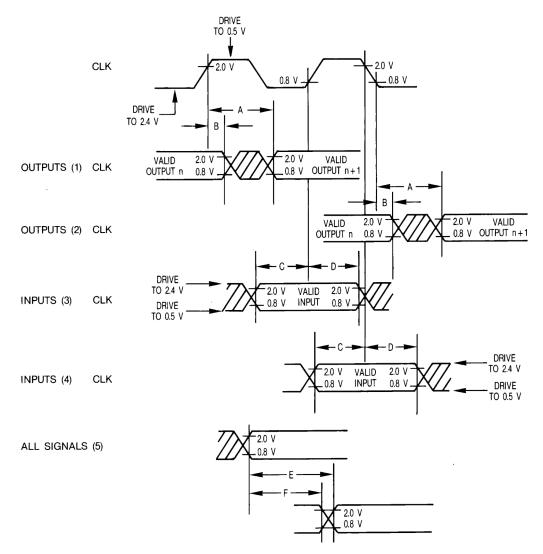

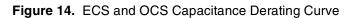

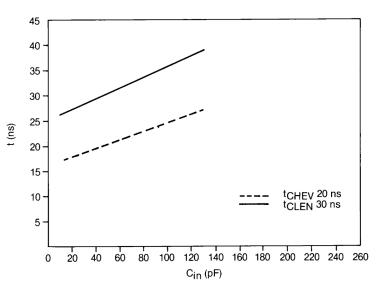

The times specified in Table 6 as dynamic characteristics are defined in Figure 9 below, by a reference number given the column "interval  $N^{\circ}$ " of the tables together with the relevant figure number.

Note: Timing measurements are referenced to and from a low voltage of 0.8V and a high voltage of 2.0V, unless otherwise noted. The voltage swing through this range should start outside and pass through the range such that the rise or fall will be linear between 0.8V and 2.0V.

Note: Timing measurements are referenced to and from a low voltage of 0.8V and a high voltage of 2.0V, unless otherwise noted. The voltage swing thorough this range should start outside and pass through the range such that the rise or fall will be linear between 0.8V and 2.0V.

Figure 11. Bus Arbitration Timing Diagram

Note: Timing measurements are referenced to and from a low voltage of 0.8V and a high voltage of 2.0V, unless otherwise noted. The voltage swing thorough this range should start outside and pass through the range such that the rise or fall will be linear between 0.8V and 2.0V.

#### Legend:

A) Maximum Output Delay Specification

- B) Minimum Output Hold Time

- C) Minimum Input Setup Time Specification

- D) Minimum Input Hold Time Specification

- E) Signal Valid to Signal Valid Specification (Maximum or Minimum)

- F) Signal Valid to Signal Invalid Specification (Maximum or Minimum)

- Notes: 1. This output timing is applicable to all parameters specified relative to the rising edge of the clock.

- 2. This out put timing is applicable to all parameters specified relative to the falling edge of the clock.

- 3. This input timing is applicable to all parameters specified relative to the falling edge of the clock.

- 4. This input timing is applicable to all parameters specified relative to the falling edge of the clock.

- 5. This timing is applicable to all parameters specified relative to the assertion/negation of another signal.

**TS68020**

Figure 15. R/W, FC, SIZ0-SIZ1, and RMC Capacitance Derating Curve

The TS68000 Family processors distinguish address spaces as supervisor / used and program/data. These four combinations are specified by the function code pins (FC0/FC1/FC2) during bus cycles, indication the particular address space. Using the function codes, the memory sub-system can distinguish between authorized access (supervisor mode is privileged access) and unauthorized access (user mode may not have access to supervisor program or data areas). To support the full privileges of the supervisor, the alternate function code registers allow the supervisor to specify an access to user program or data areas by preloading the SFC/DFC registers appropriately.

The cache registers (control — CACR, address — CAAR) allow software manipulation of the on-chip instruction cache. Control and status accesses to the instruction cache are provided by the cache control register (CACR), while the cache address register (CAAR) holds the address for those cache control functions that require an address.

#### Table 8. TS68020 Addressing Modes (Continued)

| Addressing Modes | Syntax |

|------------------|--------|

| Absolute         |        |

| Absolute Short   | xxx.W  |

| Absolute Long    | xxx.L  |

| Immediate        | =data  |

- Notes: 1. Dn = Data Register, D0-D7.

- 2. An = Address Register, A0-A7.

- d<sub>8</sub>, d<sub>16</sub> = A twos-complement, or sign—extended displacement; added as part of the effective calculation; size is 8 (d<sub>8</sub>) or 16 (d<sub>16</sub>) bits; when omitted assemblers use a value of zero.

- 4. Xn = Address or data register used as an index register; form is Xn, SIZE\*SCALE, where SIZE is.W or.L (indicates index register size) and SCALE is 1, 2, 4, or 8 (index register is multiplied by SCALE); use of SIZE and/or SCALE is optional.

- 5. bd = A two-complement base displacement; when present, size can be 16- or 32-bit.

- od = Outer displacement, added as part of effective address calculation after any memory indirection; use is optional with a size of 16- or 32-bit.

- 7. PC = Program Counter.

- 8. (data) = Immediate value of 8, 16 or 32 bits.

- 9. () = Effective Address.

- 10. [] = Use as indirect address to long word address.

| Mnemonic    | Description                                     |

|-------------|-------------------------------------------------|

|             |                                                 |

| CALLM       | Call Module                                     |

| CAS         | Compare and Swap Operands                       |

| CAS2        | Compare and Swap Operands                       |

| CHK         | Check Register Against Bound                    |

| CHK2        | Check Register Against Upper and Lower Bounds   |

| CLR         | Clear                                           |

| CMP         |                                                 |

| CMPA        | Compare                                         |

| CMPI        | Compare Address                                 |

|             | Compare Immediate                               |

|             | Compare Memory to Memory                        |

| CMP2        | Compare Register Against Upper and Lower Bounds |

| DBcc        | Test Condition, Decrement and Branch            |

|             | Signed Divide                                   |

| DIVS, DIVSL | Unsigned Divide                                 |

| DIVU, DIVUL |                                                 |

| EOR         | Logical Exclusive OR                            |

| EORI        | Logical Exclusive OR Immediate                  |

| EXG         | Exchange Registers                              |

| EXT, EXTB   | Sign Extend                                     |

| ILLEGAL     | Take Illegal Instruction Tape                   |

| JMP         | Jump                                            |

| JSR         | Jump to Subroutine                              |

| LEA         | Load Effective Address                          |

| LINK        | Link and Allocate                               |

| LSL, LSR    | Logical Shift Left and Right                    |

| MOVE        | Move                                            |

| MOVEA       | Move Address                                    |

| MOVE CCR    | Move Condition Code Register                    |

| MOVE SR     | Move Status Register                            |

| MOVE USP    | Move User Stack Pointer                         |

| MOVEC       | Move Control Register                           |

| MOVEM       | Move Multiple Registers                         |

| MOVEP       | Move Peripheral                                 |

| MOVEQ       | Move Quick                                      |

| MOVES       | Move Alternate Address Space                    |

| MULS        | Signed Multiply                                 |

| MULU        | Unsigned Multiply                               |

| NBCD        | Negate Decimal with Extend                      |

| NEG         | Negate                                          |

| NEGX        | Negate with Extend                              |

| NOP         | No Operation                                    |

|             |                                                 |

Logical Complement

T

NOT

| Table 9. | Instruction Set ( | (Continued) |

|----------|-------------------|-------------|

| Tuble 5. |                   |             |

| Mnemonic                  | Description                                       |  |  |  |

|---------------------------|---------------------------------------------------|--|--|--|

| OR                        | Logical Inclusive OR                              |  |  |  |

| ORI                       | Logical Inclusive OR Immediate                    |  |  |  |

| PACK                      | Pack BCD                                          |  |  |  |

| PEA                       | Push Effective Address                            |  |  |  |

| RESET                     | Reset External Devices                            |  |  |  |

| ROL, ROR                  | Rotate Left and Right                             |  |  |  |

| ROXL, ROXR                | Rotate with Extend Left and Right                 |  |  |  |

| RTD                       | Return and Deallocate                             |  |  |  |

| RTE                       | Return and Exception                              |  |  |  |

| RTM                       | Return from Module                                |  |  |  |

| RTR                       | Return and Restore Codes                          |  |  |  |

| RTS                       | Return from Subroutine                            |  |  |  |

| SBCD                      | Subtract Decimal with Extend                      |  |  |  |

| Scc                       | Set Conditionally                                 |  |  |  |

| STOP                      | Stop                                              |  |  |  |

| SUB                       | Subtract                                          |  |  |  |

| SUBA                      | Subtract Address                                  |  |  |  |

| SUBI                      | Subtract Immediate                                |  |  |  |

| SUBQ                      | Subtract Quick                                    |  |  |  |

| SUBX                      | Subtract with Extend                              |  |  |  |

| SWAP                      | Swap Register Words                               |  |  |  |

| TAS                       | Test Operand and Set                              |  |  |  |

| TRAP                      | Тгар                                              |  |  |  |

| TRAPcc                    | Trap Conditionally                                |  |  |  |

| TRAPV                     | Trap on Overflow                                  |  |  |  |

| TST                       | Test Operand                                      |  |  |  |

| UNLK                      | Unlink                                            |  |  |  |

| UNPK                      | Unpack BCD                                        |  |  |  |

| Co-processor Instructions |                                                   |  |  |  |

| срВСС                     |                                                   |  |  |  |

| cpDBcc                    | Branch Conditionally                              |  |  |  |

|                           | Test Co-processor Condition, Decrement and Branch |  |  |  |

| cpGEN                     | Co-processor General Instruction                  |  |  |  |

| cpRESTORE                 | Restore Internal State of Co-processor            |  |  |  |

|                           | Save Internal State of Co-processor               |  |  |  |

| cpSAVE                    | Set Conditionally                                 |  |  |  |

| cpScc                     | Trap Conditionally                                |  |  |  |

| cpTRAPcc                  |                                                   |  |  |  |

The TS68020 uses instruction continuation to support virtual memory. In order for the TS68020 to use instruction continuation, it stores its internal state on the supervisor stack when a bus cycle is terminated with a bus error signal. It then loads the program counter with the address of the virtual memory bus error handler from the exception vector table (entry number two) and resumes program execution to that new address. When the bus error exception handler routine has completed execution, an RTE instruction is executed which reloads the TS68020 with the internal state stored on the stack, reruns the faulted bus cycle (when required), and continues the suspended instruction.

Instruction continuation is crucial to the support of virtual I/O devices in memorymapped input/output systems. Since the registers of a virtual device may be simulated in the memory map, an access to such a register will cause a fault and the function of the register can be emulated by software.

Virtual Machine A typical use for a virtual machine system is the development of software, such as an operating system, for a new machine also under development and not yet available for programming use. In such a system, a governing operating system emulates the hardware of the prototype system and allows the new operating system to be executed and debugged as though it were running on the new hardware. Since the new operating system is controlled by the governing operating system, it is executed at a lower privilege level than the governing operating system. Thus, any attempts by the new operating system to use virtual resources that are not physically present (and should be emulated) are trapped to the governing system and handled by its software. In the TS68020, a virtual machine is fully supported by running the new operating system in the user mode. The governing operating system to access supervisor resources or execute privileged instructions will cause a trap to the governing operating system.

**Operand Transfer Mechanism** Though the TS68020 has a full 32-bit data bus, it offers the ability to automatically and dynamically downsize its bus to 8- or 16-bit if peripheral devices are unable to accommodate the entire 32-bit. This feature allows the programmer the ability to write code that is not bus-width specific. For example, long word (32-bit) accesses to peripherals may be used in the code, yet the TS68020 will transfer only the amount of data that the peripheral can manage. This feature allows the peripheral to define its port size as 8-, 16-, or 32-bit wide and the TS68020 will dynamically size the data transfer accordingly, using multiple bus cycles when necessary. Hence, programmers are not required to program for each device port size or know the specific port size before coding; hardware designers have flexibility to choose implementations independent of software prejudices.

This is accomplished through the use of the DSACK pins and occurs on a cycle-by-cycle basis. For example, if the processor is executing an instruction that requires the reading of a long word operand, it will attempt to read 32-bit during the first bus cycle to a long word address boundary. If the port responds that it is 32-bit wide, the TS68020 latches all 32-bit of data and continues. If the port responds that it is 16-bit wide, the TS68020 latches 16 valid bits of data and runs another cycle to obtain the other 16-bit of data. An 8-bit port is handled similarly by with four bus read cycles. Each port is fixed in assignment to particular sections of the data bus.

Justification of data on the bus is handled automatically by dynamic bus sizing. When reading 16-bit data from a 32-bit port, the data may appear on the top or bottom half of the bus, depending on the address of the data. The TS68020 determines which portion of the bus is needed to support the transfer and dynamically adjusts to read or write the data on those data lines.

The TS68020 will always transfer the maximum amount of data on all bus cycles; i.e., it always assumes the port is 32-bit wide when beginning the bus cycle. In addition, the TS68020 has no restrictions concerning alignment of operands in memory; long word operands need not be aligned on long word address boundaries. When misaligned data requires multiple bus cycles, the TS68020 aligned data requires multiple bus cycles, the TS68020 aligned data requires multiple bus cycles, the TS68020 automatically runs the minimum number of bus cycles.

The Co-processorThe co-processor interface is a mechanism for extending the instruction set of the<br/>TS68000 Family. Examples of these extensions are the addition of specialized data<br/>operands for the existing data types or, for the case of the floating point, the inclusion of<br/>new data types and operations for them as implemented by the TS68881 and TS68882<br/>floating point co-processors.

The programmer's model for the TS68000 Family of microprocessors is based on sequential, non-concurrent instruction execution. This means each instruction is completely executed prior to the beginning of the next instruction. Hence, instructions do not operate concurrently in the programmer's model. Most microprocessors implement the sequential model which greatly simplifies the programmer responsibilities since sequencing control is automatic and discrete.

The TS68000 co-processor interface is designed to extend the programmer's model and it provides full support for the sequential, non-concurrent instruction execution model. Hence, instruction execution by the co-processor is assumed to not overlap with instruction execution with the main microprocessor. Yet, the TS68000 co-processor interface does allow concurrent operation when concurrency can be properly accommodated. For example, the TS68881 or TS68882 floating-point co-processor will allow the TS68020 to proceed executing instruction while the co-processor continues a floating-point operation, up to the point that the TS68020 sends another request to the co-processor. Adhering to the sequential execution model, the request to the co-processor continues a floating-point operation, up to the co-processor completes each TS68881 and TS68882 instruction before it starts the next, and the TS68020 is allowed to proceed as it can in a concurrent fashion.

co-processors are divided into two types by their bus utilization characteristics. A coprocessor is a DMA co-processor if it can control the bus independent of the main processor. A co-processor is a non-DMA co-processor if it does not have the capability of controlling the bus. Both co-processor types utilize the same protocol and main processor resources. Implementation of a co-processor as a DMA or non-DMA type is based primarily on bus bandwidth of the co-processor, performance, and cost issues.

The communication protocol between the main processor and the co-processor necessary to execute a co-processor instruction is based on a group of co-processor interface registers (Table 10) which are defined for the TS68000 Family co-processor interface. The TS68020 hardware uses standard TS68000 asynchronous bus cycles to access the registers. Thus, the co-processor doesn't require a special bus hardware; the bus interface implemented by a co-processor for its interface register set must only satisfy the TS68020 address, data, and control signal timing to guarantee proper communication with the main processor. The TS68020 implements the communication protocol with all co-processors in hardware (and microcode) and handles all operations automatically so the programmer is only concerned with the instructions and data types provided by the co-processor as extensions to the TS68020 instruction set and data types. Other microprocessors in the TS68000 Family can operate any TS68000 co-processor even though they may not have the hardware implementation of the co-processor interface as does the TS68020. Since the co-processor is operated through the coprocessor interface registers which are accessed via normal asynchronous bus cycles, the co-processor may be used as a peripheral device. Software easily emulates the communication protocol by addressing the co-processor interface registers appropriately and passing the necessary commands and operands required by the coprocessor.

The co-processor interface registers are implemented by the co-processor in addition to those registers implemented as extensions to the TS68020 programmer's model. For example, the TS68881 implements the co-processor interface registers shown in Table 10 and the registers in the programming model, including eight 80-bit floating-point data registers and three 32-bit control/status registers used by the TS68881 programmer.

| Register            | Function                            | R/W |

|---------------------|-------------------------------------|-----|

| Response            | Requests Action from CPU            | R   |

| Control             | CPU                                 | W   |

| Save                | Initiate Save of Internal State     | R   |

| Restore             | Initiate Restore of Internal State  | R/W |

| Operation Word      | Current Co-processor Instruction    | W   |

| Command Word        | Co-processor Specific Command       | W   |

| Condition Word      | Condition to be Evaluated           | W   |

| Operand             | 32-bit Operand                      | R/W |

| Register Select     | Specifies CPU Register or Mask      | R   |

| Instruction Address | Pointer to Co-processor Instruction | R/W |

| Operand Address     | Pointer to Co-processor Operand     | R/W |

Table 10.

Co-processor Interface Registers

#### Table 11. Co-processor Primitives

| Processor Synchronization<br>Busy with Current Instruction<br>Proceed with Next Instructior<br>Service Interrupts and Re-qu<br>Proceed with Execution, Con | n, If No Trace<br>ery, If Trace Enable |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Instruction Manipulation<br>Transfer Operation Word<br>Transfer Words from Instructi                                                                       | on Stream                              |

| Exception Handling<br>Take Privilege Violation if S E<br>Take Pre-Instruction Exceptio<br>Take Mid-Instruction Exceptio<br>Take Post-Instruction Exception | on<br>on                               |

When the main processor encounters the next co-processor instruction, the main processor queries the co-processor until the co-processor is ready; meanwhile, the main processor can go on to service interrupts and do a context switch to execute other tasks, for example.

Each co-processor instruction type has specific requirements based on this simplified protocol. The co-processor interface may use as many extension words as requires to implement a co-processor instruction.

Primitives/Response The response register is the means by which the co-processor communicates service requests to the main processor. The content of the co-processor response register is a primitive instruction to the main processor which is read during co-processor communication by the main processor. The main processor "executes" this primitive, thereby providing the services requires by the co-processor. Table 11 summarizes the co-processor primitives that the TS68020 accepts.

#### **Exceptions**

**Kinds of Exceptions** Exceptions are the generated by either internal or external causes. The externally generated exceptions are the interrupts, the bus error, and reset requests. The interrupts are requests from peripheral devices for processor action while the bus error and reset pins are used for access control and processor restart. The internally generated exceptions come from instructions, address errors, tracing, or breakpoints. The TRAP, TRAPcc, TRAPV, cpTRAPcc, CHK, CHK2, and DIV instructions can all generate exceptions as part of their execution. Tracing behaves like a very high priority, internally generated interrupt whenever it is processed. The other internally generated exceptions are caused by illegal instructions, instruction fetches from odd addresses, and privilege violations.

Exception Processing Exception processing occurs in four steps. During the first step, an internal copy is made of the status register. After the copy is made, the special processor state bits in the status register are changed. The S bit is set, putting the processor into supervisor privilege state. Also, the T1 and T0 bits are negated, allowing the exception handler to execute unhindered by tracing. For the reset and interrupt exceptions, the interrupt priority mask is also updated.

In the second step, the vector number of the exception is determined. For interrupts, the vector number is obtained by a processor read that is classified as an interrupt acknowledge cycle. For co-processor detected exceptions, the victor number is included in the co-processor exception primitive response. For all other exceptions, internal logic provides the vector number. This vector number is then used to generate the address of the exception vector.

The third step is to save the current processor status. The exception stack frame is created and filled on the supervisor stack. In order to minimize the amount of machine state that is saved, various stack frame sizes are used to contain the processor state depending on the type of exception and where it occurred during instruction execution. If the exception is an interrupt and the M bit is on, the M bit is forced off, and a short four word exception stack frame is saved on the master stack which indicates that the exception is saved on the interrupt stack. If the exception is a reset, the M bit is simply forced off, and the reset vector is accessed.

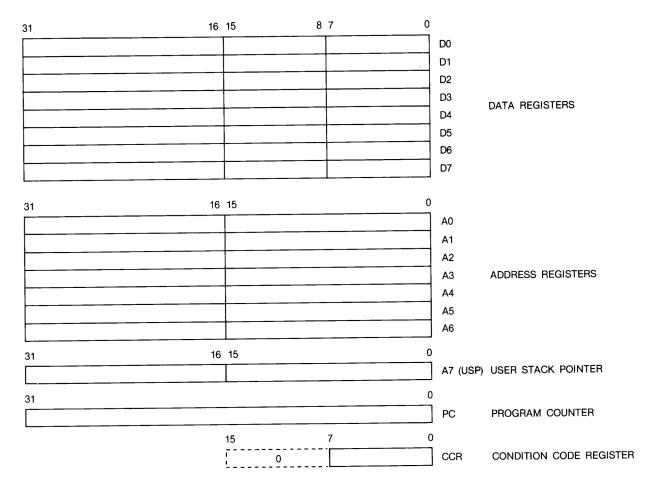

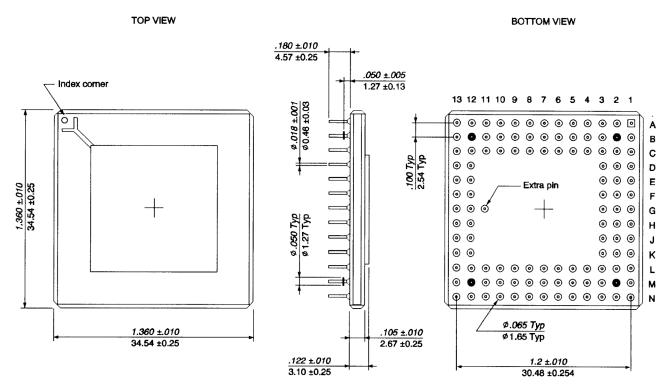

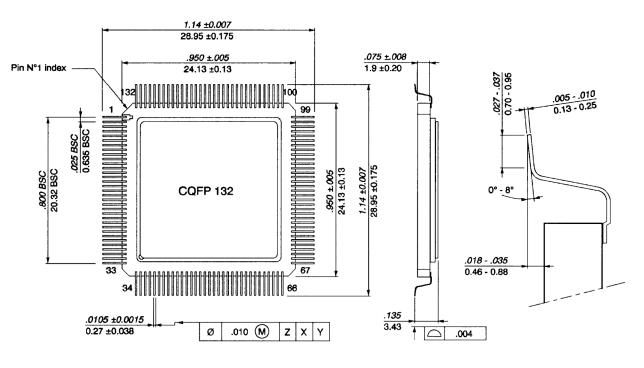

# Package Mechanical Data

Figure 24. 132 Pins - Ceramic Quad Flat Pack

Mass

PGA 114 - 6 grams typically CQFP 132 - 14 grams typically

Terminal Connections

**114-lead - Ceramic Pin**See Figure 2.**Grid Array**

**132-lead - Ceramic Quad** See Figure 3. Flat Pack

# **Ordering Information**

# **Hi-REL Product**

| Commercial Atmel<br>Part-Number | Norms       | Package      | Temperature Range<br>T <sub>c</sub> (°C) | Frequency<br>(MHz) | Drawing Number |

|---------------------------------|-------------|--------------|------------------------------------------|--------------------|----------------|

| TS68020MRB/C16                  | MIL-STD-883 | PGA 114      | -55/+125                                 | 16.67              | -              |

| TS68020MR1B/C16                 | MIL-STD-883 | PGA 114/tin  | -55/+125                                 | 16.67              | -              |

| TS68020MRB/C20                  | MIL-STD-883 | PGA 114      | -55/+125                                 | 20                 | -              |

| TS68020MR1B/C20                 | MIL-STD-883 | PGA 114/tin  | -55/+125                                 | 20                 | -              |

| TS68020MRB/C25                  | MIL-STD-883 | PGA 114      | -55/+125                                 | 25                 | -              |

| TS68020MR1B/C25                 | MIL-STD-883 | PGA 114/tin  | -55/+125                                 | 25                 | -              |

| TS68020MFB/C16                  | MIL-STD-883 | CQFP 132     | -55/+125                                 | 16.67              | -              |

| TS68020MF1B/C16                 | MIL-STD-883 | CQFP 132/tin | -55/+125                                 | 16.67              | -              |

| TS68020MFB/C20                  | MIL-STD-883 | CQFP 132     | -55/+125                                 | 20                 | -              |

| TS68020MF1B/C20                 | MIL-STD-883 | CQFP 132/tin | -55/+125                                 | 20                 | -              |

| TS68020MFB/C25                  | MIL-STD-883 | CQFP 132     | -55/+125                                 | 25                 | -              |

| TS68020MF1B/C25                 | MIL-STD-883 | CQFP 132/tin | -55/+125                                 | 25                 | -              |

| TS68020DESC02XA                 | DESC        | PGA 114/tin  | -55/+125                                 | 16.67              | 5962-8603202XA |

| TS68020DESC03XA                 | DESC        | PGA 114/tin  | -55/+125                                 | 20                 | 5962-8603203XA |

| TS68020DESC04XA                 | DESC        | PGA 114/tin  | -55/+125                                 | 25                 | 5962-8603204XA |

| TS68020DESC02XC                 | DESC        | PGA 114      | -55/+125                                 | 16.67              | 5962-8603202XC |

| TS68020DESC03XC                 | DESC        | PGA 114      | -55/+125                                 | 20                 | 5962-8603203XC |

| TS68020DESC04XC                 | DESC        | PGA 114      | -55/+125                                 | 25                 | 5962-8603204XC |

| TS68020DESC02YA                 | DESC        | CQFP 132/tin | -55/+125                                 | 16.67              | 5962-8603202YA |

| TS68020DESC03YA                 | DESC        | CQFP 132/tin | -55/+125                                 | 20                 | 5962-8603203YA |

| TS68020DESC04YA                 | DESC        | CQFP 132/tin | -55/+125                                 | 25                 | 5962-8603204YA |

| TS68020DESC02YC                 | DESC        | CQFP 132     | -55/+125                                 | 16.67              | 5962-8603202YC |

| TS68020DESC03YC                 | DESC        | CQFP 132     | -55/+125                                 | 20                 | 5962-8603203YC |

| TS68020DESC04YC                 | DESC        | CQFP 132     | -55/+125                                 | 25                 | 5962-8603204YC |

### **Standard Product**

| Commercial Atmel<br>Part-Number | Norms             | Package | Temperature Range<br>T <sub>c</sub> (°C) | Frequency<br>(MHz) | Drawing<br>Number |

|---------------------------------|-------------------|---------|------------------------------------------|--------------------|-------------------|

| TS68020VR16                     | Internal Standard | PGA 114 | -40/+85                                  | 16.67              | Internal          |

| TS68020VR20                     | Internal Standard | PGA 114 | -40/+85                                  | 20                 | Internal          |

| TS68020VR25                     | Internal Standard | PGA 114 | -40/+85                                  | 25                 | Internal          |

| TS68020MR16                     | Internal Standard | PGA 114 | -55/+125                                 | 16.67              | Internal          |

| TS68020MR20                     | Internal Standard | PGA 114 | -55/+125                                 | 20                 | Internal          |

| TS68020MR25                     | Internal Standard | PGA 114 | -55/+125                                 | 25                 | Internal          |