Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | RX                                                                               |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 32MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                                       |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 50                                                                               |

| Program Memory Size        | 64KB (64K × 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 10K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                      |

| Data Converters            | A/D 14x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

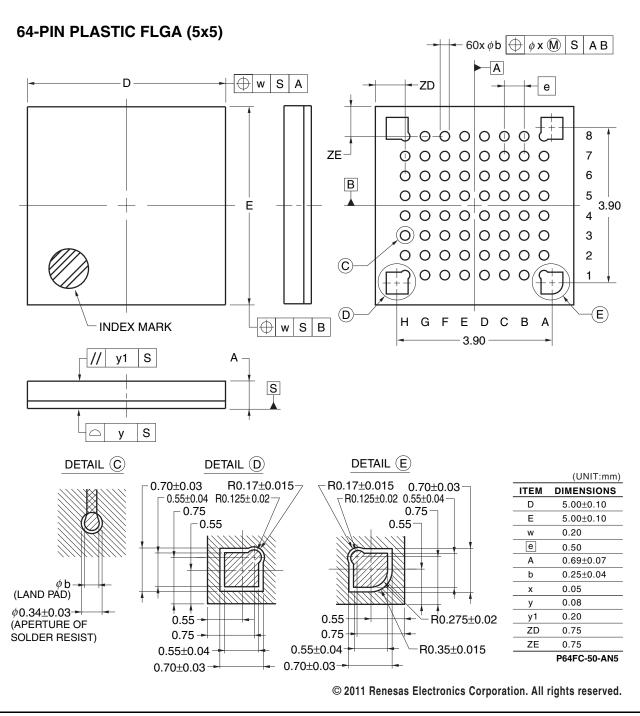

| Package / Case             | 64-WFLGA                                                                         |

| Supplier Device Package    | 64-FLGA (5x5)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f51103adlf-u0 |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Overview

## 1.1 Outline of Specifications

Table 1.1 lists the specifications, and Table 1.2 gives a comparison of the functions of the products in different packages.

Table 1.1 is for products with the greatest number of functions, so the number of peripheral modules and channels will differ in accordance with the package type. For details, see Table 1.2, Comparison of Functions for Different Packages.

| Classification        | Module/Function                                | Description         • Maximum operating frequency: 32 MHz         • 32-bit RX CPU         • Minimum instruction execution time: One instruction per one clock cycle         • Address space: 4-Gbyte linear         • Register set         General purpose: Sixteen 32-bit registers         Control: Eight 32-bit registers         Accumulator: One 64-bit register         • Basic instructions: 73         • DSP instructions: 9         • Addressing modes: 10         • Data arrangement         Instructions: Little endian         • On-chip 32-bit multiplier: 32-bit × 32-bit → 64-bit         • On-chip divider: 32-bit → 32 bits         • Barrel shifter: 32 bits                                                               |  |  |  |  |  |  |

|-----------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| CPU                   | CPU                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Memory                | ROM                                            | <ul> <li>Capacity: 8 K /16 K /32 K /64 K /96 K /128 Kbytes</li> <li>32 MHz, no-wait memory access</li> <li>Programming/erasing method:<br/>Serial programming (asynchronous serial communication), self-programming</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|                       | RAM                                            | <ul> <li>Capacity: 8 K /10 K /16 Kbytes</li> <li>32 MHz, no-wait memory access</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| MCU operating mo      | ode                                            | Single-chip mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Clock                 | Clock generation circuit                       | <ul> <li>Main clock oscillator, sub-clock oscillator, low-speed on-chip oscillator, high-speed on-chip oscillator, and IWDT-dedicated on-chip oscillator</li> <li>Oscillation stop detection: Available</li> <li>Clock frequency accuracy measurement circuit (CAC)</li> <li>Independent settings for the system clock (ICLK), peripheral module clock (PCLK), and FlashIF clock (FCLK)</li> <li>The CPU and system sections such as other bus masters run in synchronization with the system clock (ICLK): 32 MHz (at max.)</li> <li>Peripheral modules run in synchronization with the PCLK: 32 MHz (at max.)</li> <li>The ICLK frequency can only be set to FCLK, PCLKB, or PCLKD multiplied by n (n: 1, 2, 4, 8, 16, 32, 64).</li> </ul> |  |  |  |  |  |  |

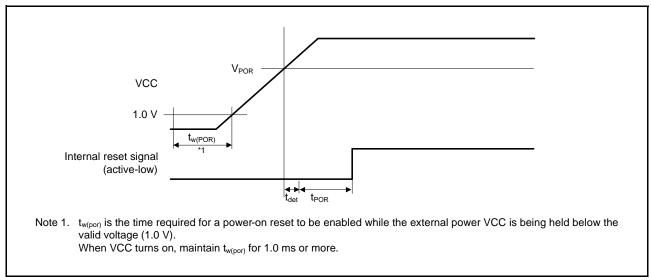

| Resets                |                                                | RES# pin reset, power-on reset, voltage monitoring reset, independent watchdog timer reset, and<br>software reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Voltage detection     | Voltage detection circuit<br>(LVDAa)           | When the voltage on VCC falls below the voltage detection level, an internal reset or internal interrupt is generated.     Voltage detection circuit 1 is capable of selecting the detection voltage from 10 levels     Voltage detection circuit 2 is capable of selecting the detection voltage from 4 levels                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Low power consumption | Low power consumption<br>functions             | <ul> <li>Module stop function</li> <li>Three low power consumption modes</li> <li>Sleep mode, deep sleep mode, and software standby mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|                       | Function for lower operating power consumption | <ul> <li>Operating power control modes</li> <li>High-speed operating mode, middle-speed operating mode, and low-speed operating mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Interrupt             | Interrupt controller (ICUb)                    | <ul> <li>Interrupt vectors: 65</li> <li>External interrupts: 9 (NMI, IRQ0 to IRQ7 pins)</li> <li>Non-maskable interrupts: 4 (NMI pin, voltage monitoring 1 interrupt, voltage monitoring 2 interrupt, and IWDT interrupt)</li> <li>16 levels specifiable for the order of priority</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| DMA                   | Data transfer controller<br>(DTCa)             | <ul> <li>Transfer modes: Normal transfer, repeat transfer, and block transfer</li> <li>Activation sources: Interrupts</li> <li>Chain transfer function</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

Table 1.1Outline of Specifications (1/3)

|                 | Fill Fullctions (5/5) |       |                          |

|-----------------|-----------------------|-------|--------------------------|

| Classifications | Pin Name              | I/O   | Description              |

| I/O ports       | PC0 to PC7            | I/O   | 8-bit input/output pins. |

|                 | PE0 to PE7            | I/O   | 8-bit input/output pins. |

|                 | PH0 to PH3            | I/O   | 4-bit input/output pins. |

|                 | PH7                   | Input | 1-bit input pin.         |

|                 | PJ6, PJ7              | I/O   | 2-bit input/output pins. |

## Table 1.4Pin Functions (3/3)

Note 1. For external clock input.

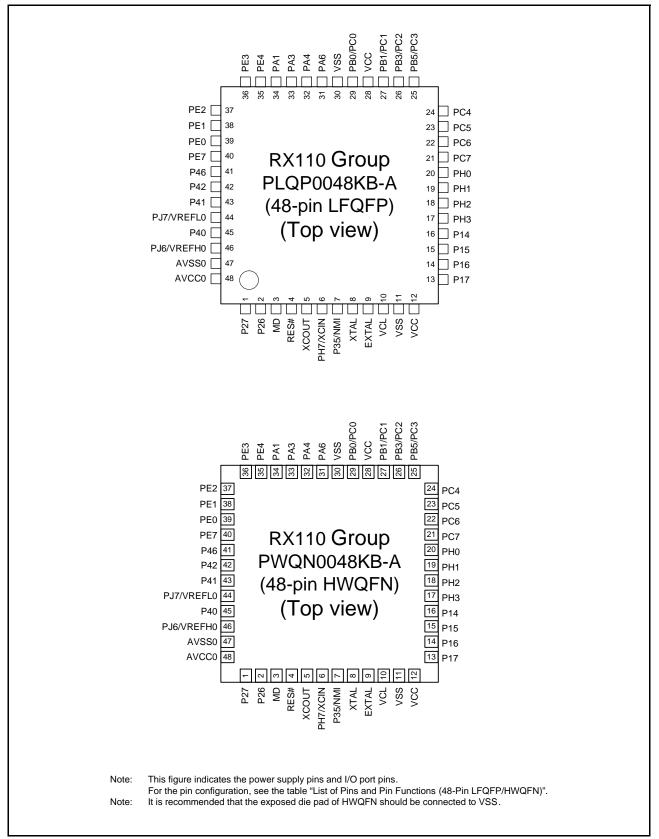

Figure 1.5Pin Assignments of the 48-Pin LFQFP/HWQFN

RENESAS

| Pin<br>No. | Power Supply, Clock,<br>System Control | I/O Port          | Timers (MTU, RTC) | Communication<br>(SCle, SClf, RSPI, RIIC) | Others     |

|------------|----------------------------------------|-------------------|-------------------|-------------------------------------------|------------|

| 45         |                                        | PA0               |                   | SSLA1                                     | CACREF     |

| 46         |                                        | PE5               | MTIOC2B           |                                           | IRQ5/AN013 |

| 47         |                                        | PE4               | MTIOC1A           | MOSIA                                     | IRQ4/AN012 |

| 48         |                                        | PE3               | MTIOC0A/MTIOC1B   | CTS12#/RTS12#/SS12#/RSPCKA                | IRQ3/AN011 |

| 49         |                                        | PE2               |                   | RXD12/RXDX12/SMISO12/SSCL12               | IRQ7/AN010 |

| 50         |                                        | PE1               |                   | TXD12/TXDX12/SIOX12/SMOSI12/<br>SSDA12    | IRQ1/AN009 |

| 51         |                                        | PE0               | MTIOC2A           | SCK12                                     | IRQ0/AN008 |

| 52         |                                        | PE7               |                   |                                           | IRQ7/AN015 |

| 53         |                                        | PE6               |                   |                                           | IRQ6/AN014 |

| 54         |                                        | P46* <sup>1</sup> |                   |                                           | AN006      |

| 55         |                                        | P44*1             |                   |                                           | AN004      |

| 56         |                                        | P43* <sup>1</sup> |                   |                                           | AN003      |

| 57         |                                        | P42* <sup>1</sup> |                   |                                           | AN002      |

| 58         |                                        | P41* <sup>1</sup> |                   |                                           | AN001      |

| 59         | VREFL0                                 | PJ7*1             |                   |                                           |            |

| 60         |                                        | P40* <sup>1</sup> |                   |                                           | AN000      |

| 61         | VREFH0                                 | PJ6* <sup>1</sup> |                   |                                           |            |

| 62         | AVSS0                                  |                   |                   |                                           |            |

| 63         | AVCC0                                  |                   |                   |                                           |            |

| 64         |                                        | P05               |                   |                                           |            |

Table 1.5

List of Pins and Pin Functions (64-Pin LFQFP/LQFP) (2/2)

Note 1. The power source of the I/O buffer for these pins is AVCCO.

| Address    | Module<br>Symbol | Register Name                     | Register<br>Symbol | Number of<br>Bits | Access<br>Size | Number of Access States |

|------------|------------------|-----------------------------------|--------------------|-------------------|----------------|-------------------------|

| 0008 C0C3h | PORT3            | Pull-Up Control Register          | PCR                | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C0C5h  | PORT5            | Pull-Up Control Register          | PCR                | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C0CAh  | PORTA            | Pull-Up Control Register          | PCR                | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C0CBh  | PORTB            | Pull-Up Control Register          | PCR                | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C0CCh  | PORTC            | Pull-Up Control Register          | PCR                | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C0CEh  | PORTE            | Pull-Up Control Register          | PCR                | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C0D1h  | PORTH            | Pull-Up Control Register          | PCR                | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C11Fh  | MPC              | Write-Protect Register            | PWPR               | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C120h  | PORT             | Port Switching Register B         | PSRB               | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C121h  | PORT             | Port Switching Register A         | PSRA               | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C14Ch  | MPC              | P14 Pin Function Control Register | P14PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C14Dh  | MPC              | P15 Pin Function Control Register | P15PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C14Eh  | MPC              | P16 Pin Function Control Register | P16PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C14Fh  | MPC              | P17 Pin Function Control Register | P17PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C156h  | MPC              | P26 Pin Function Control Register | P26PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C157h  | MPC              | P27 Pin Function Control Register | P27PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C158h  | MPC              | P30 Pin Function Control Register | P30PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C159h  | MPC              | P31 Pin Function Control Register | P31PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C15Ah  | MPC              | P32 Pin Function Control Register | P32PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C160h  | MPC              | P40 Pin Function Control Register | P40PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C160h  | MPC              | P41 Pin Function Control Register | P40PT3             | 8                 | 8              | 2 or 3 PCLKB            |

|            |                  | •                                 | P41PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C162h  | MPC              | P42 Pin Function Control Register |                    |                   |                |                         |

| 008 C163h  | MPC              | P43 Pin Function Control Register | P43PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C164h | MPC              | P44 Pin Function Control Register | P44PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C166h  | MPC              | P46 Pin Function Control Register | P46PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C190h  | MPC              | PA0 Pin Function Control Register | PA0PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C191h  | MPC              | PA1 Pin Function Control Register | PA1PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C193h  | MPC              | PA3 Pin Function Control Register | PA3PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C194h  | MPC              | PA4 Pin Function Control Register | PA4PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C196h  | MPC              | PA6 Pin Function Control Register | PA6PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C198h  | MPC              | PB0 Pin Function Control Register | PB0PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C199h  | MPC              | PB1 Pin Function Control Register | PB1PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C19Bh  | MPC              | PB3 Pin Function Control Register | PB3PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C19Dh  | MPC              | PB5 Pin Function Control Register | PB5PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C19Eh | MPC              | PB6 Pin Function Control Register | PB6PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C19Fh  | MPC              | PB7 Pin Function Control Register | PB7PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C1A2h | MPC              | PC2 Pin Function Control Register | PC2PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C1A3h  | MPC              | PC3 Pin Function Control Register | PC3PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C1A4h  | MPC              | PC4 Pin Function Control Register | PC4PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C1A5h | MPC              | PC5 Pin Function Control Register | PC5PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C1A6h  | MPC              | PC6 Pin Function Control Register | PC6PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C1A7h  | MPC              | PC7 Pin Function Control Register | PC7PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C1B0h  | MPC              | PE0 Pin Function Control Register | PE0PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C1B1h  | MPC              | PE1 Pin Function Control Register | PE1PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C1B2h  | MPC              | PE2 Pin Function Control Register | PE2PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C1B3h  | MPC              | PE3 Pin Function Control Register | PE3PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C1B4h  | MPC              | PE4 Pin Function Control Register | PE4PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C1B5h  | MPC              | PE5 Pin Function Control Register | PE5PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C1B6h  | MPC              | PE6 Pin Function Control Register | PE6PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C1B01  | MPC              |                                   | PE7PFS             | 8                 | 8              | 2 or 3 PCLKB            |

| 000 010/11 |                  | PE7 Pin Function Control Register | PE7PFS             | 8                 | 8              |                         |

| 008 C1C8h  | MPC              | PH0 Pin Function Control Register |                    |                   |                | 2 or 3 PCLKB            |

## Table 4.1 List of I/O Registers (Address Order) (11/13)

| Table 4.1 | List of I/O Registers (Address Order) (12/13) |

|-----------|-----------------------------------------------|

|-----------|-----------------------------------------------|

| Address                                          | Module<br>Symbol        | Register Name                                                                                              | Register<br>Symbol | Number of<br>Bits | Access<br>Size | Number of Access States    |

|--------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------|--------------------|-------------------|----------------|----------------------------|

| 0008 C1CAh                                       | MPC                     | PH2 Pin Function Control Register                                                                          | PH2PFS             | 8                 | 8              | 2 or 3 PCLKB               |

| 0008 C1CBh                                       | MPC                     | PH3 Pin Function Control Register                                                                          | PH3PFS             | 8                 | 8              | 2 or 3 PCLKB               |

| 0008 C1D6h                                       | MPC                     | PJ6 Pin Function Control Register                                                                          | PJ6PFS             | 8                 | 8              | 2 or 3 PCLKB               |

| 0008 C1D7h                                       | MPC                     | PJ7 Pin Function Control Register                                                                          | PJ7PFS             | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C290h                                        | SYSTEM                  | Reset Status Register 0                                                                                    | RSTSR0             | 8                 | 8              | 4 or 5 PCLKB               |

| 0008 C291h                                       | SYSTEM                  | Reset Status Register 1                                                                                    | RSTSR1             | 8                 | 8              | 4 or 5 PCLKB               |

| 008 C293h                                        | SYSTEM                  | Main Clock Oscillator Forced Oscillation Control Register                                                  | MOFCR              | 8                 | 8              | 4 or 5 PCLKB               |

| 0008 C297h                                       | SYSTEM                  | Voltage Monitoring Circuit Control Register                                                                | LVCMPCR            | 8                 | 8              | 4 or 5 PCLKB               |

| 008 C298h                                        | SYSTEM                  | Voltage Detection Level Select Register                                                                    | LVDLVLR            | 8                 | 8              | 4 or 5 PCLKB               |

| 008 C29Ah                                        | SYSTEM                  | Voltage Monitoring 1 Circuit Control Register 0                                                            | LVD1CR0            | 8                 | 8              | 4 or 5 PCLKB               |

| 008 C29Bh                                        | SYSTEM                  | Voltage Monitoring 2 Circuit Control Register 0                                                            | LVD2CR0            | 8                 | 8              | 4 or 5 PCLKB               |

| 008 C400h                                        | RTC                     | 64-Hz Counter                                                                                              | R64CNT             | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C402h                                        | RTC                     | Second Counter                                                                                             | RSECCNT            | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C402h                                        | RTC                     | Binary Counter 0                                                                                           | BCNT0              | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C404h                                        | RTC                     | Minute Counter                                                                                             | RMINCNT            | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C404h                                        | RTC                     | Binary Counter 1                                                                                           | BCNT1              | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C406h                                        | RTC                     | Hour Counter                                                                                               | RHRCNT             | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C406h                                        | RTC                     | Binary Counter 2                                                                                           | BCNT2              | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C408h                                        | RTC                     | Day-Of-Week Counter                                                                                        | RWKCNT             | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C408h                                        | RTC                     | Binary Counter 3                                                                                           | BCNT3              | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C40Ah                                        | RTC                     | Date Counter                                                                                               | RDAYCNT            | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C40Ch                                        | RTC                     | Month Counter                                                                                              | RMONCNT            | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C40Eh                                        | RTC                     | Year Counter                                                                                               | RYRCNT             | 16                | 16             | 2 or 3 PCLKB               |

| 008 C410h                                        | RTC                     | Second Alarm Register                                                                                      | RSECAR             | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C410h                                        | RTC                     | Binary Counter 0 Alarm Register                                                                            | BCNT0AR            | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C412h                                        | RTC                     | Minute Alarm Register                                                                                      | RMINAR             | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C412h                                        | RTC                     | Binary Counter 1 Alarm Register                                                                            | BCNT1AR            | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C414h                                        | RTC                     | Hour Alarm Register                                                                                        | RHRAR              | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C414h                                        | RTC                     | Binary Counter 2 Alarm Register                                                                            | BCNT2AR            | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C416h                                        | RTC                     | Day-of-Week Alarm Register                                                                                 | RWKAR              | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C416h                                        | RTC                     | Binary Counter 3 Alarm Register                                                                            | <b>BCNT3AR</b>     | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C418h                                        | RTC                     | Date Alarm Register                                                                                        | RDAYAR             | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C418h                                        | RTC                     | Binary Counter 0 Alarm Enable Register                                                                     | BCNT0AER           | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C41Ah                                        | RTC                     | Month Alarm Register                                                                                       | RMONAR             | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C41Ah                                        | RTC                     | Binary Counter 1 Alarm Enable Register                                                                     | BCNT1AER           | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C41Ch                                        | RTC                     | Year Alarm Register                                                                                        | RYRAR              | 16                | 16             | 2 or 3 PCLKB               |

| 008 C41Ch                                        | RTC                     | Binary Counter 2 Alarm Enable Register                                                                     | BCNT2AER           | 16                | 16             | 2 or 3 PCLKB               |

| 008 C41Eh                                        | RTC                     | Year Alarm Enable Register                                                                                 | RYRAREN            | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C41Eh                                        | RTC                     | Binary Counter 3 Alarm Enable Register                                                                     | BCNT3AER           | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C422h                                        | RTC                     | RTC Control Register 1                                                                                     | RCR1               | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C424h                                        | RTC                     | RTC Control Register 2                                                                                     | RCR2               | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C424h                                        | RTC                     | RTC Control Register 3                                                                                     | RCR3               | 8                 | 8              | 2 or 3 PCLKB               |

| 008 C42011                                       | RTC                     | •                                                                                                          | RADJ               | 8                 | 8              | 2 or 3 PCLKB               |

|                                                  |                         | Time Error Adjustment Register                                                                             |                    |                   |                |                            |

|                                                  |                         | Temperature Sensor Calibration Data Register                                                               | TSCDRL             | 8                 | 8              | 1 or 2 PCLKB               |

| 07F COADh                                        |                         | Temperature Sensor Calibration Data Register                                                               | TSCDRH             | 8                 | 8              | 1 or 2 PCLKB               |

| 07F C0B0h                                        | FLASH                   | Flash Start-Up Setting Monitor Register                                                                    | FSCMR              | 16                | 16             | 2 or 3 FCLK                |

| 07F C0B2h                                        | FLASH                   | Flash Access Window Start Address Monitor                                                                  | FAWSMR             | 16                | 16             | 2 or 3 FCLK                |

|                                                  | FLASH                   | Flash Access Window End Address Monitor Register                                                           | FAWEMR             | 16                | 16             | 2 or 3 FCLK                |

| 07F C0B4h                                        | EL A C' I               |                                                                                                            | FISR               | 8                 | 8              | 2 or 3 FCLK                |

| 07F C0B6h                                        | FLASH                   | Flash Initial Setting Register                                                                             |                    |                   |                |                            |

| 07F C0B4h<br>07F C0B6h<br>07F C0B7h<br>07F C0B8h | FLASH<br>FLASH<br>FLASH | Flash Extra Area Control Register Flash Extra Area Control Register Flash Error Address Monitor Register L | FEXCR              | 8                 | 8<br>16        | 2 or 3 FCLK<br>2 or 3 FCLK |

#### 5.2 **DC** Characteristics

Table 5.3DC Characteristics (1)Conditions: $2.7 \text{ V} \le \text{VCC} \le 3.6 \text{ V}, 2.7 \text{ V} \le \text{AVCC0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

|                                         | Item                                                                                                                                                                                                                                       | Symbol          | Min.        | Тур. | Max.        | Unit | Test<br>Conditions |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|------|-------------|------|--------------------|

| Schmitt trigger input voltage           | RIIC input pin<br>(except for SMBus, 5 V tolerant)                                                                                                                                                                                         | V <sub>IH</sub> | VCC × 0.7   | —    | 5.8         | V    |                    |

|                                         | Ports P16, P17,<br>port PA6, port PB0 (5 V tolerant)                                                                                                                                                                                       |                 | VCC × 0.8   | —    | 5.8         |      |                    |

|                                         | Ports P03, P05,<br>ports P14, P15,<br>ports P26, P27,<br>ports P30 to P32, P35,<br>ports P54, P55,<br>ports PA0, PA1, PA3, PA4,<br>ports PB1, PB3, PB5 to PB7,<br>ports PC0 to PC7,<br>ports PE0 to PE7,<br>ports PH0 to PH3, PH7,<br>RES# |                 | VCC × 0.8   | _    | VCC + 0.3   |      |                    |

|                                         | RIIC input pin<br>(except for SMBus)                                                                                                                                                                                                       | V <sub>IL</sub> | -0.3        | _    | VCC × 0.3   |      |                    |

|                                         | Other than RIIC input pin                                                                                                                                                                                                                  |                 | -0.3        | _    | VCC × 0.2   |      |                    |

|                                         | RIIC input pin<br>(except for SMBus)                                                                                                                                                                                                       | ΔV <sub>T</sub> | VCC × 0.05  | —    | _           |      |                    |

|                                         | Other than RIIC input pin                                                                                                                                                                                                                  |                 | VCC × 0.1   | _    | _           |      |                    |

| Input voltage                           | MD                                                                                                                                                                                                                                         | V <sub>IH</sub> | VCC × 0.9   | _    | VCC + 0.3   | V    |                    |

| (except for Schmitt trigger input pins) | XTAL (external clock input)                                                                                                                                                                                                                |                 | VCC × 0.8   | —    | VCC + 0.3   |      |                    |

|                                         | Ports P40 to P44, P46,<br>ports PJ6, PJ7                                                                                                                                                                                                   |                 | AVCC0 × 0.7 | —    | AVCC0 + 0.3 |      |                    |

|                                         | RIIC input pin (SMBus)                                                                                                                                                                                                                     |                 | 2.1         | _    | VCC + 0.3   |      |                    |

|                                         | MD                                                                                                                                                                                                                                         | V <sub>IL</sub> | -0.3        | —    | VCC × 0.1   |      |                    |

|                                         | XTAL (external clock input)                                                                                                                                                                                                                | 1               | -0.3        | —    | VCC × 0.2   |      |                    |

|                                         | Ports P40 to P44, P46,<br>ports PJ6, PJ7                                                                                                                                                                                                   |                 | -0.3        | —    | AVCC0 × 0.3 |      |                    |

|                                         | RIIC input pin (SMBus)                                                                                                                                                                                                                     | ]               | -0.3        | _    | 0.8         |      |                    |

## Table 5.4DC Characteristics (2)

Conditions: 1.8 V  $\leq$  VCC < 2.7 V, 1.8 V  $\leq$  AVCC0 < 2.7 V, VSS = AVSS0 = 0 V, T<sub>a</sub> = -40 to +105°C

|                                         | Item                                                                                                                                                                                                                                       | Symbol          | Min.        | Тур. | Max.        | Unit | Test<br>Conditions |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|------|-------------|------|--------------------|

| Schmitt trigger input voltage           | Ports P16, P17, port PA6, port PB0<br>(5 V tolerant)                                                                                                                                                                                       | V <sub>IH</sub> | VCC × 0.8   |      | 5.8         | V    |                    |

|                                         | Ports P03, P05,<br>ports P14, P15,<br>ports P26, P27,<br>ports P30 to P32, P35,<br>ports P54, P55,<br>ports PA0, PA1, PA3, PA4,<br>ports PB1, PB3, PB5 to PB7,<br>ports PC0 to PC7,<br>ports PE0 to PE7,<br>ports PH0 to PH3, PH7,<br>RES# |                 | VCC × 0.8   |      | VCC + 0.3   |      |                    |

|                                         | All pins                                                                                                                                                                                                                                   |                 | -0.3        |      | VCC × 0.2   |      |                    |

|                                         | All pins                                                                                                                                                                                                                                   | $\Delta V_T$    | VCC × 0.01  | _    | —           |      |                    |

| Input voltage                           | MD                                                                                                                                                                                                                                         | V <sub>IH</sub> | VCC × 0.9   | _    | VCC + 0.3   | V    |                    |

| (except for Schmitt trigger input pins) | XTAL (external clock input)                                                                                                                                                                                                                |                 | VCC × 0.8   | _    | VCC + 0.3   |      |                    |

|                                         | Ports P40 to P44, P46,<br>ports PJ6, PJ7                                                                                                                                                                                                   |                 | AVCC0 × 0.7 |      | AVCC0 + 0.3 |      |                    |

|                                         | MD                                                                                                                                                                                                                                         | V <sub>IL</sub> | -0.3        | _    | VCC × 0.1   |      |                    |

|                                         | XTAL (external clock input)                                                                                                                                                                                                                |                 | -0.3        | _    | VCC × 0.2   |      |                    |

|                                         | Ports P40 to P44, P46,<br>ports PJ6, PJ7                                                                                                                                                                                                   | ]               | -0.3        |      | AVCC0 × 0.3 |      |                    |

## Table 5.5DC Characteristics (3)

Conditions:  $1.8 \text{ V} \le \text{VCC} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVCC0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = 0 \text{ V}, \text{ T}_{a} = -40 \text{ to } +105^{\circ}\text{C}$

| Item                           |                                                   | Symbol           | Min. | Тур. | Max. | Unit | Test Conditions                              |  |

|--------------------------------|---------------------------------------------------|------------------|------|------|------|------|----------------------------------------------|--|

| Input leakage<br>current       | RES#, MD, port P35, port PH7                      | I <sub>in</sub>  | _    | —    | 1.0  | μA   | V <sub>in</sub> = 0 V, VCC                   |  |

| Three-state                    | Ports for 5 V tolerant                            | I <sub>TSI</sub> |      | —    | 1.0  | μA   | V <sub>in</sub> = 0 V, 5.8 V                 |  |

| leakage current<br>(off-state) | Pins other than above                             |                  | _    | —    | 1.0  |      | V <sub>in</sub> = 0 V, VCC                   |  |

| Input capacitance              | All input pins<br>(except for port P16, port P35) | C <sub>in</sub>  | _    | —    | 15   | pF   | V <sub>in</sub> = 0 mV,<br>Frequency: 1 MHz, |  |

|                                | Port P16, port P35                                | 1                | _    | —    | 30   | 1    | T <sub>a</sub> = 25°C                        |  |

## Table 5.6DC Characteristics (4)

Conditions: 1.8 V ≤ VCC ≤ 3.6 V, 1.8 V ≤ AVCC0 ≤ 3.6 V, VSS = AVSS0 = 0 V,  $T_a = -40$  to +105°C

| ltem                      |                                              | Symbol         | Min. | Тур. | Max. | Unit | Test Conditions |

|---------------------------|----------------------------------------------|----------------|------|------|------|------|-----------------|

| Input pull-up<br>resistor | All ports<br>(except for port P35, port PH7) | R <sub>U</sub> | 10   | 20   | 100  | kΩ   | $V_{in} = 0 V$  |

## Table 5.14 DC Characteristics (12)

Conditions:  $1.8 \text{ V} \le \text{VCC} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVCC0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

| Item                                              | Symbol           | Min. | Тур. | Max. | Unit | Test Conditions |

|---------------------------------------------------|------------------|------|------|------|------|-----------------|

| Permissible error of VCL pin external capacitance | C <sub>VCL</sub> | 1.4  | 4.7  | 7.0  | μF   |                 |

Note: The recommended capacitance is 4.7 µF. Variations in connected capacitors should be within the above range.

## Table 5.15 Permissible Output Currents (1)

Conditions:  $1.8 \text{ V} \le \text{VCC} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVCC0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = 0 \text{ V},$

$T_a = -40$  to +85°C (D version)

|                                 | Item                                                                                                                     | Symbol           | Max. | Unit |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------|------|------|

| Permissible output low current  | Ports P40 to P44, P46, ports PJ6, PJ7                                                                                    | I <sub>OL</sub>  | 0.4  | mA   |

| (average value per pin)         | Ports other than above                                                                                                   |                  | 8.0  |      |

| Permissible output low current  | Ports P40 to P44, P46, ports PJ6, PJ7                                                                                    |                  | 0.4  |      |

| (maximum value per pin)         | Ports other than above                                                                                                   |                  | 8.0  |      |

| Permissible output low current  | Total of ports P40 to P44, P46, ports PJ6, PJ7                                                                           | $\Sigma I_{OL}$  | 2.4  |      |

|                                 | Total of ports P03, P05, ports P26, P27, ports P30, P31                                                                  |                  | 30   |      |

|                                 | Total of ports P14 to P17, port P32, ports P54, P55, ports PB0, PB1, PB3, PB5 to PB7, ports PC2 to PC7, ports PH0 to PH3 |                  | 30   |      |

|                                 | Total of ports PA0, PA1, PA3, PA4, PA6, ports PE0 to PE7                                                                 |                  | 30   |      |

|                                 | Total of all output pins                                                                                                 |                  | 60   |      |

| Permissible output high current | Ports P40 to P44, P46, ports PJ6, PJ7                                                                                    | I <sub>OH</sub>  | -0.1 |      |

| (average value per pin)         | Ports other than above                                                                                                   |                  | -4.0 |      |

| Permissible output high current | Ports P40 to P44, P46, ports PJ6, PJ7                                                                                    |                  | -0.1 |      |

| (maximum value per pin)         | Ports other than above                                                                                                   |                  | -4.0 |      |

| Permissible output high current | Total of ports P40 to P44, P46, ports PJ6, PJ7                                                                           | Σl <sub>OH</sub> | -0.6 |      |

|                                 | Total of ports P03, P05, ports P26, P27, ports P30, P31                                                                  |                  | -10  |      |

|                                 | Total of ports P14 to P17, port P32, ports P54, P55, ports PB0, PB1, PB3, PB5 to PB7, ports PC2 to PC7, ports PH0 to PH3 |                  | -15  |      |

|                                 | Total of ports PA0, PA1, PA3, PA4, PA6, ports PE0 to PE7                                                                 |                  | -15  |      |

|                                 | Total of all output pins                                                                                                 |                  | -40  |      |

Note: Do not exceed the permissible total supply current.

## Table 5.16 Permissible Output Currents (2)

Conditions:  $1.8 \text{ V} \le \text{VCC} \le 3.6 \text{ V}$ ,  $1.8 \text{ V} \le \text{AVCC0} \le 3.6 \text{ V}$ , VSS = AVSS0 = 0 V,  $T_a = -40 \text{ to } +105^{\circ}\text{C} \text{ (G version)}$

|                                 | Item                                                                                                                     | Symbol           | Max. | Unit |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------|------|------|

| Permissible output low current  | Ports P40 to P44, P46, ports PJ6, PJ7                                                                                    | I <sub>OL</sub>  | 0.4  | mA   |

| (average value per pin)         | Ports other than above                                                                                                   |                  | 8.0  |      |

| Permissible output low current  | Ports P40 to P44, P46, ports PJ6, PJ7                                                                                    |                  | 0.4  |      |

| (maximum value per pin)         | Ports other than above                                                                                                   |                  | 8.0  |      |

| Permissible output low current  | Total of ports P40 to P44, P46, ports PJ6, PJ7                                                                           | Σl <sub>OL</sub> | 1.6  |      |

|                                 | Total of ports P03, P05, ports P26, P27, ports P30, P31                                                                  |                  | 20   |      |

|                                 | Total of ports P14 to P17, port P32, ports P54, P55, ports PB0, PB1, PB3, PB5 to PB7, ports PC2 to PC7, ports PH0 to PH3 |                  | 20   |      |

|                                 | Total of ports PA0, PA1, PA3, PA4, PA6, ports PE0 to PE7                                                                 |                  | 20   |      |

|                                 | Total of all output pins                                                                                                 |                  | 40   |      |

| Permissible output high current | Ports P40 to P44, P46, ports PJ6, PJ7                                                                                    | I <sub>ОН</sub>  | -0.1 |      |

| (average value per pin)         | Ports other than above                                                                                                   |                  | -4.0 |      |

| Permissible output high current | Ports P40 to P44, P46, ports PJ6, PJ7                                                                                    |                  | -0.1 |      |

| (maximum value per pin)         | Ports other than above                                                                                                   |                  | -4.0 |      |

| Permissible output high current | Total of ports P40 to P44, P46, ports PJ6, PJ7                                                                           | Σl <sub>OH</sub> | -0.6 |      |

|                                 | Total of ports P03, P05, ports P26, P27, ports P30, P31                                                                  |                  | -10  |      |

|                                 | Total of ports P14 to P17, port P32, ports P54, P55, ports PB0, PB1, PB3, PB5 to PB7, ports PC2 to PC7, ports PH0 to PH3 |                  | -15  |      |

|                                 | Total of ports PA0, PA1, PA3, PA4, PA6, ports PE0 to PE7                                                                 |                  | -15  | 1    |

|                                 | Total of all output pins                                                                                                 |                  | -40  | 1    |

Note: Do not exceed the permissible total supply current.

## 5.3.3 Timing of Recovery from Low Power Consumption Modes

## Table 5.24 Timing of Recovery from Low Power Consumption Modes (1)

Conditions:  $1.8 \text{ V} \le \text{VCC} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVCC0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = 0 \text{ V}, \text{ T}_{a} = -40 \text{ to } +105^{\circ}\text{C}$

| Item                                             |                                    |                                                                                                                                      | Symbol                                           | Min.               | Тур. | Max. | Unit | Test<br>Conditions |  |

|--------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------|------|------|------|--------------------|--|

| Recovery time<br>from software<br>standby mode*1 | ware mode connected to operating*2 |                                                                                                                                      | t <sub>SBYMC</sub>                               | _                  | 2    | 3    | ms   | Figure 5.28        |  |

|                                                  |                                    | External clock<br>input to main<br>clock oscillator                                                                                  | Main clock oscillator<br>operating* <sup>3</sup> | t <sub>SBYEX</sub> |      | 35   | 50   | μs                 |  |

|                                                  |                                    | Sub-clock oscillator operating         HOCO clock oscillator operating*4           LOCO clock oscillator operating         Inclusion |                                                  | t <sub>SBYSC</sub> | _    | 650  | 800  | μs                 |  |

|                                                  |                                    |                                                                                                                                      |                                                  | t <sub>SBYHO</sub> | _    | 40   | 55   | μs                 |  |

|                                                  |                                    |                                                                                                                                      |                                                  | t <sub>SBYLO</sub> | _    | 40   | 55   | μs                 |  |

Note: When the division ratios of PCLKB, PCLKD, FCLK, and ICLK are all set to 1.

Note 1. The recovery time varies depending on the state of each oscillator when the WAIT instruction is executed. The recovery time when multiple oscillators are operating varies depending on the operating state of the oscillators that are not selected as the system clock source. This applies when only the oscillator listed in each item is operating and the other oscillators are stopped.

Note 2. When the frequency of the crystal is 20 MHz.

When the main clock oscillator wait control register (MOSCWTCR) is set to 04h. Note 3. When the frequency of the external clock is 20 MHz.

When the main clock oscillator wait control register (MOSCWTCR) is set to 00h.

Note 4. When the frequency of HOCO is 32 MHz. When the high-speed clock oscillator wait control register (HOCOWTCR) is set to 05h.

## Table 5.25 Timing of Recovery from Low Power Consumption Modes (2)

Conditions:  $1.8 \text{ V} \le \text{VCC} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVCC0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = 0 \text{ V}, \text{T}_a = -40 \text{ to } +105^{\circ}\text{C}$

| Item                                             |                                                                                          |                                                                      | Symbol                                           | Min.               | Тур. | Max. | Unit | Test<br>Conditions |  |

|--------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------|--------------------|------|------|------|--------------------|--|

| Recovery time<br>from software<br>standby mode*1 | Middle-speed Crystal Main clock oscillator<br>mode connected to main clock<br>oscillator |                                                                      | t <sub>SBYMC</sub>                               | _                  | 2    | 3    | ms   | Figure 5.28        |  |

|                                                  |                                                                                          | External clock<br>input to main<br>clock oscillator                  | Main clock oscillator<br>operating* <sup>3</sup> | t <sub>SBYEX</sub> | —    | 3    | 4    | μs                 |  |

|                                                  |                                                                                          | Sub-clock oscillato                                                  | or operating                                     | t <sub>SBYSC</sub> | —    | 600  | 750  | μs                 |  |

|                                                  |                                                                                          | HOCO clock oscillator operating*4<br>LOCO clock oscillator operating |                                                  | t <sub>SBYHO</sub> | _    | 40   | 50   | μs                 |  |

|                                                  |                                                                                          |                                                                      |                                                  | t <sub>SBYLO</sub> |      | 4.8  | 7    | μs                 |  |

Note: When the division ratios of PCLKB, PCLKD, FCLK, and ICLK are all set to 1.

Note 1. The recovery time varies depending on the state of each oscillator when the WAIT instruction is executed. The recovery time when multiple oscillators are operating varies depending on the operating state of the oscillators that are not selected as the system clock source. This applies when only the oscillator listed in each item is operating and the other oscillators are stopped.

Note 2. When the frequency of the crystal is 12 MHz.

When the main clock oscillator wait control register (MOSCWTCR) is set to 04h.

Note 3. When the frequency of the external clock is 12 MHz.

When the main clock oscillator wait control register (MOSCWTCR) is set to 00h. Note 4. When the frequency of HOCO is 8 MHz.

When the high-speed clock oscillator wait control register (HOCOWTCR) is set to 05h.

## Table 5.31 Timing of On-Chip Peripheral Modules (2)

Conditions:  $1.8 \text{ V} \le \text{VCC} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVCC0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}, \text{ C} = 30 \text{ pF}$

|                                 | Item   |                                                                   | Symbol                           | Min.                                                                     | Max.                                     | Unit                    | Test Condit |

|---------------------------------|--------|-------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------|------------------------------------------|-------------------------|-------------|

| RSPCK clock cycle               | Master |                                                                   | t <sub>SPcyc</sub>               | 2                                                                        | 4096                                     | t <sub>Pcyc</sub><br>*1 | Figure 5.39 |

|                                 | Slave  |                                                                   |                                  | 8                                                                        | 4096                                     | *1                      |             |

| RSPCK clock<br>high pulse width | Master |                                                                   | t <sub>SPCKWH</sub>              | (t <sub>SPcyc</sub> – t <sub>SPCKr</sub> –<br>t <sub>SPCKf</sub> )/2 – 3 |                                          | ns                      |             |

|                                 | Slave  |                                                                   |                                  | (t <sub>SPcyc</sub> – t <sub>SPCKr</sub> –<br>t <sub>SPCKf</sub> )/2     | —                                        |                         |             |

| RSPCK clock<br>low pulse width  | Master |                                                                   | t <sub>SPCKWL</sub>              | (t <sub>SPcyc</sub> – t <sub>SPCKr</sub> –<br>t <sub>SPCKf</sub> )/2 – 3 | —                                        | ns                      |             |

|                                 | Slave  |                                                                   |                                  | (t <sub>SPcyc</sub> – t <sub>SPCKr</sub> –<br>t <sub>SPCKf</sub> )/2     | —                                        |                         |             |

| RSPCK clock                     | Output | 2.7 V or above                                                    | t <sub>SPCKr,</sub>              | —                                                                        | 10                                       | ns                      | 1           |

| rise/fall time                  |        | 1.8 V or above                                                    | t <sub>SPCKf</sub>               | —                                                                        | 15                                       |                         |             |

|                                 | Input  |                                                                   |                                  |                                                                          | 1                                        | μs                      |             |

| Data input setup                | Master | 2.7 V or above                                                    | t <sub>SU</sub>                  | 10                                                                       | —                                        | ns                      | Figure 5.40 |

| time                            |        | 1.8 V or above                                                    |                                  | 30                                                                       | _                                        |                         | Figure 5.45 |

|                                 | Slave  | 1                                                                 | 1                                | 25 – t <sub>Pcyc</sub>                                                   | -                                        |                         |             |

| Data input hold time            | Master | RSPCK set to a division<br>ratio other than PCLKB<br>divided by 2 | t <sub>H</sub>                   | t <sub>Pcyc</sub>                                                        | _                                        | ns                      |             |

|                                 |        | RSPCK set to PCLKB divided by 2                                   | t <sub>HF</sub>                  | 0                                                                        | _                                        |                         |             |

|                                 | Slave  | I                                                                 | t <sub>H</sub>                   | 20 + 2 × t <sub>Pcyc</sub>                                               | _                                        |                         |             |

| SSL setup time                  | Master |                                                                   | t <sub>LEAD</sub>                | -30 + N*2 × t <sub>SPcyc</sub>                                           | —                                        | ns                      | 1           |

|                                 | Slave  |                                                                   |                                  | 2                                                                        | _                                        | t <sub>Pcyc</sub>       |             |

| SSL hold time                   | Master |                                                                   | t <sub>LAG</sub>                 | -30 + N* <sup>3</sup> × t <sub>SPcyc</sub>                               | _                                        | ns                      | 1           |

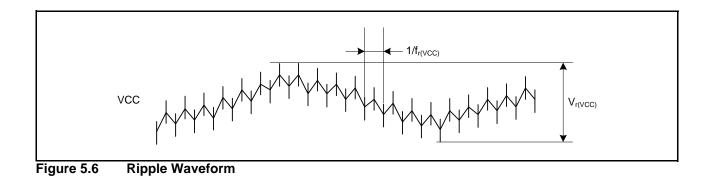

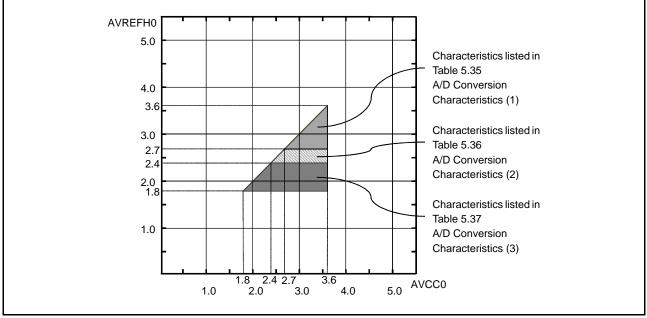

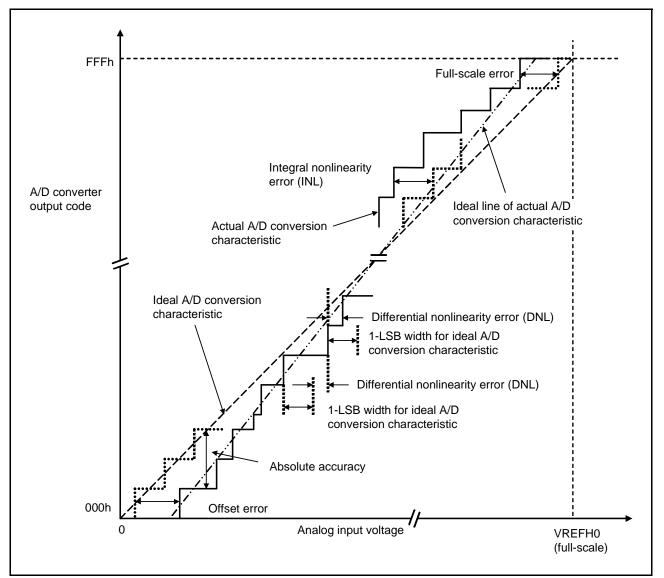

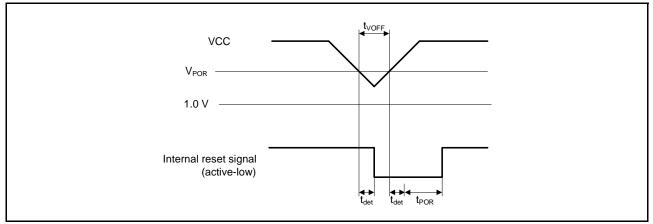

|                                 | Slave  |                                                                   |                                  | 2                                                                        | _                                        | t <sub>Pcyc</sub>       |             |