Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                            |

|----------------------------|--------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                     |

| Core Processor             | ARM® Cortex®-M4                                                                            |

| Core Size                  | 32-Bit Single-Core                                                                         |

| Speed                      | 80MHz                                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                                      |

| Number of I/O              | 51                                                                                         |

| Program Memory Size        | 256KB (256K x 8)                                                                           |

| Program Memory Type        | FLASH                                                                                      |

| EEPROM Size                | · ·                                                                                        |

| RAM Size                   | 128K x 8                                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                      |

| Oscillator Type            | Internal                                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                         |

| Mounting Type              | Surface Mount                                                                              |

| Package / Case             | 64-LQFP                                                                                    |

| Supplier Device Package    | 64-LQFP (10x10)                                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l475rct3                      |

|                            |                                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **3** Functional overview

# 3.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M4 core with FPU

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processor is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU 32-bit RISC processor features exceptional codeefficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution.

Its single precision FPU speeds up software development by using metalanguage development tools, while avoiding saturation.

With its embedded ARM core, the STM32L475xx family is compatible with all ARM tools and software.

*Figure 1* shows the general block diagram of the STM32L475xx family devices.

## 3.2 Adaptive real-time memory accelerator (ART Accelerator<sup>™</sup>)

The ART Accelerator<sup>™</sup> is a memory accelerator which is optimized for STM32 industrystandard ARM<sup>®</sup> Cortex<sup>®</sup>-M4 processors. It balances the inherent performance advantage of the ARM<sup>®</sup> Cortex<sup>®</sup>-M4 over Flash memory technologies, which normally requires the processor to wait for the Flash memory at higher frequencies.

To release the processor near 100 DMIPS performance at 80MHz, the accelerator implements an instruction prefetch queue and branch cache, which increases program execution speed from the 64-bit Flash memory. Based on CoreMark benchmark, the performance achieved thanks to the ART accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 80 MHz.

# 3.3 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

DocID027692 Rev 2

|          | Table 4. STM32L475 modes overview (continued) |                |       |                |            |                                                                                                                                              |                                                               |                                   |             |  |

|----------|-----------------------------------------------|----------------|-------|----------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------|-------------|--|

| Mode     | Regulator<br>(1)                              | CPU            | Flash | SRAM           | Clocks     | DMA & Peripherals <sup>(2)</sup>                                                                                                             | Wakeup source                                                 | Consumption <sup>(3)</sup>        | Wakeup time |  |

|          | LPR                                           |                |       | SRAM2<br>ON    |            | BOR, RTC, IWDG<br>***                                                                                                                        |                                                               | 0.35 μA w/o RTC<br>0.65 μA w/ RTC |             |  |

| Standby  | OFF                                           | Powered<br>Off | Off   | Powered<br>Off | LSE<br>LSI | All other peripherals are<br>powered off.<br>***<br>I/O configuration can be<br>floating, pull-up or pull-down                               | Reset pin<br>5 I/Os (WKUPx) <sup>(10)</sup><br>BOR, RTC, IWDG | 0.12 μA w/o RTC<br>0.42 μA w/ RTC | 14 µs       |  |

| Shutdown | OFF                                           | Powered<br>Off | Off   | Powered<br>Off | LSE        | RTC<br>***<br>All other peripherals are<br>powered off.<br>***<br>I/O configuration can be<br>floating, pull-up or pull-down <sup>(11)</sup> | Reset pin<br>5 I/Os (WKUPx) <sup>(10)</sup><br>RTC            | 0.03 μA w/o RTC<br>0.33 μA w/ RTC | 256 µs      |  |

1. LPR means Main regulator is OFF and Low-power regulator is ON.

2. All peripherals can be active or clock gated to save power consumption.

3. Typical current at V<sub>DD</sub> = 1.8 V, 25°C. Consumptions values provided running from SRAM, Flash memory Off, 80 MHz in Range 1, 26 MHz in Range 2, 2 MHz in LPRun/LPSleep.

4. The Flash memory can be put in power-down and its clock can be gated off when executing from SRAM.

5. The SRAM1 and SRAM2 clocks can be gated on or off independently.

6. U(S)ART and LPUART reception is functional in Stop mode, and generates a wakeup interrupt on Start, address match or received frame event.

7. I2C address detection is functional in Stop mode, and generates a wakeup interrupt in case of address match.

8. OTG\_FS wakeup by resume from suspend and attach detection protocol event.

9. SWPMI1 wakeup by resume from suspend.

10. The I/Os with wakeup from Standby/Shutdown capability are: PA0, PC13, PE6, PA2, PC5.

11. I/Os can be configured with internal pull-up, pull-down or floating in Shutdown mode but the configuration is lost when exiting the Shutdown mode.

23/193

Standby mode, supplied by the low-power Regulator (Standby with RAM2 retention mode).

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, WKUP pin event (configurable rising or falling edge), or an RTC event occurs (alarm, periodic wakeup, timestamp, tamper) or a failure is detected on LSE (CSS on LSE).

The system clock after wakeup is MSI up to 8 MHz.

Shutdown mode

The Shutdown mode allows to achieve the lowest power consumption. The internal regulator is switched off so that the VCORE domain is powered off. The PLL, the HSI16, the MSI, the LSI and the HSE oscillators are also switched off.

The RTC can remain active (Shutdown mode with RTC, Shutdown mode without RTC).

The BOR is not available in Shutdown mode. No power voltage monitoring is possible in this mode, therefore the switch to Backup domain is not supported.

SRAM1, SRAM2 and register contents are lost except for registers in the Backup domain.

The device exits Shutdown mode when an external reset (NRST pin), a WKUP pin event (configurable rising or falling edge), or an RTC event occurs (alarm, periodic wakeup, timestamp, tamper).

The system clock after wakeup is MSI at 4 MHz.

# 3.15 Analog to digital converter (ADC)

The device embeds 3 successive approximation analog-to-digital converters with the following features:

- 12-bit native resolution, with built-in calibration

- 5.33 Msps maximum conversion rate with full resolution

- Down to 18.75 ns sampling time

- Increased conversion rate for lower resolution (up to 8.88 Msps for 6-bit resolution)

- Up to 16 external channels, some of them shared between ADC1 and ADC2, or ADC1, ADC2 and ADC3.

- 5 Internal channels: internal reference voltage, temperature sensor, VBAT/3, DAC1 and DAC2 outputs.

- One external reference pin is available on some package, allowing the input voltage range to be independent from the power supply

- Single-ended and differential mode inputs

- Low-power design

- Capable of low-current operation at low conversion rate (consumption decreases linearly with speed)

- Dual clock domain architecture: ADC speed independent from CPU frequency

- Highly versatile digital interface

- Single-shot or continuous/discontinuous sequencer-based scan mode: 2 groups of analog signals conversions can be programmed to differentiate background and high-priority real-time conversions

- Handles two ADC converters for dual mode operation (simultaneous or interleaved sampling modes)

- Each ADC support multiple trigger inputs for synchronization with on-chip timers and external signals

- Results stored into 3 data register or in RAM with DMA controller support

- Data pre-processing: left/right alignment and per channel offset compensation

- Built-in oversampling unit for enhanced SNR

- Channel-wise programmable sampling time

- Three analog watchdog for automatic voltage monitoring, generating interrupts and trigger for selected timers

- Hardware assistant to prepare the context of the injected channels to allow fast context switching

## 3.15.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{TS}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC1\_IN17 and ADC3\_IN17 input channels which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

# 3.26 Universal synchronous/asynchronous receiver transmitter (USART)

The STM32L475xx devices have three embedded universal synchronous receiver transmitters (USART1, USART2 and USART3) and two universal asynchronous receiver transmitters (UART4, UART5).

These interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. They provide hardware management of the CTS and RTS signals, and RS485 Driver Enable. They are able to communicate at speeds of up to 10Mbit/s.

USART1, USART2 and USART3 also provide Smart Card mode (ISO 7816 compliant) and SPI-like communication capability.

All USART have a clock domain independent from the CPU clock, allowing the USARTx (x=1,2,3,4,5) to wake up the MCU from Stop mode using baudrates up to 200 Kbaud.The wake up events from Stop mode are programmable and can be:

- Start bit detection

- Any received data frame

- A specific programmed data frame

All USART interfaces can be served by the DMA controller.

| USART modes/features <sup>(1)</sup>   | USART1 | USART2 | USART3  | UART4     | UART5 | LPUART1 |

|---------------------------------------|--------|--------|---------|-----------|-------|---------|

| Hardware flow control for modem       | Х      | Х      | Х       | Х         | Х     | Х       |

| Continuous communication using DMA    | Х      | Х      | Х       | Х         | Х     | Х       |

| Multiprocessor communication          | Х      | Х      | Х       | Х         | Х     | Х       |

| Synchronous mode                      | Х      | Х      | Х       | -         | -     | -       |

| Smartcard mode                        | Х      | Х      | Х       | -         | -     | -       |

| Single-wire half-duplex communication | Х      | Х      | Х       | Х         | Х     | Х       |

| IrDA SIR ENDEC block                  | Х      | Х      | Х       | Х         | Х     | -       |

| LIN mode                              | Х      | Х      | Х       | Х         | Х     | -       |

| Dual clock domain                     | Х      | Х      | Х       | Х         | Х     | Х       |

| Wakeup from Stop 0 / Stop 1 modes     | Х      | Х      | Х       | Х         | Х     | Х       |

| Wakeup from Stop 2 mode               | -      | -      | -       | -         | -     | Х       |

| Receiver timeout interrupt            | Х      | Х      | Х       | Х         | Х     | -       |

| Modbus communication                  | Х      | Х      | Х       | Х         | Х     | -       |

| Auto baud rate detection X (4 modes)  |        |        |         | -         |       |         |

| Driver Enable                         | Х      | Х      | Х       | Х         | Х     | Х       |

| LPUART/USART data length              |        | •      | 7, 8 ar | nd 9 bits | •     | •       |

Table 12. STM32L475xx USART/UART/LPUART features

1. X = supported.

- Transmission

- Three transmit mailboxes

- Configurable transmit priority

- Reception

- Two receive FIFOs with three stages

- 14 Scalable filter banks

- Identifier list feature

- Configurable FIFO overrun

- Time-triggered communication option

- Disable automatic retransmission mode

- 16-bit free running timer

- Time Stamp sent in last two data bytes

- Management

- Maskable interrupts

- Software-efficient mailbox mapping at a unique address space

# 3.32 Secure digital input/output and MultiMediaCards Interface (SDMMC)

The card host interface (SDMMC) provides an interface between the APB peripheral bus and MultiMediaCards (MMCs), SD memory cards and SDIO cards.

The SDMMC features include the following:

- Full compliance with MultiMediaCard System Specification Version 4.2. Card support for three different databus modes: 1-bit (default), 4-bit and 8-bit

- Full compatibility with previous versions of MultiMediaCards (forward compatibility)

- Full compliance with SD Memory Card Specifications Version 2.0

- Full compliance with SD I/O Card Specification Version 2.0: card support for two different databus modes: 1-bit (default) and 4-bit

- Data transfer up to 48 MHz for the 8 bit mode

- Data write and read with DMA capability

# 3.33 Universal serial bus on-the-go full-speed (OTG\_FS)

The devices embed an USB OTG full-speed device/host/OTG peripheral with integrated transceivers. The USB OTG FS peripheral is compliant with the USB 2.0 specification and with the OTG 2.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG controller requires a dedicated 48 MHz clock that can be provided by the internal multispeed oscillator (MSI) automatically trimmed by 32.768 kHz external oscillator (LSE). This allows to use the USB device without external high speed crystal (HSE).

## 3.36 Development support

## 3.36.1 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

Debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

### 3.36.2 Embedded Trace Macrocell™

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32L475xx through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. Real-time instruction and data flow activity be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

| Table 15. STM32L475xx | pin definitions (continued) |

|-----------------------|-----------------------------|

|                       |                             |

|        | 'in<br>nber | Pin name                  |          | Ire           |       | Pin functions                                                                                                     |                             |

|--------|-------------|---------------------------|----------|---------------|-------|-------------------------------------------------------------------------------------------------------------------|-----------------------------|

| LQFP64 | LQFP100     | (function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                               | Additional functions        |

| 26     | 35          | PB0                       | I/O      | TT_a          | -     | TIM1_CH2N, TIM3_CH3,<br>TIM8_CH2N, USART3_CK,<br>QUADSPI_BK1_IO1,<br>COMP1_OUT, EVENTOUT                          | OPAMP2_<br>VOUT, ADC12_IN15 |

| 27     | 36          | PB1                       | I/O      | FT_a          | -     | TIM1_CH3N, TIM3_CH4,<br>TIM8_CH3N,<br>DFSDM_DATIN0,<br>USART3_RTS_DE,<br>QUADSPI_BK1_IO0,<br>LPTIM2_IN1, EVENTOUT | COMP1_INM, ADC12_IN16       |

| 28     | 37          | PB2                       | I/O      | FT_a          | -     | RTC_OUT, LPTIM1_OUT,<br>I2C3_SMBA, DFSDM_CKIN0,<br>EVENTOUT                                                       | COMP1_INP                   |

| -      | 38          | PE7                       | I/O      | FT            | -     | TIM1_ETR, DFSDM_DATIN2,<br>FMC_D4, SAI1_SD_B,<br>EVENTOUT                                                         | -                           |

| -      | 39          | PE8                       | I/O      | FT            | -     | TIM1_CH1N, DFSDM_CKIN2,<br>FMC_D5, SAI1_SCK_B,<br>EVENTOUT                                                        | -                           |

| -      | 40          | PE9                       | I/O      | FT            | -     | TIM1_CH1, DFSDM_CKOUT,<br>FMC_D6, SAI1_FS_B,<br>EVENTOUT                                                          | -                           |

| -      | 41          | PE10                      | I/O      | FT            | -     | TIM1_CH2N,<br>DFSDM_DATIN4,<br>TSC_G5_IO1, FMC_D7,<br>QUADSPI_CLK,<br>SAI1_MCLK_B, EVENTOUT                       | -                           |

| -      | 42          | PE11                      | I/O      | FT            | -     | TIM1_CH2, DFSDM_CKIN4,<br>TSC_G5_IO2,<br>QUADSPI_NCS, FMC_D8,<br>EVENTOUT                                         | -                           |

| -      | 43          | PE12                      | I/O      | FT            | -     | TIM1_CH3N, SPI1_NSS,<br>DFSDM_DATIN5,<br>TSC_G5_IO3,<br>QUADSPI_BK1_IO0,<br>FMC_D9, EVENTOUT                      | -                           |

| -      | 44          | PE13                      | I/O      | FT            | -     | TIM1_CH3, SPI1_SCK,<br>DFSDM_CKIN5,<br>TSC_G5_IO4,<br>QUADSPI_BK1_IO1,<br>FMC_D10, EVENTOUT                       | -                           |

| Table 15. | STM32L475xx | pin def | initions ( | (continued) | ) |

|-----------|-------------|---------|------------|-------------|---|

|           |             |         |            | oonnaca     | / |

|        | 'in<br>nber | Pin name                  |          | Ire           |       | Pin fun                                                                                                 | octions              |

|--------|-------------|---------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------------------------|----------------------|

| LQFP64 | LQFP100     | (function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                     | Additional functions |

| 50     | 77          | PA15 (JTDI)               | I/O      | FT            | (3)   | JTDI, TIM2_CH1, TIM2_ETR,<br>SPI1_NSS, SPI3_NSS,<br>UART4_RTS_DE,<br>TSC_G3_IO1, SAI2_FS_B,<br>EVENTOUT | -                    |

| 51     | 78          | PC10                      | I/O      | FT            | -     | SPI3_SCK, USART3_TX,<br>UART4_TX, TSC_G3_IO2,<br>SDMMC1_D2, SAI2_SCK_B,<br>EVENTOUT                     | -                    |

| 52     | 79          | PC11                      | I/O      | FT            | -     | SPI3_MISO, USART3_RX,<br>UART4_RX, TSC_G3_IO3,<br>SDMMC1_D3, SAI2_MCLK_B,<br>EVENTOUT                   | -                    |

| 53     | 80          | PC12                      | I/O      | FT            | -     | SPI3_MOSI, USART3_CK,<br>UART5_TX, TSC_G3_IO4,<br>SDMMC1_CK, SAI2_SD_B,<br>EVENTOUT                     | -                    |

| -      | 81          | PD0                       | I/O      | FT            | -     | SPI2_NSS, DFSDM_DATIN7,<br>CAN1_RX, FMC_D2,<br>EVENTOUT                                                 | -                    |

| -      | 82          | PD1                       | I/O      | FT            | -     | SPI2_SCK, DFSDM_CKIN7,<br>CAN1_TX, FMC_D3,<br>EVENTOUT                                                  | -                    |

| 54     | 83          | PD2                       | I/O      | FT            | -     | TIM3_ETR,<br>USART3_RTS_DE,<br>UART5_RX, TSC_SYNC,<br>SDMMC1_CMD, EVENTOUT                              | -                    |

| -      | 84          | PD3                       | I/O      | FT            | -     | SPI2_MISO, DFSDM_DATINO,<br>USART2_CTS, FMC_CLK,<br>EVENTOUT                                            | -                    |

| -      | 85          | PD4                       | I/O      | FT            | -     | SPI2_MOSI, DFSDM_CKIN0,<br>USART2_RTS_DE,<br>FMC_NOE, EVENTOUT                                          | -                    |

| -      | 86          | PD5                       | I/O      | FT            | -     | USART2_TX, FMC_NWE,<br>EVENTOUT                                                                         | -                    |

| -      | 87          | PD6                       | I/O      | FT            | -     | DFSDM_DATIN1,<br>USART2_RX, FMC_NWAIT,<br>SAI1_SD_A, EVENTOUT                                           | -                    |

| -      | 88          | PD7                       | I/O      | FT            | -     | DFSDM_CKIN1,<br>USART2_CK, FMC_NE1,<br>EVENTOUT                                                         | -                    |

| 10             |

|----------------|

| S              |

|                |

| ~              |

|                |

| ω              |

| N              |

|                |

| 4              |

| 1              |

| <b>σ</b>       |

| ×              |

| - <del>S</del> |

|                |

Pinouts and pin description

|        |      | AF0        | AF1                                | AF2                              | AF3       | AF4            | AF5       | AF6        | AF7                          |

|--------|------|------------|------------------------------------|----------------------------------|-----------|----------------|-----------|------------|------------------------------|

| Port   |      | SYS_AF     | TIM1/TIM2/<br>TIM5/TIM8/<br>LPTIM1 | TIM1/TIM2/<br>TIM3/TIM4/<br>TIM5 | TIM8      | 12C1/12C2/12C3 | SPI1/SPI2 | SPI3/DFSDM | USART1/<br>USART2/<br>USART3 |

|        | PA0  | -          | TIM2_CH1                           | TIM5_CH1                         | TIM8_ETR  | -              | -         | -          | USART2_CT                    |

|        | PA1  | -          | TIM2_CH2                           | TIM5_CH2                         | -         | -              | -         | -          | USART2_RT3<br>DE             |

|        | PA2  | -          | TIM2_CH3                           | TIM5_CH3                         | -         | -              | -         | -          | USART2_T                     |

|        | PA3  | -          | TIM2_CH4                           | TIM5_CH4                         | -         | -              | -         | -          | USART2_R                     |

|        | PA4  | -          | -                                  | -                                | -         | -              | SPI1_NSS  | SPI3_NSS   | USART2_C                     |

|        | PA5  | -          | TIM2_CH1                           | TIM2_ETR                         | TIM8_CH1N | -              | SPI1_SCK  | -          | -                            |

|        | PA6  | -          | TIM1_BKIN                          | TIM3_CH1                         | TIM8_BKIN | -              | SPI1_MISO | -          | USART3_C1                    |

|        | PA7  | -          | TIM1_CH1N                          | TIM3_CH2                         | TIM8_CH1N | -              | SPI1_MOSI | -          | -                            |

| Port A | PA8  | МСО        | TIM1_CH1                           | -                                | -         | -              | -         | -          | USART1_C                     |

|        | PA9  | -          | TIM1_CH2                           | -                                | -         | -              | -         | -          | USART1_T                     |

|        | PA10 | -          | TIM1_CH3                           | -                                | -         | -              | -         | -          | USART1_R                     |

|        | PA11 | -          | TIM1_CH4                           | TIM1_BKIN2                       | -         | -              | -         | -          | USART1_C                     |

|        | PA12 | -          | TIM1_ETR                           | -                                | -         | -              | -         | -          | USART1_RT<br>DE              |

|        | PA13 | JTMS-SWDIO | IR_OUT                             | -                                | -         | -              | -         | -          | -                            |

|        | PA14 | JTCK-SWCLK | -                                  | -                                | -         | -              | -         | -          | -                            |

|        | PA15 | JTDI       | TIM2_CH1                           | TIM2_ETR                         | -         | -              | SPI1_NSS  | SPI3_NSS   | -                            |

DocID027692 Rev 2

5

65/193

| Bus  | Boundary address          | Size<br>(bytes) | Peripheral |

|------|---------------------------|-----------------|------------|

|      | 0x4000 4000 - 0x4000 43FF | 1 KB            | Reserved   |

|      | 0x4000 3C00 - 0x4000 3FFF | 1 KB            | SPI3       |

|      | 0x4000 3800 - 0x4000 3BFF | 1 KB            | SPI2       |

|      | 0x4000 3400 - 0x4000 37FF | 1 KB            | Reserved   |

|      | 0x4000 3000 - 0x4000 33FF | 1 KB            | IWDG       |

|      | 0x4000 2C00 - 0x4000 2FFF | 1 KB            | WWDG       |

| APB1 | 0x4000 2800 - 0x4000 2BFF | 1 KB            | RTC        |

| AFDI | 0x4000 1800 - 0x4000 27FF | 4 KB            | Reserved   |

|      | 0x4000 1400 - 0x4000 17FF | 1 KB            | TIM7       |

|      | 0x4000 1000 - 0x4000 13FF | 1 KB            | TIM6       |

|      | 0x4000 0C00- 0x4000 0FFF  | 1 KB            | TIM5       |

|      | 0x4000 0800 - 0x4000 0BFF | 1 KB            | TIM4       |

|      | 0x4000 0400 - 0x4000 07FF | 1 KB            | ТІМЗ       |

|      | 0x4000 0000 - 0x4000 03FF | 1 KB            | TIM2       |

| Table 18. STM32L475xx memory map and peripheral register boundary |

|-------------------------------------------------------------------|

| addresses (continued) <sup>(1)</sup>                              |

1. The gray color is used for reserved boundary addresses.

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 48 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 46*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| <b>a a a a a a a a a a</b> |                                           |                                                           |     |      |     |      |  |  |  |

|----------------------------|-------------------------------------------|-----------------------------------------------------------|-----|------|-----|------|--|--|--|

| Symbol                     | Parameter                                 | Conditions <sup>(2)</sup>                                 | Min | Тур  | Мах | Unit |  |  |  |

| f <sub>OSC_IN</sub>        | Oscillator frequency                      | -                                                         | 4   | 8    | 48  | MHz  |  |  |  |

| R <sub>F</sub>             | Feedback resistor                         | -                                                         | -   | 200  | -   | kΩ   |  |  |  |

| 1                          |                                           | During startup <sup>(3)</sup>                             | -   | -    | 5.5 |      |  |  |  |

|                            |                                           | V <sub>DD</sub> = 3 V,<br>Rm = 30 Ω,<br>CL = 10 pF@8 MHz  | -   | 0.44 | -   |      |  |  |  |

| I <sub>DD(HSE)</sub>       | HSE current consumption                   | V <sub>DD</sub> = 3 V,<br>Rm = 45 Ω,<br>CL = 10 pF@8 MHz  | -   | 0.45 | -   |      |  |  |  |

|                            |                                           | V <sub>DD</sub> = 3 V,<br>Rm = 30 Ω,<br>CL = 5 pF@48 MHz  | -   | 0.68 | -   | mA   |  |  |  |

|                            |                                           | V <sub>DD</sub> = 3 V,<br>Rm = 30 Ω,<br>CL = 10 pF@48 MHz | -   | 0.94 | -   |      |  |  |  |

|                            |                                           | V <sub>DD</sub> = 3 V,<br>Rm = 30 Ω,<br>CL = 20 pF@48 MHz | -   | 1.77 | -   |      |  |  |  |

| G <sub>m</sub>             | Maximum critical crystal transconductance | Startup                                                   | -   | -    | 1.5 | mA/V |  |  |  |

| $t_{\rm SU(HSE)}^{(4)}$    | Startup time                              | V <sub>DD</sub> is stabilized                             | -   | 2    | -   | ms   |  |  |  |

| Table 46. HSE oscillator characteristics <sup>(1</sup> |

|--------------------------------------------------------|

|--------------------------------------------------------|

1. Guaranteed by design.

2. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

3. This consumption level occurs during the first 2/3 of the  $t_{SU(\text{HSE})}$  startup time

4. t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 20 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 15*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

| Symbol                     | Parameter                         |                   | Conditions                     | Min  | Тур     | Max   | Unit  |

|----------------------------|-----------------------------------|-------------------|--------------------------------|------|---------|-------|-------|

|                            |                                   |                   | Range 0                        | 99   | 100     | 101   |       |

|                            |                                   |                   | Range 1                        | 198  | 200     | 202   |       |

|                            |                                   |                   | Range 2                        | 396  | 400     | 404   | - kHz |

|                            |                                   |                   | Range 3                        | 792  | 800     | 808   |       |

|                            |                                   |                   | Range 4                        | 0.99 | 1       | 1.01  |       |

|                            |                                   | MSI mode          | Range 5                        | 1.98 | 2       | 2.02  |       |

|                            |                                   | INISI MODE        | Range 6                        | 3.96 | 4       | 4.04  |       |

|                            |                                   |                   | Range 7                        | 7.92 | 8       | 8.08  | MHz   |

|                            |                                   |                   | Range 8                        | 15.8 | 16      | 16.16 |       |

|                            |                                   |                   | Range 9                        | 23.8 | 24      | 24.4  | -     |

|                            | MSI frequency                     |                   | Range 10                       | 31.7 | 32      | 32.32 |       |

| f                          | after factory calibration, done   |                   | Range 11                       | 47.5 | 48      | 48.48 |       |

| f <sub>MSI</sub>           | at $V_{DD}$ =3 V and $T_A$ =30 °C |                   | Range 0                        | -    | 98.304  | -     | - kHz |

|                            |                                   |                   | Range 1                        | -    | 196.608 | -     |       |

|                            |                                   |                   | Range 2                        | -    | 393.216 | -     |       |

|                            |                                   |                   | Range 3                        | -    | 786.432 | -     |       |

|                            |                                   |                   | Range 4                        | -    | 1.016   | -     |       |

|                            |                                   | PLL mode<br>XTAL= | Range 5                        | -    | 1.999   | -     |       |

|                            |                                   | 32.768 kHz        | Range 6                        | -    | 3.998   | -     | - MHz |

|                            |                                   |                   | Range 7                        | -    | 7.995   | -     |       |

|                            |                                   |                   | Range 8                        | -    | 15.991  | -     |       |

|                            |                                   |                   | Range 9                        | -    | 23.986  | -     |       |

|                            |                                   |                   | Range 10                       | -    | 32.014  | -     |       |

|                            |                                   |                   | Range 11                       | -    | 48.005  | -     |       |

| (r (2)                     | MSI oscillator                    |                   | T <sub>A</sub> = -0 to 85 °C   | -3.5 | -       | 3     |       |

| $\Delta_{TEMP}(MSI)^{(2)}$ | frequency drift over temperature  | MSI mode          | T <sub>A</sub> = -40 to 125 °C | -8   | -       | 6     | %     |

#### Table 49. MSI oscillator characteristics<sup>(1)</sup>

#### **Electrical characteristics**

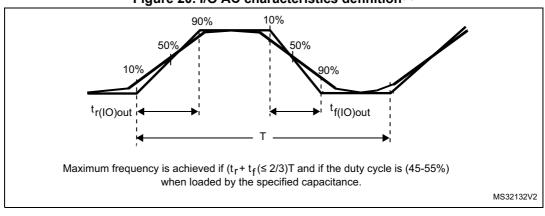

| Speed | Symbol | Parameter                       | Conditions                                 | Min | Max | Unit                                     |   |   |  |

|-------|--------|---------------------------------|--------------------------------------------|-----|-----|------------------------------------------|---|---|--|

|       |        |                                 |                                            |     |     | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V | - | 5 |  |

|       |        |                                 | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 1   |                                          |   |   |  |

|       | Fmax   | Maximum frequency               | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 0.1 | MHz                                      |   |   |  |

|       | FIIIdX | Maximum requency                | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 10  |                                          |   |   |  |

|       |        |                                 | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 1.5 |                                          |   |   |  |

| 00    |        |                                 | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 0.1 |                                          |   |   |  |

| 00    |        |                                 | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 25  |                                          |   |   |  |

|       |        |                                 | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 52  |                                          |   |   |  |

|       | Tr/Tf  | Output rise and fall time       | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 140 | ns                                       |   |   |  |

|       | 11/11  |                                 | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 17  |                                          |   |   |  |

|       |        |                                 | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 37  |                                          |   |   |  |

|       |        |                                 | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 110 |                                          |   |   |  |

|       |        |                                 | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 25  |                                          |   |   |  |

|       |        |                                 | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 10  |                                          |   |   |  |

|       | Fmax   | Maximum frequency               | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 1   | MHz                                      |   |   |  |

|       | Filldx | Maximum nequency                | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 50  |                                          |   |   |  |

|       |        |                                 | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 15  |                                          |   |   |  |

| 01    |        |                                 | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 1   |                                          |   |   |  |

| 01    |        |                                 | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 9   |                                          |   |   |  |

|       |        | Tutte Output days and fall time | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 16  |                                          |   |   |  |

|       | Tr/Tf  |                                 | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 40  |                                          |   |   |  |

|       | 11/11  | Output rise and fall time       | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 4.5 | ns                                       |   |   |  |

|       |        |                                 | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 9   |                                          |   |   |  |

|       |        |                                 | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 21  |                                          |   |   |  |

| Table 61 | . I/O AC | characteristics <sup>(1)(2)</sup> |

|----------|----------|-----------------------------------|

|----------|----------|-----------------------------------|

1. Refer to Table 61: I/O AC characteristics.

## 6.3.15 NRST pin characteristics

The NRST pin input driver uses the CMOS technology. It is connected to a permanent pull-up resistor,  $\mathsf{R}_{\mathsf{PU}}.$

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 22: General operating conditions*.

| Symbol                 | Parameter                                          | Conditions                        | Min                                 | Тур | Max                                 | Unit |

|------------------------|----------------------------------------------------|-----------------------------------|-------------------------------------|-----|-------------------------------------|------|

| V <sub>IL(NRST)</sub>  | NRST input low level voltage                       | -                                 | -                                   | -   | 0.3 <sub>x</sub> V <sub>DDIOx</sub> | v    |

| V <sub>IH(NRST)</sub>  | NRST input high level voltage                      | -                                 | 0.7 <sub>x</sub> V <sub>DDIOx</sub> | -   | -                                   | v    |

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage hysteresis            | -                                 | -                                   | 200 | -                                   | mV   |

| R <sub>PU</sub>        | Weak pull-up<br>equivalent resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                                  | 40  | 55                                  | kΩ   |

| V <sub>F(NRST)</sub>   | NRST input filtered<br>pulse                       | -                                 | -                                   | -   | 70                                  | ns   |

| V <sub>NF(NRST)</sub>  | NRST input not filtered pulse                      | 1.71 V ≤ V <sub>DD</sub> ≤ 3.6 V  | 350                                 | -   | -                                   | ns   |

Table 62. NRST pin characteristics<sup>(1)</sup>

1. Guaranteed by design.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

| Peoplution | Sampling cycle | Sampling time [ns] | RAIN max (Ω)                 |                              |  |  |

|------------|----------------|--------------------|------------------------------|------------------------------|--|--|

| Resolution | @80 MHz        | @80 MHz            | Fast channels <sup>(3)</sup> | Slow channels <sup>(4)</sup> |  |  |

|            | 2.5            | 31.25              | 220                          | N/A                          |  |  |

|            | 6.5            | 81.25              | 560                          | 330                          |  |  |

|            | 12.5           | 156.25             | 1200                         | 1000                         |  |  |

| 6 bits     | 24.5           | 306.25             | 2700                         | 2200                         |  |  |

| 0 013      | 47.5           | 593.75             | 3900                         | 3300                         |  |  |

|            | 92.5           | 1156.25            | 8200                         | 6800                         |  |  |

|            | 247.5          | 3093.75            | 18000                        | 15000                        |  |  |

|            | 640.5          | 8006.75            | 50000                        | 50000                        |  |  |

# Table 65. Maximum ADC RAIN<sup>(1)(2)</sup> (continued)

1. Guaranteed by design.

2. The I/O analog switch voltage booster is enable when V<sub>DDA</sub> < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when V<sub>DDA</sub> < 2.4V). It is disable when V<sub>DDA</sub>  $\geq$  2.4 V.

3. Fast channels are: PC0, PC1, PC2, PC3, PA0, PA1.

4. Slow channels are: all ADC inputs except the fast channels.

#### 3. Refer to Table 59: I/O static characteristics.

4. Ton is the Refresh phase duration. Toff is the Hold phase duration. Refer to RM0395 reference manual for more details.

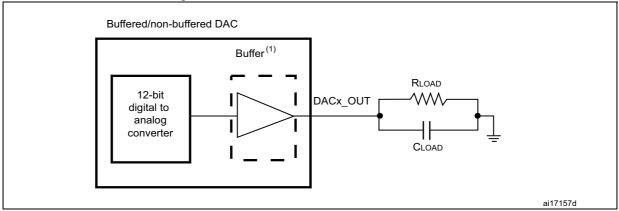

#### Figure 24. 12-bit buffered / non-buffered DAC

1. The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

| Symbol    | Parameter                                          | Conditio                                              | Min                       | Тур        | Max | Unit |     |

|-----------|----------------------------------------------------|-------------------------------------------------------|---------------------------|------------|-----|------|-----|

| DNL       | Differential non                                   | DAC output buffer ON                                  |                           | -          | -   | ±2   |     |

| DINL      | linearity <sup>(2)</sup>                           | DAC output buffer OFF                                 |                           | -          | -   | ±2   |     |

| -         | monotonicity                                       | 10 bits                                               |                           | guaranteed |     | d    |     |

| INL       | Integral non                                       | DAC output buffer ON<br>CL ≤ 50 pF, RL ≥ 5 kΩ         |                           | -          | -   | ±4   |     |

| INL       | linearity <sup>(3)</sup>                           | DAC output buffer OFF<br>CL ≤ 50 pF, no RL            |                           | -          | -   | ±4   |     |

|           |                                                    |                                                       | V <sub>REF+</sub> = 3.6 V | -          | -   | ±12  |     |

| Offset    | Offset Offset error at code 0x800 <sup>(3)</sup>   |                                                       | V <sub>REF+</sub> = 1.8 V | -          | -   | ±25  | LSB |

|           |                                                    | DAC output buffer OFF<br>CL ≤ 50 pF, no RL            |                           | -          | -   | ±8   |     |

| Offset1   | Offset error at code 0x001 <sup>(4)</sup>          | DAC output buffer OFF $CL \leq 50 \text{ pF}$ , no RL |                           | -          | -   | ±5   |     |

| OffsetCal | Offset Error at<br>code 0x800<br>after calibration | Dx800 DAC output buffer ON<br>CL < 50 pF RL > 5 kO    | V <sub>REF+</sub> = 3.6 V | -          | -   | ±5   |     |

| Unserval  |                                                    |                                                       | V <sub>REF+</sub> = 1.8 V | -          | -   | ±7   |     |

## Table 71. DAC accuracy<sup>(1)</sup>

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

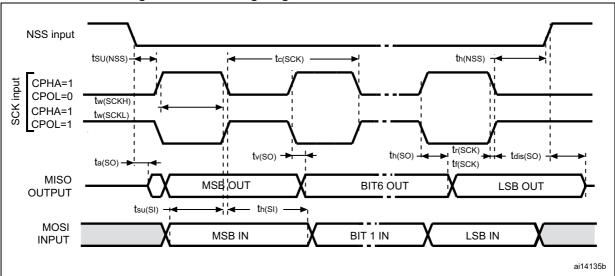

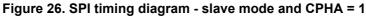

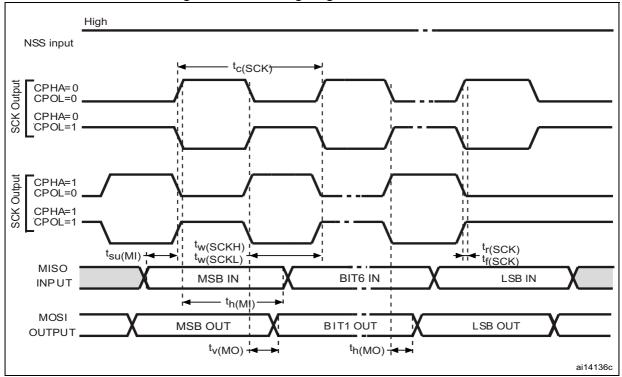

#### Figure 27. SPI timing diagram - master mode

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

DocID027692 Rev 2

In all timing tables, the  $T_{\mbox{HCLK}}$  is the HCLK clock period.

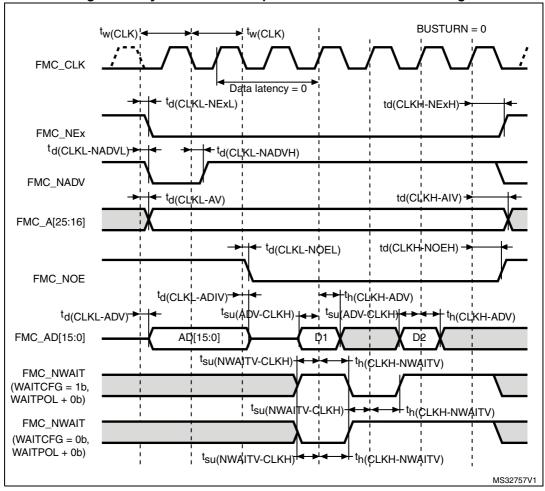

Figure 36. Synchronous multiplexed NOR/PSRAM read timings

| Cumhal |        | millimeters |        | inches <sup>(1)</sup> |        |        |

|--------|--------|-------------|--------|-----------------------|--------|--------|

| Symbol | Min    | Тур         | Мах    | Min                   | Тур    | Max    |

| А      | -      | -           | 1.600  | -                     | -      | 0.0630 |

| A1     | 0.050  | -           | 0.150  | 0.0020                | -      | 0.0059 |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170  | 0.220       | 0.270  | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090  | -           | 0.200  | 0.0035                | -      | 0.0079 |

| D      | 15.800 | 16.000      | 16.200 | 0.6220                | 0.6299 | 0.6378 |

| D1     | 13.800 | 14.000      | 14.200 | 0.5433                | 0.5512 | 0.5591 |

| D3     | -      | 12.000      | -      | -                     | 0.4724 | -      |

| Е      | 15.800 | 16.000      | 16.200 | 0.6220                | 0.6299 | 0.6378 |

| E1     | 13.800 | 14.000      | 14.200 | 0.5433                | 0.5512 | 0.5591 |

| E3     | -      | 12.000      | -      | -                     | 0.4724 | -      |

| е      | -      | 0.500       | -      | -                     | 0.0197 | -      |

| L      | 0.450  | 0.600       | 0.750  | 0.0177                | 0.0236 | 0.0295 |

| L1     | -      | 1.000       | -      | -                     | 0.0394 | -      |

| k      | 0.0°   | 3.5°        | 7.0°   | 0.0°                  | 3.5°   | 7.0°   |

| CCC    | -      | -           | 0.080  | -                     | -      | 0.0031 |

| Table 96. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package |

|-----------------------------------------------------------------------|

| mechanical data                                                       |

1. Values in inches are converted from mm and rounded to 4 decimal digits.