Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detano                     |                                                                                            |

|----------------------------|--------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                     |

| Core Processor             | ARM® Cortex®-M4                                                                            |

| Core Size                  | 32-Bit Single-Core                                                                         |

| Speed                      | 80MHz                                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                                      |

| Number of I/O              | 51                                                                                         |

| Program Memory Size        | 512KB (512K x 8)                                                                           |

| Program Memory Type        | FLASH                                                                                      |

| EEPROM Size                | -                                                                                          |

| RAM Size                   | 128K x 8                                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                      |

| Oscillator Type            | Internal                                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                          |

| Mounting Type              | Surface Mount                                                                              |

| Package / Case             | 64-LQFP                                                                                    |

| Supplier Device Package    | 64-LQFP (10x10)                                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l475ret6                      |

|                            |                                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 6 | Electrical characteristics |         |                                                                                           |  |  |  |  |  |  |  |  |

|---|----------------------------|---------|-------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|   | 6.1                        | Parame  | eter conditions                                                                           |  |  |  |  |  |  |  |  |

|   |                            | 6.1.1   | Minimum and maximum values                                                                |  |  |  |  |  |  |  |  |

|   |                            | 6.1.2   | Typical values                                                                            |  |  |  |  |  |  |  |  |

|   |                            | 6.1.3   | Typical curves                                                                            |  |  |  |  |  |  |  |  |

|   |                            | 6.1.4   | Loading capacitor                                                                         |  |  |  |  |  |  |  |  |

|   |                            | 6.1.5   | Pin input voltage                                                                         |  |  |  |  |  |  |  |  |

|   |                            | 6.1.6   | Power supply scheme                                                                       |  |  |  |  |  |  |  |  |

|   |                            | 6.1.7   | Current consumption measurement                                                           |  |  |  |  |  |  |  |  |

|   | 6.2                        | Absolut | te maximum ratings                                                                        |  |  |  |  |  |  |  |  |

|   | 6.3                        | Operati | ing conditions                                                                            |  |  |  |  |  |  |  |  |

|   |                            | 6.3.1   | General operating conditions                                                              |  |  |  |  |  |  |  |  |

|   |                            | 6.3.2   | Operating conditions at power-up / power-down                                             |  |  |  |  |  |  |  |  |

|   |                            | 6.3.3   | Embedded reset and power control block characteristics                                    |  |  |  |  |  |  |  |  |

|   |                            | 6.3.4   | Embedded voltage reference                                                                |  |  |  |  |  |  |  |  |

|   |                            | 6.3.5   | Supply current characteristics                                                            |  |  |  |  |  |  |  |  |

|   |                            | 6.3.6   | Wakeup time from low-power modes and voltage scaling         transition times         108 |  |  |  |  |  |  |  |  |

|   |                            | 6.3.7   | External clock source characteristics                                                     |  |  |  |  |  |  |  |  |

|   |                            | 6.3.8   | Internal clock source characteristics                                                     |  |  |  |  |  |  |  |  |

|   |                            | 6.3.9   | PLL characteristics                                                                       |  |  |  |  |  |  |  |  |

|   |                            | 6.3.10  | Flash memory characteristics                                                              |  |  |  |  |  |  |  |  |

|   |                            | 6.3.11  | EMC characteristics                                                                       |  |  |  |  |  |  |  |  |

|   |                            | 6.3.12  | Electrical sensitivity characteristics                                                    |  |  |  |  |  |  |  |  |

|   |                            | 6.3.13  | I/O current injection characteristics                                                     |  |  |  |  |  |  |  |  |

|   |                            | 6.3.14  | I/O port characteristics                                                                  |  |  |  |  |  |  |  |  |

|   |                            | 6.3.15  | NRST pin characteristics                                                                  |  |  |  |  |  |  |  |  |

|   |                            | 6.3.16  | Analog switches booster                                                                   |  |  |  |  |  |  |  |  |

|   |                            | 6.3.17  | Analog-to-Digital converter characteristics                                               |  |  |  |  |  |  |  |  |

|   |                            | 6.3.18  | Digital-to-Analog converter characteristics                                               |  |  |  |  |  |  |  |  |

|   |                            | 6.3.19  | Voltage reference buffer characteristics                                                  |  |  |  |  |  |  |  |  |

|   |                            | 6.3.20  | Comparator characteristics                                                                |  |  |  |  |  |  |  |  |

|   |                            | 6.3.21  | Operational amplifiers characteristics                                                    |  |  |  |  |  |  |  |  |

|   |                            | 6.3.22  | Temperature sensor characteristics                                                        |  |  |  |  |  |  |  |  |

|   |                            | 6.3.23  | V <sub>BAT</sub> monitoring characteristics                                               |  |  |  |  |  |  |  |  |

|   |                            | 6.3.24  | DFSDM characteristics                                                                     |  |  |  |  |  |  |  |  |

|   |                            | 6.3.25  | Timer characteristics                                                                     |  |  |  |  |  |  |  |  |

DocID027692 Rev 2

# 2 Description

The STM32L475xx devices are the ultra-low-power microcontrollers based on the highperformance ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core operating at a frequency of up to 80 MHz. The Cortex-M4 core features a Floating point unit (FPU) single precision which supports all ARM single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

The STM32L475xx devices embed high-speed memories (Flash memory up to 1 Mbyte, up to 128 Kbyte of SRAM), a flexible external memory controller (FSMC) for static memories (for devices with 100 pins package), a Quad SPI flash memories interface (available on all packages) and an extensive range of enhanced I/Os and peripherals connected to two APB buses, two AHB buses and a 32-bit multi-AHB bus matrix.

The STM32L475xx devices embed several protection mechanisms for embedded Flash memory and SRAM: readout protection, write protection, proprietary code readout protection and Firewall.

The devices offer up to three fast 12-bit ADCs (5 Msps), two comparators, two operational amplifiers, two DAC channels, an internal voltage reference buffer, a low-power RTC, two general-purpose 32-bit timer, two 16-bit PWM timers dedicated to motor control, seven general-purpose 16-bit timers, and two 16-bit low-power timers. The devices support four digital filters for external sigma delta modulators (DFSDM).

In addition, up to 21 capacitive sensing channels are available.

They also feature standard and advanced communication interfaces.

- Three I2Cs

- Three SPIs

- Three USARTs, two UARTs and one Low-Power UART.

- Two SAIs (Serial Audio Interfaces)

- One SDMMC

- One CAN

- One USB OTG full-speed

- One SWPMI (Single Wire Protocol Master Interface)

The STM32L475xx operates in the -40 to +85  $^{\circ}$ C (+105  $^{\circ}$ C junction), -40 to +105  $^{\circ}$ C (+125  $^{\circ}$ C junction) and -40 to +125  $^{\circ}$ C (+130  $^{\circ}$ C junction) temperature ranges from a 1.71 to 3.6 V power supply. A comprehensive set of power-saving modes allows the design of low-power applications.

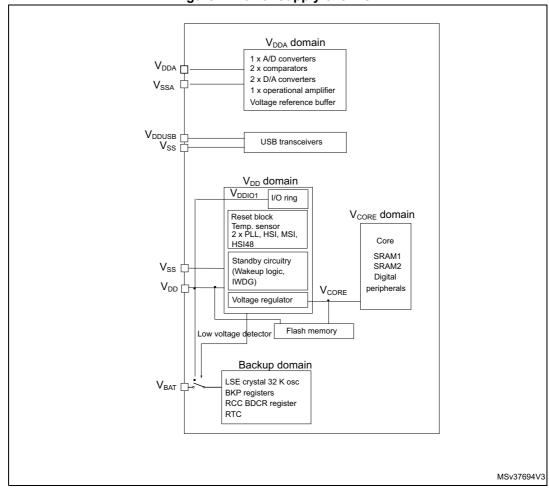

Some independent power supplies are supported: analog independent supply input for ADC, DAC, OPAMPs and comparators, 3.3 V dedicated supply input for USB and up to 14 I/Os can be supplied independently down to 1.08V<sub>-</sub> A VBAT input allows to backup the RTC and backup registers.

The STM32L475xx family offers two packages from 64-pin to 100-pin packages.

Figure 2. Power supply overview

## 3.9.2 Power supply supervisor

The device has an integrated ultra-low-power brown-out reset (BOR) active in all modes except Shutdown and ensuring proper operation after power-on and during power down. The device remains in reset mode when the monitored supply voltage  $V_{DD}$  is below a specified threshold, without the need for an external reset circuit.

The lowest BOR level is 1.71V at power on, and other higher thresholds can be selected through option bytes. The device features an embedded programmable voltage detector (PVD) that monitors the V<sub>DD</sub> power supply and compares it to the VPVD threshold. An interrupt can be generated when V<sub>DD</sub> drops below the VPVD threshold and/or when V<sub>DD</sub> is higher than the VPVD threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

In addition, the devices embeds a Peripheral Voltage Monitor which compares the independent supply voltages  $V_{DDA}$ ,  $V_{DDUSB}$  with a fixed threshold in order to ensure that the peripheral is in its functional supply range.

By default, the microcontroller is in Run mode after a system or a power Reset. It is up to the user to select one of the low-power modes described below:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Low-power run mode

This mode is achieved with VCORE supplied by the low-power regulator to minimize the regulator's operating current. The code can be executed from SRAM or from Flash, and the CPU frequency is limited to 2 MHz. The peripherals with independent clock can be clocked by HSI16.

• Low-power sleep mode

This mode is entered from the low-power run mode. Only the CPU clock is stopped. When wakeup is triggered by an event or an interrupt, the system reverts to the lowpower run mode.

• Stop 0, Stop 1 and Stop 2 modes

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the VCORE domain are stopped, the PLL, the MSI RC, the HSI16 RC and the HSE crystal oscillators are disabled. The LSE or LSI is still running.

The RTC can remain active (Stop mode with RTC, Stop mode without RTC).

Some peripherals with wakeup capability can enable the HSI16 RC during Stop mode to detect their wakeup condition.

Three Stop modes are available: Stop 0, Stop 1 and Stop 2 modes. In Stop 2 mode, most of the VCORE domain is put in a lower leakage mode.

Stop 1 offers the largest number of active peripherals and wakeup sources, a smaller wakeup time but a higher consumption than Stop 2. In Stop 0 mode, the main regulator remains ON, allowing a very fast wakeup time but with much higher consumption.

The system clock when exiting from Stop 0, Stop1 or Stop2 modes can be either MSI up to 48 MHz or HSI16, depending on software configuration.

• Standby mode

The Standby mode is used to achieve the lowest power consumption with BOR. The internal regulator is switched off so that the VCORE domain is powered off. The PLL, the MSI RC, the HSI16 RC and the HSE crystal oscillators are also switched off.

The RTC can remain active (Standby mode with RTC, Standby mode without RTC).

The brown-out reset (BOR) always remains active in Standby mode.

The state of each I/O during standby mode can be selected by software: I/O with internal pull-up, internal pull-down or floating.

After entering Standby mode, SRAM1 and register contents are lost except for registers in the Backup domain and Standby circuitry. Optionally, SRAM2 can be retained in

# 3.27 Low-power universal asynchronous receiver transmitter (LPUART)

The device embeds one Low-Power UART. The LPUART supports asynchronous serial communication with minimum power consumption. It supports half duplex single wire communication and modem operations (CTS/RTS). It allows multiprocessor communication.

The LPUART has a clock domain independent from the CPU clock, and can wakeup the system from Stop mode using baudrates up to 220 Kbaud. The wake up events from Stop mode are programmable and can be:

- Start bit detection

- Any received data frame

- A specific programmed data frame

Only a 32.768 kHz clock (LSE) is needed to allow LPUART communication up to 9600 baud. Therefore, even in Stop mode, the LPUART can wait for an incoming frame while having an extremely low energy consumption. Higher speed clock can be used to reach higher baudrates.

LPUART interface can be served by the DMA controller.

| Table 15, ST | M32L475xx r  | oin definitions | (continued) |

|--------------|--------------|-----------------|-------------|

|              | MOLLTI OAA P |                 | (continueu) |

|        | in<br>nber | Pin name                     |          | er            |            | Pin fur                                                                            | ictions                                    |

|--------|------------|------------------------------|----------|---------------|------------|------------------------------------------------------------------------------------|--------------------------------------------|

| LQFP64 | LQFP100    | (function after reset)       | Pin type | I/O structure | Notes      | Alternate functions                                                                | Additional functions                       |

| -      | 4          | PE5                          | I/O      | FT            | -          | TRACED2, TIM3_CH3,<br>DFSDM_CKIN3,<br>TSC_G7_IO4, FMC_A21,<br>SAI1_SCK_A, EVENTOUT | -                                          |

| -      | 5          | PE6                          | I/O      | FT            | -          | TRACED3, TIM3_CH4,<br>FMC_A22, SAI1_SD_A,<br>EVENTOUT                              | RTC_TAMP3/<br>WKUP3                        |

| 1      | 6          | VBAT                         | S        | -             | -          | -                                                                                  | -                                          |

| 2      | 7          | PC13                         | I/O      | FT            | (1)<br>(2) | EVENTOUT                                                                           | RTC_TAMP1/<br>RTC_TS/<br>RTC_OUT/<br>WKUP2 |

| 3      | 8          | PC14-<br>OSC32_IN<br>(PC14)  | I/O      | FT            | (1)<br>(2) | EVENTOUT                                                                           | OSC32_IN                                   |

| 4      | 9          | PC15-<br>OSC32_OUT<br>(PC15) | I/O      | FT            | (1)<br>(2) | EVENTOUT                                                                           | OSC32_OUT                                  |

| -      | 10         | VSS                          | S        | -             | -          | -                                                                                  | -                                          |

| -      | 11         | VDD                          | S        | -             | -          | -                                                                                  | -                                          |

| 5      | 12         | PH0-OSC_IN<br>(PH0)          | I/O      | FT            | -          | EVENTOUT                                                                           | OSC_IN                                     |

| 6      | 13         | PH1-OSC_OUT<br>(PH1)         | I/O      | FT            | -          | EVENTOUT                                                                           | OSC_OUT                                    |

| 7      | 14         | NRST                         | I/O      | RST           | -          | -                                                                                  | -                                          |

| 8      | 15         | PC0                          | I/O      | FT_fa         | -          | LPTIM1_IN1, I2C3_SCL,<br>DFSDM_DATIN4,<br>LPUART1_RX, LPTIM2_IN1,<br>EVENTOUT      | ADC123_IN1                                 |

| 9      | 16         | PC1                          | I/O      | FT_fa         | -          | LPTIM1_OUT, I2C3_SDA,<br>DFSDM_CKIN4,<br>LPUART1_TX, EVENTOUT                      | ADC123_IN2                                 |

| 10     | 17         | PC2                          | I/O      | FT_a          | -          | LPTIM1_IN2, SPI2_MISO,<br>DFSDM_CKOUT, EVENTOUT                                    | ADC123_IN3                                 |

| 11     | 18         | PC3                          | I/O      | FT_a          | -          | LPTIM1_ETR, SPI2_MOSI,<br>SAI1_SD_A, LPTIM2_ETR,<br>EVENTOUT                       | ADC123_IN4                                 |

| -      | 19         | VSSA                         | S        | -             | -          | -                                                                                  | -                                          |

| -      | 20         | VREF-                        | S        | -             | -          | -                                                                                  | -                                          |

| Table 15. STM32L475xx | pin definitions | (continued) |

|-----------------------|-----------------|-------------|

|                       |                 | (ooninaoa)  |

|        | 'in<br>nber | Pin name               |          | Ire           |       | Pin fun                                                                                                                                           | ictions              |

|--------|-------------|------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| LQFP64 | LQFP100     | (function after reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                                               | Additional functions |

| 35     | 53          | PB14                   | I/O      | FT_f          | -     | TIM1_CH2N, TIM8_CH2N,<br>I2C2_SDA, SPI2_MISO,<br>DFSDM_DATIN2,<br>USART3_RTS_DE,<br>TSC_G1_IO3, SWPMI1_RX,<br>SAI2_MCLK_A, TIM15_CH1,<br>EVENTOUT | -                    |

| 36     | 54          | PB15                   | I/O      | FT            | _     | RTC_REFIN, TIM1_CH3N,<br>TIM8_CH3N, SPI2_MOSI,<br>DFSDM_CKIN2,<br>TSC_G1_IO4,<br>SWPMI1_SUSPEND,<br>SAI2_SD_A, TIM15_CH2,<br>EVENTOUT             | -                    |

| -      | 55          | PD8                    | I/O      | FT            | -     | USART3_TX, FMC_D13,<br>EVENTOUT                                                                                                                   | -                    |

| -      | 56          | PD9                    | I/O      | FT            | -     | USART3_RX, FMC_D14,<br>SAI2_MCLK_A, EVENTOUT                                                                                                      | -                    |

| -      | 57          | PD10                   | I/O      | FT            | -     | USART3_CK, TSC_G6_IO1,<br>FMC_D15, SAI2_SCK_A,<br>EVENTOUT                                                                                        | -                    |

| -      | 58          | PD11                   | I/O      | FT            | -     | USART3_CTS, TSC_G6_IO2,<br>FMC_A16, SAI2_SD_A,<br>LPTIM2_ETR, EVENTOUT                                                                            | -                    |

| -      | 59          | PD12                   | I/O      | FT            | -     | TIM4_CH1,<br>USART3_RTS_DE,<br>TSC_G6_IO3, FMC_A17,<br>SAI2_FS_A, LPTIM2_IN1,<br>EVENTOUT                                                         | -                    |

| -      | 60          | PD13                   | I/O      | FT            | -     | TIM4_CH2, TSC_G6_IO4,<br>FMC_A18, LPTIM2_OUT,<br>EVENTOUT                                                                                         | -                    |

| -      | 61          | PD14                   | I/O      | FT            | -     | TIM4_CH3, FMC_D0,<br>EVENTOUT                                                                                                                     | -                    |

| -      | 62          | PD15                   | I/O      | FT            | -     | TIM4_CH4, FMC_D1,<br>EVENTOUT                                                                                                                     | -                    |

| 37     | 63          | PC6                    | I/O      | FT            | -     | TIM3_CH1, TIM8_CH1,<br>DFSDM_CKIN3,<br>TSC_G4_IO1, SDMMC1_D6,<br>SAI2_MCLK_A, EVENTOUT                                                            | -                    |

|        | 'in<br>nber | Pin name               |          | Ire           |       | Pin fun                                                                                                                   | ctions               |

|--------|-------------|------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------------------------------------------|----------------------|

| LQFP64 | LQFP100     | (function after reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                       | Additional functions |

| 38     | 64          | PC7                    | I/O      | FT            | -     | TIM3_CH2, TIM8_CH2,<br>DFSDM_DATIN3,<br>TSC_G4_IO2, SDMMC1_D7,<br>SAI2_MCLK_B, EVENTOUT                                   | -                    |

| 39     | 65          | PC8                    | I/O      | FT            | -     | TIM3_CH3, TIM8_CH3,<br>TSC_G4_IO3, SDMMC1_D0,<br>EVENTOUT                                                                 | -                    |

| 40     | 66          | PC9                    | I/O      | FT            | -     | TIM8_BKIN2, TIM3_CH4,<br>TIM8_CH4, TSC_G4_IO4,<br>OTG_FS_NOE, SDMMC1_D1,<br>SAI2_EXTCLK,<br>TIM8_BKIN2_COMP1,<br>EVENTOUT | -                    |

| 41     | 67          | PA8                    | I/O      | FT            | -     | MCO, TIM1_CH1,<br>USART1_CK, OTG_FS_SOF,<br>LPTIM2_OUT, EVENTOUT                                                          | -                    |

| 42     | 68          | PA9                    | I/O      | FT_u          | -     | TIM1_CH2, USART1_TX,<br>TIM15_BKIN, EVENTOUT                                                                              | OTG_FS_VBUS          |

| 43     | 69          | PA10                   | I/O      | FT_u          | -     | TIM1_CH3, USART1_RX,<br>OTG_FS_ID, TIM17_BKIN,<br>EVENTOUT                                                                | -                    |

| 44     | 70          | PA11                   | I/O      | FT_u          | -     | TIM1_CH4, TIM1_BKIN2,<br>USART1_CTS, CAN1_RX,<br>OTG_FS_DM,<br>TIM1_BKIN2_COMP1,<br>EVENTOUT                              | -                    |

| 45     | 71          | PA12                   | I/O      | FT_u          | -     | TIM1_ETR,<br>USART1_RTS_DE, CAN1_TX,<br>OTG_FS_DP, EVENTOUT                                                               | -                    |

| 46     | 72          | PA13<br>(JTMS-SWDIO)   | I/O      | FT            | (3)   | JTMS-SWDIO, IR_OUT,<br>OTG_FS_NOE, EVENTOUT                                                                               | -                    |

| 47     | -           | VSS                    | S        | -             | -     | -                                                                                                                         | -                    |

| 48     | 73          | VDDUSB                 | S        | -             | -     | -                                                                                                                         | -                    |

| -      | 74          | VSS                    | S        | -             | -     | -                                                                                                                         | -                    |

| -      | 75          | VDD                    | S        | -             | -     |                                                                                                                           | -                    |

| 49     | 76          | PA14<br>(JTCK-SWCLK)   | I/O      | FT            | (3)   | JTCK-SWCLK, EVENTOUT                                                                                                      | -                    |

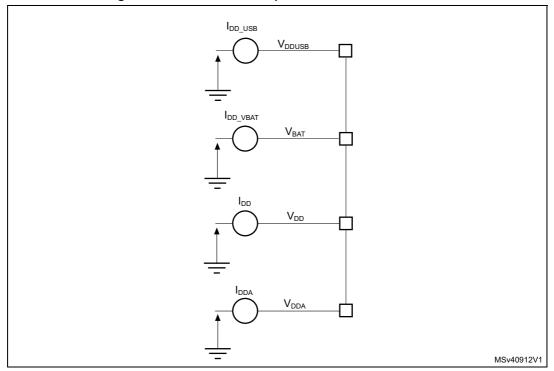

## 6.1.7 Current consumption measurement

## Figure 11. Current consumption measurement scheme

## 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 19: Voltage characteristics*, *Table 20: Current characteristics* and *Table 21: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                             | Ratings                                                                                  | Min                  | Мах                                                                                       | Unit |

|------------------------------------|------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------|------|

| V <sub>DDX</sub> - V <sub>SS</sub> | External main supply voltage (including $V_{DD}$ , $V_{DDA}$ , $V_{DDUSB}$ , $V_{BAT}$ ) | -0.3                 | 4.0                                                                                       | V    |

|                                    | Input voltage on FT_xxx pins                                                             | V <sub>SS</sub> -0.3 | min (V <sub>DD</sub> , V <sub>DDA</sub> , V <sub>DDUSB</sub> )<br>+ 4.0 <sup>(3)(4)</sup> |      |

| V <sub>IN</sub> <sup>(2)</sup>     | Input voltage on TT_xx pins                                                              | V <sub>SS</sub> -0.3 | 4.0                                                                                       | V    |

|                                    | Input voltage on BOOT0 pin                                                               | V <sub>SS</sub>      | 9.0                                                                                       |      |

|                                    | Input voltage on any other pins                                                          | V <sub>SS</sub> -0.3 | 4.0                                                                                       |      |

| ΔV <sub>DDx</sub>                  | Variations between different V <sub>DDX</sub> power pins of the same domain              | -                    | 50                                                                                        | mV   |

| V <sub>SSx</sub> -V <sub>SS</sub>  | Variations between all the different ground pins <sup>(5)</sup>                          | -                    | 50                                                                                        | mV   |

| Table 19. | Voltage | characteristics <sup>(1)</sup> |

|-----------|---------|--------------------------------|

|-----------|---------|--------------------------------|

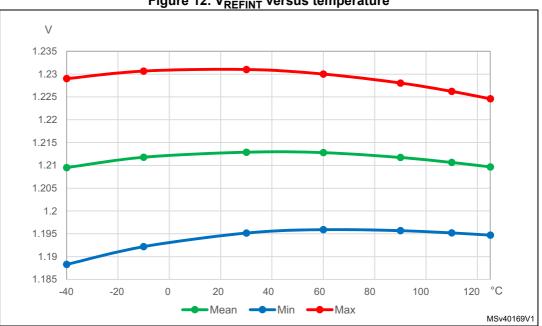

Figure 12. V<sub>REFINT</sub> versus temperature

**Electrical characteristics**

DocID027692 Rev 2

2

98/193

| •                                                                                     | 5                                                                      | Conditions                                                                  |       |       |       | TYP    |        |       | MAX <sup>(1)</sup> |       |        |        |      | Unit |

|---------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------|-------|-------|--------|--------|-------|--------------------|-------|--------|--------|------|------|

| Symbol Parameter -                                                                    | -                                                                      | V <sub>DD</sub>                                                             | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | 25 °C | 55 °C              | 85 °C | 105 °C | 125 °C | Ur   |      |

|                                                                                       | Supply                                                                 |                                                                             | 1.8 V | 6.59  | 24.7  | 92.7   | 208    | 437   | 16                 | 62    | 232    | 520    | 1093 | 1    |

| I <sub>DD</sub> (Stop 1)                                                              | current in                                                             |                                                                             | 2.4 V | 6.65  | 24.8  | 92.9   | 209    | 439   | 17                 | 62    | 232    | 523    | 1098 | μ    |

|                                                                                       | Stop 1 mode,                                                           | _                                                                           | 3 V   | 6.65  | 24.9  | 93.3   | 210    | 442   | 17                 | 62    | 233    | 525    | 1105 | - μ  |

|                                                                                       | RTC disabled                                                           |                                                                             | 3.6 V | 6.70  | 25.1  | 93.8   | 212    | 447   | 17                 | 63    | 235    | 530    | 1118 |      |

|                                                                                       |                                                                        |                                                                             | 1.8 V | 6.88  | 25.0  | 93.1   | 209    | 439   | 17                 | 63    | 233    | 523    | 1098 |      |

|                                                                                       |                                                                        | RTC clocked by LSI                                                          | 2.4 V | 7.02  | 25.2  | 93.7   | 210    | 441   | 18                 | 63    | 234    | 525    | 1103 |      |

|                                                                                       |                                                                        |                                                                             | 3 V   | 7.12  | 25.4  | 94.2   | 212    | 444   | 18                 | 64    | 236    | 530    | 1110 |      |

|                                                                                       |                                                                        |                                                                             | 3.6 V | 7.25  | 25.7  | 95.2   | 214    | 449   | 18                 | 64    | 238    | 535    | 1123 | μΑ   |

|                                                                                       | Supply                                                                 | RTC clocked by LSE<br>bypassed, at 32768 Hz                                 | 1.8 V | 6.91  | 25.2  | 93.4   | 210    | 440   | 17                 | 63    | 234    | 525    | 1100 |      |

| I <sub>DD</sub> (Stop 1                                                               | current in stop                                                        |                                                                             | 2.4 V | 7.04  | 25.3  | 94.2   | 211    | 443   | 18                 | 63    | 236    | 528    | 1108 |      |

| with RTC)                                                                             | 1 mode,                                                                |                                                                             | 3 V   | 7.19  | 25.7  | 95.0   | 212    | 446   | 18                 | 64    | 238    | 530    | 1115 |      |

|                                                                                       | RTC enabled                                                            |                                                                             | 3.6 V | 7.97  | 26.0  | 96.1   | 215    | 451   | 20                 | 65    | 240    | 538    | 1128 |      |

|                                                                                       |                                                                        | RTC clocked by LSE quartz <sup>(2)</sup> in low drive mode                  | 1.8 V | 6.85  | 25.0  | 93.0   | 208.3  | -     | 17                 | 63    | 233    | 521    | -    |      |

|                                                                                       |                                                                        |                                                                             | 2.4 V | 6.94  | 25.1  | 93.2   | 209.3  | -     | 17                 | 63    | 233    | 523    | -    |      |

|                                                                                       |                                                                        |                                                                             | 3 V   | 7.10  | 25.2  | 93.6   | 210.3  | -     | 18                 | 63    | 234    | 526    | -    | 1    |

|                                                                                       |                                                                        |                                                                             | 3.6 V | 7.34  | 25.4  | 94.1   | 212.3  | -     | 18                 | 64    | 235    | 531    | -    |      |

| Supply<br>I <sub>DD</sub> (wakeup current during<br>from Stop1) wakeup from<br>Stop 1 | Wakeup clock MSI = 48 MHz,<br>voltage Range 1,<br>See <sup>(3)</sup> . | 3 V                                                                         | 1.47  | -     | -     | -      | -      |       |                    |       |        |        |      |      |

|                                                                                       | current during wakeup from                                             | Wakeup clock MSI = 4 MHz,<br>voltage Range 2,<br>See <sup>(3)</sup> .       | 3 V   | 1.7   | -     | -      | -      | -     |                    |       | -      |        |      | m    |

|                                                                                       | Stop 1                                                                 | Wakeup clock<br>HSI16 = 16 MHz,<br>voltage Range 1,<br>See <sup>(3)</sup> . | 3 V   | 1.62  | -     | -      | -      | -     |                    |       |        |        |      |      |

1. Guaranteed based on test during characterization, unless otherwise specified.

2. Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8 pF loading capacitors.

3. Wakeup with code execution from Flash. Average value given for a typical wakeup time as specified in *Table 41: Low-power mode wakeup timings*.

| ctrica          |  |

|-----------------|--|

| I characteristi |  |

| ഗ   |  |

|-----|--|

| -   |  |

|     |  |

| ~   |  |

|     |  |

| ω   |  |

| N   |  |

|     |  |

| 4   |  |

| 1   |  |

| сл  |  |

| ×   |  |

| - C |  |

| ~   |  |

|     |  |

|                            |                                             | Conditions                                       |                 |       |       | TYP   |        |        | MAX <sup>(1)</sup> |       |              |        | <b>.</b> |   |

|----------------------------|---------------------------------------------|--------------------------------------------------|-----------------|-------|-------|-------|--------|--------|--------------------|-------|--------------|--------|----------|---|

| Symbol                     | Parameter                                   | -                                                | V <sub>DD</sub> | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | 25 °C              | 55 °C | 85 °C        | 105 °C | 125 °C   | U |

|                            |                                             |                                                  | 1.8 V           | 114   | 355   | 1540  | 4146   | 10735  | 176                | 888   | 3850         | 10365  | 26838    | T |

|                            |                                             |                                                  | 2.4 V           | 138   | 407   | 1795  | 4828   | 12451  | 223                | 1018  | 4488         | 12070  | 31128    |   |

|                            | Supply current                              | no independent watchdog                          | 3 V             | 150   | 486   | 2074  | 5589   | 14291  | 263                | 1215  | 5185         | 13973  | 35728    | 1 |

| In Standby<br>Mode (backup |                                             | 3.6 V                                            | 198             | 618   | 2608  | 6928  | 17499  | 383    | 1545               | 6520  | 17320<br>(2) | 43748  |          |   |

|                            | registers<br>retained),                     |                                                  | 1.8 V           | 317   | -     | -     | -      | -      | -                  | -     | -            | -      | -        | 1 |

|                            | RTC disabled                                | with independent                                 | 2.4 V           | 391   | -     | -     | -      | -      | -                  | -     | -            | -      | -        |   |

|                            |                                             | watchdog                                         | 3 V             | 438   | -     | -     | -      | -      | -                  | -     | -            | -      | -        | 1 |

|                            |                                             | 3.6 V                                            | 566             | -     | -     | -     | -      | -      | -                  | -     | -            | -      | 1        |   |

|                            |                                             |                                                  | 1.8 V           | 377   | 621   | 1873  | 4564   | 11318  | 491                | 1207  | 4250         | 10867  | 27537    | Ī |

|                            | RTC clocked by LSI, no independent watchdog | 2.4 V                                            | 464             | 756   | 2210  | 5348  | 13166  | 614    | 1436               | 4986  | 12694        | 31986  |          |   |

|                            |                                             | 3 V                                              | 572             | 913   | 2599  | 6219  | 15197  | 770    | 1727               | 5815  | 14729        | 36815  |          |   |

|                            |                                             | 3.6 V                                            | 722             | 1144  | 3253  | 7724  | 18696  | 1012   | 2176               | 7294  | 18275        | 45184  |          |   |

|                            |                                             | RTC clocked by LSI, with<br>independent watchdog | 1.8 V           | 456   | -     | -     | -      | -      | -                  | -     | -            | -      | I        |   |

|                            | Supply ourrept                              |                                                  | 2.4 V           | 557   | -     | -     | -      | -      | -                  | -     | -            | -      | -        |   |

|                            | in Standby                                  |                                                  | 3 V             | 663   | -     | -     | -      | -      | -                  | -     | -            | -      | I        |   |

| I <sub>DD</sub> (Standby   | mode (backup                                |                                                  | 3.6 V           | 885   | -     | -     | -      | -      | -                  | -     | -            | -      | I        |   |

| with RTC)                  | registers<br>retained),                     |                                                  | 1.8 V           | 289   | 527   | 1747  | 4402   | 11009  | -                  | -     | -            | -      | -        |   |

|                            | RTC enabled                                 | RTC clocked by LSE                               | 2.4 V           | 396   | 671   | 2108  | 5202   | 12869  | -                  | -     | -            | -      | -        |   |

|                            |                                             | bypassed at 32768Hz                              | 3 V             | 528   | 853   | 2531  | 6095   | 14915  | -                  | -     | -            | -      | -        |   |

|                            |                                             |                                                  | 3.6 V           | 710   | 1111  | 3115  | 7470   | 18221  | -                  | -     | -            | -      | -        |   |

|                            |                                             |                                                  | 1.8 V           | 416   | 640   | 1862  | 4479   | 11908  | -                  | -     | -            | -      | -        |   |

|                            |                                             | RTC clocked by LSE                               | 2.4 V           | 514   | 796   | 2193  | 5236   | 13689  | -                  | -     | -            | -      | -        |   |

|                            |                                             | quartz <sup>(3)</sup> in low drive mode          | 3 V             | 652   | 961   | 2589  | 6103   | 15598  | -                  | -     | -            | -      | -        |   |

|                            |                                             |                                                  | 3.6 V           | 821   | 1226  | 3235  | 7551   | 17947  | -                  | -     | -            | -      | -        | l |

5

| Symbol               | Parameter                                                          |                            |                             | Тур       | Max   | Unit |  |

|----------------------|--------------------------------------------------------------------|----------------------------|-----------------------------|-----------|-------|------|--|

|                      |                                                                    | Dense 1                    | Wakeup clock MSI = 48 MHz   | 6.2       | 10.2  |      |  |

|                      |                                                                    | Range 1                    | Wakeup clock HSI16 = 16 MHz | 6.3       | 8.99  |      |  |

|                      | Wake up time from Stop 1<br>mode to Run mode in Flash              | Range 2                    | Wakeup clock MSI = 24 MHz   | 6.3 10.46 |       |      |  |

|                      |                                                                    |                            | Wakeup clock HSI16 = 16 MHz | 6.3       | 8.87  |      |  |

|                      |                                                                    |                            | Wakeup clock MSI = 4 MHz    | 8.0       | 13.23 |      |  |

|                      |                                                                    | Dense 1                    | Wakeup clock MSI = 48 MHz   | 4.5       | 5.78  |      |  |

|                      | Wake up time from Stop 1                                           | Range 1                    | Wakeup clock HSI16 = 16 MHz | 5.5       | 7.1   |      |  |

| t <sub>WUSTOP1</sub> | mode to Run mode in                                                |                            | Wakeup clock MSI = 24 MHz   | 5.0       | 6.5   | μs   |  |

|                      | SRAM1                                                              | Range 2                    | Wakeup clock HSI16 = 16 MHz | 5.5       | 7.1   |      |  |

|                      |                                                                    |                            | Wakeup clock MSI = 4 MHz    | 8.2       | 13.5  |      |  |

|                      | Wake up time from Stop 1<br>mode to Low-power run<br>mode in Flash | Regulator in<br>low-power  | Wekeun eleek MOL – 2 MUL    | 12.7      | 20    |      |  |

|                      | Wake up time from Stop 1<br>mode to Low-power run<br>mode in SRAM1 | mode (LPR=1 in<br>PWR_CR1) | Wakeup clock MSI = 2 MHz    |           | 21.5  |      |  |

|                      |                                                                    | Danag 1                    | Wakeup clock MSI = 48 MHz   | 8.0       | 9.4   |      |  |

|                      | Wake up time from Stop 2<br>mode to Run mode in Flash              | Range 1                    | Wakeup clock HSI16 = 16 MHz | 7.3       | 9.3   |      |  |

|                      |                                                                    | Range 2                    | Wakeup clock MSI = 24 MHz   | 8.2       | 9.9   |      |  |

|                      |                                                                    |                            | Wakeup clock HSI16 = 16 MHz | 7.3       | 9.3   |      |  |

|                      |                                                                    |                            | Wakeup clock MSI = 4 MHz    | 10.6      | 15.8  |      |  |

| twustop2             |                                                                    | Dense 1                    | Wakeup clock MSI = 48 MHz   | 5.1       | 6.7   | μs   |  |

|                      | Wake up time from Stop 2                                           | Range 1                    | Wakeup clock HSI16 = 16 MHz | 5.7       | 8     |      |  |

|                      | mode to Run mode in                                                |                            | Wakeup clock MSI = 24 MHz   | 5.5       | 6.65  |      |  |

|                      | SRAM1                                                              | Range 2                    | Wakeup clock HSI16 = 16 MHz | 5.7       | 7.53  |      |  |

|                      |                                                                    |                            | Wakeup clock MSI = 4 MHz    | 8.2       | 16.6  |      |  |

| 4                    | Wakeup time from Standby                                           | Range 1                    | Wakeup clock MSI = 8 MHz    | 14.3      | 20.8  |      |  |

| <sup>I</sup> WUSTBY  | <sup>t</sup> WUSTBY mode to Run mode                               |                            | Wakeup clock MSI = 4 MHz    |           | 35.5  | μs   |  |

| t <sub>WUSTBY</sub>  | Wakeup time from Standby                                           | Panao 1                    | Wakeup clock MSI = 8 MHz    | 14.3      | 24.3  |      |  |

| SRAM2                | with SRAM2 to Run mode                                             | Range 1                    | Wakeup clock MSI = 4 MHz    | 20.1      | 38.5  | μs   |  |

| t <sub>WUSHDN</sub>  | Wakeup time from<br>Shutdown mode to Run<br>mode                   | Range 1                    | Wakeup clock MSI = 4 MHz    | 256       | 330.6 | μs   |  |

Table 41. Low-power mode wakeup timings<sup>(1)</sup> (continued)

1. Guaranteed by characterization results.

## High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 48 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 46*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                  | Parameter                                 | Conditions <sup>(2)</sup>                                 | Min | Тур  | Мах | Unit |

|-------------------------|-------------------------------------------|-----------------------------------------------------------|-----|------|-----|------|

| f <sub>OSC_IN</sub>     | Oscillator frequency                      | -                                                         | 4   | 8    | 48  | MHz  |

| R <sub>F</sub>          | Feedback resistor                         | -                                                         | -   | 200  | -   | kΩ   |

|                         |                                           | During startup <sup>(3)</sup>                             | -   | -    | 5.5 |      |

| I <sub>DD(HSE)</sub>    |                                           | V <sub>DD</sub> = 3 V,<br>Rm = 30 Ω,<br>CL = 10 pF@8 MHz  | -   | 0.44 | -   |      |

|                         | HSE current consumption                   | V <sub>DD</sub> = 3 V,<br>Rm = 45 Ω,<br>CL = 10 pF@8 MHz  | -   | 0.45 | -   |      |

|                         |                                           | V <sub>DD</sub> = 3 V,<br>Rm = 30 Ω,<br>CL = 5 pF@48 MHz  | -   | 0.68 | -   | mA   |

|                         |                                           | V <sub>DD</sub> = 3 V,<br>Rm = 30 Ω,<br>CL = 10 pF@48 MHz | -   | 0.94 | -   |      |

|                         |                                           | V <sub>DD</sub> = 3 V,<br>Rm = 30 Ω,<br>CL = 20 pF@48 MHz | -   | 1.77 | -   |      |

| G <sub>m</sub>          | Maximum critical crystal transconductance | Startup                                                   | -   | -    | 1.5 | mA/V |

| $t_{\rm SU(HSE)}^{(4)}$ | Startup time                              | V <sub>DD</sub> is stabilized                             | -   | 2    | -   | ms   |

| Table 46. HSE oscillator characteristics <sup>(1</sup> |

|--------------------------------------------------------|

|--------------------------------------------------------|

1. Guaranteed by design.

2. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

3. This consumption level occurs during the first 2/3 of the  $t_{SU(\text{HSE})}$  startup time

4. t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 20 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 15*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

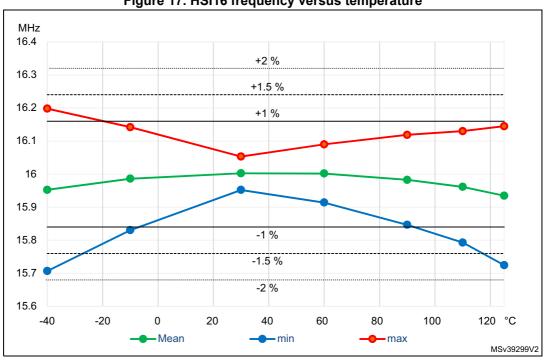

Figure 17. HSI16 frequency versus temperature

DocID027692 Rev 2

| Symbol           | Parameter                                          | Conditions                                                                                                                | Min | Тур | Max                    | Unit |

|------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------|------|

|                  |                                                    | $V_{IN} \le Max(V_{DDXXX})^{(4)}$                                                                                         | -   | -   | ±100                   |      |

|                  | FT_xx input leakage current <sup>(3)</sup>         | $\begin{array}{l} Max(V_{DDXXX}) \leq V_{IN} \leq \\ Max(V_{DDXXX}) + 1 \ V^{(4)(5)} \end{array}$                         | -   | -   | 650 <sup>(3)(6)</sup>  |      |

|                  |                                                    | $\begin{array}{l} {\sf Max}({\sf V}_{{\sf DDXXX}})\text{+}1~{\sf V} < \\ {\sf VIN} \leq 5.5~{\sf V}^{(3)(5)} \end{array}$ | -   | -   | 200 <sup>(6)</sup>     |      |

|                  |                                                    | $V_{IN} \le Max(V_{DDXXX})^{(4)}$                                                                                         | -   | -   | ±150                   |      |

| l <sub>lkg</sub> | FT_lu, FT_u and<br>PC3 IO                          | $\begin{array}{l} Max(V_{DDXXX}) \leq V_{IN} \leq \\ Max(V_{DDXXX}) + 1 \ V^{(4)} \end{array}$                            | -   | -   | 2500 <sup>(3)(7)</sup> | nA   |

|                  |                                                    | Max(V <sub>DDXXX</sub> )+1 V < VIN ≤ 5.5 V <sup>(4)(5)(7)</sup>                                                           | -   | -   | 250 <sup>(7)</sup>     |      |

|                  | TT_xx input leakage current                        | $V_{IN} \le Max(V_{DDXXX})^{(6)}$                                                                                         | -   | -   | ±150                   |      |

|                  |                                                    | Max(V <sub>DDXXX</sub> ) ≤ V <sub>IN</sub> < 3.6 V <sup>(6)</sup>                                                         | -   | -   | 2000 <sup>(3)</sup>    |      |

| R <sub>PU</sub>  | Weak pull-up<br>equivalent resistor <sup>(8)</sup> | V <sub>IN</sub> = V <sub>SS</sub>                                                                                         | 25  | 40  | 55                     | kΩ   |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(8)</sup>  | V <sub>IN</sub> = V <sub>DDIOx</sub>                                                                                      | 25  | 40  | 55                     | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                                | -                                                                                                                         | -   | 5   | -                      | pF   |

Table 59. I/O static characteristics (continued)

1. Refer to Figure 19: I/O input characteristics.

- 2. Tested in production.

- 3. Guaranteed by design.

- 4. Max(V<sub>DDXXX</sub>) is the maximum value of all the I/O supplies. Refer to Table: Legend/Abbreviations used in the pinout table.

- 5. All TX\_xx IO except FT\_lu, FT\_u and PC3.

- 6. This value represents the pad leakage of the IO itself. The total product pad leakage is provided by this formula:  $I_{Total\_Ileak\_max} = 10 \ \mu A + [number of IOs where V_{IN} is applied on the pad] \times I_{Ikg}(Max)$ .

- 7. To sustain a voltage higher than MIN(V<sub>DD</sub>, V<sub>DDA</sub>, V<sub>DDUSB</sub>) +0.3 V, the internal Pull-up and Pull-Down resistors must be disabled.

- Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

| Symbol                 | Parameter                                                                                    | Co                                                                        | Min                                                | Тур | Мах                                | Unit                               |    |  |

|------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------|-----|------------------------------------|------------------------------------|----|--|

|                        |                                                                                              | DAC_OUT                                                                   | DAC output buffer<br>ON, C <sub>SH</sub> = 100 nF  | -   | 0.7                                | 3.5                                | me |  |

|                        | Sampling time in sample<br>and hold mode (code<br>transition between the                     | pin connected                                                             | DAC output buffer<br>OFF, C <sub>SH</sub> = 100 nF | -   | 10.5                               | 18                                 | ms |  |

| <sup>t</sup> SAMP      | lowest input code and the<br>highest input code when<br>DACOUT reaches final<br>value ±1LSB) | DAC_OUT<br>pin not<br>connected<br>(internal<br>connection<br>only)       | DAC output buffer<br>OFF                           | -   | 2                                  | 3.5                                | μs |  |

| I <sub>leak</sub>      | Output leakage current                                                                       | Sample and ho DAC_OUT pin                                                 |                                                    | -   | -                                  | _(3)                               | nA |  |

| Cl <sub>int</sub>      | Internal sample and hold capacitor                                                           |                                                                           | -                                                  | 5.2 | 7                                  | 8.8                                | pF |  |

| t <sub>TRIM</sub>      | Middle code offset trim time                                                                 | DAC output bu                                                             | 50                                                 | -   | -                                  | μs                                 |    |  |

| V <sub>offset</sub>    | Middle code offset for 1                                                                     | V <sub>REF+</sub> = 3.6 V                                                 |                                                    | I   | 1500                               | -                                  | μV |  |

| ♥ offset               | trim code step                                                                               | V <sub>REF+</sub> = 1.8 V                                                 |                                                    | -   | 750                                | -                                  | μv |  |

|                        | DAC consumption from<br>V <sub>DDA</sub>                                                     | DAC output<br>buffer ON                                                   | No load, middle<br>code (0x800)                    | I   | 315                                | 500                                |    |  |

|                        |                                                                                              |                                                                           | No load, worst code<br>(0xF1C)                     | -   | 450                                | 670                                |    |  |

| I <sub>DDA</sub> (DAC) |                                                                                              | DAC output<br>buffer OFF                                                  | No load, middle<br>code (0x800)                    | -   | -                                  | 0.2                                | μA |  |

|                        |                                                                                              | Sample and hold mode, C <sub>SH</sub> =<br>100 nF                         |                                                    | -   | 315 x<br>Ton/(Ton<br>+Toff)<br>(4) | 670 x<br>Ton/(Ton<br>+Toff)<br>(4) |    |  |

|                        |                                                                                              | DAC output                                                                | No load, middle<br>code (0x800)                    | -   | 185                                | 240                                |    |  |

|                        |                                                                                              | buffer ON                                                                 | No load, worst code<br>(0xF1C)                     | -   | 340                                | 400                                |    |  |

|                        |                                                                                              | DAC output<br>buffer OFF                                                  | No load, middle<br>code (0x800)                    | -   | 155                                | 205                                |    |  |

| I <sub>DDV</sub> (DAC) | DAC consumption from<br>V <sub>REF+</sub>                                                    | Sample and ho<br>C <sub>SH</sub> = 100 nF,                                | old mode, buffer ON,<br>worst case                 | -   | 185 x<br>Ton/(Ton<br>+Toff)<br>(4) | 400 x<br>Ton/(Ton<br>+Toff)<br>(4) | μA |  |

|                        |                                                                                              | Sample and hold mode, buffer OFF,<br>C <sub>SH</sub> = 100 nF, worst case |                                                    | -   | 155 x<br>Ton/(Ton<br>+Toff)<br>(4) | 205 x<br>Ton/(Ton<br>+Toff)<br>(4) |    |  |

Table 70. DAC characteristics<sup>(1)</sup> (continued)

1. Guaranteed by design.

2. In buffered mode, the output can overshoot above the final value for low input code (starting from min value).

## **Electrical characteristics**

| Symbol                                  | Parameter                                            | Con            | ditions                                | Min | Тур        | Мах | Unit   |

|-----------------------------------------|------------------------------------------------------|----------------|----------------------------------------|-----|------------|-----|--------|

|                                         |                                                      | PGA Gain = 2   |                                        | -   | 80/80      | -   |        |

|                                         | R2/R1 internal                                       | PGA Gain = 4   |                                        | -   | 120/<br>40 | -   |        |

| R <sub>network</sub>                    | resistance<br>values in PGA<br>mode <sup>(5)</sup>   | PGA Gain = 8   |                                        | -   | 140/<br>20 | -   | kΩ/kΩ  |

|                                         |                                                      | PGA Gain = 16  |                                        | -   | 150/<br>10 | -   |        |

| Delta R                                 | Resistance<br>variation (R1 or<br>R2)                |                | -15                                    | -   | 15         | %   |        |

| PGA gain error                          | PGA gain error                                       |                | -                                      | -1  | -          | 1   | %      |

|                                         | PGA bandwidth<br>for different non<br>inverting gain | Gain = 2       | -                                      | -   | GBW/<br>2  | -   | - MHz  |

| PGA BW                                  |                                                      | Gain = 4       | -                                      | -   | GBW/<br>4  | -   |        |

| FGA BW                                  |                                                      | Gain = 8       | -                                      | -   | GBW/<br>8  | -   |        |

|                                         |                                                      | Gain = 16      | -                                      | -   | GBW/<br>16 | -   |        |

|                                         |                                                      | Normal mode    | at 1 kHz, Output<br>loaded with 4 kΩ   | -   | 500        | -   |        |

| 07                                      | Voltage noise                                        | Low-power mode | at 1 kHz, Output<br>loaded with 20 kΩ  | -   | 600        | -   | nV/√Hz |

| en                                      | density                                              | Normal mode    | at 10 kHz, Output<br>loaded with 4 kΩ  | -   | 180        | -   | nv/vHz |

|                                         |                                                      | Low-power mode | at 10 kHz, Output<br>loaded with 20 kΩ | -   | 290        | -   |        |

|                                         | OPAMP                                                | Normal mode    | no Load, quiescent                     | -   | 120        | 260 |        |

| I <sub>dda</sub> (opamp) <sup>(3)</sup> | consumption<br>from V <sub>DDA</sub>                 | Low-power mode | mode                                   | -   | 45         | 100 | μA     |

Table 74. OPAMP characteristics<sup>(1)</sup> (continued)

1. Guaranteed by design, unless otherwise specified.

2. The temperature range is limited to 0 °C-125 °C when  $V_{\text{DDA}}$  is below 2 V

3. Guaranteed by characterization results.

4. Mostly I/O leakage, when used in analog mode. Refer to I<sub>lkg</sub> parameter in *Table 59: I/O static characteristics*.

5. R2 is the internal resistance between OPAMP output and OPAMP inverting input. R1 is the internal resistance between OPAMP inverting input and ground. The PGA gain =1+R2/R1

## **SAI characteristics**

Unless otherwise specified, the parameters given in *Table 86* for SAI are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in*Table 22: General operating conditions*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels:  $0.5 \times V_{DD}$

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CK,SD,FS).

| Symbol                   | Parameter                          | Conditions                                                            | Min | Мах  | Unit |

|--------------------------|------------------------------------|-----------------------------------------------------------------------|-----|------|------|

| f <sub>MCLK</sub>        | SAI Main clock output              | -                                                                     | -   | 50   | MHz  |

|                          |                                    | Master transmitter<br>2.7 ≤ V <sub>DD</sub> ≤ 3.6<br>Voltage Range 1  | -   | 18.5 |      |

|                          |                                    | Master transmitter<br>1.71 ≤ V <sub>DD</sub> ≤ 3.6<br>Voltage Range 1 | -   | 12.5 |      |

|                          |                                    | Master receiver<br>Voltage Range 1                                    | -   | 25   |      |

| f <sub>CK</sub>          | SAI clock frequency <sup>(2)</sup> | Slave transmitter<br>2.7 ≤ V <sub>DD</sub> ≤ 3.6<br>Voltage Range 1   | -   | 22.5 | MHz  |

|                          |                                    | Slave transmitter<br>1.71 ≤ V <sub>DD</sub> ≤ 3.6<br>Voltage Range 1  | -   | 14.5 |      |

|                          |                                    | Slave receiver<br>Voltage Range 1                                     | -   | 25   |      |

|                          |                                    | Voltage Range 2                                                       | -   | 12.5 |      |

| +                        | FS valid time                      | Master mode<br>2.7 $\leq$ V <sub>DD</sub> $\leq$ 3.6                  | -   | 22   | 20   |

| t <sub>v(FS)</sub>       |                                    | Master mode<br>$1.71 \le V_{DD} \le 3.6$                              | -   | 40   | ns   |

| t <sub>h(FS)</sub>       | FS hold time                       | Master mode                                                           | 10  | -    | ns   |

| t <sub>su(FS)</sub>      | FS setup time                      | Slave mode                                                            | 1   | -    | ns   |

| t <sub>h(FS)</sub>       | FS hold time                       | Slave mode                                                            | 2   | -    | ns   |

| t <sub>su(SD_A_MR)</sub> | Data input setup time              | Master receiver                                                       | 2.5 | -    | 200  |

| t <sub>su(SD_B_SR)</sub> |                                    | Slave receiver                                                        | 3   | -    | ns   |

| t <sub>h(SD_A_MR)</sub>  | Data input hold time               | Master receiver                                                       | 8   | -    | ns   |

| t <sub>h(SD_B_SR)</sub>  |                                    | Slave receiver                                                        | 4   | -    | 115  |

## Table 86. SAI characteristics<sup>(1)</sup>

## 6.3.27 FSMC characteristics

Unless otherwise specified, the parameters given in *Table 90* to *Table 95* for the FMC interface are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 22*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output

characteristics.

## Asynchronous waveforms and timings

*Figure 34* and *Figure 35* represent asynchronous waveforms and *Table 90* through *Table 93* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- AddressSetupTime = 0x1

- AddressHoldTime = 0x1

- DataSetupTime = 0x1 (except for asynchronous NWAIT mode, DataSetupTime = 0x5)

- BusTurnAroundDuration = 0x0

In all timing tables, the THCLK is the HCLK clock period.