Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betano                     |                                                                                            |

|----------------------------|--------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                     |

| Core Processor             | ARM® Cortex®-M4                                                                            |

| Core Size                  | 32-Bit Single-Core                                                                         |

| Speed                      | 80MHz                                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                                      |

| Number of I/O              | 51                                                                                         |

| Program Memory Size        | 1MB (1M x 8)                                                                               |

| Program Memory Type        | FLASH                                                                                      |

| EEPROM Size                | -                                                                                          |

| RAM Size                   | 128K x 8                                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                      |

| Oscillator Type            | Internal                                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                         |

| Mounting Type              | Surface Mount                                                                              |

| Package / Case             | 64-LQFP                                                                                    |

| Supplier Device Package    | 64-LQFP (10x10)                                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l475rgt7tr                    |

|                            |                                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                    | ionalitie        |                  | o 0/1                |                        | op 2 |                   | ndby | Shutdown          |                  |                   |   |                   |      |

|----------------------------------------------------|------------------|------------------|----------------------|------------------------|------|-------------------|------|-------------------|------------------|-------------------|---|-------------------|------|

| Peripheral                                         | Run              | Sleep            | Low-<br>power<br>run | Low-<br>power<br>sleep | -    | Wakeup capability | -    | Wakeup capability | -                | Wakeup capability | - | Wakeup capability | VBAT |

| CPU                                                | Y                | -                | Y                    | -                      | -    | -                 | -    | -                 | -                | -                 | - | -                 | -    |

| Flash memory (up to 1 MB)                          | O <sup>(2)</sup> | O <sup>(2)</sup> | O <sup>(2)</sup>     | O <sup>(2)</sup>       | -    | -                 | -    | -                 | -                | -                 | - | -                 | -    |

| SRAM1 (up to<br>96 KB)                             | Y                | Y <sup>(3)</sup> | Y                    | Y <sup>(3)</sup>       | Y    | -                 | Y    | -                 | -                | -                 | - | -                 | -    |

| SRAM2 (32 KB)                                      | Y                | Y <sup>(3)</sup> | Y                    | Y <sup>(3)</sup>       | Y    | -                 | Y    | -                 | O <sup>(4)</sup> | -                 | - | -                 | -    |

| FSMC                                               | 0                | 0                | 0                    | 0                      | -    | -                 | -    | -                 | -                | -                 | - | -                 | -    |

| Quad SPI                                           | 0                | 0                | 0                    | 0                      | -    | -                 | -    | -                 | -                | -                 | - | -                 | -    |

| Backup Registers                                   | Y                | Y                | Y                    | Y                      | Y    | -                 | Y    | -                 | Y                | -                 | Y | -                 | Y    |

| Brown-out reset<br>(BOR)                           | Y                | Y                | Y                    | Y                      | Y    | Y                 | Y    | Y                 | Y                | Y                 | - | -                 | -    |

| Programmable<br>Voltage Detector<br>(PVD)          | 0                | 0                | 0                    | 0                      | 0    | 0                 | 0    | 0                 | -                | -                 | - | -                 | -    |

| Peripheral Voltage<br>Monitor (PVMx;<br>x=1,2,3,4) | 0                | 0                | 0                    | 0                      | 0    | 0                 | 0    | 0                 | -                | -                 | - | -                 | -    |

| DMA                                                | 0                | 0                | 0                    | 0                      | -    | -                 | -    | -                 | -                | -                 | - | -                 | -    |

| High Speed Internal<br>(HSI16)                     | 0                | 0                | 0                    | 0                      | (5)  | -                 | (5)  | -                 | -                | -                 | - | -                 | -    |

| High Speed<br>External (HSE)                       | 0                | 0                | 0                    | 0                      | -    | -                 | -    | -                 | -                | -                 | - | -                 | -    |

| Low Speed Internal<br>(LSI)                        | 0                | 0                | 0                    | 0                      | 0    | -                 | 0    | -                 | 0                | -                 | - | -                 | -    |

| Low Speed External (LSE)                           | 0                | 0                | 0                    | 0                      | 0    | -                 | 0    | -                 | 0                | -                 | 0 | -                 | 0    |

| Multi-Speed Internal<br>(MSI)                      | 0                | 0                | 0                    | 0                      | -    | -                 | -    | -                 | -                | -                 | - | -                 | -    |

| Clock Security<br>System (CSS)                     | 0                | 0                | 0                    | 0                      | -    | -                 | -    | -                 | -                | -                 | - | -                 | -    |

| Clock Security<br>System on LSE                    | 0                | 0                | 0                    | 0                      | 0    | 0                 | 0    | 0                 | 0                | 0                 | - | -                 | -    |

| RTC / Auto wakeup                                  | 0                | 0                | 0                    | 0                      | 0    | 0                 | 0    | 0                 | 0                | 0                 | 0 | 0                 | 0    |

| Number of RTC<br>Tamper pins                       | 3                | 3                | 3                    | 3                      | 3    | 0                 | 3    | 0                 | 3                | 0                 | 3 | 0                 | 3    |

| Table 5. Functionalities depending on the working mode <sup>(1</sup> | ) |

|----------------------------------------------------------------------|---|

|----------------------------------------------------------------------|---|

interrupt is generated if enabled. LSE failure can also be detected and generated an interrupt.

- Clock-out capability:

- MCO: microcontroller clock output: it outputs one of the internal clocks for external use by the application

- LSCO: low speed clock output: it outputs LSI or LSE in all low-power modes (except VBAT).

Several prescalers allow to configure the AHB frequency, the high speed APB (APB2) and the low speed APB (APB1) domains. The maximum frequency of the AHB and the APB domains is 80 MHz.

## 3.36 Development support

## 3.36.1 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

Debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

## 3.36.2 Embedded Trace Macrocell™

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32L475xx through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. Real-time instruction and data flow activity be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

|        | 'in<br>nber | Pin name               |          | Ire           |       | Pin fun                                                                                                                   | ctions               |

|--------|-------------|------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------------------------------------------|----------------------|

| LQFP64 | LQFP100     | (function after reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                       | Additional functions |

| 38     | 64          | PC7                    | I/O      | FT            | -     | TIM3_CH2, TIM8_CH2,<br>DFSDM_DATIN3,<br>TSC_G4_IO2, SDMMC1_D7,<br>SAI2_MCLK_B, EVENTOUT                                   | -                    |

| 39     | 65          | PC8                    | I/O      | FT            | -     | TIM3_CH3, TIM8_CH3,<br>TSC_G4_IO3, SDMMC1_D0,<br>EVENTOUT                                                                 | -                    |

| 40     | 66          | PC9                    | I/O      | FT            | -     | TIM8_BKIN2, TIM3_CH4,<br>TIM8_CH4, TSC_G4_IO4,<br>OTG_FS_NOE, SDMMC1_D1,<br>SAI2_EXTCLK,<br>TIM8_BKIN2_COMP1,<br>EVENTOUT | -                    |

| 41     | 67          | PA8                    | I/O      | FT            | -     | MCO, TIM1_CH1,<br>USART1_CK, OTG_FS_SOF,<br>LPTIM2_OUT, EVENTOUT                                                          | -                    |

| 42     | 68          | PA9                    | I/O      | FT_u          | -     | TIM1_CH2, USART1_TX,<br>TIM15_BKIN, EVENTOUT                                                                              | OTG_FS_VBUS          |

| 43     | 69          | PA10                   | I/O      | FT_u          | -     | TIM1_CH3, USART1_RX,<br>OTG_FS_ID, TIM17_BKIN,<br>EVENTOUT                                                                | -                    |

| 44     | 70          | PA11                   | I/O      | FT_u          | -     | TIM1_CH4, TIM1_BKIN2,<br>USART1_CTS, CAN1_RX,<br>OTG_FS_DM,<br>TIM1_BKIN2_COMP1,<br>EVENTOUT                              | -                    |

| 45     | 71          | PA12                   | I/O      | FT_u          | -     | TIM1_ETR,<br>USART1_RTS_DE, CAN1_TX,<br>OTG_FS_DP, EVENTOUT                                                               | -                    |

| 46     | 72          | PA13<br>(JTMS-SWDIO)   | I/O      | FT            | (3)   | JTMS-SWDIO, IR_OUT,<br>OTG_FS_NOE, EVENTOUT                                                                               | -                    |

| 47     | -           | VSS                    | S        | -             | -     | -                                                                                                                         | -                    |

| 48     | 73          | VDDUSB                 | S        | -             | -     | -                                                                                                                         | -                    |

| -      | 74          | VSS                    | S        | -             | -     | -                                                                                                                         | -                    |

| -      | 75          | VDD                    | S        | -             | -     |                                                                                                                           | -                    |

| 49     | 76          | PA14<br>(JTCK-SWCLK)   | I/O      | FT            | (3)   | JTCK-SWCLK, EVENTOUT                                                                                                      | -                    |

| on in Run<br>ru   |                        | ow-pow<br>rom SR |       | modes,    | code v    | with dat | a proce | essing |           |           |      |

|-------------------|------------------------|------------------|-------|-----------|-----------|----------|---------|--------|-----------|-----------|------|

|                   | TYP MAX <sup>(1)</sup> |                  |       |           |           |          |         |        |           |           |      |

| f <sub>HCLK</sub> | 25 °C                  | 55 °C            | 85 °C | 105<br>°C | 125<br>°C | 25 °C    | 55 °C   | 85 °C  | 105<br>°C | 125<br>°C | Unit |

| 26 MHz            | 2.88                   | 2.94             | 3.05  | 3.23      | 3.58      | 3.18     | 3.26    | 3.40   | 4.02      | 4.65      |      |

| 16 MHz            | 1.83                   | 1.87             | 1.98  | 2.15      | 2.50      | 2.01     | 2.16    | 2.30   | 2.72      | 3.34      |      |

| 8 MHz             | 0.97                   | 1.00             | 1.11  | 1.27      | 1.62      | 1.07     | 1.16    | 1.32   | 1.73      | 2.36      |      |

| 4 MHz             | 0.54                   | 0.57             | 0.67  | 0.84      | 1.18      | 0.59     | 0.69    | 0.88   | 1.23      | 1.96      |      |

| 2 MHz             | 0.33                   | 0.36             | 0.46  | 0.62      | 0.96      | 0.37     | 0.45    | 0.63   | 0.98      | 1.70      |      |

| 1 MHz             | 0.22                   | 0.25             | 0.35  | 0.51      | 0.85      | 0.25     | 0.33    | 0.50   | 0.86      | 1.57      |      |

| 100 kHz           | 0.12                   | 0.15             | 0.25  | 0.41      | 0.75      | 0.15     | 0.21    | 0.39   | 0.74      | 1.45      | mA   |

| 80 MHz            | 10.2                   | 10.3             | 10.5  | 10.7      | 11.1      | 11.22    | 11.57   | 11.86  | 12.07     | 13.11     |      |

| 72 MHz            | 9.25                   | 9.31             | 9.46  | 9.68      | 10.1      | 10.18    | 10.41   | 10.55  | 10.76     | 11.80     |      |

| 64 MHz            | 8.25                   | 8.31             | 8.46  | 8.67      | 9.08      | 9.08     | 9.37    | 9.66   | 9.87      | 10.91     |      |

| 48 MHz            | 6.26                   | 6.33             | 6.48  | 6.69      | 7.11      | 6.89     | 7.11    | 7.25   | 7.67      | 8.50      |      |

| 32 MHz            | 4.22                   | 4.28             | 4.42  | 4.63      | 5.03      | 4.64     | 4.86    | 5.15   | 5.56      | 6.19      |      |

| 24 MHz            | 3.20                   | 3.25             | 3.38  | 3.59      | 3.99      | 3.52     | 3.70    | 3.84   | 4.26      | 5.09      |      |

| 16 MHz            | 2.18                   | 2.22             | 2.35  | 2.55      | 2.94      | 2.40     | 2.55    | 2.84   | 3.25      | 4.09      |      |

300

180

95

55

380

243

160

122

573

435

353

314

927

810

728

679

1677

1560

1478

1429

μA

#### Table 28. Current consumption in Ru

Conditions

Voltage

scaling

Range 2

Range 1

2 MHz

1 MHz

400 kHz

100 kHz

242

130

61

26

275

162

90

56

384

269

197

163

562

445

374

339

924

809

734

702

1. Guaranteed by characterization results, unless otherwise specified.

$f_{HCLK} = f_{MSI}$

all peripherals disable

FLASH in power-down

$f_{HCLK} = f_{HSE}$  up to

peripherals disable

48MHz included,

bypass mode

48 MHz all

PLL ON above

92/193

Symbol

I<sub>DD</sub>(Run)

I<sub>DD</sub>(LPRun)

Parameter

Supply

current in

Run mode

Supply

current in

low-power

run mode

DocID027692 Rev 2

STM32L475xx

- 1. The BusMatrix is automatically active when at least one master is ON (CPU, DMA).

- 2. The GPIOx (x= A...H) dynamic current consumption is approximately divided by a factor two versus this table values when the GPIO port is locked thanks to LCKK and LCKy bits in the GPIOx\_LCKR register. In order to save the full GPIOx current consumption, the GPIOx clock should be disabled in the RCC when all port I/Os are used in alternate function or analog mode (clock is only required to read or write into GPIO registers, and is not used in AF or analog modes).

- 3. The AHB to APB1 Bridge is automatically active when at least one peripheral is ON on the APB1.

- 4. The AHB to APB2 Bridge is automatically active when at least one peripheral is ON on the APB2.

# 6.3.6 Wakeup time from low-power modes and voltage scaling transition times

The wakeup times given in *Table 41* are the latency between the event and the execution of the first user instruction.

The device goes in low-power mode after the WFE (Wait For Event) instruction.

| Symbol               | Parameter                                                           |                 | Conditions                                                                                                                          | Тур | Max        | Unit          |  |

|----------------------|---------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|------------|---------------|--|

| twusleep             | Wakeup time from Sleep mode to Run mode                             |                 | -<br>Wakeup in Flash with Flash in power-down during<br>ow-power sleep mode (SLEEP_PD=1 in<br>FLASH_ACR) and with clock MSI = 2 MHz |     |            | Nb of         |  |

| twulpsleep           | Wakeup time from Low-<br>power sleep mode to Low-<br>power run mode | low-power sleep |                                                                                                                                     |     |            | CPU<br>cycles |  |

|                      |                                                                     | Range 1         | Wakeup clock MSI = 48 MHz                                                                                                           | 5.6 | 10.9       |               |  |

|                      | Wake up time from Stop 0<br>mode to Run mode in Flash               | Range           | Wakeup clock HSI16 = 16 MHz                                                                                                         | 4.7 | 10.4       |               |  |

|                      |                                                                     |                 | Wakeup clock MSI = 24 MHz                                                                                                           | 5.7 | 11.1       |               |  |

|                      |                                                                     | Range 2         | Wakeup clock HSI16 = 16 MHz                                                                                                         | 4.5 | 10.5       |               |  |

| +                    |                                                                     |                 | Wakeup clock MSI = 4 MHz                                                                                                            | 6.6 | 14.2       |               |  |

| <sup>t</sup> WUSTOP0 |                                                                     | Panga 1         | Wakeup clock MSI = 48 MHz                                                                                                           | 0.7 | μs<br>2.05 |               |  |

|                      | Wake up time from Stop 0                                            | Range 1         | Wakeup clock HSI16 = 16 MHz                                                                                                         | 1.7 | 2.8        |               |  |

|                      | mode to Run mode in                                                 |                 | Wakeup clock MSI = 24 MHz                                                                                                           | 0.8 | 2.72       | 72            |  |

|                      | SRAM1                                                               | Range 2         | Wakeup clock HSI16 = 16 MHz                                                                                                         | 1.7 | 2.8        |               |  |

|                      |                                                                     |                 | Wakeup clock MSI = 4 MHz                                                                                                            | 2.4 | 11.32      |               |  |

## Table 41. Low-power mode wakeup timings<sup>(1)</sup>

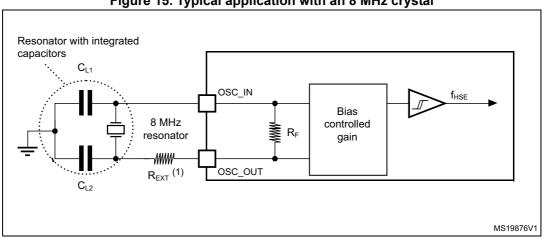

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Figure 15. Typical application with an 8 MHz crystal

1. R<sub>EXT</sub> value depends on the crystal characteristics.

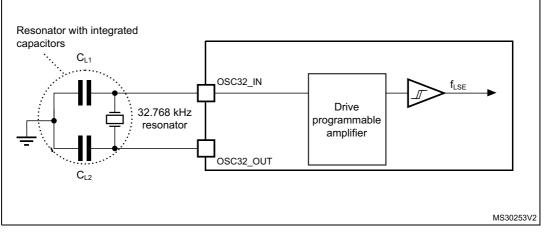

#### Low-speed external clock generated from a crystal resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 47*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| r                     | Table 47. LSE                  | oscillator characteristics (f <sub>LSE</sub> = 32.768 | KHZ) | ,<br> |      | i    |

|-----------------------|--------------------------------|-------------------------------------------------------|------|-------|------|------|

| Symbol                | Parameter                      | Conditions <sup>(2)</sup>                             | Min  | Тур   | Max  | Unit |

|                       |                                | LSEDRV[1:0] = 00<br>Low drive capability              | -    | 250   | -    |      |

|                       |                                | LSEDRV[1:0] = 01<br>Medium low drive capability       | -    | 315   | -    | 54   |

| I <sub>DD(LSE)</sub>  | LSE current consumption        | LSEDRV[1:0] = 10<br>Medium high drive capability      | -    | 500   | -    | nA   |

|                       |                                | LSEDRV[1:0] = 11<br>High drive capability             | -    | 630   | -    |      |

|                       | Maximum critical crystal<br>gm | LSEDRV[1:0] = 00<br>Low drive capability              | -    | -     | 0.5  |      |

| Gm                    |                                | LSEDRV[1:0] = 01<br>Medium low drive capability       | -    | -     | 0.75 | μA/V |

| Gm <sub>critmax</sub> |                                | LSEDRV[1:0] = 10<br>Medium high drive capability      | -    | -     | 1.7  |      |

|                       |                                | LSEDRV[1:0] = 11<br>High drive capability             | -    | -     | 2.7  |      |

| $t_{SU(LSE)}^{(3)}$   | Startup time                   | V <sub>DD</sub> is stabilized                         | -    | 2     | -    | s    |

| Table 47. LSE oscillator cha | racteristics (f <sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup> |

|------------------------------|-------------------------------------------------------------|

|                              |                                                             |

- 1. Guaranteed by design.

- 2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

- 3. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Figure 16. Typical application with a 32.768 kHz crystal

*Note:* An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions                                                          | Monitored<br>frequency band | Max vs.<br>[f <sub>HSE</sub> /f <sub>HCLK</sub> ]                     | Unit |

|------------------|------------|---------------------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------|------|

|                  |            |                                                                     |                             | Max vs.<br>[f <sub>HSE =</sub> 8 MHz /<br>f <sub>HCLK =</sub> 80 MHz] |      |

|                  |            |                                                                     | 0.1 MHz to 30 MHz           | -2                                                                    |      |

| 0                | Peak level | V <sub>DD</sub> = 3.6 V, T <sub>A</sub> = 25 °C,<br>LQFP100 package | 30 MHz to 130 MHz           | -9                                                                    | dBµV |

| S <sub>EMI</sub> | reak level | compliant with<br>IEC 61967-2                                       | 130 MHz to 1 GHz            | 6                                                                     |      |

|                  |            | IEC 01907-2                                                         | EMI Level                   | 3.5                                                                   | -    |

Table 55. EMI characteristics

## 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

## Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the ANSI/JEDEC standard.

| Table 56. | ESD | absolute | maximum | ratings |

|-----------|-----|----------|---------|---------|

|           |     | 40001410 |         |         |

| Symbol                | Ratings                                               | Conditions                                                    | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|---------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = +25$ °C, conforming<br>to ANSI/ESDA/JEDEC<br>JS-001    | 2     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | $T_A = +25 \text{ °C},$<br>conforming to ANSI/ESD<br>STM5.3.1 | C3    | 250                             | v    |

1. Guaranteed by characterization results.

| Symbol           | Parameter                                          | Conditions                                                                                                                | Min | Тур | Max                    | Unit |

|------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------|------|

|                  |                                                    | $V_{IN} \le Max(V_{DDXXX})^{(4)}$                                                                                         | -   | -   | ±100                   |      |

|                  | FT_xx input leakage current <sup>(3)</sup>         | $\begin{array}{l} Max(V_{DDXXX}) \leq V_{IN} \leq \\ Max(V_{DDXXX}) + 1 \ V^{(4)(5)} \end{array}$                         | -   | -   | 650 <sup>(3)(6)</sup>  |      |

|                  |                                                    | $\begin{array}{l} {\sf Max}({\sf V}_{{\sf DDXXX}})\text{+}1~{\sf V} < \\ {\sf VIN} \leq 5.5~{\sf V}^{(3)(5)} \end{array}$ | -   | -   | 200 <sup>(6)</sup>     |      |

|                  |                                                    | $V_{IN} \le Max(V_{DDXXX})^{(4)}$                                                                                         | -   | -   | ±150                   |      |

| l <sub>lkg</sub> | FT_lu, FT_u and<br>PC3 IO                          | $\begin{array}{l} Max(V_{DDXXX}) \leq V_{IN} \leq \\ Max(V_{DDXXX}) + 1 \ V^{(4)} \end{array}$                            | -   | -   | 2500 <sup>(3)(7)</sup> | nA   |

|                  |                                                    | Max(V <sub>DDXXX</sub> )+1 V < VIN ≤ 5.5 V <sup>(4)(5)(7)</sup>                                                           | -   | -   | 250 <sup>(7)</sup>     |      |

|                  | TT_xx input leakage                                | $V_{IN} \le Max(V_{DDXXX})^{(6)}$                                                                                         | -   | -   | ±150                   |      |

|                  | current                                            | Max(V <sub>DDXXX</sub> ) ≤ V <sub>IN</sub> < 3.6 V <sup>(6)</sup>                                                         | -   | -   | 2000 <sup>(3)</sup>    |      |

| R <sub>PU</sub>  | Weak pull-up<br>equivalent resistor <sup>(8)</sup> | V <sub>IN</sub> = V <sub>SS</sub>                                                                                         | 25  | 40  | 55                     | kΩ   |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(8)</sup>  | V <sub>IN</sub> = V <sub>DDIOx</sub>                                                                                      | 25  | 40  | 55                     | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                                | -                                                                                                                         | -   | 5   | -                      | pF   |

Table 59. I/O static characteristics (continued)

1. Refer to Figure 19: I/O input characteristics.

- 2. Tested in production.

- 3. Guaranteed by design.

- 4. Max(V<sub>DDXXX</sub>) is the maximum value of all the I/O supplies. Refer to Table: Legend/Abbreviations used in the pinout table.

- 5. All TX\_xx IO except FT\_lu, FT\_u and PC3.

- 6. This value represents the pad leakage of the IO itself. The total product pad leakage is provided by this formula:  $I_{Total\_Ileak\_max} = 10 \ \mu A + [number of IOs where V_{IN} is applied on the pad] \times I_{Ikg}(Max)$ .

- 7. To sustain a voltage higher than MIN(V<sub>DD</sub>, V<sub>DDA</sub>, V<sub>DDUSB</sub>) +0.3 V, the internal Pull-up and Pull-Down resistors must be disabled.

- Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

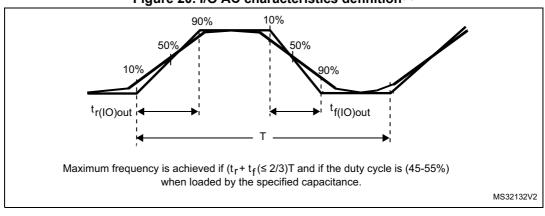

1. Refer to Table 61: I/O AC characteristics.

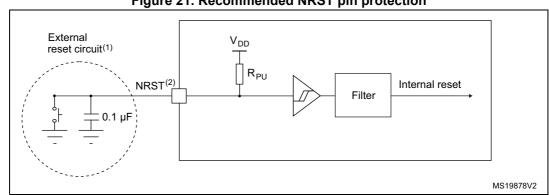

## 6.3.15 NRST pin characteristics

The NRST pin input driver uses the CMOS technology. It is connected to a permanent pull-up resistor,  $\mathsf{R}_{\mathsf{PU}}.$

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 22: General operating conditions*.

| Symbol                 | Parameter                                          | Conditions                        | Min                                 | Тур | Мах                                 | Unit |

|------------------------|----------------------------------------------------|-----------------------------------|-------------------------------------|-----|-------------------------------------|------|

| V <sub>IL(NRST)</sub>  | NRST input low level voltage                       | -                                 | -                                   | -   | 0.3 <sub>x</sub> V <sub>DDIOx</sub> | v    |

| V <sub>IH(NRST)</sub>  | NRST input high level voltage                      | -                                 | 0.7 <sub>x</sub> V <sub>DDIOx</sub> | -   | -                                   | v    |

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage hysteresis            | -                                 | -                                   | 200 | -                                   | mV   |

| R <sub>PU</sub>        | Weak pull-up<br>equivalent resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                                  | 40  | 55                                  | kΩ   |

| V <sub>F(NRST)</sub>   | NRST input filtered<br>pulse                       | -                                 | -                                   | -   | 70                                  | ns   |

| V <sub>NF(NRST)</sub>  | NRST input not filtered pulse                      | 1.71 V ≤ V <sub>DD</sub> ≤ 3.6 V  | 350                                 | -   | -                                   | ns   |

Table 62. NRST pin characteristics<sup>(1)</sup>

1. Guaranteed by design.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

Figure 21. Recommended NRST pin protection

1. The reset network protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 62: NRST pin characteristics. Otherwise the reset will not be taken into account by the device.

## 6.3.16 Analog switches booster

| Symbol                 | Parameter                                                         | Min  | Тур | Мах | Unit |

|------------------------|-------------------------------------------------------------------|------|-----|-----|------|

| V <sub>DD</sub>        | Supply voltage                                                    | 1.62 | -   | 3.6 | v    |

| V <sub>BOOST</sub>     | Boost supply                                                      | 2.7  | -   | 4   | v    |

| t <sub>SU(BOOST)</sub> | Booster startup time                                              | -    | -   | 240 | μs   |

|                        | Booster consumption for $1.62 \vee \leq V_{DD} \leq 2.0 \vee$     | -    | -   | 250 |      |

| I <sub>DD(BOOST)</sub> | Booster consumption for 2.0 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V | -    | -   | 500 | μA   |

|                        | Booster consumption for 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V | -    | -   | 900 |      |

Table 63. Analog switches booster characteristics<sup>(1)</sup>

1. Guaranteed by design.

|             | Table 00. Abc accuracy - initied test conditions 1. A A A (continued)                      |                             |                          |                          |     |      |     |    |

|-------------|--------------------------------------------------------------------------------------------|-----------------------------|--------------------------|--------------------------|-----|------|-----|----|

| Sym-<br>bol | Parameter                                                                                  | C                           | Min                      | Тур                      | Max | Unit |     |    |

|             |                                                                                            | ADC clock frequency ≤       | Single                   | Fast channel (max speed) | -   | -74  | -73 |    |

| THD         | Total80 MHz,harmonicSampling rate $\leq$ 5.33 Msps,distortion $V_{DDA} = V_{REF+} = 3 V$ , | ended                       | Slow channel (max speed) | -                        | -74 | -73  | dB  |    |

|             |                                                                                            | $V_{DDA} = V_{REF+} = 3 V,$ | Differential             | Fast channel (max speed) | -   | -79  | -76 | uв |

|             |                                                                                            | TA = 25 °C                  | Differential             | Slow channel (max speed) | -   | -79  | -76 |    |

| Table 66. ADC accuracy - limited test conditions 1 <sup>(1)(2)(3)</sup> (continu |

|----------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------|

1. Guaranteed by design.

2. ADC DC accuracy values are measured after internal calibration.

- 3. ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

- 4. The I/O analog switch voltage booster is enable when V<sub>DDA</sub> < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when V<sub>DDA</sub> < 2.4 V). It is disable when V<sub>DDA</sub>  $\geq$  2.4 V. No oversampling.

| Sym-<br>bol | Parameter               | (                                | Conditions <sup>(4</sup> | )                        | Min  | Тур  | Max | Unit  |

|-------------|-------------------------|----------------------------------|--------------------------|--------------------------|------|------|-----|-------|

|             |                         |                                  | Single                   | Fast channel (max speed) | -    | 4    | 6.5 |       |

| ET          | Total                   |                                  | ended                    | Slow channel (max speed) | -    | 4    | 6.5 |       |

|             | unadjusted<br>error     |                                  | Differential             | Fast channel (max speed) | -    | 3.5  | 5.5 |       |

|             |                         |                                  | Dillerential             | Slow channel (max speed) | -    | 3.5  | 5.5 |       |

|             |                         |                                  | Single                   | Fast channel (max speed) | -    | 1    | 4.5 |       |

| EO          | Offset                  |                                  | ended                    | Slow channel (max speed) | -    | 1    | 5   |       |

| EU          | error                   |                                  | Differential             | Fast channel (max speed) | -    | 1.5  | 3   |       |

|             |                         |                                  | Dillerential             | Slow channel (max speed) | -    | 1.5  | 3   |       |

|             |                         |                                  | Single                   | Fast channel (max speed) | -    | 2.5  | 6   |       |

| EG          | Gain error              |                                  | ended                    | Slow channel (max speed) | -    | 2.5  | 6   |       |

| EG          | Gainenor                |                                  | Differential             | Fast channel (max speed) | -    | 2.5  | 3.5 | - LSB |

|             |                         |                                  | Differential             | Slow channel (max speed) | -    | 2.5  | 3.5 |       |

|             |                         |                                  | Single                   | Fast channel (max speed) | -    | 1    | 1.5 |       |

| ED          | Differential linearity  |                                  | ended                    | Slow channel (max speed) | -    | 1    | 1.5 |       |

| ED          | error                   | ADC clock frequency ≤<br>80 MHz, | Differential             | Fast channel (max speed) | -    | 1    | 1.2 |       |

|             |                         |                                  |                          | Slow channel (max speed) | -    | 1    | 1.2 | -     |

|             |                         | Sampling rate $\leq 5.33$ Msps,  | Single                   | Fast channel (max speed) | -    | 1.5  | 3.5 |       |

| EL          | Integral                | $2 V \leq V_{DDA}$               | ended                    | Slow channel (max speed) | -    | 1.5  | 3.5 |       |

| EL          | linearity<br>error      |                                  | Differential             | Fast channel (max speed) | -    | 1    | 3   |       |

|             |                         |                                  | Differential             | Slow channel (max speed) | -    | 1    | 2.5 |       |

|             |                         |                                  | Single                   | Fast channel (max speed) | 10   | 10.5 | -   |       |

| ENOB        | Effective               |                                  | ended                    | Slow channel (max speed) | 10   | 10.5 | -   | hita  |

| ENUD        | number of bits          |                                  | Differential             | Fast channel (max speed) | 10.7 | 10.9 | -   | bits  |

|             |                         |                                  | Differential             | Slow channel (max speed) | 10.7 | 10.9 | -   |       |

|             | Oisse al ta             |                                  | Single                   | Fast channel (max speed) | 62   | 65   | -   |       |

| SINAD       | Signal-to-<br>noise and |                                  | ended                    | Slow channel (max speed) | 62   | 65   | -   |       |

| SINAD       | distortion              |                                  | Differential             | Fast channel (max speed) | 66   | 67.4 | -   |       |

|             | ratio                   |                                  | Differential             | Slow channel (max speed) | 66   | 67.4 | -   |       |

|             |                         |                                  | Single                   | Fast channel (max speed) | 64   | 66   | -   | dB    |

|             | Signal-to-              |                                  | ended                    | Slow channel (max speed) | 64   | 66   | -   |       |

| SNR         | noise ratio             |                                  | Differential             | Fast channel (max speed) | 66.5 | 68   | -   |       |

|             |                         |                                  | Differential             | Slow channel (max speed) | 66.5 | 68   | -   |       |

|             | Table 01. Abo accuracy - minted test conditions 2 (continued) |                                                    |              |                          |     |      |     |    |

|-------------|---------------------------------------------------------------|----------------------------------------------------|--------------|--------------------------|-----|------|-----|----|

| Sym-<br>bol | Parameter                                                     | C                                                  | Min          | Тур                      | Max | Unit |     |    |

|             |                                                               | ADC clock frequency ≤                              | Single       | Fast channel (max speed) | -   | -74  | -65 |    |

| THD         | Total                                                         | otal 80 MHz,<br>armonic Sampling rate ≤ 5.33 Msps, | ended        | Slow channel (max speed) | -   | -74  | -67 | dB |

|             | distortion                                                    |                                                    | Differential | Fast channel (max speed) | -   | -79  | -70 | uВ |

|             |                                                               |                                                    |              | Slow channel (max speed) | -   | -79  | -71 |    |

Table 67. ADC accuracy - limited test conditions  $2^{(1)(2)(3)}$  (continued)

1. Guaranteed by design.

2. ADC DC accuracy values are measured after internal calibration.

- 3. ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

- 4. The I/O analog switch voltage booster is enable when V<sub>DDA</sub> < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when V<sub>DDA</sub> < 2.4 V). It is disable when V<sub>DDA</sub>  $\geq$  2.4 V. No oversampling.

| Sym-<br>bol | Parameter               | (                                                              | Conditions <sup>(4</sup> | )                        | Min  | Тур  | Max | Unit                 |

|-------------|-------------------------|----------------------------------------------------------------|--------------------------|--------------------------|------|------|-----|----------------------|

|             |                         |                                                                | Single                   | Fast channel (max speed) | -    | 5.5  | 7.5 |                      |

| ET          | Total                   |                                                                | ended                    | Slow channel (max speed) | -    | 4.5  | 6.5 |                      |

|             | unadjusted<br>error     |                                                                | Differential             | Fast channel (max speed) | -    | 4.5  | 7.5 |                      |

|             |                         |                                                                | Dillerential             | Slow channel (max speed) | -    | 4.5  | 5.5 |                      |

|             |                         |                                                                | Single                   | Fast channel (max speed) | -    | 2    | 5   |                      |

| EO          | Offset                  |                                                                | ended                    | Slow channel (max speed) | -    | 2.5  | 5   |                      |

| EU          | error                   |                                                                | Differential             | Fast channel (max speed) | -    | 2    | 3.5 |                      |

|             |                         |                                                                | Differential             | Slow channel (max speed) | -    | 2.5  | 3   |                      |

|             |                         |                                                                | Single                   | Fast channel (max speed) | -    | 4.5  | 7   |                      |

| EG          | Gain error              |                                                                | ended                    | Slow channel (max speed) | -    | 3.5  | 6   |                      |

| EG          | Gainenor                |                                                                | Differential             | Fast channel (max speed) | -    | 3.5  | 4   | - LSB<br>-<br>-<br>- |

|             |                         |                                                                | Dillerential             | Slow channel (max speed) | -    | 3.5  | 5   |                      |

|             |                         |                                                                | Single                   | Fast channel (max speed) | -    | 1.2  | 1.5 |                      |

| ED          | Differential linearity  |                                                                | ended                    | Slow channel (max speed) | -    | 1.2  | 1.5 |                      |

| ED          | error                   | ADC clock frequency ≤<br>80 MHz,<br>Sampling rate ≤ 5.33 Msps, | Differential             | Fast channel (max speed) | -    | 1    | 1.2 |                      |

|             |                         |                                                                |                          | Slow channel (max speed) | -    | 1    | 1.2 |                      |

|             |                         | 1.65 V ≤ V <sub>DDA</sub> = V <sub>REF+</sub> ≤<br>3.6 V,      | Single                   | Fast channel (max speed) | -    | 3    | 3.5 |                      |

| EL          | Integral<br>linearity   | S.o v,<br>Voltage scaling Range 1                              | ended                    | Slow channel (max speed) | -    | 2.5  | 3.5 |                      |

| EL          | error                   |                                                                | Differential             | Fast channel (max speed) | -    | 2    | 2.5 |                      |

|             |                         |                                                                | Dillerential             | Slow channel (max speed) | -    | 2    | 2.5 |                      |

|             |                         |                                                                | Single                   | Fast channel (max speed) | 10   | 10.4 | -   |                      |

| ENOB        | Effective number of     |                                                                | ended                    | Slow channel (max speed) | 10   | 10.4 | -   | bits                 |

| ENOD        | bits                    |                                                                | Differential             | Fast channel (max speed) | 10.6 | 10.7 | -   | DILS                 |

|             |                         |                                                                | Dillerential             | Slow channel (max speed) | 10.6 | 10.7 | -   |                      |

|             | Cignal to               |                                                                | Single                   | Fast channel (max speed) | 62   | 64   | -   |                      |

| SINAD       | Signal-to-<br>noise and |                                                                | ended                    | Slow channel (max speed) | 62   | 64   | -   |                      |

| SINAD       | distortion<br>ratio     |                                                                | Differential             | Fast channel (max speed) | 65   | 66   | -   |                      |

|             | 1400                    | Differen                                                       |                          | Slow channel (max speed) | 65   | 66   | -   | ٩D                   |

|             |                         |                                                                | Single                   | Fast channel (max speed) | 63   | 65   | -   | dB                   |

| SNR         | Signal-to-              |                                                                | ended                    | Slow channel (max speed) | 63   | 65   | -   | 1                    |

| SINK        | noise ratio             |                                                                | Differential             | Fast channel (max speed) | 66   | 67   | -   |                      |

|             |                         |                                                                | Differential             | Slow channel (max speed) | 66   | 67   | -   |                      |

| Symbol                                               | Parameter                    | Conditions               | Min | Тур | Max | Unit |  |

|------------------------------------------------------|------------------------------|--------------------------|-----|-----|-----|------|--|

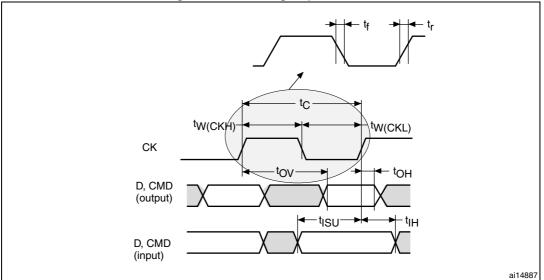

| CMD, D outputs (referenced to CK) in SD default mode |                              |                          |     |     |     |      |  |

| t <sub>OVD</sub>                                     | Output valid default time SD | f <sub>PP</sub> = 50 MHz | -   | 4.5 | 5   | ns   |  |

| t <sub>OHD</sub>                                     | Output hold default time SD  | f <sub>PP</sub> = 50 MHz | 0   | -   | -   | ns   |  |

Table 87. SD / MMC dynamic characteristics,  $V_{DD}$ =2.7 V to 3.6 V<sup>(1)</sup> (continued)

1. Guaranteed by characterization results.

| Table 88. eMMC dynamic characteristics, $V_{DD} = 1.71 \text{ V to } 1.9 \text{ V}^{(1)(2)}$ |

|----------------------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------------|

| Symbol                                         | Parameter                                  | Conditions               | Min | Тур  | Max  | Unit |  |  |

|------------------------------------------------|--------------------------------------------|--------------------------|-----|------|------|------|--|--|

| f <sub>PP</sub>                                | Clock frequency in data transfer mode      | -                        | 0   | -    | 50   | MHz  |  |  |

| -                                              | SDIO_CK/f <sub>PCLK2</sub> frequency ratio | -                        | -   | -    | 4/3  | -    |  |  |

| t <sub>W(CKL)</sub>                            | Clock low time                             | f <sub>PP</sub> = 50 MHz | 8   | 10   | -    | ns   |  |  |

| t <sub>W(CKH)</sub>                            | Clock high time                            | f <sub>PP</sub> = 50 MHz | 8   | 10   | -    | ns   |  |  |

| CMD, D inputs (referenced to CK) in eMMC mode  |                                            |                          |     |      |      |      |  |  |

| t <sub>ISU</sub>                               | Input setup time HS                        | f <sub>PP</sub> = 50 MHz | 0   | -    | -    | ns   |  |  |

| t <sub>IH</sub>                                | Input hold time HS                         | f <sub>PP</sub> = 50 MHz | 5   | -    | -    | ns   |  |  |

| CMD, D outputs (referenced to CK) in eMMC mode |                                            |                          |     |      |      |      |  |  |

| t <sub>OV</sub>                                | Output valid time HS                       | f <sub>PP</sub> = 50 MHz | -   | 13.5 | 15.5 | ns   |  |  |

| t <sub>OH</sub>                                | Output hold time HS                        | f <sub>PP</sub> = 50 MHz | 9   | -    | -    | ns   |  |  |

|                                                |                                            |                          |     |      |      |      |  |  |

1. Guaranteed by characterization results.

2. C<sub>LOAD</sub> = 20pF.

| Figure | 32. | SDIO | high-speed mode |  |

|--------|-----|------|-----------------|--|

| iguio  | ~~. | 0010 | mgn opooa moao  |  |

DocID027692 Rev 2

| Currente al | millimeters |        |        | inches <sup>(1)</sup> |        |        |  |

|-------------|-------------|--------|--------|-----------------------|--------|--------|--|

| Symbol      | Min         | Тур    | Мах    | Min                   | Тур    | Max    |  |

| А           | -           | -      | 1.600  | -                     | -      | 0.0630 |  |

| A1          | 0.050       | -      | 0.150  | 0.0020                | -      | 0.0059 |  |

| A2          | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |

| b           | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |

| С           | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |  |

| D           | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| D1          | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| D3          | -           | 12.000 | -      | -                     | 0.4724 | -      |  |

| Е           | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| E1          | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| E3          | -           | 12.000 | -      | -                     | 0.4724 | -      |  |

| е           | -           | 0.500  | -      | -                     | 0.0197 | -      |  |

| L           | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |

| L1          | -           | 1.000  | -      | -                     | 0.0394 | -      |  |

| k           | 0.0°        | 3.5°   | 7.0°   | 0.0°                  | 3.5°   | 7.0°   |  |

| CCC         | -           | -      | 0.080  | -                     | -      | 0.0031 |  |

| Table 96. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package |

|-----------------------------------------------------------------------|

| mechanical data                                                       |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

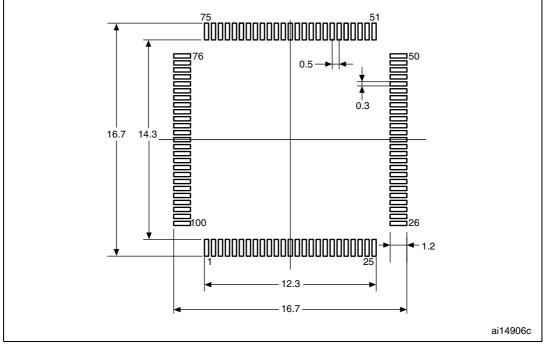

# Figure 39. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

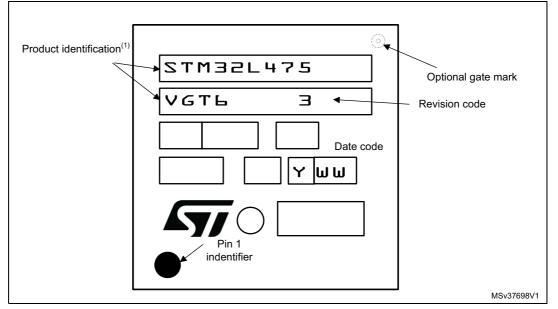

## **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 40. LQFP100 marking (package top view)

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering

samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

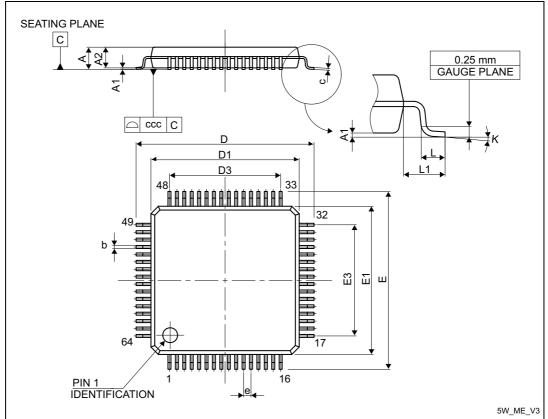

## 7.2 LQFP64 package information

Figure 41. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Table 97. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat |

|-------------------------------------------------------------|

| package mechanical data                                     |

| Symbol | millimeters |        |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|--------|-------|-----------------------|--------|--------|--|

|        | Min         | Тур    | Мах   | Min                   | Тур    | Max    |  |

| А      | -           | -      | 1.600 | -                     | -      | 0.0630 |  |

| A1     | 0.050       | -      | 0.150 | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350       | 1.400  | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170       | 0.220  | 0.270 | 0.0067                | 0.0087 | 0.0106 |  |

| с      | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |  |

| D      | -           | 12.000 | -     | -                     | 0.4724 | -      |  |

| D1     | -           | 10.000 | -     | -                     | 0.3937 | -      |  |

| D3     | -           | 7.500  | -     | -                     | 0.2953 | -      |  |