# E·XFL

#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                                              |

|----------------------------|-----------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                                  |

| Speed                      | 80MHz                                                                                               |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                                               |

| Number of I/O              | 82                                                                                                  |

| Program Memory Size        | 512KB (512K x 8)                                                                                    |

| Program Memory Type        | FLASH                                                                                               |

| EEPROM Size                | -                                                                                                   |

| RAM Size                   | 128K x 8                                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                                        |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                               |

| Oscillator Type            | Internal                                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                   |

| Mounting Type              | Surface Mount                                                                                       |

| Package / Case             | 100-LQFP                                                                                            |

| Supplier Device Package    | 100-LQFP (14x14)                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l475vet6                               |

|                            |                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |       | 6.3.26   | Communication interfaces characteristics | 161 |

|---|-------|----------|------------------------------------------|-----|

|   |       | 6.3.27   | FSMC characteristics                     | 173 |

| 7 | Pack  | age info | ormation                                 | 182 |

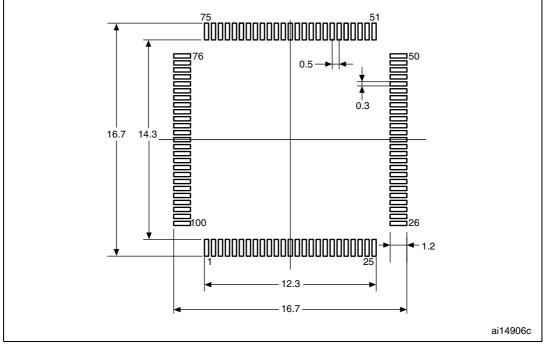

|   | 7.1   | LQFP1    | 00 package information                   | 182 |

|   | 7.2   | LQFP6    | 4 package information                    | 185 |

|   | 7.3   | Therma   | al characteristics                       | 188 |

|   |       | 7.3.1    | Reference document                       | 188 |

|   |       | 7.3.2    | Selecting the product temperature range  | 188 |

| 8 | Part  | number   | ing                                      | 191 |

| 9 | Revis | sion his | tory                                     | 192 |

|          | Table 4. STM32L475 modes overview (continued) |                |       |                |            |                                                                                                                                              |                                                               |                                   |             |  |  |

|----------|-----------------------------------------------|----------------|-------|----------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------|-------------|--|--|

| Mode     | Regulator<br>(1)                              | CPU            | Flash | SRAM           | Clocks     | DMA & Peripherals <sup>(2)</sup>                                                                                                             | Wakeup source                                                 | Consumption <sup>(3)</sup>        | Wakeup time |  |  |

|          | LPR                                           |                |       | SRAM2<br>ON    |            | BOR, RTC, IWDG<br>***                                                                                                                        |                                                               | 0.35 μA w/o RTC<br>0.65 μA w/ RTC |             |  |  |

| Standby  | OFF                                           | Powered<br>Off | Off   | Powered<br>Off | LSE<br>LSI | All other peripherals are<br>powered off.<br>***<br>I/O configuration can be<br>floating, pull-up or pull-down                               | Reset pin<br>5 I/Os (WKUPx) <sup>(10)</sup><br>BOR, RTC, IWDG | 0.12 μA w/o RTC<br>0.42 μA w/ RTC | 14 µs       |  |  |

| Shutdown | OFF                                           | Powered<br>Off | Off   | Powered<br>Off | LSE        | RTC<br>***<br>All other peripherals are<br>powered off.<br>***<br>I/O configuration can be<br>floating, pull-up or pull-down <sup>(11)</sup> | Reset pin<br>5 I/Os (WKUPx) <sup>(10)</sup><br>RTC            | 0.03 μA w/o RTC<br>0.33 μA w/ RTC | 256 µs      |  |  |

1. LPR means Main regulator is OFF and Low-power regulator is ON.

2. All peripherals can be active or clock gated to save power consumption.

3. Typical current at V<sub>DD</sub> = 1.8 V, 25°C. Consumptions values provided running from SRAM, Flash memory Off, 80 MHz in Range 1, 26 MHz in Range 2, 2 MHz in LPRun/LPSleep.

4. The Flash memory can be put in power-down and its clock can be gated off when executing from SRAM.

5. The SRAM1 and SRAM2 clocks can be gated on or off independently.

6. U(S)ART and LPUART reception is functional in Stop mode, and generates a wakeup interrupt on Start, address match or received frame event.

7. I2C address detection is functional in Stop mode, and generates a wakeup interrupt in case of address match.

8. OTG\_FS wakeup by resume from suspend and attach detection protocol event.

9. SWPMI1 wakeup by resume from suspend.

10. The I/Os with wakeup from Standby/Shutdown capability are: PA0, PC13, PE6, PA2, PC5.

11. I/Os can be configured with internal pull-up, pull-down or floating in Shutdown mode but the configuration is lost when exiting the Shutdown mode.

23/193

Standby mode, supplied by the low-power Regulator (Standby with RAM2 retention mode).

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, WKUP pin event (configurable rising or falling edge), or an RTC event occurs (alarm, periodic wakeup, timestamp, tamper) or a failure is detected on LSE (CSS on LSE).

The system clock after wakeup is MSI up to 8 MHz.

Shutdown mode

The Shutdown mode allows to achieve the lowest power consumption. The internal regulator is switched off so that the VCORE domain is powered off. The PLL, the HSI16, the MSI, the LSI and the HSE oscillators are also switched off.

The RTC can remain active (Shutdown mode with RTC, Shutdown mode without RTC).

The BOR is not available in Shutdown mode. No power voltage monitoring is possible in this mode, therefore the switch to Backup domain is not supported.

SRAM1, SRAM2 and register contents are lost except for registers in the Backup domain.

The device exits Shutdown mode when an external reset (NRST pin), a WKUP pin event (configurable rising or falling edge), or an RTC event occurs (alarm, periodic wakeup, timestamp, tamper).

The system clock after wakeup is MSI at 4 MHz.

### 3.11 Clocks and startup

The clock controller (see *Figure 3*) distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

- Clock prescaler: to get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler

- **Safe clock switching:** clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management:** to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- System clock source: four different clock sources can be used to drive the master clock SYSCLK:

- 4-48 MHz high-speed external crystal or ceramic resonator (HSE), that can supply a PLL. The HSE can also be configured in bypass mode for an external clock.

- 16 MHz high-speed internal RC oscillator (HSI16), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 12 frequencies from 100 kHz to 48 MHz. When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be automatically trimmed by hardware to reach better than ±0.25% accuracy. In this mode the MSI can feed the USB device, saving the need of an external high-speed crystal (HSE). The MSI can supply a PLL.

- System PLL which can be fed by HSE, HSI16 or MSI, with a maximum frequency at 80 MHz.

- **Auxiliary clock source:** two ultralow-power clock sources that can be used to drive the real-time clock:

- 32.768 kHz low-speed external crystal (LSE), supporting four drive capability modes. The LSE can also be configured in bypass mode for an external clock.

- 32 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock accuracy is ±5% accuracy.

- **Peripheral clock sources:** Several peripherals (USB, SDMMC, RNG, SAI, USARTs, I2Cs, LPTimers, ADC, SWPMI) have their own independent clock whatever the system clock. Three PLLs, each having three independent outputs allowing the highest flexibility, can generate independent clocks for the ADC, the USB/SDMMC/RNG and the two SAIs.

- **Startup clock:** after reset, the microcontroller restarts by default with an internal 4 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- **Clock security system (CSS):** this feature can be enabled by software. If a HSE clock failure occurs, the master clock is automatically switched to HSI16 and a software

### 3.23.3 Basic timers (TIM6 and TIM7)

The basic timers are mainly used for DAC trigger generation. They can also be used as generic 16-bit timebases.

### 3.23.4 Low-power timer (LPTIM1 and LPTIM2)

The devices embed two low-power timers. These timers have an independent clock and are running in Stop mode if they are clocked by LSE, LSI or an external clock. They are able to wakeup the system from Stop mode.

LPTIM1 is active in Stop 0, Stop 1 and Stop 2 modes.

LPTIM2 is active in Stop 0 and Stop 1 mode.

This low-power timer supports the following features:

- 16-bit up counter with 16-bit autoreload register

- 16-bit compare register

- Configurable output: pulse, PWM

- Continuous/ one shot mode

- Selectable software/hardware input trigger

- Selectable clock source

- Internal clock sources: LSE, LSI, HSI16 or APB clock

- External clock source over LPTIM input (working even with no internal clock source running, used by pulse counter application).

- Programmable digital glitch filter

- Encoder mode (LPTIM1 only)

### 3.23.5 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC (LSI) and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

### 3.23.6 System window watchdog (WWDG)

The window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

# 3.28 Serial peripheral interface (SPI)

Three SPI interfaces allow communication up to 40 Mbits/s in master and up to 24 Mbits/s slave modes, in half-duplex, full-duplex and simplex modes. The 3-bit prescaler gives 8 master mode frequencies and the frame size is configurable from 4 bits to 16 bits. The SPI interfaces support NSS pulse mode, TI mode and Hardware CRC calculation.

All SPI interfaces can be served by the DMA controller.

## 3.29 Serial audio interfaces (SAI)

The device embeds 2 SAI. Refer to *Table 13: SAI implementation* for the features implementation. The SAI bus interface handles communications between the microcontroller and the serial audio protocol.

The SAI peripheral supports:

- Two independent audio sub-blocks which can be transmitters or receivers with their respective FIFO.

- 8-word integrated FIFOs for each audio sub-block.

- Synchronous or asynchronous mode between the audio sub-blocks.

- Master or slave configuration independent for both audio sub-blocks.

- Clock generator for each audio block to target independent audio frequency sampling when both audio sub-blocks are configured in master mode.

- Data size configurable: 8-, 10-, 16-, 20-, 24-, 32-bit.

- Peripheral with large configurability and flexibility allowing to target as example the following audio protocol: I2S, LSB or MSB-justified, PCM/DSP, TDM, AC'97 and SPDIF out.

- Up to 16 slots available with configurable size and with the possibility to select which ones are active in the audio frame.

- Number of bits by frame may be configurable.

- Frame synchronization active level configurable (offset, bit length, level).

- First active bit position in the slot is configurable.

- LSB first or MSB first for data transfer.

- Mute mode.

- Stereo/Mono audio frame capability.

- Communication clock strobing edge configurable (SCK).

- Error flags with associated interrupts if enabled respectively.

- Overrun and underrun detection.

- Anticipated frame synchronization signal detection in slave mode.

- Late frame synchronization signal detection in slave mode.

- Codec not ready for the AC'97 mode in reception.

- Interruption sources when enabled:

- Errors.

- FIFO requests.

- DMA interface with 2 dedicated channels to handle access to the dedicated integrated FIFO of each SAI audio sub-block.

- Transmission

- Three transmit mailboxes

- Configurable transmit priority

- Reception

- Two receive FIFOs with three stages

- 14 Scalable filter banks

- Identifier list feature

- Configurable FIFO overrun

- Time-triggered communication option

- Disable automatic retransmission mode

- 16-bit free running timer

- Time Stamp sent in last two data bytes

- Management

- Maskable interrupts

- Software-efficient mailbox mapping at a unique address space

# 3.32 Secure digital input/output and MultiMediaCards Interface (SDMMC)

The card host interface (SDMMC) provides an interface between the APB peripheral bus and MultiMediaCards (MMCs), SD memory cards and SDIO cards.

The SDMMC features include the following:

- Full compliance with MultiMediaCard System Specification Version 4.2. Card support for three different databus modes: 1-bit (default), 4-bit and 8-bit

- Full compatibility with previous versions of MultiMediaCards (forward compatibility)

- Full compliance with SD Memory Card Specifications Version 2.0

- Full compliance with SD I/O Card Specification Version 2.0: card support for two different databus modes: 1-bit (default) and 4-bit

- Data transfer up to 48 MHz for the 8 bit mode

- Data write and read with DMA capability

# 3.33 Universal serial bus on-the-go full-speed (OTG\_FS)

The devices embed an USB OTG full-speed device/host/OTG peripheral with integrated transceivers. The USB OTG FS peripheral is compliant with the USB 2.0 specification and with the OTG 2.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG controller requires a dedicated 48 MHz clock that can be provided by the internal multispeed oscillator (MSI) automatically trimmed by 32.768 kHz external oscillator (LSE). This allows to use the USB device without external high speed crystal (HSE).

| Na        | me                     | Abbreviation                                                                    | Definition                                                                 |  |  |  |  |

|-----------|------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|

| Pin r     | name                   | Unless otherwise specified in reset is the same as the actu                     | brackets below the pin name, the pin function during and after al pin name |  |  |  |  |

|           |                        | S                                                                               | Supply pin                                                                 |  |  |  |  |

| Pin       | type                   | I                                                                               | Input only pin                                                             |  |  |  |  |

|           |                        | I/O                                                                             | Input / output pin                                                         |  |  |  |  |

|           |                        | FT                                                                              | 5 V tolerant I/O                                                           |  |  |  |  |

|           |                        | TT                                                                              | 3.6 V tolerant I/O                                                         |  |  |  |  |

|           |                        | B Dedicated BOOT0 pin                                                           |                                                                            |  |  |  |  |

|           |                        | RST Bidirectional reset pin with embedded weak pull-up r                        |                                                                            |  |  |  |  |

| I/O str   | ructure                | Option for TT or FT I/Os                                                        |                                                                            |  |  |  |  |

|           |                        | _f <sup>(1)</sup> I/O, Fm+ capable                                              |                                                                            |  |  |  |  |

|           |                        | _u <sup>(2)</sup> I/O, with USB function supplied by V <sub>DDUSB</sub>         |                                                                            |  |  |  |  |

|           |                        | _a <sup>(3)</sup> I/O, with Analog switch function supplied by V <sub>DDA</sub> |                                                                            |  |  |  |  |

| No        | otes                   | Unless otherwise specified by                                                   | y a note, all I/Os are set as analog inputs during and after reset.        |  |  |  |  |

| Pin       | Alternate<br>functions | Functions selected through GPIOx_AFR registers                                  |                                                                            |  |  |  |  |

| functions | Additional functions   | Functions directly selected/enabled through peripheral registers                |                                                                            |  |  |  |  |

| Table 14. Legend/abbreviations used in the | ninout table |

|--------------------------------------------|--------------|

| Table 14. Legend/abbreviations used in the | pinout table |

1. The related I/O structures in *Table 15* are: FT\_f, FT\_fa, FT\_f, FT\_fa.

2. The related I/O structures in *Table 15* are: FT\_u.

3. The related I/O structures in *Table 15* are: FT\_a, FT\_fa, TT\_a.

| Table 15. STM32L475xx | pin | definitions |

|-----------------------|-----|-------------|

|-----------------------|-----|-------------|

| -      | 'in<br>nber | Pin name                  |          | Ire           |       | Pin fur                                                                            | ctions               |  |  |

|--------|-------------|---------------------------|----------|---------------|-------|------------------------------------------------------------------------------------|----------------------|--|--|

| LQFP64 | LQFP100     | (function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                | Additional functions |  |  |

| -      | 1           | PE2                       | I/O      | FT            | -     | TRACECK, TIM3_ETR,<br>TSC_G7_IO1, FMC_A23,<br>SAI1_MCLK_A, EVENTOUT                | -                    |  |  |

| -      | 2           | PE3                       | I/O      | FT            | -     | TRACED0, TIM3_CH1,<br>TSC_G7_IO2, FMC_A19,<br>SAI1_SD_B, EVENTOUT                  | -                    |  |  |

| -      | 3           | PE4                       | I/O      | FT            | -     | TRACED1, TIM3_CH2,<br>DFSDM_DATIN3,<br>TSC_G7_IO3, FMC_A20,<br>SAI1_FS_A, EVENTOUT | -                    |  |  |

|        | Pin<br>Number Pin name |                            | Pin name |               |       | Pin fun                                                                                                                                                   | ctions               |

|--------|------------------------|----------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| LQFP64 | LQFP100                | (function after<br>reset)  | Pin type | I/O structure | Notes | Alternate functions                                                                                                                                       | Additional functions |

| 55     | 89                     | PB3<br>(JTDO-<br>TRACESWO) | I/O      | FT_a          | (3)   | JTDO-TRACESWO,<br>TIM2_CH2, SPI1_SCK,<br>SPI3_SCK,<br>USART1_RTS_DE,<br>SAI1_SCK_B, EVENTOUT                                                              | COMP2_INM            |

| 56     | 90                     | PB4<br>(NJTRST)            | I/O      | FT_a          | (3)   | NJTRST, TIM3_CH1,<br>SPI1_MISO, SPI3_MISO,<br>USART1_CTS,<br>UART5_RTS_DE,<br>TSC_G2_IO1, SAI1_MCLK_B,<br>TIM17_BKIN, EVENTOUT                            | COMP2_INP            |

| 57     | 91                     | PB5                        | I/O      | FT_a          | -     | LPTIM1_IN1, TIM3_CH2,<br>I2C1_SMBA, SPI1_MOSI,<br>SPI3_MOSI, USART1_CK,<br>UART5_CTS, TSC_G2_IO2,<br>COMP2_OUT, SAI1_SD_B,<br>TIM16_BKIN, EVENTOUT        | -                    |

| 58     | 92                     | PB6                        | I/O      | FT_fa         | -     | LPTIM1_ETR, TIM4_CH1,<br>TIM8_BKIN2, I2C1_SCL,<br>DFSDM_DATIN5,<br>USART1_TX, TSC_G2_IO3,<br>TIM8_BKIN2_COMP2,<br>SAI1_FS_B, TIM16_CH1N,<br>EVENTOUT      | COMP2_INP            |

| 59     | 93                     | PB7                        | I/O      | FT_fa         | -     | LPTIM1_IN2, TIM4_CH2,<br>TIM8_BKIN, I2C1_SDA,<br>DFSDM_CKIN5,<br>USART1_RX, UART4_CTS,<br>TSC_G2_IO4, FMC_NL,<br>TIM8_BKIN_COMP1,<br>TIM17_CH1N, EVENTOUT | COMP2_INM, PVD_IN    |

| 60     | 94                     | BOOT0                      | I        | -             | -     | -                                                                                                                                                         | -                    |

| 61     | 95                     | PB8                        | I/O      | FT_f          | -     | TIM4_CH3, I2C1_SCL,<br>DFSDM_DATIN6, CAN1_RX,<br>SDMMC1_D4, SAI1_MCLK_A,<br>TIM16_CH1, EVENTOUT                                                           | -                    |

| 62     | 96                     | PB9                        | I/O      | FT_f          | -     | IR_OUT, TIM4_CH4,<br>I2C1_SDA, SPI2_NSS,<br>DFSDM_CKIN6, CAN1_TX,<br>SDMMC1_D5, SAI1_FS_A,<br>TIM17_CH1, EVENTOUT                                         | -                    |

| -      | 97                     | PE0                        | I/O      | FT            | -     | TIM4_ETR, FMC_NBL0,<br>TIM16_CH1, EVENTOUT                                                                                                                | -                    |

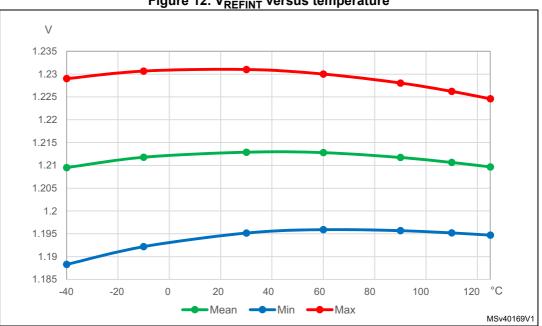

Figure 12. V<sub>REFINT</sub> versus temperature

|                       |                        | Conditions                           |                    |                   | ТҮР    |       |       |        |        | MAX <sup>(1)</sup> |       |       |        |        |      |    |

|-----------------------|------------------------|--------------------------------------|--------------------|-------------------|--------|-------|-------|--------|--------|--------------------|-------|-------|--------|--------|------|----|

| Symbol Paramet        | Parameter              | -                                    | Voltage<br>scaling | f <sub>HCLK</sub> | 25 °C  | 55 °C | 85 °C | 105 °C | 125 °C | 25 °C              | 55 °C | 85 °C | 105 °C | 125 °C | Unit |    |

|                       |                        |                                      |                    | 26 MHz            | 2.88   | 2.93  | 3.05  | 3.23   | 3.58   | 3.20               | 3.37  | 3.51  | 3.93   | 4.76   |      |    |

|                       |                        |                                      |                    | 16 MHz            | 1.83   | 1.87  | 1.98  | 2.16   | 2.49   | 2.01               | 2.16  | 2.30  | 2.72   | 3.34   |      |    |

|                       |                        |                                      |                    | 8 MHz             | 0.98   | 1.02  | 1.12  | 1.29   | 1.62   | 1.10               | 1.17  | 1.31  | 1.73   | 2.56   |      |    |

|                       |                        |                                      | Range 2            | 4 MHz             | 0.55   | 0.59  | 0.69  | 0.85   | 1.18   | 0.61               | 0.70  | 0.89  | 1.24   | 1.95   |      |    |

|                       |                        | in PLL ON above                      | ,                  | 2 MHz             | 0.34   | 0.37  | 0.47  | 0.64   | 0.96   | 0.37               | 0.46  | 0.64  | 0.98   | 1.71   |      |    |

|                       |                        |                                      |                    | 1 MHz             | 0.23   | 0.26  | 0.36  | 0.53   | 0.85   | 0.27               | 0.33  | 0.50  | 0.86   | 1.57   |      |    |

|                       | Supply                 |                                      |                    | 100 kHz           | 0.14   | 0.17  | 0.27  | 0.43   | 0.75   | 0.17               | 0.21  | 0.38  | 0.74   | 1.44   |      |    |

| I <sub>DD</sub> (Run) | current in<br>Run mode |                                      |                    |                   | 80 MHz | 10.2  | 10.3  | 10.5   | 10.7   | 11.1               | 11.22 | 11.8  | 12.1   | 12.5   | 13.3 | mA |

|                       |                        |                                      |                    | 72 MHz            | 9.24   | 9.31  | 9.47  | 9.69   | 10.1   | 10.16              | 10.7  | 11.0  | 11.4   | 12.2   | -    |    |

|                       |                        |                                      |                    | 64 MHz            | 8.25   | 8.32  | 8.46  | 8.68   | 9.09   | 9.08               | 9.6   | 9.9   | 10.3   | 11.1   |      |    |

|                       |                        |                                      | Range 1            | 48 MHz            | 6.28   | 6.35  | 6.5   | 6.72   | 7.11   | 6.91               | 7.3   | 7.6   | 8.0    | 8.8    |      |    |

|                       |                        |                                      |                    | 32 MHz            | 4.24   | 4.30  | 4.44  | 4.65   | 5.04   | 4.66               | 4.97  | 5.26  | 5.67   | 6.51   |      |    |

|                       |                        |                                      |                    | 24 MHz            | 3.21   | 3.27  | 3.4   | 3.61   | 3.98   | 3.53               | 3.76  | 4.05  | 4.46   | 5.30   |      |    |

|                       |                        |                                      |                    | 16 MHz            | 2.19   | 2.24  | 2.36  | 2.56   | 2.94   | 2.41               | 2.66  | 2.95  | 3.16   | 3.99   |      |    |

|                       | Supply                 |                                      |                    | 2 MHz             | 272    | 303   | 413   | 592    | 958    | 330                | 393   | 579   | 954    | 1704   |      |    |

| <sub>DD</sub> (LPRun) | Supply<br>current in   | f <sub>HCLK</sub> = f <sub>MSI</sub> |                    | 1 MHz             | 154    | 184   | 293   | 473    | 835    | 195                | 265   | 457   | 822    | 1572   |      |    |

| DD(LFRUII)            | Low-power              | all peripherals disab                | ole                | 400 kHz           | 78     | 108   | 217   | 396    | 758    | 110                | 180   | 380   | 755    | 1505   | μA   |    |

| run mode              |                        |                                      | 100 kHz            | 42                | 73     | 182   | 360   | 723    | 75     | 138                | 331   | 706   | 1456   |        |      |    |

Table 26. Current consumption in Run and Low-power run modes, code with data processing

1. Guaranteed by characterization results, unless otherwise specified.

90/193

DocID027692 Rev 2

STM32L475xx

**Electrical characteristics**

|      | Peripheral                        | Range 1 | Range 2 | Low-power run<br>and sleep | Unit   |

|------|-----------------------------------|---------|---------|----------------------------|--------|

|      | SRAM2                             | 1.6     | 1.4     | 1.6                        |        |

| AHB  | TSC                               | 1.8     | 1.4     | 1.6                        | µA/MHz |

|      | All AHB Peripherals               | 118.5   | 77.3    | 87.6                       |        |

|      | AHB to APB1 bridge <sup>(3)</sup> | 0.9     | 0.7     | 0.9                        |        |

|      | CAN1                              | 4.6     | 4.0     | 4.4                        |        |

|      | DAC1                              | 2.4     | 1.9     | 2.2                        |        |

|      | I2C1 independent clock domain     | 3.7     | 3.1     | 3.2                        |        |

|      | I2C1 APB clock domain             | 1.3     | 1.1     | 1.5                        |        |

|      | I2C2 independent clock domain     | 3.7     | 3.0     | 3.2                        |        |

|      | I2C2 APB clock domain             | 1.4     | 1.1     | 1.5                        |        |

|      | I2C3 independent clock domain     | 2.9     | 2.3     | 2.5                        |        |

|      | I2C3 APB clock domain             | 0.9     | 0.9     | 1.1                        |        |

|      | LPUART1 independent clock domain  | 2.1     | 1.6     | 2.0                        |        |

|      | LPUART1 APB clock domain          | 0.6     | 0.6     | 0.6                        |        |

|      | LPTIM1 independent clock domain   | 3.3     | 2.6     | 2.9                        | µA/MHz |

|      | LPTIM1 APB clock domain           | 0.9     | 0.8     | 1.0                        |        |

| APB1 | LPTIM2 independent clock domain   | 3.1     | 2.7     | 2.9                        |        |

|      | LPTIM2 APB clock domain           | 0.8     | 0.6     | 0.7                        |        |

|      | OPAMP                             | 0.4     | 0.4     | 0.3                        |        |

|      | PWR                               | 0.5     | 0.5     | 0.4                        |        |

|      | SPI2                              | 1.8     | 1.6     | 1.6                        |        |

|      | SPI3                              | 2.1     | 1.7     | 1.8                        |        |

|      | SWPMI1 independent clock domain   | 2.3     | 1.8     | 2.2                        |        |

|      | SWPMI1 APB clock domain           | 1.1     | 1.1     | 1.0                        |        |

|      | TIM2                              | 6.8     | 5.7     | 6.3                        |        |

|      | TIM3                              | 5.4     | 4.6     | 5.0                        |        |

|      | TIM4                              | 5.2     | 4.4     | 4.9                        |        |

|      | TIM5                              | 6.5     | 5.5     | 6.1                        |        |

|      | TIM6                              | 1.1     | 1.0     | 1.0                        |        |

|      | TIM7                              | 1.1     | 0.9     | 1.0                        |        |

Table 40. Peripheral current consumption (continued)

| Symbol                     | Parameter                                           |                   | Conditions                     | Min  | Тур     | Max   | Unit  |

|----------------------------|-----------------------------------------------------|-------------------|--------------------------------|------|---------|-------|-------|

|                            |                                                     |                   | Range 0                        | 99   | 100     | 101   |       |

|                            |                                                     |                   | Range 1                        | 198  | 200     | 202   |       |

|                            |                                                     |                   | Range 2                        | 396  | 400     | 404   | - kHz |

|                            |                                                     |                   | Range 3                        | 792  | 800     | 808   |       |

|                            |                                                     |                   | Range 4                        | 0.99 | 1       | 1.01  |       |

|                            |                                                     | MSI mode          | Range 5                        | 1.98 | 2       | 2.02  |       |

|                            |                                                     | INISI MODE        | Range 6                        | 3.96 | 4       | 4.04  |       |

|                            |                                                     |                   | Range 7                        | 7.92 | 8       | 8.08  | MHz   |

| f <sub>MSI</sub>           |                                                     |                   | Range 8                        | 15.8 | 16      | 16.16 |       |

|                            |                                                     |                   | Range 9                        | 23.8 | 24      | 24.4  | -     |

|                            | MSI frequency<br>after factory<br>calibration, done |                   | Range 10                       | 31.7 | 32      | 32.32 |       |

|                            |                                                     |                   | Range 11                       | 47.5 | 48      | 48.48 |       |

|                            | at $V_{DD}$ =3 V and $T_A$ =30 °C                   |                   | Range 0                        | -    | 98.304  | -     | - kHz |

|                            |                                                     |                   | Range 1                        | -    | 196.608 | -     |       |

|                            |                                                     |                   | Range 2                        | -    | 393.216 | -     |       |

|                            |                                                     |                   | Range 3                        | -    | 786.432 | -     |       |

|                            |                                                     |                   | Range 4                        | -    | 1.016   | -     |       |

|                            |                                                     | PLL mode<br>XTAL= | Range 5                        | -    | 1.999   | -     |       |

|                            |                                                     | 32.768 kHz        | Range 6                        | -    | 3.998   | -     | - MHz |

|                            |                                                     |                   | Range 7                        | -    | 7.995   | -     |       |

|                            |                                                     |                   | Range 8                        | -    | 15.991  | -     |       |

|                            |                                                     |                   | Range 9                        | -    | 23.986  | -     |       |

|                            |                                                     |                   | Range 10                       | -    | 32.014  | -     |       |

|                            |                                                     |                   | Range 11                       | -    | 48.005  | -     |       |

| (r (2)                     | MSI oscillator                                      |                   | T <sub>A</sub> = -0 to 85 °C   | -3.5 | -       | 3     |       |

| $\Delta_{TEMP}(MSI)^{(2)}$ | frequency drift over temperature                    | MSI mode          | T <sub>A</sub> = -40 to 125 °C | -8   | -       | 6     | %     |

### Table 49. MSI oscillator characteristics<sup>(1)</sup>

### **Electrical characteristics**

| Speed | Symbol        | Parameter                 | Conditions                                 | Min | Max | Unit      |  |

|-------|---------------|---------------------------|--------------------------------------------|-----|-----|-----------|--|

|       |               |                           | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 5   |           |  |

|       |               |                           | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 1   |           |  |

|       | Fmax          | Maximum frequency         | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 0.1 | MHz       |  |

|       | FIIIdX        | Maximum frequency         | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 10  |           |  |

|       |               |                           | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 1.5 |           |  |

| 00    |               |                           | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 0.1 |           |  |

| 00    |               |                           | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 25  |           |  |

|       |               |                           | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 52  |           |  |

|       | Tr/Tf<br>Fmax | Output rise and fall time | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 140 | ne        |  |

|       |               |                           | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 17  | ns        |  |

|       |               |                           | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 37  |           |  |

|       |               |                           | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 110 |           |  |

|       |               | Maximum frequency         | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 25  |           |  |

|       |               |                           | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 10  |           |  |

|       |               |                           | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 1   | - MHz     |  |

|       |               | Maximum nequency          | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 50  |           |  |

|       |               |                           | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 15  |           |  |

| 01    |               |                           | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 1   |           |  |

| 01    |               |                           | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 9   |           |  |

|       |               | - I - I                   | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 16  |           |  |

|       | Tr/Tf         |                           | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 40  |           |  |

|       | 11/11         | Output rise and fall time | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 4.5 | – ns<br>– |  |

|       |               |                           | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 9   |           |  |

|       |               |                           | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 21  |           |  |

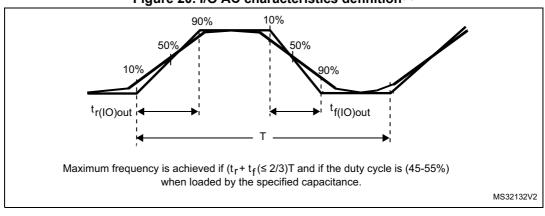

| Table 61 | . I/O AC | characteristics <sup>(1)(2)</sup> |

|----------|----------|-----------------------------------|

|----------|----------|-----------------------------------|

1. Refer to Table 61: I/O AC characteristics.

### 6.3.15 NRST pin characteristics

The NRST pin input driver uses the CMOS technology. It is connected to a permanent pull-up resistor,  $\mathsf{R}_{\mathsf{PU}}.$

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 22: General operating conditions*.

| Symbol                 | Parameter                                          | Conditions                        | Min                                 | Тур | Max                                 | Unit |

|------------------------|----------------------------------------------------|-----------------------------------|-------------------------------------|-----|-------------------------------------|------|

| V <sub>IL(NRST)</sub>  | NRST input low level voltage                       | -                                 | -                                   | -   | 0.3 <sub>x</sub> V <sub>DDIOx</sub> | v    |

| V <sub>IH(NRST)</sub>  | NRST input high level voltage                      | -                                 | 0.7 <sub>x</sub> V <sub>DDIOx</sub> | -   | -                                   | v    |

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage hysteresis            | -                                 | -                                   | 200 | -                                   | mV   |

| R <sub>PU</sub>        | Weak pull-up<br>equivalent resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                                  | 40  | 55                                  | kΩ   |

| V <sub>F(NRST)</sub>   | NRST input filtered<br>pulse                       | -                                 | -                                   | -   | 70                                  | ns   |

| V <sub>NF(NRST)</sub>  | NRST input not filtered pulse                      | 1.71 V ≤ V <sub>DD</sub> ≤ 3.6 V  | 350                                 | -   | -                                   | ns   |

Table 62. NRST pin characteristics<sup>(1)</sup>

1. Guaranteed by design.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

| Symbol                    | Parameter                                          | Conditions                                        | Min     | Тур                                                             | Мах     | Unit               |

|---------------------------|----------------------------------------------------|---------------------------------------------------|---------|-----------------------------------------------------------------|---------|--------------------|

|                           | Triagon conversion                                 | CKMODE = 00                                       | 2.5     | 3                                                               | 3.5     |                    |

| +                         | Trigger conversion<br>latency Injected channels    | CKMODE = 01                                       | -       | -                                                               | 3.0     | 1 /f               |

| t <sub>latrinj</sub>      | aborting a regular conversion                      | CKMODE = 10                                       | -       | -                                                               | 3.25    | 1/f <sub>ADC</sub> |

|                           |                                                    | CKMODE = 11                                       | -       | -                                                               | 3.125   |                    |

| +                         | Sampling time                                      | f <sub>ADC</sub> = 80 MHz                         | 0.03125 | -                                                               | 8.00625 | μs                 |

| t <sub>s</sub>            |                                                    | -                                                 | 2.5     | -                                                               | 640.5   | 1/f <sub>ADC</sub> |

| t <sub>ADCVREG_STUP</sub> | ADC voltage regulator start-up time                | -                                                 | -       | -                                                               | 20      | μs                 |

|                           | Total conversion time<br>(including sampling time) | f <sub>ADC</sub> = 80 MHz<br>Resolution = 12 bits | 0.1875  | -                                                               | 8.1625  | μs                 |

| t <sub>CONV</sub>         |                                                    | Resolution = 12 bits                              | success | ts + 12.5 cycles for<br>successive approximation<br>= 15 to 653 |         |                    |

|                           |                                                    | fs = 5 Msps                                       | -       | 730                                                             | 830     |                    |

| I <sub>DDA</sub> (ADC)    | ADC consumption from the $V_{DDA}$ supply          | fs = 1 Msps                                       | -       | 160                                                             | 220     | μA                 |

|                           |                                                    | fs = 10 ksps                                      | -       | 16                                                              | 50      |                    |

|                           | ADC consumption from                               | fs = 5 Msps                                       | -       | 130                                                             | 160     |                    |

| I <sub>DDV_S</sub> (ADC)  | the V <sub>REF+</sub> single ended                 | fs = 1 Msps                                       | -       | 30                                                              | 40      | μA                 |

|                           | mode                                               | fs = 10 ksps                                      | -       | 0.6                                                             | 2       |                    |

|                           | ADC consumption from                               | fs = 5 Msps                                       | -       | 260                                                             | 310     |                    |

| I <sub>DDV_D</sub> (ADC)  | the V <sub>REF+</sub> differential                 | fs = 1 Msps                                       | -       | 60                                                              | 70      | μA                 |

|                           | mode                                               | fs = 10 ksps                                      | -       | 1.3                                                             | 3       |                    |

Table 64. ADC characteristics<sup>(1) (2)</sup> (continued)

1. Guaranteed by design

2. The I/O analog switch voltage booster is enable when V<sub>DDA</sub> < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when V<sub>DDA</sub> < 2.4V). It is disable when V<sub>DDA</sub>  $\geq$  2.4 V.

V<sub>REF+</sub> can be internally connected to V<sub>DDA</sub> and V<sub>REF-</sub> can be internally connected to V<sub>SSA</sub>, depending on the package. Refer to Section 4: Pinouts and pin description for further details.

|             | Table 00. ADC accuracy - minited test conditions 14 A A (continued) |                                         |                          |                          |     |     |     |      |

|-------------|---------------------------------------------------------------------|-----------------------------------------|--------------------------|--------------------------|-----|-----|-----|------|

| Sym-<br>bol | Parameter                                                           | C                                       | Conditions <sup>(4</sup> | )                        | Min | Тур | Max | Unit |

|             |                                                                     | ADC clock frequency ≤                   | Single                   | Fast channel (max speed) | -   | -74 | -73 |      |

| THD         | Total<br>THD harmonic                                               | 80 MHz,<br>Sampling rate ≤ 5.33 Msps, . | ended                    | Slow channel (max speed) | -   | -74 | -73 | dB   |

| distortion  | $V_{} = V_{} = 3 V_{}$                                              | Differential                            | Fast channel (max speed) | -                        | -79 | -76 | uв  |      |

|             | TA = 25 °C                                                          | Differential                            | Slow channel (max speed) | -                        | -79 | -76 |     |      |

| Table 66. ADC accuracy - limited test conditions 1 <sup>(1)(2)(3)</sup> (continu |

|----------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------|

1. Guaranteed by design.

2. ADC DC accuracy values are measured after internal calibration.

- 3. ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

- 4. The I/O analog switch voltage booster is enable when V<sub>DDA</sub> < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when V<sub>DDA</sub> < 2.4 V). It is disable when V<sub>DDA</sub>  $\geq$  2.4 V. No oversampling.

### **USB** characteristics

The STM32L475xx USB interface is fully compliant with the USB specification version 2.0 and is USB-IF certified (for Full-speed device operation).

| Symbol                          | Parameter                                      | Conditions           | Min                | Тур  | Max  | Unit |

|---------------------------------|------------------------------------------------|----------------------|--------------------|------|------|------|

| V <sub>DDUSB</sub>              | USB transceiver operating voltage              |                      | 3.0 <sup>(1)</sup> | -    | 3.6  | V    |

| R <sub>PUI</sub>                | Embedded USB_DP pull-up val                    | 900                  | 1250               | 1600 |      |      |

| R <sub>PUR</sub>                | Embedded USB_DP pull-up value during reception |                      | 1400               | 2300 | 3200 | Ω    |

| Z <sub>DRV</sub> <sup>(2)</sup> | Output driver impedance <sup>(3)</sup>         | Driving high and low | 28                 | 36   | 44   | Ω    |

| Table 89 | . USB | electrical | characteristics |

|----------|-------|------------|-----------------|

|----------|-------|------------|-----------------|

1. The STM32L475xx USB functionality is ensured down to 2.7 V but not the full USB electrical characteristics which are degraded in the 2.7-to-3.0 V voltage range.

2. Guaranteed by design.

3. No external termination series resistors are required on USB\_DP (D+) and USB\_DM (D-); the matching impedance is already included in the embedded driver.

### CAN (controller area network) interface

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

# Figure 39. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

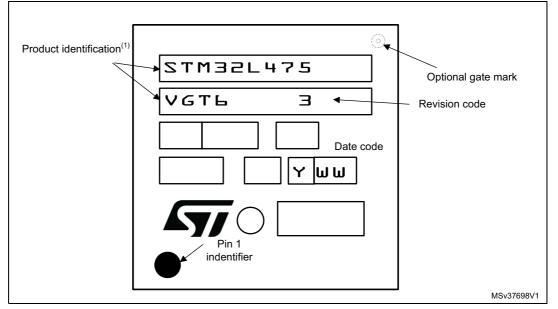

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 40. LQFP100 marking (package top view)

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID027692 Rev 2