Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 010110                   |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Active                                                               |

| Core Processor             | Coldfire V1                                                          |

| Core Size                  | 32-Bit Single-Core                                                   |

| Speed                      | 50MHz                                                                |

| Connectivity               | I <sup>2</sup> C, SCI, SPI, USB OTG                                  |

| Peripherals                | LVD, PWM, WDT                                                        |

| Number of I/O              | 33                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 16K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                          |

| Data Converters            | A/D 8x12b                                                            |

| Oscillator Type            | External                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 44-LQFP                                                              |

| Supplier Device Package    | 44-LQFP (10x10)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcf51jm32vld |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.1 Device Comparison

The MCF51JM128 series consists of the devices compared in Table 1.

### Table 1. MCF51JM128 Series Device Comparison

| Facture                                             | М      | CF51JM1 | 28     | MCF51JM64 |                  |        | MCF51JM32 |        |        |

|-----------------------------------------------------|--------|---------|--------|-----------|------------------|--------|-----------|--------|--------|

| Feature                                             | 80-pin | 64-pin  | 44-pin | 80-pin    | 64-pin           | 44-pin | 80-pin    | 64-pin | 44-pin |

| Flash memory size (KB)                              |        | 128     |        |           | 64               |        |           | 32     |        |

| RAM size (KB)                                       |        | 16      |        |           | 16               |        |           | 16     |        |

| V1 ColdFire core with BDM (background debug module) |        |         |        |           | Yes              |        |           |        |        |

| ACMP (analog comparator)                            |        |         |        |           | Yes              |        |           |        |        |

| ADC channels (12-bit)                               | 1      | 2       | 8      | 1         | 2                | 8      | 1         | 2      | 8      |

| CAN (controller area network)                       | Yes    | Yes     | No     | Yes       | Yes              | No     | Yes       | Yes    | No     |

| RNGA + CAU                                          |        | 1       |        | 1         | Yes <sup>1</sup> | 1      | 1         |        |        |

| CMT (carrier modulator timer)                       |        |         |        |           | Yes              |        |           |        |        |

| COP (computer operating properly)                   |        |         |        |           | Yes              |        |           |        |        |

| IIC1 (inter-integrated circuit)                     |        |         |        |           | Yes              |        |           |        |        |

| IIC2                                                | Yes    | N       | 0      | Yes       | Yes No           |        | Yes No    |        | lo     |

| IRQ (interrupt request input)                       | Yes    |         |        |           |                  |        |           |        |        |

| KBI (keyboard interrupts)                           | 8      | 8       | 6      | 8         | 8                | 6      | 8         | 8      | 6      |

| LVD (low-voltage detector)                          | Yes    |         |        |           |                  |        |           |        |        |

| MCG (multipurpose clock generator)                  | Yes    |         |        |           |                  |        |           |        |        |

| Port I/O <sup>2</sup>                               | 66     | 51      | 33     | 66        | 51               | 33     | 66        | 51     | 33     |

| RGPIO (rapid general-purpose I/O)                   | 16     | 6       | 0      | 16        | 6                | 0      | 16        | 6      | 0      |

| RTC (real-time counter)                             |        | 1       |        | 1         | Yes              | 1      |           |        |        |

| SCI1 (serial communications interface)              |        |         |        |           | Yes              |        |           |        |        |

| SCI2                                                |        |         |        |           | Yes              |        |           |        |        |

| SPI1 (serial peripheral interface)                  |        |         |        |           | Yes              |        |           |        |        |

| SPI2                                                |        |         |        |           | Yes              |        |           |        |        |

| TPM1 (timer/pulse-width modulator) channels         | 6      | 6       | 4      | 6         | 6                | 4      | 6         | 6      | 4      |

| TPM2 channels                                       |        |         |        |           | 2                |        |           |        |        |

| USBOTG (USB On-The-Go dual-role controller)         | Yes    |         |        |           |                  |        |           |        |        |

| XOSC (crystal oscillator)                           |        |         |        |           | Yes              |        |           |        |        |

<sup>1</sup> Only existed on special part number

<sup>2</sup> Up to 16 pins on Ports A, H, and J are shared with the ColdFire Rapid GPIO module.

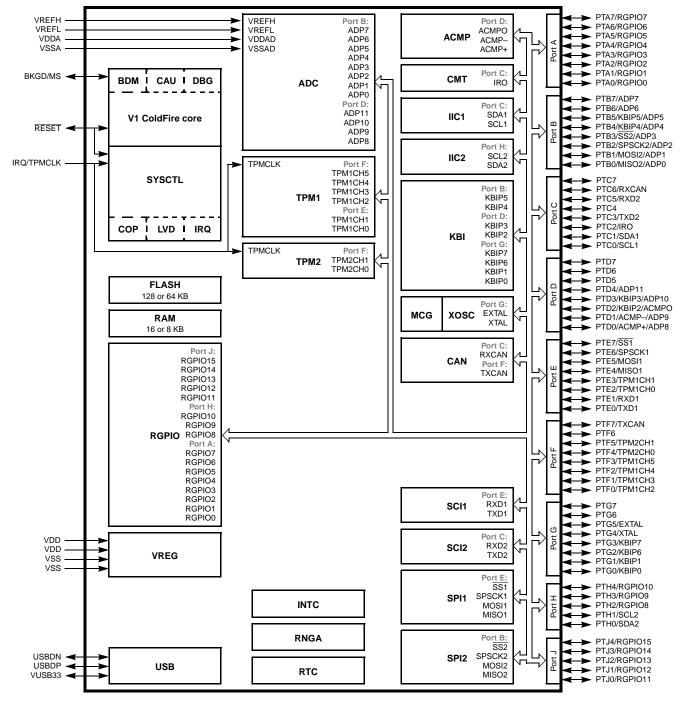

### 1.2 Block Diagram

Figure 1 shows the connections between the MCF51JM128 series pins and modules.

### 1.3.1 Feature List

- 32-bit Version 1 ColdFire Central Processor Unit (CPU)

- Up to 50.33 MHz at 2.7 V 5.5 V

- Performance (Dhrystone 2.1):

- 0.94 Dhrystone 2.1 MIPS per MHz when running from internal RAM

- 0.76 Dhrystone 2.1 MIPS per MHz when running from flash

- Implements Instruction Set Revision C (ISA\_C)

- Supports up to 30 peripheral interrupt requests and seven software interrupts

- On-chip memory

- Up to 128 KB Flash memory with read/program/erase over full operating voltage and temperature range

- Up to 16 KB static random access memory (RAM)

- Security circuitry to prevent unauthorized access to RAM and flash contents

- Power-saving modes

- Two low-power stop plus wait modes

- Peripheral clock enable register can disable clocks to unused modules, thereby reducing currents; this behavior allows clocks to remain enabled to specific perhipherals in Stop3 mode

- Very lower power real-time counter for use in run, wait, and stop modes with internal and external clock sources

- Four Clock Source Options

- Oscillator (XOSC) Loop-control Pierce oscillator; crystal or ceramic resonator range of 31.25 kHz to 38.4 kHz or 1 MHz to 16 MHz

- FLL/PLL controlled by internal or external reference

- Trimmable internal reference allows 0.2% resolution and 2% deviation

- System protection features

- Watchdog computer operating properly (COP) reset with option to run from dedicated 1 kHz internal clock source or bus clock

- Low-voltage detection with reset or interrupt; selectable trip points

- Illegal opcode and illegal address detection with programmable reset or exception response

- Flash block protection

- Debug support

- Single-wire Background debug interface

- 4 Program Counters plus two address (optional data) breakpoint registers with programmable 1- or 2-level trigger response

- 64-entry processor status and debug data trace buffer with programmable start/stop conditions

- Universal Serial Bus (USB) On-The-Go dual-role controller

- Full-speed USB device controller

- Fully compliant with USB specification 1.1 and 2.0

- 16 bidirectional endpoints, with double buffering to provide the maximum throughput

- Supports control, bulk, interrupt, and isochronous endpoints

- Supports bus-powered capability with low-power consumption

- Full-speed / low-speed host controller

- Host mode allows control, bulk, interrupt, and isochronous transfers

- OTG protocol logic

- On-chip USB transceiver

- On-chip 3.3 V USB regulator and pull-up resistors save system cost

- Controller area network (MSCAN)

- Implementation of the CAN protocol Version 2.0A/B

- Five receive buffers with FIFO storage scheme

- Three transmit buffers with internal prioritization using a "local priority" concept

- Flexible maskable identifier filter programmable as 2x32-bit, 4x16-bit, or 8x8-bit

- Programmable wakeup functionality with integrated low-pass filter

- Programmable loopback mode supports self-test operation

- Programmable bus-off recovery functionality

- Internal timer for time-stamping of received and transmitted messages

- Cryptographic acceleration unit (CAU)

- Co-processor support of DES, 3DES, AES, MD5, and SHA-1

- Random number generator accelerator (RNGA)

- 32-bit random number generator that complies with FIPS-140

- Analog-to-digital converter (ADC)

- 12-channel, 12-bit resolution

- Output formatted in 12-, 10-, or 8-bit right-justified format

- Single or continuous conversion, and selectable asynchronous hardware conversion trigger

- Operation in Stop3 mode

- Automatic compare function

- Internal temperature sensor

- Analog comparators (ACMP)

- Selectable interrupt on rising edge, falling edge, or either rising or falling edges of comparator output

- Option to compare to fixed internal bandgap reference voltage

- Option to route output to TPM module

- Operation in Stop3 mode

- Inter-integrated circuit (IIC)

- Up to 100 kbps with maximum bus loading

- Multi-master operation

- Programmable slave address

- Supports broadcast mode and 10-bit address extension

- Serial communications interfaces (SCI)

- Two SCIs with full-duplex, non-return-to-zero (NRZ) format

- LIN master extended break generation

- LIN slave extended break detection

- Programmable 8-bit or 9-bit character length

- Wake up on active edge

- Serial peripheral interfaces (SPI)

- Two serial peripheral interfaces with full-duplex or single-wire bidirectional

- Double-buffered transmit and receive

- Programmable transmit bit rate, phase, polarity, and Slave Select output

- MSB-first or LSB-first shifting

- Timer/pulse width modulator (TPM)

- 16-bit free-running or modulo up/down count operation

- Up to eight channels, where each channel can be an input capture, output compare, or edge-aligned PWM

- One interrupt per channel plus terminal count interrupt

- RTC

- 8-bit modulus counter with binary- or decimal-based prescaler

- External clock source for precise time base, time-of-day, calendar or task scheduling functions

- Free running on-chip low power oscillator (1 kHz) for cyclic wake-up without external components

- Carrier modulator timer (CMT)

- carrier generator, modulator, and transmitter drive the infrared out (IRO) pin

- operation in independent high/low time control, baseband, FSK, and direct IRO control modes

- Input/Output

- 66 GPIOs

- Eight keyboard interrupt pins with selectable polarity

- Hysteresis and configurable pull-up device on all input pins; configurable slew rate and drive strength on all output pins

- 16 bits of Rapid GPIO connected to the processor's local 32-bit platform bus with set, clear, and faster toggle functionality

### 1.4 Part Numbers

### Table 3. Orderable Part Number Summary

| Freescale Part<br>Number | Description                                                      | Flash / SRAM<br>(KB) | Package | Temperature    |

|--------------------------|------------------------------------------------------------------|----------------------|---------|----------------|

| MCF51JM128EVLK           | MCF51JM128 ColdFire Microcontroller<br>with CAU and RNGA Enabled | 128 / 16             | 80 LQFP | –40 to +105 °C |

| MCF51JM128VLK            | MCF51JM128 ColdFire Microcontroller                              | 128 / 16             | 80 LQFP | –40 to +105 °C |

| MCF51JM128EVLH           | MCF51JM128 ColdFire Microcontroller<br>with CAU and RNGA Enabled | 128 / 16             | 64 LQFP | –40 to +105 °C |

| MCF51JM128VLH            | MCF51JM128 ColdFire Microcontroller                              | 128 / 16             | 64 LQFP | –40 to +105 °C |

| MCF51JM128EVQH           | MCF51JM128 ColdFire Microcontroller<br>with CAU and RNGA Enabled | 128 / 16             | 64 QFP  | –40 to +105 °C |

| MCF51JM128VQH            | MCF51JM128 ColdFire Microcontroller                              | 128 / 16             | 64 QFP  | –40 to +105 °C |

| MCF51JM128EVLD           | MCF51JM128 ColdFire Microcontroller<br>with CAU and RNGA Enabled | 128 / 16             | 44 LQFP | –40 to +105 °C |

| MCF51JM128VLD            | MCF51JM128 ColdFire Microcontroller                              | 128 / 16             | 44 LQFP | –40 to +105 °C |

| MCF51JM64EVLK            | MCF51JM64 ColdFire Microcontroller<br>with CAU and RNGA Enabled  | 64 / 16              | 80 LQFP | –40 to +105 °C |

| MCF51JM64VLK             | MCF51JM64 ColdFire Microcontroller                               | 64 / 16              | 80 LQFP | –40 to +105 °C |

| MCF51JM64EVLH            | MCF51JM64 ColdFire Microcontroller<br>with CAU and RNGA Enabled  | 64 / 16              | 64 LQFP | –40 to +105 °C |

| MCF51JM64VLH             | MCF51JM64 ColdFire Microcontroller                               | 64 / 16              | 64 LQFP | –40 to +105 °C |

| MCF51JM64EVQH            | MCF51JM64 ColdFire Microcontroller<br>with CAU and RNGA Enabled  | 64 / 16              | 64 QFP  | −40 to +105 °C |

| MCF51JM64VQH             | MCF51JM64 ColdFire Microcontroller                               | 64 / 16              | 64 QFP  | –40 to +105 °C |

| Pin | Num | ber | < Lov    | vest Priority> | Highest        |

|-----|-----|-----|----------|----------------|----------------|

| 80  | 64  | 44  | Port Pin | Alt 1          | Alt 2          |

| 16  | 16  | 11  | PTE3     | TPM1CH1        | —              |

| 17  |     | —   | PTC7     | _              | —              |

| 18  | —   | _   | PTH0     | SDA2           | —              |

| 19  |     |     | PTH1     | SCL2           | —              |

| 20  |     | _   | PTH2     | RGPIO8         | —              |

| 21  | _   | _   | PTH3     | RGPIO9         | —              |

| 22  |     |     | PTH4     | RGPIO10        | —              |

| 23  | 17  | 12  | PTE4     | MISO1          | —              |

| 24  | 18  | 13  | PTE5     | MOSI1          | —              |

| 25  | 19  | 14  | PTE6     | SPSCK1         | —              |

| 26  | 20  | 15  | PTE7     | SS1            | —              |

| 27  | 21  | 16  | _        | _              | VDD            |

| 28  | 22  | 17  | _        | _              | VSS            |

| 29  | 23  | 18  | _        | _              | USBDN          |

| 30  | 24  | 19  | _        | _              | USBDP          |

| 31  | 25  | 20  | _        | _              | VUSB33         |

| 32  | 26  | 21  | PTG0     | KBIP0          | USB_ALT_CLK    |

| 33  | 27  | 22  | PTG1     | KBIP1          | —              |

| 34  | 28  |     | PTA0     | RGPIO0         | USB_SESSVLD    |

| 35  | 29  |     | PTA1     | RGPIO1         | USB_SESSEND    |

| 36  | 30  | _   | PTA2     | RGPIO2         | USB_VBUSVLD    |

| 37  | 31  | _   | PTA3     | RGPIO3         | USB_PULLUP(D+) |

| 38  | 32  | _   | PTA4     | RGPIO4         | USB_DM_DOWN    |

| 39  | 33  | _   | PTA5     | RGPIO5         | USB_DP_DOWN    |

| 40  |     | _   | PTA6     | RGPIO6         | USB_ID         |

| 41  | —   | —   | PTA7     | RGPI07         | —              |

| 42  | 34  | 23  | PTB0     | MISO2          | ADP0           |

| 43  | 35  | 24  | PTB1     | MOSI2          | ADP1           |

| 44  | 36  | 25  | PTB2     | SPSCK2         | ADP2           |

| 45  | 37  | 26  | PTB3     | SS2            | ADP3           |

| 46  | 38  | 27  | PTB4     | KBIP4          | ADP4           |

| 47  | 39  | 28  | PTB5     | KBIP5          | ADP5           |

| 48  | 40  | —   | PTB6     | ADP6           |                |

### Table 4. Pin Assignments by Package and Pin Sharing Priority (continued)

| Pin | Num | ber | < Lov    | west <b>Priority</b> > H | lighest |

|-----|-----|-----|----------|--------------------------|---------|

| 80  | 64  | 44  | Port Pin | Alt 1                    | Alt 2   |

| 49  | 41  |     | PTB7     | ADP7                     |         |

| 50  | 42  | 29  | PTD0     | ADP8                     | ACMP+   |

| 51  | 43  | 30  | PTD1     | ADP9                     | ACMP-   |

| 52  | 44  | 31  | _        | —                        | VDDA    |

| 53  | 45  |     | _        | —                        | VREFH   |

| 54  | 46  | 32  | _        | —                        | VREFL   |

| 55  | 47  |     | _        | —                        | VSSA    |

| 56  | 48  | 33  | PTD2     | KBIP2                    | ACMPO   |

| 57  | —   | —   | PTJ0     | RGPIO11                  | —       |

| 58  | —   | —   | PTJ1     | RGPIO12                  | —       |

| 59  | —   | —   | PTJ2     | RGPIO13                  | —       |

| 60  | —   | —   | PTJ3     | RGPIO14                  | —       |

| 61  | —   | —   | PTJ4     | RGPIO15                  | —       |

| 62  | 49  | —   | PTD3     | KBIP3                    | ADP10   |

| 63  | 50  | —   | PTD4     | ADP11                    | _       |

| 64  | 51  | —   | PTD5     | _                        | _       |

| 65  | 52  | —   | PTD6     |                          | _       |

| 66  | 53  | —   | PTD7     | _                        | _       |

| 67  | 54  | 34  | PTG2     | KBIP6                    |         |

| 68  | 55  | 35  | PTG3     | KBIP7                    | —       |

| 69  | 56  | 36  | _        | BKGD                     | MS      |

| 70  | 57  | 37  | PTG4     | XTAL                     |         |

| 71  | 58  | 38  | PTG5     | EXTAL                    |         |

| 72  | 59  | 39  |          | —                        | VSS     |

| 73  | —   | —   |          | —                        | VDD     |

| 74  | —   | —   | PTG6     | —                        | —       |

| 75  | —   |     | PTG7     | —                        | —       |

| 76  | 60  | 40  | PTC0     | SCL1                     | —       |

| 77  | 61  | 41  | PTC1     | SDA1                     | —       |

| 78  | 62  | 42  | PTC2     | IRO                      | —       |

| 79  | 63  | 43  | PTC3     | TXD2                     | —       |

| 80  | 64  | 44  | PTC5     | RXD2                     | —       |

### Table 4. Pin Assignments by Package and Pin Sharing Priority (continued)

- <sup>3</sup> 1s Single Layer Board, one signal layer

- <sup>4</sup> 2s2p Four Layer Board, 2 signal and 2 power layers

The average chip-junction temperature (T<sub>J</sub>) in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \times \theta_{JA})$$

Eqn. 1

where:

$T_A$  = Ambient temperature,  $^{\circ}C\theta_{JA}$  = Package thermal resistance, junction-to-ambient,  $^{\circ}C/WP_D = P_{int} + P_{I/O}P_{int} = I_{DD} \times V_{DD}$ , Watts — chip internal power $P_{I/O}$  = Power dissipation on input and output pins — user determined

For most applications,  $P_{I/O} \ll P_{int}$  and can be neglected. An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:

$$P_{D} = K \div (T_{J} + 273^{\circ}C)$$

Eqn. 2

Solving equations 1 and 2 for K gives:

$$K = P_D \times (T_A + 273^{\circ}C) + \theta_{JA} \times (P_D)^2$$

Eqn. 3

where K is a constant pertaining to the particular part. K can be determined from equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving equations 1 and 2 iteratively for any value of  $T_A$ .

### 2.4 Electrostatic Discharge (ESD) Protection Characteristics

Although damage from static discharge is much less common on these devices than on early CMOS circuits, normal handling precautions should be used to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing is in conformity with CDF-AEC-Q00 Stress Test Qualification for Automotive Grade Integrated Circuits. (http://www.aecouncil.com/) This device was qualified to AEC-Q100 Rev E.

A device is considered to have failed if, after exposure to ESD pulses, the device no longer meets the device specification requirements. Complete DC parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

| Model      | Description                 | Symbol | Value | Unit |

|------------|-----------------------------|--------|-------|------|

|            | Series Resistance           | R1     | 1500  | Ω    |

| Human Body | Storage Capacitance         | С      | 100   | pF   |

|            | Number of Pulse per pin     | _      | 3     |      |

| Latch-up   | Minimum input voltage limit |        | -2.5  | V    |

|            | Maximum input voltage limit |        | 7.5   | V    |

Table 8. ESD and Latch-up Test Conditions

- <sup>1</sup> Typical values are based on characterization data at 25°C unless otherwise stated.

- <sup>2</sup> Operating voltage with USB enabled can be found in Section 2.14, "USB Electricals."

- <sup>3</sup> Measured with  $V_{In} = V_{DD}$  or  $V_{SS}$ .

- <sup>4</sup> Measured with  $V_{In} = V_{SS}$ .

- <sup>5</sup> Measured with  $V_{In} = V_{DD}$ .

- <sup>6</sup> This is the voltage below which the contents of RAM are not guaranteed to be maintained.

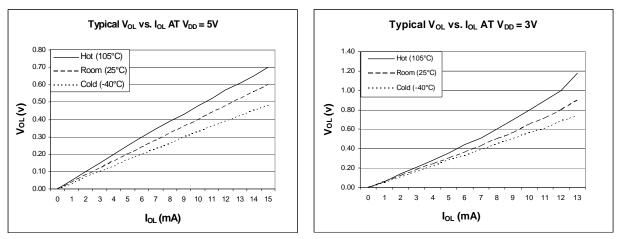

Figure 5. Typical Low-side Drive (sink) characteristics – High Drive (PTxDSn = 1)

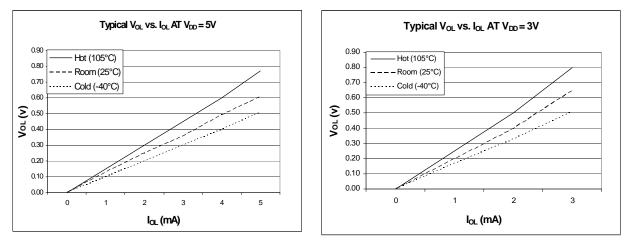

Figure 6. Typical Low-side Drive (sink) characteristics – Low Drive (PTxDSn = 0)

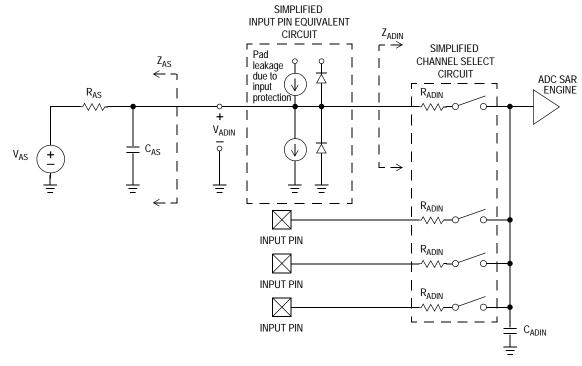

Figure 9. ADC Input Impedance Equivalency Diagram

| Characteristic                                  | Conditions              | С | Symb               | Min  | Typ <sup>1</sup> | Max | Unit | Comment              |

|-------------------------------------------------|-------------------------|---|--------------------|------|------------------|-----|------|----------------------|

| Supply Current<br>ADLPC=1<br>ADLSMP=1<br>ADCO=1 |                         | Т | I <sub>DDAD</sub>  | _    | 133              | _   | μΑ   |                      |

| Supply Current<br>ADLPC=1<br>ADLSMP=0<br>ADCO=1 |                         | T | I <sub>DDAD</sub>  | _    | 218              | _   | μΑ   |                      |

| Supply Current<br>ADLPC=0<br>ADLSMP=1<br>ADCO=1 |                         | Т | I <sub>DDAD</sub>  | —    | 327              | —   | μA   |                      |

| Supply Current<br>ADLPC=0<br>ADLSMP=0<br>ADCO=1 |                         | Р | I <sub>DDAD</sub>  |      | 0.582            | 1   | mA   |                      |

| Supply Current                                  | Stop, Reset, Module Off |   | I <sub>DDAD</sub>  |      | 0.011            | 1   | μΑ   |                      |

| ADC                                             | High Speed (ADLPC=0)    | Т | f <sub>ADACK</sub> | 2    | 3.3              | 5   | MHz  | t <sub>ADACK</sub> = |

| Asynchronous<br>Clock Source                    | Low Power (ADLPC=1)     |   |                    | 1.25 | 2                | 3.3 | 1    | 1/f <sub>ADACK</sub> |

| Table 14. 5 Volt 12-bit ADC Characteristics | (V <sub>REFH</sub> = V <sub>DDA</sub> | , V <sub>REFL</sub> = V <sub>SSA</sub> ) |

|---------------------------------------------|---------------------------------------|------------------------------------------|

|---------------------------------------------|---------------------------------------|------------------------------------------|

### 2.10 MCG Specifications

Table 16. MCG Frequency Specifications (Temperature Range = -40 to 125°C Ambient)

| Num | С | Rati                                                       | Symbol                   | Min                           | Typical <sup>1</sup>     | Max                                                            | Unit                                            |                   |

|-----|---|------------------------------------------------------------|--------------------------|-------------------------------|--------------------------|----------------------------------------------------------------|-------------------------------------------------|-------------------|

| 1   | Ρ | Internal reference frequence<br>= 5 V and temperature = 25 | f <sub>int_ft</sub>      | _                             | 32.768                   | —                                                              | kHz                                             |                   |

| 2   | Ρ | Average internal reference                                 | frequency – untrimmed    | f <sub>int_ut</sub>           | 31.25                    |                                                                | 39.0625                                         | kHz               |

| 3   | Т | Internal reference startup ti                              | me                       | t <sub>irefst</sub>           | —                        | 60                                                             | 100                                             | μs                |

|     | Ρ | DCO output frequency                                       | Low range (DRS=00)       |                               | 16                       | _                                                              | 20                                              |                   |

| 4   | Ρ | range - untrimmed <sup>2</sup>                             | Mid range (DRS=01)       | f <sub>dco_ut</sub>           | 32                       | _                                                              | 40                                              | MHz               |

|     | Ρ |                                                            | High range (DRS=10)      |                               | 48                       |                                                                | 60                                              |                   |

|     | Ρ | DCO output frequency <sup>2</sup>                          | Low range (DRS=00)       |                               | —                        | 19.92                                                          | —                                               |                   |

| 5   | Ρ | Reference =32768Hz                                         | Mid range (DRS=01)       | f <sub>dco_DMX32</sub>        | —                        | 39.85                                                          | —                                               | MHz               |

|     | Ρ | and DMX32 = 1                                              | High range (DRS=10)      |                               | —                        | 59.77                                                          | —                                               |                   |

| 6   | D | Resolution of trimmed DCC voltage and temperature (u       | ,                        | $\Delta f_{dco\_res\_t}$      | —                        | ±0.1                                                           | ±0.2                                            | %f <sub>dco</sub> |

| 7   | D | Resolution of trimmed DCC voltage and temperature (n       |                          | $\Delta f_{dco\_res\_t}$      | _                        | ±0.2                                                           | ±0.4                                            | %f <sub>dco</sub> |

| 8   | D | Total deviation of trimmed D voltage and temperature       | CO output frequency over | $\Delta f_{dco_t}$            | —                        | 0.5<br>-1.0                                                    | ±2                                              | %f <sub>dco</sub> |

| 9   | D | Total deviation of trimmed D fixed voltage and temperatu   |                          | $\Delta f_{dco_t}$            | —                        | ±0.5                                                           | ±1                                              | %f <sub>dco</sub> |

| 10  | D | FLL acquisition time <sup>3</sup>                          |                          | t <sub>fll_acquire</sub>      | —                        | _                                                              | 1                                               | ms                |

| 11  | D | PLL acquisition time <sup>4</sup>                          |                          | t <sub>pll_acquire</sub>      | —                        | _                                                              | 1                                               | ms                |

| 12  | D | Long term Jitter of DCO ou<br>2ms interval) <sup>5</sup>   | put clock (averaged over | C <sub>Jitter</sub>           | _                        | 0.02                                                           | 0.2                                             | %f <sub>dco</sub> |

| 13  | D | VCO operating frequency                                    |                          | f <sub>vco</sub>              | 7.0                      | _                                                              | 55.0                                            | MHz               |

| 14  | D | Jitter of PLL output clock m                               |                          | f <sub>pll_jitter_625ns</sub> | —                        | 0.566 <sup>5</sup>                                             | —                                               | %f <sub>pll</sub> |

| 15  | D | Lock entry frequency tolera                                |                          | D <sub>lock</sub>             | ±1.49                    | _                                                              | ±2.98                                           | %                 |

| 16  | D | Lock exit frequency tolerand                               | ce <sup>8</sup>          | D <sub>unl</sub>              | ±4.47                    | _                                                              | ±5.97                                           | %                 |

| 17  | D | Lock time — FLL                                            |                          | t <sub>fll_lock</sub>         | _                        | _                                                              | t <sub>fll_acquire+</sub><br>1075(1/fint_t<br>) | S                 |

| 18  | D | Lock time — PLL                                            | t <sub>pll_lock</sub>    | _                             | _                        | t <sub>pll_acquire+</sub><br>1075(1/ <sup>f</sup> pll_r<br>ef) | S                                               |                   |

| 19  | D | Loss of external clock minir<br>= 0                        | num frequency – RANGE    | f <sub>loc_low</sub>          | (3/5) x f <sub>int</sub> | _                                                              | —                                               | kHz               |

<sup>1</sup> Data in Typical column was characterized at 5.0 V, 25C or is typical recommended value

<sup>2</sup> The resulting bus clock frequency should not exceed the maximum specified bus clock frequency of the device.

<sup>3</sup> This specification applies to any time the FLL reference source or reference divider is changed, trim value changed or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

<sup>4</sup> This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

- <sup>5</sup> Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>BUS</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the FLL circuitry via V<sub>DD</sub> and V<sub>SS</sub> and variation in crystal oscillator frequency increase the C<sub>Jitter</sub> percentage for a given interval.

- <sup>6</sup> 625 ns represents 5 time quanta for CAN applications, under worst case conditions of 8 MHz CAN bus clock, 1 Mbps CAN bus speed, and 8 time quanta per bit for bit time settings. 5 time quanta is the minimum time between a synchronization edge and the sample point of a bit using 8 time quanta per bit.

- <sup>7</sup> Below D<sub>lock</sub> minimum, the MCG is guaranteed to enter lock. Above D<sub>lock</sub> maximum, the MCG will not enter lock. But if the MCG is already in lock, then the MCG may stay in lock.

- <sup>8</sup> Below D<sub>unl</sub> minimum, the MCG will not exit lock if already in lock. Above D<sub>unl</sub> maximum, the MCG is guaranteed to exit lock.

### 2.11 AC Characteristics

This section describes ac timing characteristics for each peripheral system.

### 2.11.1 Control Timing

| Num | С | Parameter                                                                                                                                                                                                                                                           | Symbol                                | Min                           | Typ <sup>1</sup>     | Мах  | Unit |

|-----|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------|----------------------|------|------|

| 1   |   | Bus frequency (t <sub>cyc</sub> = 1/f <sub>Bus</sub> )                                                                                                                                                                                                              | f <sub>Bus</sub>                      | dc                            | _                    | 24   | MHz  |

| 2   |   | Internal low-power oscillator period                                                                                                                                                                                                                                | t <sub>LPO</sub>                      | 700                           |                      | 1300 | μS   |

| 3   |   | External reset pulse width <sup>2</sup><br>(t <sub>cyc</sub> = 1/f <sub>Self_reset</sub> )                                                                                                                                                                          | t <sub>extrst</sub>                   | 100                           |                      | _    | ns   |

| 4   |   | Reset low drive                                                                                                                                                                                                                                                     | t <sub>rstdrv</sub>                   | 66 x t <sub>cyc</sub>         |                      | _    | ns   |

| 5   |   | Active background debug mode latch setup time                                                                                                                                                                                                                       | t <sub>MSSU</sub>                     | 500                           |                      | —    | ns   |

| 6   |   | Active background debug mode latch hold time                                                                                                                                                                                                                        | t <sub>MSH</sub>                      | 100                           |                      | —    | ns   |

| 7   |   | IRQ pulse width<br>Asynchronous path <sup>2</sup><br>Synchronous path <sup>3</sup>                                                                                                                                                                                  | t <sub>ILIH,</sub> t <sub>IHIL</sub>  | 100<br>1.5 x t <sub>cyc</sub> | _                    | _    | ns   |

| 8   |   | KBIPx pulse width<br>Asynchronous path <sup>2</sup><br>Synchronous path <sup>3</sup>                                                                                                                                                                                | t <sub>ILIH,</sub> t <sub>IHIL</sub>  | 100<br>1.5 x t <sub>cyc</sub> | _                    | _    | ns   |

| 9   |   | Port rise and fall time (load = 50 pF) <sup>4</sup><br>Slew rate control disabled (PTxSE = 0) High drive<br>Slew rate control enabled (PTxSE = 1) High drive<br>Slew rate control disabled (PTxSE = 0) Low drive<br>Slew rate control enabled (PTxSE = 1) Low drive | t <sub>Rise</sub> , t <sub>Fall</sub> | —                             | 11<br>35<br>40<br>75 |      | ns   |

### Table 17. Control Timing

<sup>1</sup> Typical values are based on characterization data at  $V_{DD}$  = 5.0V, 25°C unless otherwise stated.

<sup>2</sup> This is the shortest pulse guaranteed to be recognized as a reset pin request. Shorter pulses are not guaranteed to override reset requests from internal sources.

<sup>3</sup> This is the minimum pulse width guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In stop mode, the synchronizer is bypassed so shorter pulses can be recognized in that case.

$^4$  Timing is shown with respect to 20% V<sub>DD</sub> and 80% V<sub>DD</sub> levels. Temperature range –40°C to 105°C.

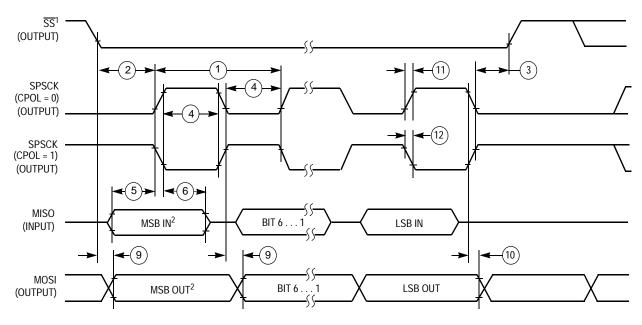

#### NOTES:

- 1.  $\overline{SS}$  output mode (DDS7 = 1, SSOE = 1).

- 2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

### Figure 14. SPI Master Timing (CPHA = 0)

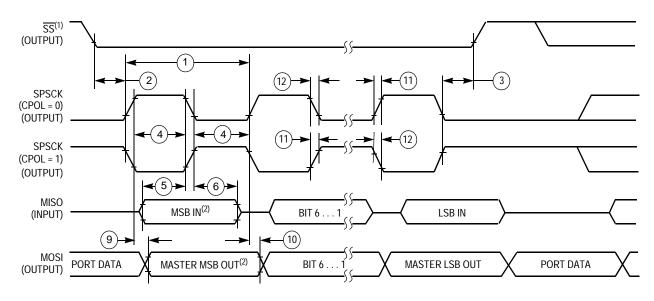

NOTES:

1.  $\overline{SS}$  output mode (DDS7 = 1, SSOE = 1).

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

#### Figure 15. SPI Master Timing (CPHA = 1)

## 2.13 Flash Specifications

This section provides details about program/erase times and program-erase endurance for the Flash memory.

Program and erase operations do not require any special power sources other than the normal V<sub>DD</sub> supply.

| Num | С | Characteristic                                                                                                                        | Symbol                  | Min Typ <sup>1</sup> Max |             | Мах  | Unit              |

|-----|---|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------|-------------|------|-------------------|

| 1   |   | Supply voltage for program/erase                                                                                                      | V <sub>prog/erase</sub> | 2.7                      |             | 5.5  | V                 |

| 2   |   | Supply voltage for read operation                                                                                                     | V <sub>Read</sub>       | 2.7                      |             | 5.5  | V                 |

| 3   |   | Internal FCLK frequency <sup>2</sup>                                                                                                  | f <sub>FCLK</sub>       | 150                      | 20          |      | kHz               |

| 4   |   | Internal FCLK period (1/FCLK)                                                                                                         | t <sub>Fcyc</sub>       | 5                        |             | 6.67 | μs                |

| 5   |   | Byte program time (random location) <sup>(2)</sup>                                                                                    | t <sub>prog</sub>       | 9                        |             |      | t <sub>Fcyc</sub> |

| 6   |   | Byte program time (burst mode) <sup>(2)</sup>                                                                                         | t <sub>Burst</sub>      | 4                        |             |      | t <sub>Fcyc</sub> |

| 7   |   | Page erase time <sup>3</sup>                                                                                                          | t <sub>Page</sub>       |                          | 4000        |      | t <sub>Fcyc</sub> |

| 8   |   | Mass erase time <sup>(2)</sup>                                                                                                        | t <sub>Mass</sub>       | 20,000                   |             |      | t <sub>Fcyc</sub> |

| 9   | с | Program/erase endurance <sup>4</sup><br>T <sub>L</sub> to T <sub>H</sub> = $-40^{\circ}$ C to + $105^{\circ}$ C<br>T = $25^{\circ}$ C |                         | 10,000                   | <br>100,000 |      | cycles            |

| 10  |   | Data retention <sup>5</sup>                                                                                                           | t <sub>D_ret</sub>      | 15                       | 100         | _    | years             |

<sup>1</sup> Typical values are based on characterization data at  $V_{DD} = 5.0 \text{ V}$ , 25°C unless otherwise stated.

<sup>2</sup> The frequency of this clock is controlled by a software setting.

- <sup>3</sup> These values are hardware state machine controlled. User code does not need to count cycles. This information supplied for calculating approximate time to program and erase.

- <sup>4</sup> Typical endurance for Flash was evaluated for this product family on the 9S12Dx64. For additional information on how Freescale Semiconductor defines typical endurance, please refer to Engineering Bulletin EB619/D, *Typical Endurance for Nonvolatile Memory*.

- <sup>5</sup> Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25°C using the Arrhenius equation. For additional information on how Freescale Semiconductor defines typical data retention, please refer to Engineering Bulletin EB618/D, Typical Data Retention for Nonvolatile Memory.

### 2.14 USB Electricals

The USB electricals for the USBOTG module conform to the standards documented by the Universal Serial Bus Implementers Forum. For the most up-to-date standards, visit http://www.usb.org.

If the Freescale USBOTG implementation requires additional or deviant electrical characteristics, this space would be used to communicate that information.

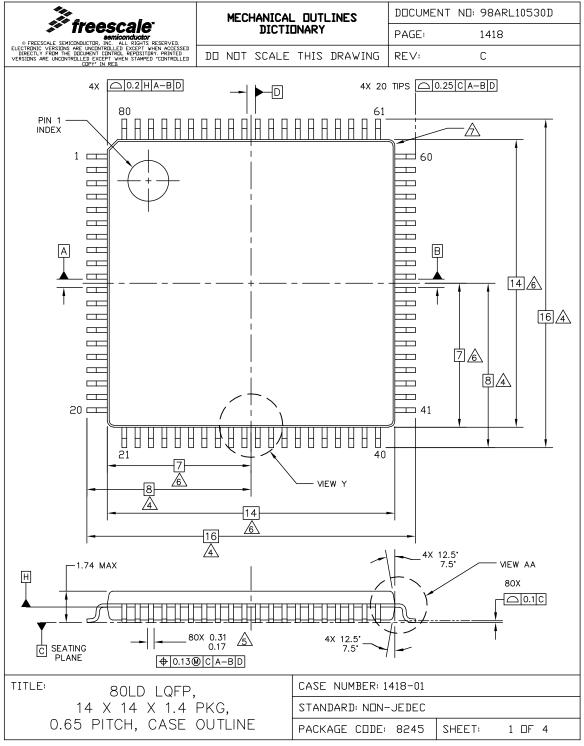

**Mechanical Outline Drawings**

# 3 Mechanical Outline Drawings

# 3.1 80-pin LQFP

Figure 18. 80-pin LQFP Diagram - I

N

| *** freescale.                                                                                                                                                                                                                                                                                                                                          | MECHANICAL OUTLINES |                      | DOCUMENT NO: 98ARL10530D |       |      |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|--------------------------|-------|------|------|

|                                                                                                                                                                                                                                                                                                                                                         | DICTI               | ONARY                | PAGE:                    |       | 1418 |      |

| <ul> <li>FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.<br/>ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br/>DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY. PRINTED<br/>VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED<br/>COPY" IN RED.</li> </ul>                                                                         | DO NOT SCALE        | THIS DRAWING         | REV:                     |       | С    |      |

| NOTES:                                                                                                                                                                                                                                                                                                                                                  |                     |                      |                          |       |      |      |

| 1. DIMENSIONS ARE IN MILLIMETERS.                                                                                                                                                                                                                                                                                                                       |                     |                      |                          |       |      |      |

| 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.                                                                                                                                                                                                                                                                                                   |                     |                      |                          |       |      |      |

| 3. DATUMS A, B AND D TO BE DETERMINED AT DATUM PLANE H.                                                                                                                                                                                                                                                                                                 |                     |                      |                          |       |      |      |

| A. DIMENSIONS TO BE DETERMINED AT SEATING PLANE C.                                                                                                                                                                                                                                                                                                      |                     |                      |                          |       |      |      |

| 5. THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR<br>PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE UPPER LIMIT<br>BY MORE THAN 0.08 mm AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE<br>LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN<br>PROTRUSION AND ADJACENT LEAD SHALL NOT BE LESS THAN 0.07 mm. |                     |                      |                          |       |      |      |

| 6. THIS DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION<br>IS 0.25 mm PER SIDE. THIS DIMENSION IS MAXIMUM PLASTIC BODY SIZE DIMENSION<br>INCLUDING MOLD MISMATCH.                                                                                                                                                                      |                     |                      |                          |       |      |      |

| A EXACT SHAPE OF EACH CORNER IS OPTIONAL.                                                                                                                                                                                                                                                                                                               |                     |                      |                          |       |      |      |

| AND 0.25 mm FROM THE LEAD TIP.                                                                                                                                                                                                                                                                                                                          |                     |                      |                          |       |      |      |

| AND 0.23 MIN FROM THE LEAD IF.                                                                                                                                                                                                                                                                                                                          |                     |                      |                          |       |      |      |

|                                                                                                                                                                                                                                                                                                                                                         |                     |                      |                          |       |      |      |

|                                                                                                                                                                                                                                                                                                                                                         |                     |                      |                          |       |      |      |

|                                                                                                                                                                                                                                                                                                                                                         |                     |                      |                          |       |      |      |

|                                                                                                                                                                                                                                                                                                                                                         |                     |                      |                          |       |      |      |

|                                                                                                                                                                                                                                                                                                                                                         |                     |                      |                          |       |      |      |

|                                                                                                                                                                                                                                                                                                                                                         |                     |                      |                          |       |      |      |

|                                                                                                                                                                                                                                                                                                                                                         |                     |                      |                          |       |      |      |

|                                                                                                                                                                                                                                                                                                                                                         |                     |                      |                          |       |      |      |

|                                                                                                                                                                                                                                                                                                                                                         |                     |                      |                          |       |      |      |

|                                                                                                                                                                                                                                                                                                                                                         |                     |                      |                          |       |      |      |

|                                                                                                                                                                                                                                                                                                                                                         |                     |                      |                          |       |      |      |

|                                                                                                                                                                                                                                                                                                                                                         |                     |                      |                          |       |      |      |

|                                                                                                                                                                                                                                                                                                                                                         |                     |                      |                          |       |      |      |

|                                                                                                                                                                                                                                                                                                                                                         |                     |                      |                          |       |      |      |

|                                                                                                                                                                                                                                                                                                                                                         |                     |                      |                          |       |      |      |

|                                                                                                                                                                                                                                                                                                                                                         |                     |                      |                          |       |      |      |

| TITLE: 80LD LQFP,<br>14 X 14 X 1.4<br>0.65 PITCH, CASE                                                                                                                                                                                                                                                                                                  | PKG,                | CASE NUMBER: 1418-01 |                          |       |      |      |

|                                                                                                                                                                                                                                                                                                                                                         |                     | STANDARD: NON-       | -JEDEC                   |       |      |      |

|                                                                                                                                                                                                                                                                                                                                                         |                     | PACKAGE CODE:        | 8245                     | SHEET | : 3  | OF 4 |

Figure 20. 80-pin LQFP Diagram - III

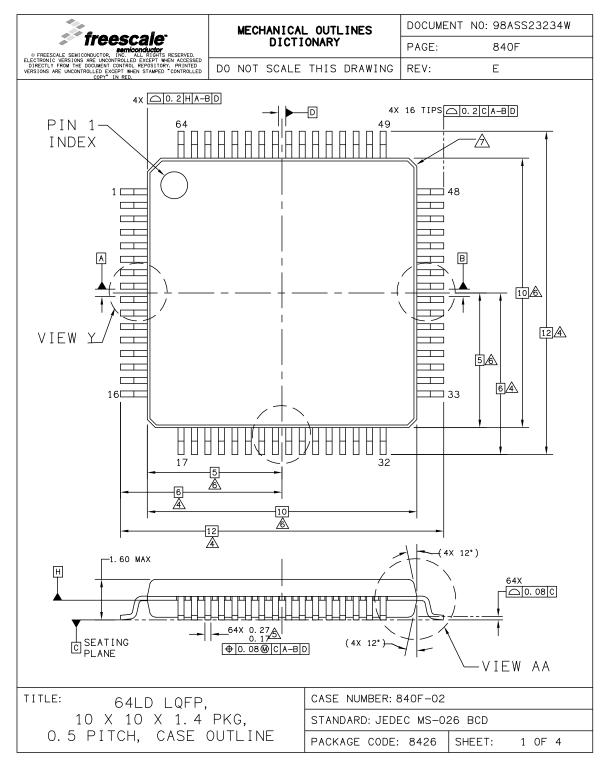

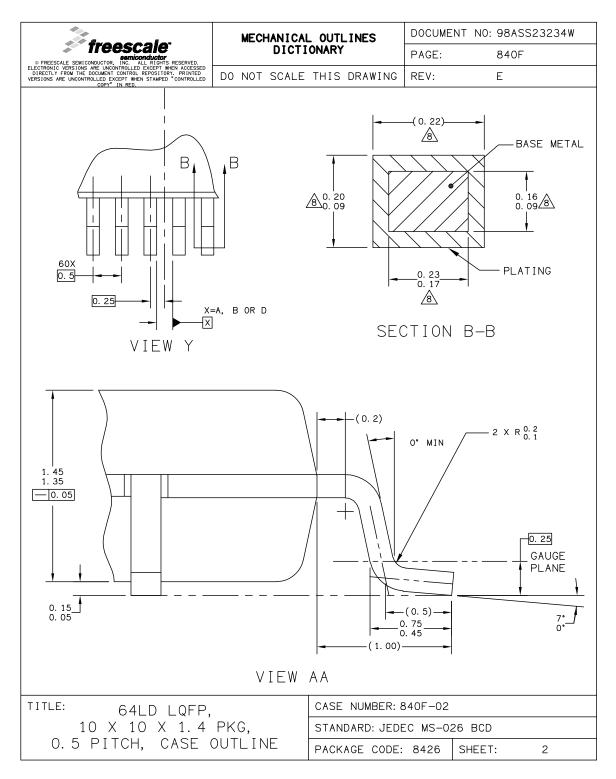

### 3.2 64-pin LQFP

Figure 21. 64-pin LQFP Diagram - I

Mechanical Outline Drawings

Figure 22. 64-pin LQFP Diagram - II

NP

**Mechanical Outline Drawings**

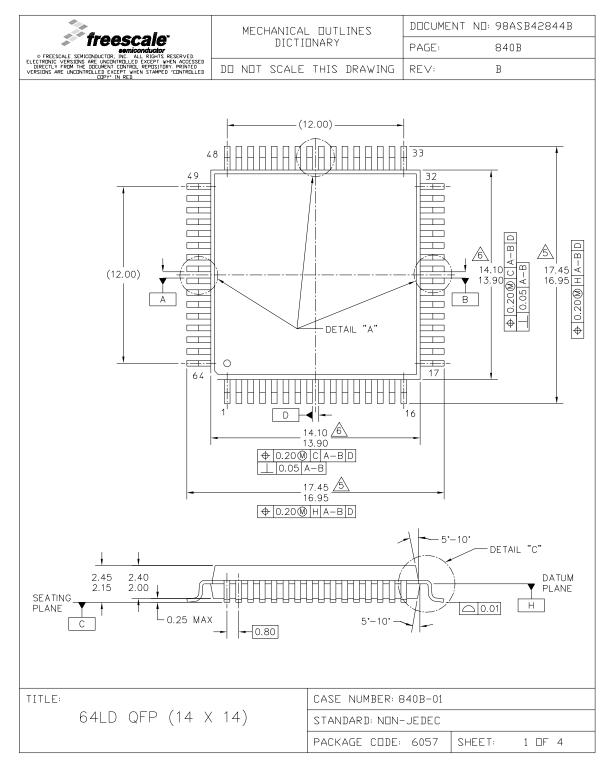

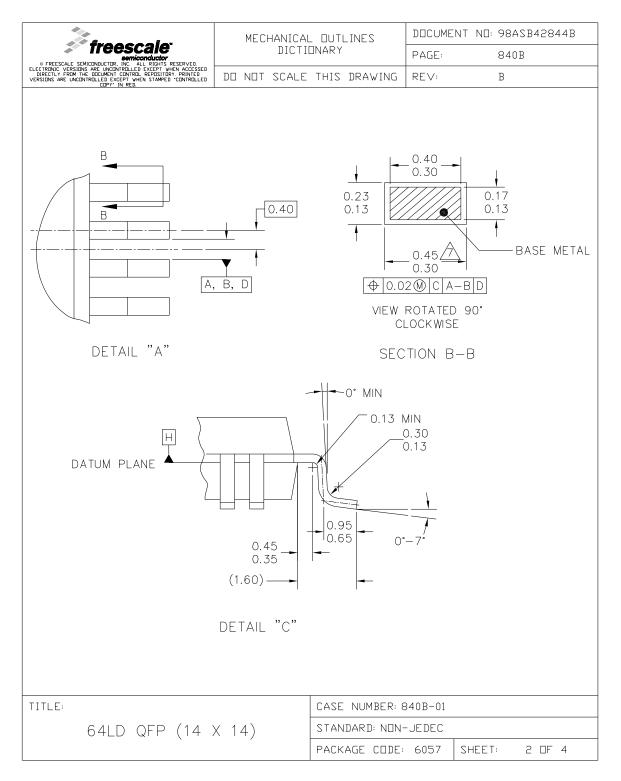

# 3.3 64-pin QFP

Figure 24. 64-pin QFP Diagram - I

Figure 25. 64-pin QFP Diagram - II