#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                     |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 20MHz                                                                       |

| Connectivity               | CANbus, SCI, SSU                                                            |

| Peripherals                | LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 45                                                                          |

| Program Memory Size        | 32KB (32K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | ·                                                                           |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-BQFP                                                                     |

| Supplier Device Package    | 64-QFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36034ghv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Keep safety first in your circuit designs!

Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any thirdparty's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

# Contents

| Sect | ion 1 C  | Overview                                     | 1  |

|------|----------|----------------------------------------------|----|

| 1.1  | Feature  | s                                            | 1  |

| 1.2  | Internal | Block Diagram                                |    |

| 1.3  | Pin Arr  | angement                                     |    |

| 1.4  | Pin Fun  | actions                                      | 5  |

| Sect | ion 2 C  | CPU                                          | 9  |

| 2.1  | Address  | s Space and Memory Map                       |    |

| 2.2  | Registe  | r Configuration                              | 14 |

|      | 2.2.1    | General Registers                            |    |

|      | 2.2.2    | Program Counter (PC)                         |    |

|      | 2.2.3    | Condition-Code Register (CCR)                |    |

| 2.3  | Data Fo  | ormats                                       |    |

|      | 2.3.1    | General Register Data Formats                |    |

|      | 2.3.2    | Memory Data Formats                          |    |

| 2.4  | Instruct | ion Set                                      |    |

|      | 2.4.1    | Table of Instructions Classified by Function |    |

|      | 2.4.2    | Basic Instruction Formats                    |    |

| 2.5  | Address  | sing Modes and Effective Address Calculation |    |

|      | 2.5.1    | Addressing Modes                             |    |

|      | 2.5.2    | Effective Address Calculation                |    |

| 2.6  | Basic B  | Sus Cycle                                    |    |

|      | 2.6.1    | Access to On-Chip Memory (RAM, ROM)          |    |

|      | 2.6.2    | On-Chip Peripheral Modules                   |    |

| 2.7  | CPU St   | ates                                         | 40 |

| 2.8  | Usage 1  | Notes                                        |    |

|      | 2.8.1    | Notes on Data Access to Empty Areas          |    |

|      | 2.8.2    | EEPMOV Instruction                           |    |

|      | 2.8.3    | Bit-Manipulation Instruction                 |    |

| Sect | ion 3 E  | Exception Handling                           | 49 |

| 3.1  |          | on Sources and Vector Address                |    |

| 3.2  | -        | r Descriptions                               |    |

|      | 3.2.1    | Interrupt Edge Select Register 1 (IEGR1)     |    |

|      | 3.2.2    | Interrupt Edge Select Register 2 (IEGR2)     |    |

|      | 3.2.3    | Interrupt Enable Register 1 (IENR1)          |    |

## RENESAS

• On-chip memory

|                               |           | Ν                   | lodel                                                                         |           |          |

|-------------------------------|-----------|---------------------|-------------------------------------------------------------------------------|-----------|----------|

| Product Classification        | ı         | Standard<br>Version | On-Chip Power-<br>On Reset and<br>Low-Voltage<br>Detecting Circuit<br>Version | ROM       | RAM      |

| Flash memory version          | H8/36057F | HD64F36057          | HD64F36057G                                                                   | 56 kbytes | 3 kbytes |

| (F-ZTAT <sup>™</sup> version) | H8/36054F | HD64F36054          | HD64F36054G                                                                   | 32 kbytes | 2 kbytes |

|                               | H8/36037F | HD64F36037          | HD64F36037G                                                                   | 56 kbytes | 3 kbytes |

|                               | H8/36034F | HD64F36034          | HD64F36034G                                                                   | 32 kbytes | 2 kbytes |

| Masked ROM version            | H8/36057  | HD64336057          | HD64336057G                                                                   | 56 kbytes | 2 kbytes |

|                               | H8/36054  | HD64336054          | HD64336054G                                                                   | 32 kbytes | 2 kbytes |

|                               | H8/36037  | HD64336037          | HD64336037G                                                                   | 56 kbytes | 2 kbytes |

|                               | H8/36036  | HD64336036          | HD64336036G                                                                   | 48 kbytes | 2 kbytes |

|                               | H8/36035  | HD64336035          | HD64336035G                                                                   | 40 kbytes | 2 kbytes |

|                               | H8/36034  | HD64336034          | HD64336034G                                                                   | 32 kbytes | 2 kbytes |

|                               | H8/36033  | HD64336033          | HD64336033G                                                                   | 24 kbytes | 1 kbyte  |

|                               | H8/36032  | HD64336032          | HD64336032G                                                                   | 16 kbytes | 1 kbyte  |

- General I/O ports

- I/O pins: 45 I/O pins, including 8 large current ports ( $I_{oL} = 20 \text{ mA}, @V_{oL} = 1.5 \text{ V}$ )

- Input-only pins: 8 input pins (also used for analog input)

- Supports various power-down modes

Note: F-ZTAT<sup>TM</sup> is a trademark of Renesas Technology Corp.

• Compact package

| Package | Code   | Body Size        | Pin Pitch |

|---------|--------|------------------|-----------|

| LQFP-64 | FP-64K | 10.0	imes10.0 mm | 0.5 mm    |

| QFP-64  | FP-64A | 14.0	imes14.0 mm | 0.8 mm    |

### 2.4 Instruction Set

#### 2.4.1 Table of Instructions Classified by Function

The H8/300H CPU has 62 instructions. Tables 2.2 to 2.9 summarize the instructions in each functional category. The notation used in tables 2.2 to 2.9 is defined below.

| Symbol        | Description                                            |

|---------------|--------------------------------------------------------|

| Rd            | General register (destination)*                        |

| Rs            | General register (source)*                             |

| Rn            | General register*                                      |

| ERn           | General register (32-bit register or address register) |

| (EAd)         | Destination operand                                    |

| (EAs)         | Source operand                                         |

| CCR           | Condition-code register                                |

| Ν             | N (negative) flag in CCR                               |

| Z             | Z (zero) flag in CCR                                   |

| V             | V (overflow) flag in CCR                               |

| С             | C (carry) flag in CCR                                  |

| PC            | Program counter                                        |

| SP            | Stack pointer                                          |

| #IMM          | Immediate data                                         |

| disp          | Displacement                                           |

| +             | Addition                                               |

| _             | Subtraction                                            |

| ×             | Multiplication                                         |

| ÷             | Division                                               |

| ^             | Logical AND                                            |

| $\vee$        | Logical OR                                             |

| $\oplus$      | Logical XOR                                            |

| $\rightarrow$ | Move                                                   |

| 7             | NOT (logical complement)                               |

| :3/:8/:16/:24 | 3-, 8-, 16-, or 24-bit length                          |

Table 2.1

Operation Notation

|       |          | Initial |     |                                                                                                |

|-------|----------|---------|-----|------------------------------------------------------------------------------------------------|

| Bit   | Bit Name | Value   | R/W | Description                                                                                    |

| 1     | DCMP1    | 0       | R/W | Data Compare Condition Select 1 and 0                                                          |

| 0     | DCMP0    | 0       | R/W | These bits set the comparison condition between the data set in BDR and the internal data bus. |

|       |          |         |     | 00: No data comparison                                                                         |

|       |          |         |     | 01: Compares lower 8-bit data between BDRL and data bus                                        |

|       |          |         |     | 10: Compares upper 8-bit data between BDRH and data bus                                        |

|       |          |         |     | 11: Compares 16-bit data between BDR and data bus                                              |

| Logor | adl      |         |     |                                                                                                |

[Legend] X: Don't care.

When an address break is set in the data read cycle or data write cycle, the data bus used will depend on the combination of the byte/word access and address. Table 4.1 shows the access and data bus used. When an I/O register space with an 8-bit data bus width is accessed in word size, a byte access is generated twice. For details on data widths of each register, see section 21.1, Register Addresses (Address Order).

### Table 4.1 Access and Data Bus Used

|                                         | Word         | Access       | Byte Access  |              |  |  |  |  |

|-----------------------------------------|--------------|--------------|--------------|--------------|--|--|--|--|

|                                         | Even Address | Odd Address  | Even Address | Odd Address  |  |  |  |  |

| ROM space                               | Upper 8 bits | Lower 8 bits | Upper 8 bits | Upper 8 bits |  |  |  |  |

| RAM space                               | Upper 8 bits | Lower 8 bits | Upper 8 bits | Upper 8 bits |  |  |  |  |

| I/O register with 8-bit data bus width  | Upper 8 bits | Upper 8 bits | Upper 8 bits | Upper 8 bits |  |  |  |  |

| I/O register with 16-bit data bus width | Upper 8 bits | Lower 8 bits | _            | —            |  |  |  |  |

### 10.4 Operation

### 10.4.1 Interval Timer Operation

When bit TMB17 in TMB1 is cleared to 0, timer B1 functions as an 8-bit interval timer. Upon reset, TCB1 is cleared to H'00 and bit TMB17 is cleared to 0, so up-counting and interval timing resume immediately. The operating clock of the timer B1 is selected from seven internal clock signals output by prescaler S, or an external clock input at pin TMB1. The selection is made by bits TMB12 to TMB10 in TMB1.

After the count value in TMB1 reaches H'FF, the next clock signal input causes timer B1 to overflow, setting flag IRRTB1 in IRR2 to 1. If IENTB1 in IENR2 is 1, an interrupt is requested to the CPU.

At overflow, TCB1 returns to H'00 and starts counting up again. During interval timer operation (TMB17 = 0), when a value is set in TLB1, the same value is set in TCB1.

### 10.4.2 Auto-Reload Timer Operation

Setting bit TMB17 in TMB1 to 1 causes timer B1 to function as an 8-bit auto-reload timer. When a reload value is set in TLB1, the same value is loaded into TCB1, becoming the value from which TCB1 starts its count. After the count value in TCB1 reaches H'FF, the next clock signal input causes timer B1 to overflow. The TLB1 value is then loaded into TCB1, and the count continues from that value. The overflow period can be set within a range from 1 to 256 input clocks, depending on the TLB1 value.

The clock sources and interrupts in auto-reload mode are the same as in interval mode. In auto-reload mode (TMB17 = 1), when a new value is set in TLB1, the TLB1 value is also loaded into TCB1.

### 10.4.3 Event Counter Operation

Timer B1 can operate as an event counter in which TMIB1 is set to an event input pin. External event counting is selected by setting bits TMB12 to TMB10 in TMB1 to 1. TCB1 counts up at rising or falling edge of an external event signal input at pin TMB1.

When timer B1 is used to count external event input, bit IRQ1 in PMR1 should be set to 1 and IEN1 in IENR1 should be cleared to 0 to disable IRQ1 interrupt requests.

- Eleven interrupt sources

- Four compare match/input capture interrupts and an overflow interrupt are available for each channel. An underflow interrupt can be set for channel 1.

| Item                                                   |            | Channel 0                                                          | Channel 1                                                        |  |  |  |  |

|--------------------------------------------------------|------------|--------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|--|

| Count clock                                            |            | Internal clocks: φ, φ/2, φ/4, φ/8<br>External clock: FTIOA0 (TCLK) |                                                                  |  |  |  |  |

| General registe<br>(output compare<br>capture register | e/input    | GRA_0, GRB_0, GRC_0, GRD_0                                         | GRA_1, GRB_1, GRC_1, GRD_1                                       |  |  |  |  |

| Buffer register                                        |            | GRC_0, GRD_0                                                       | GRC_1, GRD_1                                                     |  |  |  |  |

| I/O pins                                               |            | FTIOA0, FTIOB0, FTIOC0,<br>FTIOD0                                  | FTIOA1, FTIOB1, FTIOC1,<br>FTIOD1                                |  |  |  |  |

| Counter clearing                                       | g function | Compare match/input capture of GRA_0, GRB_0, GRC_0, or GRD_0       | Compare match/input capture of GRA_1, GRB_1, GRC_1, or GRD_1     |  |  |  |  |

| Compare                                                | 0 output   | Yes                                                                | Yes                                                              |  |  |  |  |

| match output                                           | 1 output   | Yes                                                                | Yes                                                              |  |  |  |  |

|                                                        | output     | Yes                                                                | Yes                                                              |  |  |  |  |

| Input capture fu                                       | nction     | Yes                                                                | Yes                                                              |  |  |  |  |

| Synchronous of                                         | peration   | Yes                                                                | Yes                                                              |  |  |  |  |

| PWM mode                                               |            | Yes                                                                | Yes                                                              |  |  |  |  |

| Reset synchron mode                                    | ous PWM    | Yes                                                                | Yes                                                              |  |  |  |  |

| Complementary mode                                     | / PWM      | Yes                                                                | Yes                                                              |  |  |  |  |

| Buffer function                                        |            | Yes                                                                | Yes                                                              |  |  |  |  |

| Interrupt source                                       | es         | Compare match/input capture A0<br>to D0<br>Overflow                | Compare match/input capture A1<br>to D1<br>Overflow<br>Underflow |  |  |  |  |

### Table 12.1 Timer Z Functions

#### 12.3.9 Timer Control Register (TCR)

The TCR registers select a TCNT counter clock, an edge when an external clock is selected, and counter clearing sources. Timer Z has a total of two TCR registers, one for each channel.

| Bit | Bit Name  | Initial<br>Value | R/W | Description                                                                                                             |

|-----|-----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------|

|     |           |                  | -   | Description                                                                                                             |

| 7   | CCLR2     | 0                | R/W | Counter Clear 2 to 0                                                                                                    |

| 6   | CCLR1     | 0                | R/W | 000: Disables TCNT clearing                                                                                             |

| 5   | CCLR0     | 0                | R/W | 001: Clears TCNT by GRA compare match/input<br>capture* <sup>1</sup>                                                    |

|     |           |                  |     | 010: Clears TCNT by GRB compare match/input<br>capture*1                                                                |

|     |           |                  |     | 011: Synchronization clear; Clears TCNT in synchronous with counter clearing of the other channel's timer* <sup>2</sup> |

|     |           |                  |     | 000: Disables TCNT clearing                                                                                             |

|     |           |                  |     | 001: Clears TCNT by GRC compare match/input<br>capture* <sup>1</sup>                                                    |

|     |           |                  |     | 010: Clears TCNT by GRD compare match/input<br>capture* <sup>1</sup>                                                    |

|     |           |                  |     | 011: Synchronization clear; Clears TCNT in synchronous with counter clearing of the other channel's timer* <sup>2</sup> |

| 4   | CKEG1     | 0                | R/W | Clock Edge 1 and 0                                                                                                      |

| 3   | CKEG0     | 0                | R/W | 00: Count at rising edge                                                                                                |

|     |           |                  |     | 01: Count at falling edge                                                                                               |

|     |           |                  |     | 1X: Count at both edges                                                                                                 |

| 2   | TPSC2     | 0                | R/W | Time Prescaler 2 to 0                                                                                                   |

| 1   | TPSC1     | 0                | R/W | 000: Internal clock: count by $\phi$                                                                                    |

| 0   | TPSC0     | 0                | R/W | 001: Internal clock: count by $\phi/2$                                                                                  |

|     |           |                  |     | 010: Internal clock: count by φ/4                                                                                       |

|     |           |                  |     | 011: Internal clock: count by                                                                                           |

|     |           |                  |     | 1XX: External clock: count by FTIOA0 (TCLK) pin input                                                                   |

|     | 1 14/1 01 | D (              |     | the standard management of the second barrier second states                                                             |

Notes: 1. When GR functions as an output compare register, TCNT is cleared by compare match. When GR functions as input capture, TCNT is cleared by input capture.

RENESAS

2. Synchronous operation is set by TMDR.

3. X: Don't care

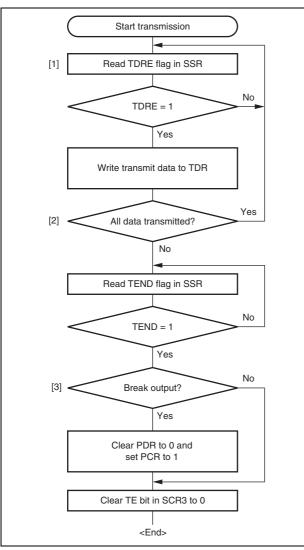

- [1] Read SSR and check that the TDRE flag is set to 1, then write transmit data to TDR. When data is written to TDR, the TDRE flag is automaticaly cleared to 0.

- [2] To continue serial transmission, read 1 from the TDRE flag to confirm that writing is possible, then write data to TDR. When data is written to TDR, the TDRE flag is automaticaly cleared to 0.

- [3] To output a break in serial transmission, after setting PCR to 1 and PDR to 0, clear TxD in PMR1 to 0, then clear the TE bit in SCR3 to 0.

Figure 14.6 Sample Serial Transmission Data Flowchart (Asynchronous Mode)

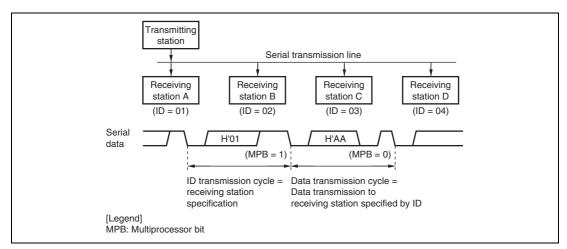

#### Figure 14.15 Example of Inter-Processor Communication Using Multiprocessor Format (Transmission of Data H'AA to Receiving Station A)

### 14.6.1 Multiprocessor Serial Data Transmission

Figure 14.14 shows a sample flowchart for multiprocessor serial data transmission. For an ID transmission cycle, set the MPBT bit in SSR to 1 before transmission. For a data transmission cycle, clear the MPBT bit in SSR to 0 before transmission. All other SCI3 operations are the same as those in asynchronous mode.

### 15.5 Operation

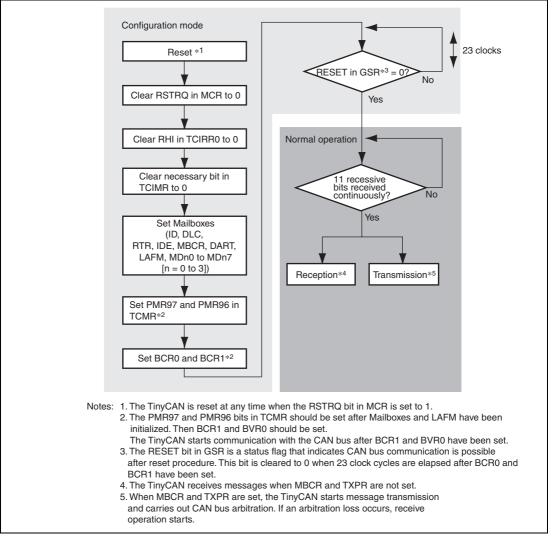

#### 15.5.1 TinyCAN Initial Settings

Figure 15.4 shows a flowchart for reset clearing of the TinyCAN. After a reset is cleared, all registers are initialized.

Figure 15.4 Reset Clearing Flowchart

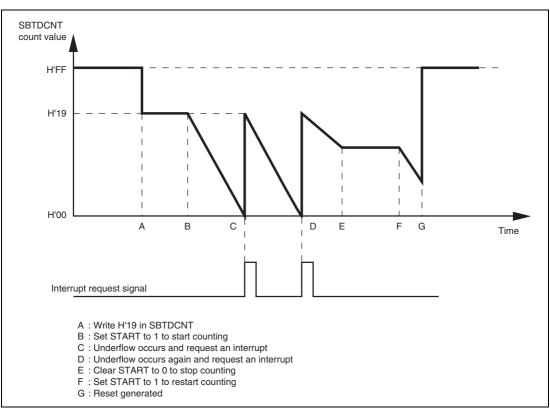

Figure 17.4 Example of Subtimer Operation

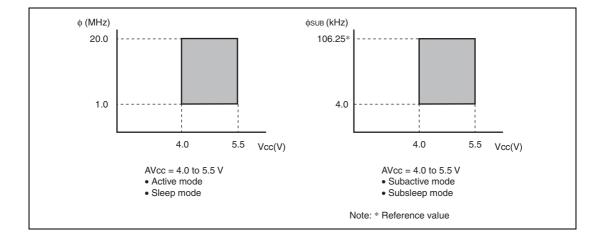

#### Range of Power Supply Voltage and Oscillation Frequency when Subtimer is Used:

#### Table 22.16 Controller Area Network for Tiny (TinyCAN) Timing

$V_{cc} = 2.7$  to 5.5 V,  $V_{ss} = 0.0$  V,  $T_a = -20$  to  $+75^{\circ}C$  (regular specifications) or  $T_a = -40$  to  $+85^{\circ}C$  (wide-range specifications), unless otherwise indicated.

|                                 |                   | Applicable     | Test            |            | Value    | s           |         | Reference   |

|---------------------------------|-------------------|----------------|-----------------|------------|----------|-------------|---------|-------------|

| Item                            | Symbol            | Pins           | Condition       | Min. Typ.  |          | Max.        | Unit    | Figure      |

| Transmit<br>data delay<br>time* | t <sub>htxd</sub> | HTXD           |                 | _          | _        | 50          | ns      | Figure 22.6 |

| Receive<br>data setup<br>time*  | t <sub>HRXS</sub> | HRXD           |                 | 50         | _        | _           | ns      | _           |

| Receive<br>data hold<br>time*   | t <sub>HRXH</sub> | HRXD           |                 | 50         | —        | _           | ns      | _           |

| Note: *                         | Although th       | ne TinyCAN inp | out/output sign | al is asyn | chronous | , its state | is dete | rmined to   |

have changed at the rising-edge (two clock cycles) of the CK clock shown in figure 22.6.

### 4. Shift Instructions

|          |             |              |     |    |      |           | ng<br>Lei   |     |          | nd<br>/tes | ) |              |                |          |            |                |   |                | No.<br>State |          |

|----------|-------------|--------------|-----|----|------|-----------|-------------|-----|----------|------------|---|--------------|----------------|----------|------------|----------------|---|----------------|--------------|----------|

| Mnemonic |             | Operand Size | #xx | -  | @ERn | @(d, ERn) | @-ERn/@ERn+ | @aa | @(d, PC) | @aa        |   | Operation    | Condition Code |          |            |                |   |                | Normal       | Advanced |

|          | 1           | -            | ŧ   | Rn | 0    | 0         | 0           | 8   | 0        | 0          |   |              | Т              | н        | N          | z              | ۷ | С              |              |          |

| SHAL     | SHAL.B Rd   | В            |     | 2  |      |           |             |     |          |            |   | C <b>-</b> 0 | -              | -        | \$         | €              | ↕ | \$             | 2            |          |

|          | SHAL.W Rd   | W            |     | 2  |      |           |             |     |          |            |   |              | -              | -        | \$         | €              | ↕ | \$             | 2            |          |

|          | SHAL.L ERd  | L            |     | 2  |      |           |             |     |          |            |   | MSB LSB      | -              | -        | \$         | \$             | ↕ | \$             | 2            |          |

| SHAR     | SHAR.B Rd   | В            |     | 2  |      |           |             |     |          |            |   | ► C          | -              | -        | \$         | \$             | 0 | \$             | 2            |          |

|          | SHAR.W Rd   | W            |     | 2  |      |           |             |     |          |            |   |              | -              | -        | \$         | €              | 0 | \$             | 2            |          |

|          | SHAR.L ERd  | L            |     | 2  |      |           |             |     |          |            |   | MSB LSB      | _              | _        | \$         | ↕              | 0 | \$             | 2            | 2        |

| SHLL     | SHLL.B Rd   | В            |     | 2  |      |           |             |     |          |            |   | C0           | _              | _        | \$         | ↕              | 0 | \$             | 2            |          |

| ŀ        | SHLL.W Rd   | W            |     | 2  |      |           |             |     |          |            |   |              | _              | _        | \$         | ↕              | 0 | \$             | 2            | 2        |

|          | SHLL.L ERd  | L            |     | 2  |      |           |             |     |          |            |   | MSB LSB      | -              | _        | \$         | €              | 0 | \$             | 2            |          |

| SHLR     | SHLR.B Rd   | В            |     | 2  |      |           |             |     |          |            |   | 0 -> C       | -              | -        | \$         | €              | 0 | ↕              | 2            | _        |

|          | SHLR.W Rd   | W            |     | 2  |      |           |             |     |          |            |   |              | -              | -        | \$         | €              | 0 | \$             | 2            |          |

|          | SHLR.L ERd  | L            |     | 2  |      |           |             |     |          |            |   | MSB LSB      | -              | -        | €          | €              | 0 | ↕              | 2            | 2        |

| ROTXL    | ROTXL.B Rd  | В            |     | 2  |      |           |             |     |          |            |   |              | _              | -        | \$         | €              | 0 | $\updownarrow$ | 2            | 2        |

|          | ROTXL.W Rd  | W            |     | 2  |      |           |             |     |          |            |   |              | _              | -        | \$         | €              | 0 | \$             | 2            | 2        |

|          | ROTXL.L ERd | L            |     | 2  |      |           |             |     |          |            |   | MSB 🔶 LSB    | —              | _        | \$         | €              | 0 | \$             | 2            | 2        |

| ROTXR    | ROTXR.B Rd  | В            |     | 2  |      |           |             |     |          |            |   | ┍╸────┝╸┏╴   | —              | <u> </u> | \$         | €              | 0 | $\updownarrow$ | 2            | 2        |

|          | ROTXR.W Rd  | W            |     | 2  |      |           |             |     |          |            |   |              | _              | -        | \$         | €              | 0 | $\updownarrow$ | 2            | 2        |

|          | ROTXR.L ERd | L            |     | 2  |      |           |             |     |          |            |   | MSB → LSB    | —              | —        | \$         | €              | 0 | \$             | 2            | 2        |

| ROTL     | ROTL.B Rd   | В            |     | 2  |      |           |             |     |          |            |   |              | —              | -        | $\uparrow$ | $\updownarrow$ | 0 | $\updownarrow$ | 2            | 2        |

|          | ROTL.W Rd   | W            |     | 2  |      |           |             |     |          |            |   |              | —              | -        | \$         | €              | 0 | $\updownarrow$ | 2            | 2        |

|          | ROTL.L ERd  | L            |     | 2  |      |           |             |     |          |            |   | MSB - LSB    | —              | -        | €          | €              | 0 | ↕              | 2            | 2        |

| ROTR     | ROTR.B Rd   | В            |     | 2  |      |           |             |     |          |            |   | ► ►C         | —              | _        | \$         | €              | 0 | $\updownarrow$ | 2            | 2        |

|          | ROTR.W Rd   | W            |     | 2  |      |           |             |     |          |            |   |              | _              | _        | \$         | €              | 0 | $\updownarrow$ | 2            | 2        |

|          | ROTR.L ERd  | L            |     | 2  |      |           |             |     |          |            |   | MSB          | -              | -        | \$         | \$             | 0 | \$             | 2            | 2        |

## A.2 Operation Code Map

### Table A.2 Operation Code Map (1)

|                                                   |    | e A.2                       | e A.2                                               |   |       | щ   |                  |             |                                    |     |      |     |               |    |     |     |     |  |  |  |  |

|---------------------------------------------------|----|-----------------------------|-----------------------------------------------------|---|-------|-----|------------------|-------------|------------------------------------|-----|------|-----|---------------|----|-----|-----|-----|--|--|--|--|

|                                                   | ш. | Table A.2<br>(2)            | Table A.2<br>(2)                                    |   |       | BLE |                  |             |                                    |     |      |     |               |    |     |     |     |  |  |  |  |

|                                                   | ш  | ADDX                        | SUBX                                                |   |       | BGT | JSR              |             | A.2                                |     |      |     |               |    |     |     |     |  |  |  |  |

| Instruction when most significant bit of BH is 0. |    |                             | 0                                                   |   |       | BLT |                  |             | Table A.2<br>(3)                   |     |      |     |               |    |     |     |     |  |  |  |  |

|                                                   | U  | MOV                         | CMP                                                 |   |       | BGE | BSR              |             |                                    |     |      |     |               |    |     |     |     |  |  |  |  |

|                                                   | 8  | Table A.2 Table A.2 (2) (2) | Table A.2 Table A.2 (2)                             |   |       | BMI |                  | ^ ^         | EEPMOV                             |     |      |     |               |    |     |     |     |  |  |  |  |

| ignifica<br>ignifica                              | ٩  | Table A.2<br>(2)            | Table A.2<br>(2)                                    |   |       | BPL | JMP              |             | Table A.2 Table A.2 EEPMOV (2) (2) |     |      |     |               |    |     |     |     |  |  |  |  |

| most s<br>most s                                  | 6  |                             | m                                                   |   |       | BVS |                  |             | Table A.2<br>(2)                   |     |      |     |               |    |     |     |     |  |  |  |  |

| when 1<br>when 1                                  | 8  | ADD                         | SUB                                                 |   |       | BVC | Table A.2<br>(2) |             | NOM                                |     |      |     |               |    |     |     |     |  |  |  |  |

| truction                                          | 7  | LDC                         | Table A.2<br>(2)                                    |   | MOV.B | BEQ | TRAPA            | BST<br>BIST | BLD                                | ADD | ADDX | CMP | SUBX          | OR | XOR | AND | MOV |  |  |  |  |

|                                                   | 9  | ANDC                        | AND.B                                               |   |       |     |                  |             |                                    | BNE | RTE  |     | BAND<br>BIAND |    |     |     |     |  |  |  |  |

|                                                   | 2  | XORC                        | XOR.B                                               |   |       | BCS | BSR              |             | BXOR<br>BIXOR                      |     |      |     |               |    |     |     |     |  |  |  |  |

| byte<br>BL                                        | 4  | ORC                         | OR.B                                                |   |       | BCC | RTS              | OR          | BOR<br>BIOR                        |     |      |     |               |    |     |     |     |  |  |  |  |

| 2nd byte<br>BH BL                                 | e  | LDC                         | Table A.2<br>(2)                                    |   |       | BLS | DIVXU            |             | מ                                  |     |      |     |               |    |     |     |     |  |  |  |  |

| 1st byte<br>AH AL                                 | 5  | STC                         | Table A.2<br>(2)                                    |   |       | BHI | MULXU            | i<br>i      | BCLH                               |     |      |     |               |    |     |     |     |  |  |  |  |

|                                                   | -  | Table A.2<br>(2)            | Table A.2 Table A.2 Table A.2 Table A.2 (2) (2) (2) |   |       | BRN | DIVXU            | ł           | BNO                                |     |      |     |               |    |     |     |     |  |  |  |  |

| ion cod                                           | 0  | NOP                         | Table A.2<br>(2)                                    |   |       | BRA | MULXU            |             | BSE                                |     |      |     |               |    |     |     |     |  |  |  |  |

| Instruction code:                                 | AH | 0                           | -                                                   | N | ю     | 4   | ы                | 9           | 7                                  | ø   | თ    | ¥   | В             | U  | ۵   | ш   | ш   |  |  |  |  |

#### Appendix

| Instruction | Mnemonic           | Instruction<br>Fetch<br>I | Branch<br>Addr. Read<br>J | Stack<br>Operation<br>K | Byte Data<br>Access<br>L | Word Data<br>Access<br>M | Internal<br>Operation<br>N |

|-------------|--------------------|---------------------------|---------------------------|-------------------------|--------------------------|--------------------------|----------------------------|

| Bcc         | BLT d:8            | 2                         |                           |                         |                          |                          |                            |

|             | BGT d:8            | 2                         |                           |                         |                          |                          |                            |

|             | BLE d:8            | 2                         |                           |                         |                          |                          |                            |

|             | BRA d:16(BT d:16)  | 2                         |                           |                         |                          |                          | 2                          |

|             | BRN d:16(BF d:16)  | 2                         |                           |                         |                          |                          | 2                          |

|             | BHI d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BLS d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BCC d:16(BHS d:16) | 2                         |                           |                         |                          |                          | 2                          |

|             | BCS d:16(BLO d:16) | 2                         |                           |                         |                          |                          | 2                          |

|             | BNE d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BEQ d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BVC d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BVS d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BPL d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BMI d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BGE d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BLT d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BGT d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BLE d:16           | 2                         |                           |                         |                          |                          | 2                          |

| BCLR        | BCLR #xx:3, Rd     | 1                         |                           |                         |                          |                          |                            |

|             | BCLR #xx:3, @ERd   | 2                         |                           |                         | 2                        |                          |                            |

|             | BCLR #xx:3, @aa:8  | 2                         |                           |                         | 2                        |                          |                            |

|             | BCLR Rn, Rd        | 1                         |                           |                         |                          |                          |                            |

|             | BCLR Rn, @ERd      | 2                         |                           |                         | 2                        |                          |                            |

|             | BCLR Rn, @aa:8     | 2                         |                           |                         | 2                        |                          |                            |

| BIAND       | BIAND #xx:3, Rd    | 1                         |                           |                         |                          |                          |                            |

|             | BIAND #xx:3, @ERd  | 2                         |                           |                         | 1                        |                          |                            |

|             | BIAND #xx:3, @aa:8 | 2                         |                           |                         | 1                        |                          |                            |

| BILD        | BILD #xx:3, Rd     | 1                         |                           |                         |                          |                          |                            |

|             | BILD #xx:3, @ERd   | 2                         |                           |                         | 1                        |                          |                            |

|             | BILD #xx:3, @aa:8  | 2                         |                           |                         | 1                        |                          |                            |

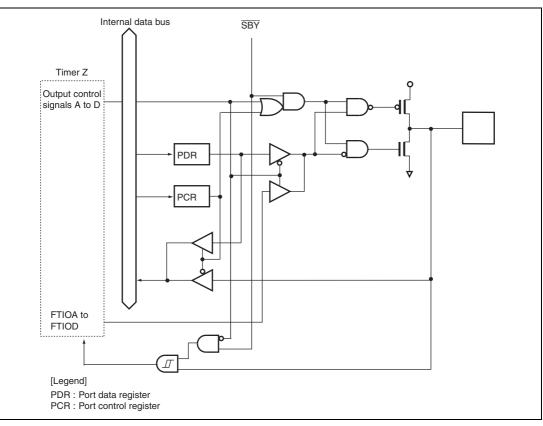

Figure B.12 Port 6 Block Diagram (P67 to P60)

# Index

# A

| A/D converter                        | 391  |

|--------------------------------------|------|

| Sample-and-hold circuit              | 398  |

| Scan mode                            | 397  |

| Single mode                          | 397  |

| Address break                        | 67   |

| Addressing modes                     | 32   |

| Absolute address                     | 33   |

| Immediate                            | 34   |

| Memory indirect                      | 34   |

| Program-counter relative             | 34   |

| Register direct                      |      |

| Register indirect                    | 33   |

| Register indirect with displacement. | 33   |

| Register indirect with post-incremen | t 33 |

| Register indirect with pre-decrement | t 33 |

# С

| Clock pulse generators            | 73  |

|-----------------------------------|-----|

| Prescaler S                       | 76  |

| System clock generator            | 74  |

| Condition field                   | 31  |

| Condition-code register (CCR)     | 16  |

| Controller area network (TinyCAN) | 295 |

| Mailbox                           | 340 |

| Message reception                 | 336 |

| Message transmission              | 327 |

| Time Quanta                       | 326 |

| TinyCAN standby transition        | 342 |

| CPU                               | 9   |

# E

| Effective address           | 36 |

|-----------------------------|----|

| Effective address extension | 31 |

| Exception handling          | 49 |

| Reset exception handling | 59 |

|--------------------------|----|

| Stack status             | 63 |

| Trap instruction         | 49 |

## G

| General registers15 | General | registers |  | 15 |

|---------------------|---------|-----------|--|----|

|---------------------|---------|-----------|--|----|

# I

| I/O ports                           | 111 |

|-------------------------------------|-----|

| Instruction set                     | 21  |

| Arithmetic operations instructions. | 23  |

| Bit manipulation instructions       | 26  |

| Block data transfer instructions    | 30  |

| Branch instructions                 | 28  |

| Data transfer instructions          | 22  |

| Logic operations instructions       | 25  |

| Shift instructions                  |     |

| System control instructions         |     |

| Internal power supply Step-down     |     |

| circuit                             | 413 |

| Interrupt                           |     |

| Internal interrupts                 | 61  |

| Interrupt response time             |     |

| IRQ3 to IRQ0 interrupts             |     |

| NMI interrupt                       |     |

| WKP5 to WKP0 interrupts             |     |

| Interrupt mask bit                  |     |

| 1                                   |     |

# L

RENESAS

| Large current ports                    | 2 |

|----------------------------------------|---|

| Low-voltage detection circuit          | 3 |

| LVDI (interrupt by low voltage detect) |   |

| circuit41                              | 0 |