#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | Н8/300Н                                                                      |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20MHz                                                                        |

| Connectivity               | CANbus, SCI, SSU                                                             |

| Peripherals                | PWM, WDT                                                                     |

| Number of I/O              | 45                                                                           |

| Program Memory Size        | 56KB (56K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 3K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-LQFP                                                                      |

| Supplier Device Package    | 64-LFQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36037fzjv |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **General Precautions on Handling of Product**

- 1. Treatment of NC Pins

- Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

- 2. Treatment of Unused Input Pins

- Note: Fix all unused input pins to high or low level. Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a passthrough current flows internally, and a malfunction may occur.

- 3. Processing before Initialization

- Note: When power is first supplied, the product's state is undefined. The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

- 4. Prohibition of Access to Undefined or Reserved Addresses

- Note: Access to undefined or reserved addresses is prohibited. The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

## Contents

| Sect | ion 1 C  | Overview                                     | 1  |

|------|----------|----------------------------------------------|----|

| 1.1  | Feature  | s                                            | 1  |

| 1.2  | Internal | Block Diagram                                |    |

| 1.3  | Pin Arr  | angement                                     | 4  |

| 1.4  | Pin Fun  | actions                                      | 5  |

| Sect | ion 2 C  | CPU                                          | 9  |

| 2.1  | Address  | s Space and Memory Map                       |    |

| 2.2  | Registe  | r Configuration                              | 14 |

|      | 2.2.1    | General Registers                            |    |

|      | 2.2.2    | Program Counter (PC)                         |    |

|      | 2.2.3    | Condition-Code Register (CCR)                |    |

| 2.3  | Data Fo  | ormats                                       |    |

|      | 2.3.1    | General Register Data Formats                |    |

|      | 2.3.2    | Memory Data Formats                          |    |

| 2.4  | Instruct | ion Set                                      |    |

|      | 2.4.1    | Table of Instructions Classified by Function |    |

|      | 2.4.2    | Basic Instruction Formats                    |    |

| 2.5  | Address  | sing Modes and Effective Address Calculation |    |

|      | 2.5.1    | Addressing Modes                             |    |

|      | 2.5.2    | Effective Address Calculation                |    |

| 2.6  | Basic B  | Sus Cycle                                    |    |

|      | 2.6.1    | Access to On-Chip Memory (RAM, ROM)          |    |

|      | 2.6.2    | On-Chip Peripheral Modules                   |    |

| 2.7  | CPU St   | ates                                         |    |

| 2.8  | Usage 1  | Notes                                        |    |

|      | 2.8.1    | Notes on Data Access to Empty Areas          |    |

|      | 2.8.2    | EEPMOV Instruction                           |    |

|      | 2.8.3    | Bit-Manipulation Instruction                 |    |

| Sect | ion 3 E  | Exception Handling                           | 49 |

| 3.1  |          | on Sources and Vector Address                |    |

| 3.2  | -        | r Descriptions                               |    |

|      | 3.2.1    | Interrupt Edge Select Register 1 (IEGR1)     |    |

|      | 3.2.2    | Interrupt Edge Select Register 2 (IEGR2)     |    |

|      | 3.2.3    | Interrupt Enable Register 1 (IENR1)          |    |

## RENESAS

## Section 4 Address Break

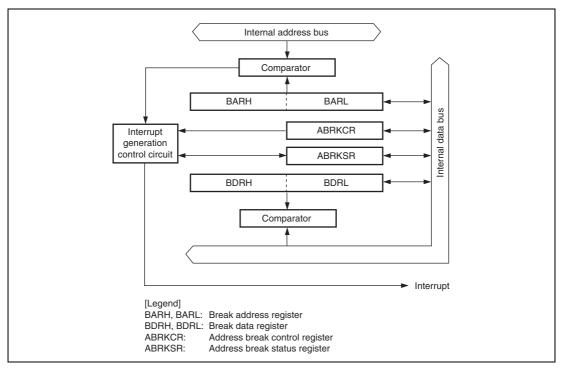

The address break simplifies on-board program debugging. It requests an address break interrupt when the set break condition is satisfied. The interrupt request is not affected by the I bit in CCR. Break conditions that can be set include instruction execution at a specific address and a combination of access and data at a specific address. With the address break function, the execution start point of a program containing a bug is detected and execution is branched to the correcting program. Figure 4.1 shows a block diagram of the address break.

Figure 4.1 Block Diagram of Address Break

|       |          | Initial |     |                                                                                                |

|-------|----------|---------|-----|------------------------------------------------------------------------------------------------|

| Bit   | Bit Name | Value   | R/W | Description                                                                                    |

| 1     | DCMP1    | 0       | R/W | Data Compare Condition Select 1 and 0                                                          |

| 0     | DCMP0    | 0       | R/W | These bits set the comparison condition between the data set in BDR and the internal data bus. |

|       |          |         |     | 00: No data comparison                                                                         |

|       |          |         |     | 01: Compares lower 8-bit data between BDRL and data bus                                        |

|       |          |         |     | 10: Compares upper 8-bit data between BDRH and data bus                                        |

|       |          |         |     | 11: Compares 16-bit data between BDR and data bus                                              |

| Logor | adl      |         |     |                                                                                                |

[Legend] X: Don't care.

When an address break is set in the data read cycle or data write cycle, the data bus used will depend on the combination of the byte/word access and address. Table 4.1 shows the access and data bus used. When an I/O register space with an 8-bit data bus width is accessed in word size, a byte access is generated twice. For details on data widths of each register, see section 21.1, Register Addresses (Address Order).

#### Table 4.1 Access and Data Bus Used

|                                         | Word         | Access       | Byte Access  |              |  |

|-----------------------------------------|--------------|--------------|--------------|--------------|--|

|                                         | Even Address | Odd Address  | Even Address | Odd Address  |  |

| ROM space                               | Upper 8 bits | Lower 8 bits | Upper 8 bits | Upper 8 bits |  |

| RAM space                               | Upper 8 bits | Lower 8 bits | Upper 8 bits | Upper 8 bits |  |

| I/O register with 8-bit data bus width  | Upper 8 bits | Upper 8 bits | Upper 8 bits | Upper 8 bits |  |

| I/O register with 16-bit data bus width | Upper 8 bits | Lower 8 bits | _            | —            |  |

## 7.4 Flash Memory Programming/Erasing

A software method using the CPU is employed to program and erase flash memory in the onboard programming modes. Depending on the FLMCR1 setting, the flash memory operates in one of the following four modes: Program mode, program-verify mode, erase mode, and erase-verify mode. The programming control program in boot mode and the user program/erase control program in user program mode use these operating modes in combination to perform programming/erasing. Flash memory programming and erasing should be performed in accordance with the descriptions in section 7.4.1, Program/Program-Verify and section 7.4.2, Erase/Erase-Verify, respectively.

### 7.4.1 Program/Program-Verify

When writing data or programs to the flash memory, the program/program-verify flowchart shown in figure 7.3 should be followed. Performing programming operations according to this flowchart will enable data or programs to be written to the flash memory without subjecting the chip to voltage stress or sacrificing program data reliability.

- 1. Programming must be done to an empty address. Do not reprogram an address to which programming has already been performed.

- 2. Programming should be carried out 128 bytes at a time. A 128-byte data transfer must be performed even if writing fewer than 128 bytes. In this case, H'FF data must be written to the extra addresses.

- 3. Prepare the following data storage areas in RAM: A 128-byte programming data area, a 128byte reprogramming data area, and a 128-byte additional-programming data area. Perform reprogramming data computation according to table 7.4, and additional programming data computation according to table 7.5.

- 4. Consecutively transfer 128 bytes of data in byte units from the reprogramming data area or additional-programming data area to the flash memory. The program address and 128-byte data are latched in the flash memory. The lower 8 bits of the start address in the flash memory destination area must be H'00 or H'80.

- 5. The time during which the P bit is set to 1 is the programming time. Table 7.6 shows the allowable programming times.

- 6. The watchdog timer (WDT) is set to prevent overprogramming due to program runaway, etc. An overflow cycle of approximately 6.6 ms is allowed.

- 7. For a dummy write to a verify address, write 1-byte data H'FF to an address whose lower 2 bits are B'00. Verify data can be read in words or in longwords from the address to which a dummy write was performed.

| Program Data | Verify Data | Reprogram Data | Comments                |

|--------------|-------------|----------------|-------------------------|

| 0            | 0           | 1              | Programming completed   |

| 0            | 1           | 0              | Reprogram bit           |

| 1            | 0           | 1              | _                       |

| 1            | 1           | 1              | Remains in erased state |

#### Table 7.4 Reprogram Data Computation Table

#### Table 7.5 Additional-Program Data Computation Table

| Reprogram Data | Verify Data | Additional-Program<br>Data | Comments                  |

|----------------|-------------|----------------------------|---------------------------|

| 0              | 0           | 0                          | Additional-program bit    |

| 0              | 1           | 1                          | No additional programming |

| 1              | 0           | 1                          | No additional programming |

| 1              | 1           | 1                          | No additional programming |

#### Table 7.6Programming Time

| n<br>(Number of Writes) | Programming<br>Time | In Additional<br>Programming | Comments |  |

|-------------------------|---------------------|------------------------------|----------|--|

| 1 to 6                  | 30                  | 10                           |          |  |

| 7 to 1,000              | 200                 | _                            |          |  |

Note: Time shown in  $\mu$ s.

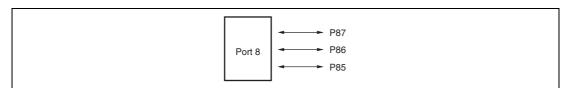

## 9.6 Port 8

Port 8 is a general I/O port. Each pin of the port 8 is shown in figure 9.6.

#### Figure 9.6 Port 8 Pin Configuration

Port 8 has the following registers.

- Port control register 8 (PCR8)

- Port data register 8 (PDR8)

#### 9.6.1 Port Control Register 8 (PCR8)

PCR8 selects inputs/outputs in bit units for pins to be used as general I/O ports of port 8.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                |

|--------|----------|------------------|-----|--------------------------------------------------------------------------------------------|

| 7      | PCR87    | 0                | W   | When each of the port 8 pins P87 to P85 functions as a                                     |

| 6      | PCR86    | 0                | W   | general I/O port, setting a PCR8 bit to 1 makes the                                        |

| 5      | PCR85    | 0                | W   | corresponding pin an output port, while clearing the bit to 0 makes the pin an input port. |

| 4 to 0 |          |                  | _   | Reserved                                                                                   |

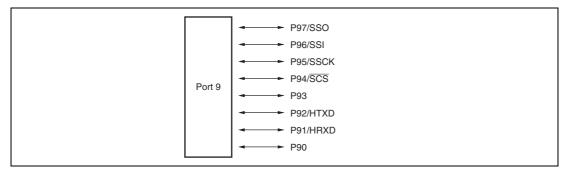

## 9.7 Port 9

Port 9 is a general I/O port also functioning as a TinyCAN I/O pin and an SSU I/O pin. Each pin of the port 9 is shown in figure 9.7.

Port 9 has the following registers.

- Port control register 9 (PCR9)

- Port data register 9 (PDR9)

#### 9.7.1 Port Control Register 9 (PCR9)

PCR9 selects inputs/outputs in bit units for pins to be used as general I/O ports of port 9.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                     |

|-----|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------|

| 7   | PCR97    | 0                | W   | When each of the port 9 pins P97 to P90 functions as a                                                          |

| 6   | PCR96    | 0                | W   | general I/O port, setting a PCR9 bit to 1 makes the corresponding pin an output port, while clearing the bit to |

| 5   | PCR95    | 0                | W   | 0 makes the pin an input port.                                                                                  |

| 4   | PCR94    | 0                | W   |                                                                                                                 |

| 3   | PCR93    | 0                | W   |                                                                                                                 |

| 2   | PCR92    | 0                | W   |                                                                                                                 |

| 1   | PCR91    | 0                | W   |                                                                                                                 |

| 0   | PCR90    | 0                | W   |                                                                                                                 |

## Section 11 Timer V

The timer V is an 8-bit timer based on an 8-bit counter. The timer V counts external events. Compare-match signals with two registers can also be used to reset the counter, request an interrupt, or output a pulse signal with an arbitrary duty cycle. Counting can be initiated by a trigger input at the TRGV pin, enabling pulse output control to be synchronized to the trigger, with an arbitrary delay from the trigger input. Figure 11.1 shows a block diagram of the timer V.

### 11.1 Features

- Choice of seven clock signals is available.

Choice of six internal clock sources (φ/128, φ/64, φ/32, φ/16, φ/8, φ/4) or an external clock.

- Counter can be cleared by compare match A or B, or by an external reset signal. If the count stop function is selected, the counter can be halted when cleared.

- Timer output is controlled by two independent compare match signals, enabling pulse output with an arbitrary duty cycle, PWM output, and other applications.

- Three interrupt sources: compare match A, compare match B, timer overflow

- Counting can be initiated by trigger input at the TRGV pin. The rising edge, falling edge, or both edges of the TRGV input can be selected.

- Eleven interrupt sources

- Four compare match/input capture interrupts and an overflow interrupt are available for each channel. An underflow interrupt can be set for channel 1.

| Item                                                   |          | Channel 0                                                          | Channel 1                                                        |  |  |  |

|--------------------------------------------------------|----------|--------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|

| Count clock                                            |          | Internal clocks: φ, φ/2, φ/4, φ/8<br>External clock: FTIOA0 (TCLK) |                                                                  |  |  |  |

| General registe<br>(output compare<br>capture register | e/input  | GRA_0, GRB_0, GRC_0, GRD_0                                         | GRA_1, GRB_1, GRC_1, GRD_1                                       |  |  |  |

| Buffer register                                        |          | GRC_0, GRD_0                                                       | GRC_1, GRD_1                                                     |  |  |  |

| I/O pins                                               |          | FTIOA0, FTIOB0, FTIOC0,<br>FTIOD0                                  | FTIOA1, FTIOB1, FTIOC1,<br>FTIOD1                                |  |  |  |

| Counter clearing function                              |          | Compare match/input capture of GRA_0, GRB_0, GRC_0, or GRD_0       | Compare match/input capture of GRA_1, GRB_1, GRC_1, or GRD_1     |  |  |  |

| Compare                                                | 0 output | Yes                                                                | Yes                                                              |  |  |  |

| match output                                           | 1 output | Yes                                                                | Yes                                                              |  |  |  |

|                                                        | output   | Yes                                                                | Yes                                                              |  |  |  |

| Input capture fu                                       | nction   | Yes                                                                | Yes                                                              |  |  |  |

| Synchronous of                                         | peration | Yes                                                                | Yes                                                              |  |  |  |

| PWM mode                                               |          | Yes                                                                | Yes                                                              |  |  |  |

| Reset synchron mode                                    | ous PWM  | Yes                                                                | Yes                                                              |  |  |  |

| Complementary PWM mode                                 |          | Yes                                                                | Yes                                                              |  |  |  |

| Buffer function                                        |          | Yes                                                                | Yes                                                              |  |  |  |

| Interrupt source                                       | es       | Compare match/input capture A0<br>to D0<br>Overflow                | Compare match/input capture A1<br>to D1<br>Overflow<br>Underflow |  |  |  |

### Table 12.1 Timer Z Functions

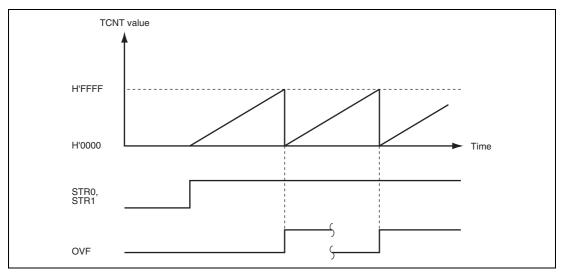

**Free-Running Count Operation and Periodic Count Operation:** Immediately after a reset, the TCNT counters for channels 0 and 1 are all designated as free-running counters. When the relevant bit in TSTR is set to 1, the corresponding TCNT counter starts an increment operation as a free-running counter. When TCNT overflows, the OVF flag in TSR is set to 1. If the value of the OVIE bit in the corresponding TIER is 1 at this point, timer Z requests an interrupt. After overflow, TCNT starts an increment operation again from H'0000.

Figure 12.8 illustrates free-running counter operation.

Figure 12.8 Free-Running Counter Operation

When compare match is selected as the TCNT clearing source, the TCNT counter for the relevant channel performs periodic count operation. The GR registers for setting the period are designated as output compare registers, and counter clearing by compare match is selected by means of bits CCLR1 and CCLR0 in TCR. After the settings have been made, TCNT starts an increment operation as a periodic counter when the corresponding bit in TSTR is set to 1. When the count value matches the value in GR, the IMFA, IMFB, IMFC, or IMFD flag in TSR is set to 1 and TCNT is cleared to H'0000.

If the value of the corresponding IMIEA, IMIEB, IMIEC, or IMIED bit in TIER is 1 at this point, the timer Z requests an interrupt. After a compare match, TCNT starts an increment operation again from H'0000.

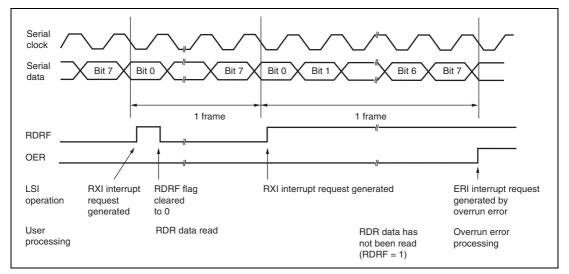

#### 14.5.4 Serial Data Reception (Clocked Synchronous Mode)

Figure 14.12 shows an example of SCI3 operation for reception in clocked synchronous mode. In serial reception, the SCI3 operates as described below.

- 1. The SCI3 performs internal initialization synchronous with a synchronization clock input or output, starts receiving data.

- 2. The SCI3 stores the receive data in RSR.

- 3. If an overrun error occurs (when reception of the next data is completed while the RDRF flag in SSR is still set to 1), the OER bit in SSR is set to 1. If the RIE bit in SCR3 is set to 1 at this time, an ERI interrupt request is generated, receive data is not transferred to RDR, and the RDRF flag remains to be set to 1.

- 4. If reception is completed successfully, the RDRF bit in SSR is set to 1, and receive data is transferred to RDR. If the RIE bit in SCR3 is set to 1 at this time, an RXI interrupt request is generated.

Figure 14.12 Example of SCI3 Reception in Clocked Synchronous Mode

Reception cannot be resumed while a receive error flag is set to 1. Accordingly, clear the OER, FER, PER, and RDRF bits to 0 before resuming reception. Figure 14.13 shows a sample flow chart for serial data reception.

|         |          | Initial |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|----------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit     | Bit Name | Value   | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4       | SOL      | 0       | R/W | Serial Data Output Level Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         |          |         |     | Although the value in the last bit of transmit data is<br>retained in the serial data output after the end of<br>transmission, the output level of serial data can be<br>changed by manipulating this bit before or after<br>transmission. When the output level is changed, the<br>SOLP bit should be cleared to 0 and the MOV instruction<br>should be used. If this bit is written during data transfer,<br>erroneous operation may occur. Therefore this bit must<br>not be manipulated during transmission. |

|         |          |         |     | 0: Shows serial data output level to low in reading.<br>Changes serial data output level to low in writing                                                                                                                                                                                                                                                                                                                                                                                                       |

|         |          |         |     | 1: Shows serial data output level to high in reading.<br>Changes serial data output level to high in writing                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3       | SOLP     | 1       | R/W | SOL Write Protect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         |          |         |     | When output level of serial data is changed, the MOV instruction is used to set the SOL bit to 1 and clear this bit to 0 or to clear the SOL bit and this bit to 0.                                                                                                                                                                                                                                                                                                                                              |

|         |          |         |     | 0: In writing, output level can be changed according to the value of the SOL bit.                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         |          |         |     | <ol> <li>In reading, this bit is always read as 1. In writing, it<br/>cannot be modified output level.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                |

| 2       | SCKS     | 0       | R/W | SSCK Pin Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         |          |         |     | Selects whether the SSCK pin functions as a port or a serial clock pin.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |          |         |     | 0: Functions as a port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         |          |         |     | 1: Functions as a serial clock pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1       | CSS1     | 0       | R/W | SCS Pin Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0       | CSS0     | 0       | R/W | Selects whether the $\overline{SCS}$ pin functions as a port, an $\overline{SCS}$ input, or $\overline{SCS}$ output. When the SSUMS bit in SSCRL is 0, the $\overline{SCS}$ pin functions as a port regardless of the setting of this bit.                                                                                                                                                                                                                                                                       |

|         |          |         |     | 00: Functions as a port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |          |         |     | 01: Functions as an SCS input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         |          |         |     | 1X: Functions as an $\overline{\text{SCS}}$ output (however, functions as an $\overline{\text{SCS}}$ input before starting transfer)                                                                                                                                                                                                                                                                                                                                                                             |

| [Leaend | 11       |         |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

[Legend]

X: Don't care.

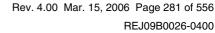

#### 16.4.4 Communication Modes and Pin Functions

The SSU switches functions of the input/output pin in each communication mode according to the settings of the MSS bit in SSCRH and the RE and TE bits in SSER. Figure 16.2 shows the relationship between communication modes and the input/output pins.

| Communication                    |       | egister S |     | Pin State |    |     |     |      |

|----------------------------------|-------|-----------|-----|-----------|----|-----|-----|------|

| Mode                             | SSUMS | BIDE      | MSS | TE        | RE | SSI | SSO | SSCK |

| Clocked                          | 0     | *         | 0   | 0         | 1  | In  | _   | In   |

| Synchronous<br>Communication     |       |           |     | 1         | 0  | _   | Out | In   |

| Mode                             |       |           |     |           | 1  | In  | Out | In   |

|                                  |       |           | 1   | 0         | 1  | In  | —   | Out  |

|                                  |       |           |     | 1         | 0  | _   | Out | Out  |

|                                  |       |           |     |           | 1  | In  | Out | Out  |

| Four-Line Bus                    | 1     | 0         | 0   | 0         | 1  | _   | In  | In   |

| Communication<br>Mode            |       |           |     | 1         | 0  | Out | _   | In   |

| Mode                             |       |           |     |           | 1  | Out | In  | In   |

|                                  |       |           | 1   | 0         | 1  | In  | _   | Out  |

|                                  |       |           |     | 1         | 0  | _   | Out | Out  |

|                                  |       |           |     |           | 1  | In  | Out | Out  |

| Four-Line Bus                    | 1     | 1         | 0   | 0         | 1  |     | In  | In   |

| (Bidirectional)<br>Communication |       |           |     | 1         | 0  |     | Out | In   |

| Mode                             |       |           | 1   | 0         | 1  |     | In  | Out  |

|                                  |       |           |     | 1         | 0  |     | Out | Out  |

| <b>Table 16.2</b> | <b>Relationship between</b> | Communication | Modes and | <b>Input/Output Pins</b> |

|-------------------|-----------------------------|---------------|-----------|--------------------------|

|-------------------|-----------------------------|---------------|-----------|--------------------------|

[Legend]

--: Can be used as a general I/O port.

Figure 16.11 Example of Operation in Data Transmission (MSS = 1)

RENESAS

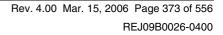

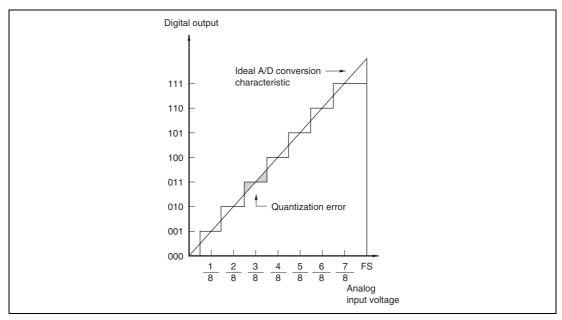

Figure 18.5 A/D Conversion Accuracy Definitions (2)

# Section 20 Power Supply Circuit

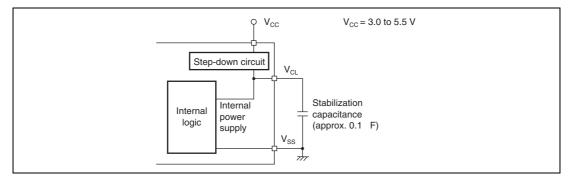

This LSI incorporates an internal power supply step-down circuit. Use of this circuit enables the internal power supply to be fixed at a constant level of approximately 3.0 V, independently of the voltage of the power supply connected to the external  $V_{cc}$  pin. As a result, the current consumed when an external power supply is used at 3.0 V or above can be held down to virtually the same low level as when used at approximately 3.0 V. If the external power supply is 3.0 V or below, the internal voltage will be practically the same as the external voltage. It is, of course, also possible to use the same level of external power supply voltage and internal power supply voltage without using the internal power supply step-down circuit.

## 20.1 When Using Internal Power Supply Step-Down Circuit

Connect the external power supply to the  $V_{cc}$  pin, and connect a capacitance of approximately 0.1  $\mu$ F between  $V_{cc}$  and  $V_{ss}$ , as shown in figure 20.1. The internal step-down circuit is made effective simply by adding this external circuit. In the external circuit interface, the external power supply voltage connected to  $V_{cc}$  and the GND potential connected to  $V_{ss}$  are the reference levels. For example, for port input/output levels, the  $V_{cc}$  level is the reference for the high level, and the  $V_{ss}$  level is that for the low level. The A/D converter analog power supply is not affected by the internal step-down circuit.

Figure 20.1 Power Supply Connection when Internal Step-Down Circuit is Used

|                         |                  | Applicable                                                                                                                                                                                     |                                                       |                 | Value | s    |                                         | Reference   |

|-------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------|-------|------|-----------------------------------------|-------------|

| Item                    | Symbol           |                                                                                                                                                                                                | Test Condition                                        | Min.            | Тур.  | Max. | Unit                                    | Figure      |

| RES pin low width       | t <sub>REL</sub> | RES                                                                                                                                                                                            | At power-on and in<br>modes other than<br>those below | t <sub>rc</sub> | _     | _    | ms                                      | Figure 22.2 |

|                         |                  |                                                                                                                                                                                                | In active mode and sleep mode operation               | 1500            |       | _    | ns                                      | _           |

| Input pin high<br>width | t <sub>in</sub>  | NMI,         IRQ0 to         IRQ3,         WKP0 to         WKP5,         TMCIV,         TMRIV,         TRGV,         ADTRG,         FTIOA0 to         FTIOD0,         FTIOA1 to         FTIOD1 |                                                       | 2               | _     | _    | t <sub>cyc</sub><br>t <sub>subcyc</sub> | Figure 22.3 |

| Input pin low<br>width  | t,L              | NMI,         IRQ0 to         IRQ3,         WKP0 to         WKP5,         TMCIV,         TRGV,         ADTRG,         FTIOA0 to         FTIOD0,         FTIOA1 to         FTIOD1                |                                                       | 2               |       | _    | t <sub>cyc</sub><br>t <sub>subcyc</sub> | -           |

Notes: 1. When an external clock is input, the minimum system clock oscillation frequency is 1.0 MHz.

2. Determined by the MA2, MA1, MA0, SA1, and SA0 bits in the system control register 2 (SYSCR2).

#### Table 22.13 DC Characteristics (2)

$V_{cc} = 2.7$  to 5.5 V,  $V_{ss} = 0.0$  V,  $T_a = -20$  to  $+75^{\circ}C$  (regular specifications) or  $T_a = -40$  to  $+85^{\circ}C$  (wide-range specifications), unless otherwise indicated.

|                                        |                           |                              |                             |      | Value | s    |      |

|----------------------------------------|---------------------------|------------------------------|-----------------------------|------|-------|------|------|

| Item                                   | Symbol                    | Applicable Pins              | Test Condition              | Min. | Тур.  | Max. | Unit |

| Allowable output low current (per pin) | I <sub>ol</sub>           | Output pins<br>except port 6 | $V_{\rm cc}$ = 4.0 to 5.5 V | _    | _     | 2.0  | mA   |

|                                        |                           | Port 6                       | -                           | _    | _     | 20.0 |      |

|                                        |                           | Output pins<br>except port 6 |                             | _    | _     | 0.5  | _    |

|                                        |                           | Port 6                       | -                           | _    | —     | 10.0 | _    |

| Allowable output low current (total)   | $\Sigma {\rm I}_{\rm OL}$ | Output pins<br>except port 6 | $V_{cc}$ = 4.0 to 5.5 V     | _    | _     | 40.0 | mA   |

|                                        |                           | Port 6                       | -                           | _    | _     | 80.0 |      |

|                                        |                           | Output pins<br>except port 6 |                             | _    | _     | 20.0 | _    |

|                                        |                           | Port 6                       | -                           | _    | —     | 40.0 | _    |

| Allowable output high                  | -I <sub>OH</sub>          | All output pins              | $V_{\rm cc}$ = 4.0 to 5.5 V | —    | —     | 2.0  | mA   |

| current (per pin)                      |                           |                              |                             | _    | _     | 0.2  |      |

| Allowable output high                  | $\Sigma  -I_{OH} $        | All output pins              | $V_{\rm cc}$ = 4.0 to 5.5 V | _    | _     | 30.0 | mA   |

| current (total)                        |                           |                              |                             |      |       | 8.0  |      |

### Table A.1 Instruction Set

#### 1. Data Transfer Instructions

|          |                        |              | Addressing Mode and<br>Instruction Length (bytes) |    |      |           |                                                                         |     |          |       | ) |                                                                                   |                |   |    |    |   |        | No. of<br>States <sup>*1</sup> |    |

|----------|------------------------|--------------|---------------------------------------------------|----|------|-----------|-------------------------------------------------------------------------|-----|----------|-------|---|-----------------------------------------------------------------------------------|----------------|---|----|----|---|--------|--------------------------------|----|

| Mnemonic |                        | Operand Size | #xx                                               | Rn | @ERn | @(d, ERn) | @-ERn/@ERn+                                                             | @aa | @(d, PC) | @ @aa | 1 | Operation                                                                         | Condition Code |   |    | v  | с | Normal | Advanced                       |    |

| MOV      | MOV.B #xx:8, Rd        | В            | 2                                                 |    |      |           |                                                                         |     |          |       |   | #xx:8 → Rd8                                                                       | -              | _ | \$ | \$ | 0 | _      | 2                              | 2  |

|          | MOV.B Rs, Rd           | В            |                                                   | 2  |      |           |                                                                         |     |          |       |   | $Rs8 \rightarrow Rd8$                                                             | _              | _ | \$ | \$ | 0 | —      | 2                              | 2  |

|          | MOV.B @ERs, Rd         | В            |                                                   |    | 2    |           |                                                                         |     |          |       |   | @ERs $\rightarrow$ Rd8                                                            | -              | — | \$ | \$ | 0 | —      | 4                              | ŀ  |

|          | MOV.B @(d:16, ERs), Rd | В            |                                                   |    |      | 4         |                                                                         |     |          |       |   | @(d:16, ERs) → Rd8                                                                | —              | - | \$ | \$ | 0 | —      | 6                              |    |

|          | MOV.B @(d:24, ERs), Rd | В            |                                                   |    |      | 8         |                                                                         |     |          |       |   | @(d:24, ERs) → Rd8                                                                | -              | — | \$ | \$ | 0 | —      | 1                              | 0  |

|          | MOV.B @ERs+, Rd        | в            |                                                   |    |      |           | 2                                                                       |     |          |       |   | @ERs → Rd8<br>ERs32+1 → ERs32                                                     | -              | — | \$ | \$ | 0 | -      | 6                              | ;  |

|          | MOV.B @aa:8, Rd        | В            |                                                   |    |      |           |                                                                         | 2   |          |       |   | @aa:8 $\rightarrow$ Rd8                                                           | —              | — | \$ | \$ | 0 | —      | 4                              | ł  |

|          | MOV.B @aa:16, Rd       | В            |                                                   |    |      |           |                                                                         | 4   |          |       |   | @aa:16 $\rightarrow$ Rd8                                                          | —              | — | \$ | \$ | 0 | —      | - 6                            |    |

|          | MOV.B @aa:24, Rd       | В            |                                                   |    |      |           |                                                                         | 6   |          |       |   | @aa:24 $\rightarrow$ Rd8                                                          | —              | — | \$ | \$ | 0 | —      | 8                              | 3  |

|          | MOV.B Rs, @ERd         | В            |                                                   |    | 2    |           |                                                                         |     |          |       |   | $Rs8 \rightarrow @ERd$                                                            | —              | — | \$ | \$ | 0 | —      | 4                              | ł  |

|          | MOV.B Rs, @(d:16, ERd) | В            |                                                   |    |      | 4         |                                                                         |     |          |       |   | Rs8 $\rightarrow$ @(d:16, ERd)                                                    | —              | — | \$ | \$ | 0 | —      | 6                              | ;  |

|          | MOV.B Rs, @(d:24, ERd) | В            |                                                   |    |      | 8         |                                                                         |     |          |       |   | $Rs8 \rightarrow @(d:24, ERd)$                                                    | —              | — | \$ | \$ | 0 | —      | 1                              | 0  |

|          | MOV.B Rs, @-ERd        | В            |                                                   |    |      |           | 2                                                                       |     |          |       |   | $\begin{array}{l} ERd32-1 \rightarrow ERd32 \\ Rs8 \rightarrow @ ERd \end{array}$ | —              | — | \$ | \$ | 0 | —      | 6                              | ;  |

|          | MOV.B Rs, @aa:8        | В            |                                                   |    |      |           |                                                                         | 2   |          |       |   | Rs8 $\rightarrow$ @aa:8                                                           | —              | — | \$ | \$ | 0 | —      | 4                              | ł  |

|          | MOV.B Rs, @aa:16       | В            |                                                   |    |      |           |                                                                         | 4   |          |       |   | Rs8 $\rightarrow$ @aa:16                                                          | —              | — | \$ | \$ | 0 | —      | 6                              | ;  |

|          | MOV.B Rs, @aa:24       | В            |                                                   |    |      |           |                                                                         | 6   |          |       |   | $Rs8 \rightarrow @aa:24$                                                          | —              | — | \$ | \$ | 0 | —      | 8                              | 3  |

|          | MOV.W #xx:16, Rd       | W            | 4                                                 |    |      |           |                                                                         |     |          |       |   | #xx:16 → Rd16                                                                     | —              | — | \$ | \$ | 0 | —      | 4                              | ł  |

|          | MOV.W Rs, Rd           | W            |                                                   | 2  |      |           |                                                                         |     |          |       |   | $Rs16 \rightarrow Rd16$                                                           | —              | — | \$ | \$ | 0 | —      | 2                              | 2  |

|          | MOV.W @ERs, Rd         | W            |                                                   |    | 2    |           |                                                                         |     |          |       |   | @ERs $\rightarrow$ Rd16                                                           | -              | — | \$ | \$ | 0 | —      | 4                              | ł  |

|          | MOV.W @(d:16, ERs), Rd | W            |                                                   |    |      | 4         |                                                                         |     |          |       |   | @(d:16, ERs) → Rd16                                                               | —              | — | \$ | \$ | 0 | —      | 6                              | \$ |

|          | MOV.W @(d:24, ERs), Rd | W            |                                                   |    |      | 8         |                                                                         |     |          |       |   | @(d:24, ERs) → Rd16                                                               | -              | — | \$ | \$ | 0 | —      | 1                              | 0  |

|          | MOV.W @ERs+, Rd        | w            |                                                   |    |      |           | 2                                                                       |     |          |       |   | @ERs → Rd16<br>ERs32+2 → @ERd32                                                   | -              | — | \$ | \$ | 0 | -      | 6                              | i  |

|          | MOV.W @aa:16, Rd       | W            |                                                   |    |      |           |                                                                         | 4   |          |       |   | @aa:16 $\rightarrow$ Rd16                                                         | —              | — | \$ | \$ | 0 | —      | e                              | ;  |

|          | MOV.W @aa:24, Rd       | W            |                                                   |    |      |           |                                                                         | 6   |          |       |   | @aa:24 $\rightarrow$ Rd16                                                         | -              | — | \$ | \$ | 0 | —      | 8                              | ;  |

|          | MOV.W Rs, @ERd         | W            |                                                   |    | 2    |           |                                                                         |     |          |       |   | $Rs16 \rightarrow @ERd$                                                           | —              | — | \$ | \$ | 0 | —      | 4                              | ł  |

|          | MOV.W Rs, @(d:16, ERd) | W            |                                                   |    |      | 4         |                                                                         |     |          |       |   | $Rs16 \rightarrow @(d:16, ERd)$                                                   | —              | - | \$ | \$ | 0 | —      | 6                              | ;  |

|          | MOV.W Rs, @(d:24, ERd) | W            |                                                   |    |      | 8         | 8 Rs16 $\rightarrow$ @(d:24, ERd) $  \updownarrow$ $\updownarrow$ 0 $-$ |     | 1        | 0     |   |                                                                                   |                |   |    |    |   |        |                                |    |