#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                      |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20MHz                                                                        |

| Connectivity               | CANbus, SCI, SSU                                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                           |

| Number of I/O              | 45                                                                           |

| Program Memory Size        | 56KB (56K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 3K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-LQFP                                                                      |

| Supplier Device Package    | 64-LFQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36037gfzv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Preface

The H8/36057 Group and H8/36037 Group are single-chip microcomputers made up of the high-speed H8/300H CPU employing Renesas Technology-original architecture as their cores, and the peripheral functions required to configure a system. The H8/300H CPU has an instruction set that is compatible with the H8/300 CPU.

- Target Users: This manual was written for users who will be using the H8/36057 Group and H8/36037 Group in the design of application systems. Target users are expected to understand the fundamentals of electrical circuits, logical circuits, and microcomputers.

- Objective: This manual was written to explain the hardware functions and electrical characteristics of the H8/36057 Group and H8/36037 Group to the target users. Refer to the H8/300H Series Software Manual for a detailed description of the instruction set.

Notes on reading this manual:

- In order to understand the overall functions of the chip Read the manual according to the contents. This manual can be roughly categorized into parts on the CPU, system control functions, peripheral functions, and electrical characteristics.

- In order to understand the details of the CPU's functions Read the H8/300H Series Software Manual.

- In order to understand the details of a register when its name is known Read the index that is the final part of the manual to find the page number of the entry on the register. The addresses, bits, and initial values of the registers are summarized in section 21, List of Registers.

| Example: | Register name: | The following notation is used for cases when the same or a similar function, e.g. serial communication interface, is |

|----------|----------------|-----------------------------------------------------------------------------------------------------------------------|

|          |                | implemented on more than one channel:                                                                                 |

|          |                | XXX_N (XXX is the register name and N is the channel                                                                  |

|          |                | number)                                                                                                               |

|          | Bit order:     | The MSB is on the left and the LSB is on the right.                                                                   |

### Section 12 Timer Z

| Figure 12.1  | Timer Z Block Diagram                                                   | 165 |

|--------------|-------------------------------------------------------------------------|-----|

| Figure 12.2  | Timer Z (Channel 0) Block Diagram                                       | 166 |

| Figure 12.3  | Timer Z (Channel 1) Block Diagram                                       | 167 |

| Figure 12.4  | Example of Outputs in Reset Synchronous PWM Mode and Complementary      |     |

|              | PWM Mode                                                                | 174 |

| Figure 12.5  | Accessing Operation of 16-Bit Register (between CPU and TCNT (16 Bits)) | 186 |

| Figure 12.6  | Accessing Operation of 8-Bit Register (between CPU and TSTR (8 Bits))   | 186 |

| Figure 12.7  | Example of Counter Operation Setting Procedure                          | 187 |

| Figure 12.8  | Free-Running Counter Operation                                          | 188 |

| Figure 12.9  | Periodic Counter Operation                                              | 189 |

| Figure 12.10 | Count Timing at Internal Clock Operation                                | 189 |

| Figure 12.11 | Count Timing at External Clock Operation (Both Edges Detected)          | 190 |

| Figure 12.12 | Example of Setting Procedure for Waveform Output by Compare Match       | 191 |

| Figure 12.13 | Example of 0 Output/1 Output Operation                                  | 192 |

| Figure 12.14 | Example of Toggle Output Operation                                      | 193 |

| Figure 12.15 | Output Compare Timing                                                   | 194 |

| Figure 12.16 | Example of Input Capture Operation Setting Procedure                    | 195 |

| Figure 12.17 | Example of Input Capture Operation                                      | 196 |

| Figure 12.18 | Input Capture Signal Timing                                             | 197 |

| Figure 12.19 | Example of Synchronous Operation Setting Procedure                      | 198 |

| Figure 12.20 | Example of Synchronous Operation                                        | 199 |

| Figure 12.21 | Example of PWM Mode Setting Procedure                                   | 201 |

| Figure 12.22 | Example of PWM Mode Operation (1)                                       | 202 |

| Figure 12.23 | Example of PWM Mode Operation (2)                                       |     |

| Figure 12.24 | Example of PWM Mode Operation (3)                                       | 204 |

| Figure 12.25 |                                                                         |     |

| Figure 12.26 |                                                                         |     |

| Figure 12.27 | Example of Reset Synchronous PWM Mode Operation (OLS0 = OLS1 = 1)       | 208 |

| Figure 12.28 |                                                                         |     |

| Figure 12.29 |                                                                         |     |

| Figure 12.30 | Canceling Procedure of Complementary PWM Mode                           |     |

| Figure 12.31 | Example of Complementary PWM Mode Operation (1)                         | 214 |

| Figure 12.32 | (1) Example of Complementary PWM Mode Operation                         |     |

| -            | (TPSC2 = TPSC1 = TPSC0 = 0) (2)                                         | 216 |

| Figure 12.32 | (2) Example of Complementary PWM Mode Operation                         |     |

| -            | (Other than $TPSC2 = TPSC1 = TPSC0$ ) (3)                               | 217 |

| Figure 12.33 | Timing of Overshooting                                                  |     |

| -            | Timing of Undershooting                                                 |     |

| -            | Compare Match Buffer Operation                                          |     |

| -            |                                                                         |     |

Rev. 4.00 Mar. 15, 2006 Page xxiii of xxxii

# RENESAS

#### BCLR instruction executed

BCLR #0, @PCR5

The BCLR instruction is executed for PCR5.

| • | After executing | BCLR | instruction |

|---|-----------------|------|-------------|

|---|-----------------|------|-------------|

|              | P57          | P56           | P55          | P54          | P53          | P52          | P51          | P50           |

|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Input/output | Output       | Output        | Output       | Output       | Output       | Output       | Output       | Input         |

| Pin state    | Low<br>level | High<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | High<br>level |

| PCR5         | 1            | 1             | 1            | 1            | 1            | 1            | 1            | 0             |

| PDR5         | 1            | 0             | 0            | 0            | 0            | 0            | 0            | 0             |

- Description on operation

- 1. When the BCLR instruction is executed, first the CPU reads PCR5. Since PCR5 is a write-only register, the CPU reads a value of H'FF, even though the PCR5 value is actually H'3F.

- 2. Next, the CPU clears bit 0 in the read data to 0, changing the data to H'FE.

- 3. Finally, H'FE is written to PCR5 and BCLR instruction execution ends.

As a result of this operation, bit 0 in PCR5 becomes 0, making P50 an input port. However, bits 7 and 6 in PCR5 change to 1, so that P57 and P56 change from input pins to output pins. To prevent this problem, store a copy of the PDR5 data in a work area in memory and manipulate data of the bit in the work area, then write this data to PDR5.

#### • Prior to executing BCLR instruction

| MOV.B | #3F, | ROL   |

|-------|------|-------|

| MOV.B | ROL, | @RAM0 |

| MOV.B | ROL, | @PCR5 |

The PCR5 value (H'3F) is written to a work area in memory (RAM0) as well as to PCR5.

|              | P57          | P56           | P55          | P54          | P53          | P52          | P51          | P50          |

|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Input/output | Input        | Input         | Output       | Output       | Output       | Output       | Output       | Output       |

| Pin state    | Low<br>level | High<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level |

| PCR5         | 0            | 0             | 1            | 1            | 1            | 1            | 1            | 1            |

| PDR5         | 1            | 0             | 0            | 0            | 0            | 0            | 0            | 0            |

| RAM0         | 0            | 0             | 1            | 1            | 1            | 1            | 1            | 1            |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                              |

|-----|----------|------------------|-----|----------------------------------------------------------------------------------------------------------|

| 3   | IRRI3    | 0                | R/W | IRQ3 Interrupt Request Flag                                                                              |

|     |          |                  |     | [Setting condition]                                                                                      |

|     |          |                  |     | When $\overline{IRQ3}$ pin is designated for interrupt input and the designated signal edge is detected. |

|     |          |                  |     | [Clearing condition]                                                                                     |

|     |          |                  |     | When IRRI3 is cleared by writing 0                                                                       |

| 2   | IRRI2    | 0                | R/W | IRQ2 Interrupt Request Flag                                                                              |

|     |          |                  |     | [Setting condition]                                                                                      |

|     |          |                  |     | When IRQ2 pin is designated for interrupt input and the designated signal edge is detected.              |

|     |          |                  |     | [Clearing condition]                                                                                     |

|     |          |                  |     | When IRRI2 is cleared by writing 0                                                                       |

| 1   | IRRI1    | 0                | R/W | IRQ1 Interrupt Request Flag                                                                              |

|     |          |                  |     | [Setting condition]                                                                                      |

|     |          |                  |     | When IRQ1 pin is designated for interrupt input and the designated signal edge is detected.              |

|     |          |                  |     | [Clearing condition]                                                                                     |

|     |          |                  |     | When IRRI1 is cleared by writing 0                                                                       |

| 0   | IRRI0    | 0                | R/W | IRQ0 Interrupt Request Flag                                                                              |

|     |          |                  |     | [Setting condition]                                                                                      |

|     |          |                  |     | When IRQ0 pin is designated for interrupt input and the designated signal edge is detected.              |

|     |          |                  |     | [Clearing condition]                                                                                     |

|     |          |                  |     | When IRRI0 is cleared by writing 0                                                                       |

# 3.3 Reset Exception Handling

When the  $\overline{\text{RES}}$  pin goes low, all processing halts and this LSI enters the reset. The internal state of the CPU and the registers of the on-chip peripheral modules are initialized by the reset. To ensure that this LSI is reset at power-up, hold the  $\overline{\text{RES}}$  pin low until the clock pulse generator output stabilizes. To reset the chip during operation, hold the  $\overline{\text{RES}}$  pin low for at least 10 system clock cycles. When the  $\overline{\text{RES}}$  pin goes high after being held low for the necessary time, this LSI starts reset exception handling. The reset exception handling sequence is shown in figure 3.1. However, for the reset exception handling sequence of the product with on-chip power-on reset circuit, refer to section 19, Power-On Reset and Low-Voltage Detection Circuits (Optional).

The reset exception handling sequence is as follows:

- 1. Set the I bit in the condition code register (CCR) to 1.

- 2. The CPU generates a reset exception handling vector address (from H'0000 to H'0001), the data in that address is sent to the program counter (PC) as the start address, and program execution starts from that address.

The FLMCR1, FLMCR2, and EBR1 settings are retained, however program mode or erase mode is aborted at the point at which the error occurred. Program mode or erase mode cannot be reentered by re-setting the P or E bit. However, PV and EV bit settings are retained, and a transition can be made to verify mode. Error protection can be cleared only by a power-on reset.

## 7.6 Programmer Mode

In programmer mode, a PROM programmer can be used to perform programming/erasing via a socket adapter, just as a discrete flash memory. Use a PROM programmer that supports the MCU device type with the on-chip 64-kbyte flash memory (FZTAT64V5).

### 7.7 Power-Down States for Flash Memory

In user mode, the flash memory will operate in either of the following states:

• Normal operating mode

The flash memory can be read and written to at high speed.

• Power-down operating mode

The power supply circuit of flash memory can be partly halted. As a result, flash memory can be read with low power consumption.

Standby mode

All flash memory circuits are halted.

Table 7.7 shows the correspondence between the operating modes of this LSI and the flash memory. In subactive mode, the flash memory can be set to operate in power-down mode with the PDWND bit in FLPWCR. When the flash memory returns to its normal operating state from power-down mode or standby mode, a period to stabilize operation of the power supply circuits that were stopped is needed. When the flash memory returns to its normal operating state, bits STS2 to STS0 in SYSCR1 must be set to provide a wait time of at least 20 µs, even when the external clock is being used.

### • P22/TXD pin

| Register      | PMR1 | PCR2  |                |

|---------------|------|-------|----------------|

| Bit Name      | TXD  | PCR22 | Pin Function   |

| Setting Value | 0    | 0     | P22 input pin  |

|               |      | 1     | P22 output pin |

|               | 1    | Х     | TXD output pin |

# [Legend]

X: Don't care.

#### • P21/RXD pin

| Register      | SCR3 | PCR2  |                |

|---------------|------|-------|----------------|

| Bit Name      | RE   | PCR21 | Pin Function   |

| Setting Value | 0    | 0     | P21 input pin  |

|               |      | 1     | P21 output pin |

|               | 1    | Х     | RXD input pin  |

### [Legend]

X: Don't care.

#### • P20/SCK3 pin

| Register      | SCR3 |      | SMR | PCR2  |                 |

|---------------|------|------|-----|-------|-----------------|

| Bit Name      | CKE1 | CKE0 | СОМ | PCR20 | Pin Function    |

| Setting Value | 0    | 0    | 0   | 0     | P20 input pin   |

|               |      |      |     | 1     | P20 output pin  |

|               | 0    | 0    | 1   | Х     | SCK3 output pin |

|               | 0    | 1    | Х   | Х     | SCK3 output pin |

|               | 1    | Х    | Х   | Х     | SCK3 input pin  |

[Legend]

X: Don't care.

### 9.6.2 Port Data Register 8 (PDR8)

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                               |

|--------|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | P87      | 0                | R/W | PDR8 stores output data for port 8 pins.                                                                                                  |

| 6      | P86      | 0                | R/W | If PDR8 is read while PCR8 bits are set to 1, the value                                                                                   |

| 5      | P85      | 0                | R/W | stored in PDR8 is read. If PDR8 is read while PCR8 bits are cleared to 0, the pin states are read regardless of the value stored in PDR8. |

| 4 to 0 | _        | All 1            |     | Reserved                                                                                                                                  |

|        |          |                  |     | These bits are always read as 1.                                                                                                          |

PDR8 is a general I/O port data register of port 8.

#### 9.6.3 Pin Functions

The correspondence between the register specification and the port functions is shown below.

• P87 pin

| Register      | PCR8  |                |

|---------------|-------|----------------|

| Bit Name      | PCR87 | Pin Function   |

| Setting Value | 0     | P87 input pin  |

|               | 1     | P87 output pin |

• P86 pin

| Register      | PCR8  |                |

|---------------|-------|----------------|

| Bit Name      | PCR86 | Pin Function   |

| Setting Value | 0     | P86 input pin  |

|               | 1     | P86 output pin |

• P85 pin

| Register F      |       |                |

|-----------------|-------|----------------|

| Bit Name        | PCR85 | Pin Function   |

| Setting Value ( | 0     | P85 input pin  |

|                 | 1     | P85 output pin |

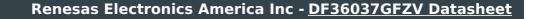

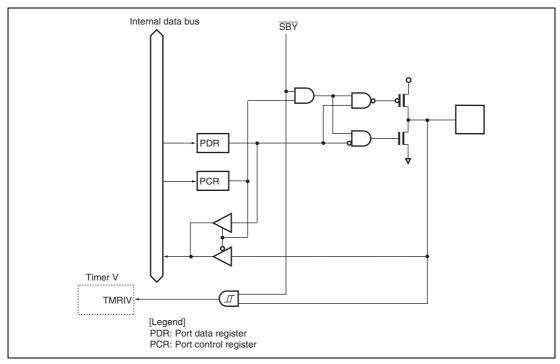

Figure 11.1 Block Diagram of Timer V

| Bit | Bit Name | Initial<br>value | R/W | Description                                                |

|-----|----------|------------------|-----|------------------------------------------------------------|

| 2   | IOC2     | 0                | R/W | I/O Control C2 to C0                                       |

| 1   | IOC1     | 0                | R/W | GRC is an output compare register:                         |

| 0   | IOC0     | 0                | R/W | 000: Disables pin output by compare match                  |

|     |          |                  |     | 001: 0 output by GRC compare match                         |

|     |          |                  |     | 010: 1 output by GRC compare match                         |

|     |          |                  |     | 011: Toggle Output by GRC compare match                    |

|     |          |                  |     | GRC is an input capture register:                          |

|     |          |                  |     | 100: Input capture to GRC at the rising edge               |

|     |          |                  |     | 101: Input capture to GRC at the falling edge              |

|     |          |                  |     | 11X: Input capture to GRC at both rising and falling edges |

[Legend]

X: Don't care

#### 12.3.11 Timer Status Register (TSR)

TSR indicates generation of an overflow/underflow of TCNT and a compare match/input capture of GRA, GRB, GRC, and GRD. These flags are interrupt sources. If an interrupt is enabled by a corresponding bit in TIER, TSR requests an interrupt for the CPU. Timer Z has two TSR registers, one for each channel.

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                      |

|------|----------|------------------|-----|--------------------------------------------------|

| 7, 6 | _        | All 1            | _   | Reserved                                         |

|      |          |                  |     | These bits are always read as 1.                 |

| 5    | UDF*     | 0                | R/W | Underflow Flag                                   |

|      |          |                  |     | [Setting condition]                              |

|      |          |                  |     | When TCNT_1 underflows                           |

|      |          |                  |     | [Clearing condition]                             |

|      |          |                  |     | • When 0 is written to UDF after reading UDF = 1 |

| 4    | OVF      | 0                | R/W | Overflow Flag                                    |

|      |          |                  |     | [Setting condition]                              |

|      |          |                  |     | When the TCNT value underflows                   |

|      |          |                  |     | [Clearing condition]                             |

|      |          |                  |     | • When 0 is written to OVF after reading OVF = 1 |

|      |          |                  |     | [Clearing condition]                             |

RENESAS

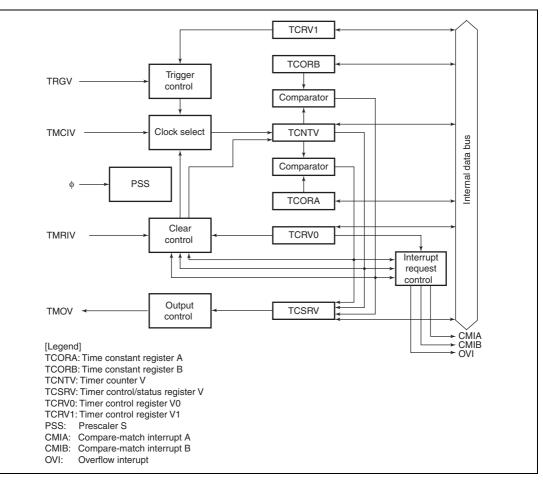

Figure 12.24 Example of PWM Mode Operation (3)

RENESAS

### 12.4.7 Complementary PWM Mode

Three PWM waveforms for non-overlapped normal and counter phases are output by combining channels 0 and 1.

In complementary PWM mode, the FTIOB0 to FTIOD0 and FTIOA1 to FTIOD1 pins become PWM-output pins automatically. TCNT\_0 and TCNT\_1 perform an increment or decrement operation. Tables 12.6 and 12.7 show the output pins and register settings in complementary PWM mode, respectively.

Figure 12.29 shows the example of complementary PWM mode setting procedure.

| Channel | Pin Name | I/O    | Pin Function                                                           |

|---------|----------|--------|------------------------------------------------------------------------|

| 0       | FTIOC0   | Output | Toggle output in synchronous with PWM cycle                            |

| 0       | FTIOB0   | Output | PWM output 1                                                           |

| 0       | FTIOD0   | Output | PWM output 1 (counter-phase waveform non-overlapped with PWM output 1) |

| 1       | FTIOA1   | Output | PWM output 2                                                           |

| 1       | FTIOC1   | Output | PWM output 2 (counter-phase waveform non-overlapped with PWM output 2) |

| 1       | FTIOB1   | Output | PWM output 3                                                           |

| 1       | FTIOD1   | Output | PWM output 3 (counter-phase waveform non-overlapped with PWM output 3) |

Table 12.6

Output Pins in Complementary PWM Mode

#### 14.3.1 Receive Shift Register (RSR)

RSR is a shift register that is used to receive serial data input from the RXD pin and convert it into parallel data. When one frame of data has been received, it is transferred to RDR automatically. RSR cannot be directly accessed by the CPU.

#### 14.3.2 Receive Data Register (RDR)

RDR is an 8-bit register that stores received data. When the SCI3 has received one frame of serial data, it transfers the received serial data from RSR to RDR, where it is stored. After this, RSR is receive-enabled. As RSR and RDR function as a double buffer in this way, continuous receive operations are possible. After confirming that the RDRF bit in SSR is set to 1, read RDR only once. RDR cannot be written to by the CPU. RDR is initialized to H'00.

### 14.3.3 Transmit Shift Register (TSR)

TSR is a shift register that transmits serial data. To perform serial data transmission, the SCI3 first transfers transmit data from TDR to TSR automatically, then sends the data that starts from the LSB to the TXD pin. TSR cannot be directly accessed by the CPU.

#### 14.3.4 Transmit Data Register (TDR)

TDR is an 8-bit register that stores data for transmission. When the SCI3 detects that TSR is empty, it transfers the transmit data written in TDR to TSR and starts transmission. The doublebuffered structure of TDR and TSR enables continuous serial transmission. If the next transmit data has already been written to TDR during transmission of one-frame data, the SCI3 transfers the written data to TSR to continue transmission. To achieve reliable serial transmission, write transmit data to TDR only once after confirming that the TDRE bit in SSR is set to 1. TDR is initialized to H'FF.

#### 14.3.7 Serial Status Register (SSR)

SSR is a register containing status flags of the SCI3 and multiprocessor bits for transfer. 1 cannot be written to flags TDRE, RDRF, OER, PER, and FER; they can only be cleared.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                            |

|-----|----------|------------------|-----|----------------------------------------------------------------------------------------|

| 7   | TDRE     | 1                | R/W | Transmit Data Register Empty                                                           |

|     |          |                  |     | Indicates whether TDR contains transmit data.                                          |

|     |          |                  |     | [Setting conditions]                                                                   |

|     |          |                  |     | • When the TE bit in SCR3 is 0                                                         |

|     |          |                  |     | When data is transferred from TDR to TSR                                               |

|     |          |                  |     | [Clearing conditions]                                                                  |

|     |          |                  |     | • When 0 is written to TDRE after reading TDRE = 1                                     |

|     |          |                  |     | When the transmit data is written to TDR                                               |

| 6   | RDRF     | 0                | R/W | Receive Data Register Full                                                             |

|     |          |                  |     | Indicates that the received data is stored in RDR.                                     |

|     |          |                  |     | [Setting condition]                                                                    |

|     |          |                  |     | When serial reception ends normally and receive data<br>is transferred from RSR to RDR |

|     |          |                  |     | [Clearing conditions]                                                                  |

|     |          |                  |     | • When 0 is written to RDRF after reading RDRF = 1                                     |

|     |          |                  |     | When data is read from RDR                                                             |

| 5   | OER      | 0                | R/W | Overrun Error                                                                          |

|     |          |                  |     | [Setting condition]                                                                    |

|     |          |                  |     | When an overrun error occurs in reception                                              |

|     |          |                  |     | [Clearing condition]                                                                   |

|     |          |                  |     | • When 0 is written to OER after reading OER = 1                                       |

| 4   | FER      | 0                | R/W | Framing Error                                                                          |

|     |          |                  |     | [Setting condition]                                                                    |

|     |          |                  |     | When a framing error occurs in reception                                               |

|     |          |                  |     | [Clearing condition]                                                                   |

|     |          |                  |     | • When 0 is written to FER after reading FER = 1                                       |

### 15.5.3 Message Transmission

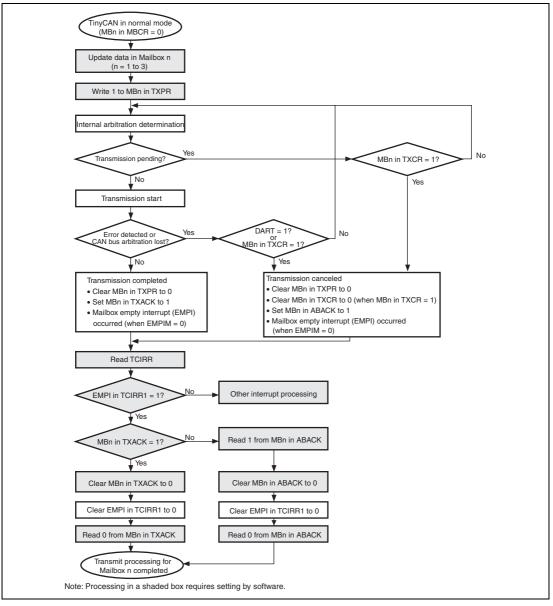

Message Transmission Request: Figure 15.6 shows a transmission flowchart.

Figure 15.6 Transmission Request Flowchart

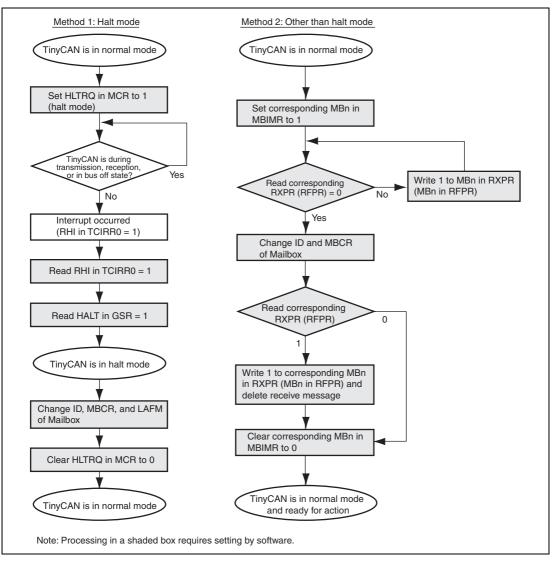

Figure 15.17 Flowchart for Changing ID, MBCR, and LAFM of Receive Mailbox

### 16.4.11 Interrupt Requests

The SSU has five interrupt requests: transmit data empty, transmit end, receive data full, overrun error, and conflict error. Since these interrupt requests are assigned to the common vector address, interrupt sources must be determined by flags. Table 16.3 lists the interrupt requests.

#### Table 16.3 Interrupt Requests

| Interrupt Request   | Abbreviation | Interrupt Condition    |

|---------------------|--------------|------------------------|

| Transmit data empty | ТХІ          | (TIE = 1), (TDRE = 1)  |

| Transmit end        | TEI          | (TEIE = 1), (TEND = 1) |

| Receive data full   | RXI          | (RIE = 1), (RDRF = 1)  |

| Overrun error       | OEI          | (RIE = 1), (ORER = 1)  |

| Conflict error      | CEI          | (CEIE = 1), (CE = 1)   |

When an interrupt condition shown in table 16.3 is 1 and the I bit in CCR is 0, the CPU executes the interrupt exception handling. Each interrupt source must be cleared during the exception handling. Note that the TDRE and TEND bits are automatically cleared by writing transmit data in SSTDR and the RDRF bit is automatically cleared by reading SSRDR. When transmit data is written in SSTDR, the TDRE bit is set again at the same time. Then if the TDRE bit is cleared, additional one byte of data may be transmitted.

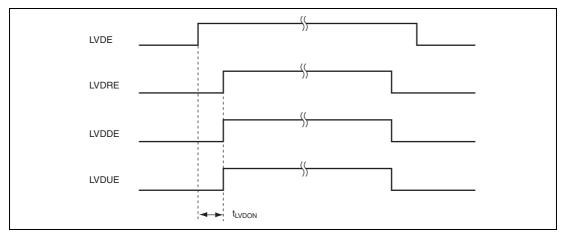

### Procedures for Clearing Settings when Using LVDR and LVDI:

To operate or release the low-voltage detection circuit normally, follow the procedure described below. Figure 19.5 shows the timing for the operation and release of the low-voltage detection circuit.

- 1. To operate the low-voltage detection circuit, set the LVDE bit in LVDCR to 1.

- 2. Wait for 50  $\mu$ s (t<sub>LVDON</sub>) until the reference voltage and the low-voltage-detection power supply have stabilized by a software timer, etc. Then, clear the LVDDF and LVDUF bits in LVDSR to 0 and set the LVDRE, LVDDE, and LVDUE bits in LVDCR to 1, as required.

- 3. To release the low-voltage detection circuit, start by clearing all of the LVDRE, LVDDE, and LVDUE bits to 0. Then clear the LVDE bit to 0. The LVDE bit must not be cleared to 0 at the same timing as the LVDRE, LVDDE, and LVDUE bits because incorrect operation may occur.

Figure 19.5 Timing for Operation/Release of Low-Voltage Detection Circuit

|     |            |              | Addressing Mode and<br>Instruction Length (bytes) |    |     |           |            |     |          |     | ) |                                                  |                |   |   |   |   | No. of<br>States <sup>*1</sup> |          |    |

|-----|------------|--------------|---------------------------------------------------|----|-----|-----------|------------|-----|----------|-----|---|--------------------------------------------------|----------------|---|---|---|---|--------------------------------|----------|----|

|     |            | Operand Size | ×                                                 |    | ERn | @(d, ERn) | -ERn/@ERn+ | @aa | @(d, PC) | @aa |   | Operation                                        | Condition Code |   |   |   |   | Normal                         | Advanced |    |

|     |            | ő            | XX#                                               | Rn | 0   | 0         | 0          | 0   | 0        | 0   | Ι |                                                  | I              | н | N | z | ۷ | С                              | Ň        | ¥  |

| JMP | JMP @ERn   | —            |                                                   |    | 2   |           |            |     |          |     |   | $PC \gets ERn$                                   | -              | - | - | — | — | —                              | 4        | 4  |

|     | JMP @aa:24 | —            |                                                   |    |     |           |            | 4   |          |     |   | PC ← aa:24                                       | -              | - | - | — | — | —                              | (        | 6  |

|     | JMP @@aa:8 |              |                                                   |    |     |           |            |     |          | 2   |   | PC ← @aa:8                                       | —              | - | - | — | — | —                              | 8        | 10 |

| BSR | BSR d:8    | -            |                                                   |    |     |           |            |     | 2        |     |   | $PC \rightarrow @-SP$<br>$PC \leftarrow PC+d:8$  | -              | - | - | — | — | —                              | 6        | 8  |

|     | BSR d:16   | -            |                                                   |    |     |           |            |     | 4        |     |   | $PC \rightarrow @-SP$<br>$PC \leftarrow PC+d:16$ | -              | - | - | - | — | —                              | 8        | 10 |

| JSR | JSR @ERn   | -            |                                                   |    | 2   |           |            |     |          |     |   | $PC \rightarrow @-SP$<br>$PC \leftarrow ERn$     | -              | - | - | - | — | —                              | 6        | 8  |

|     | JSR @aa:24 | -            |                                                   |    |     |           |            | 4   |          |     |   | $PC \rightarrow @-SP$<br>$PC \leftarrow aa:24$   | -              | - | - | — | - | —                              | 8        | 10 |

|     | JSR @@aa:8 | -            |                                                   |    |     |           |            |     |          | 2   |   | $PC \rightarrow @-SP$<br>$PC \leftarrow @aa:8$   | -              | - | - | - | - | —                              | 8        | 12 |

| RTS | RTS        | _            |                                                   |    |     |           |            |     |          |     | 2 | $PC \leftarrow @SP+$                             | -              | - | - | - | - | -                              | 8        | 10 |

Figure B.15 Port 7 Block Diagram (P74)