#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                     |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 20MHz                                                                       |

| Connectivity               | CANbus, SCI, SSU                                                            |

| Peripherals                | LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 45                                                                          |

| Program Memory Size        | 56KB (56K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | ·                                                                           |

| RAM Size                   | 3K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-BQFP                                                                     |

| Supplier Device Package    | 64-QFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36037ghv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Keep safety first in your circuit designs!

Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any thirdparty's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

|         | 19.3.1                     | Power-On Reset Circuit                                            |     |  |  |  |  |  |

|---------|----------------------------|-------------------------------------------------------------------|-----|--|--|--|--|--|

|         | 19.3.2                     | Low-Voltage Detection Circuit                                     |     |  |  |  |  |  |

|         |                            | -                                                                 |     |  |  |  |  |  |

| Sectio  | on 20                      | Power Supply Circuit                                              |     |  |  |  |  |  |

| 20.1    |                            | Using Internal Power Supply Step-Down Circuit                     |     |  |  |  |  |  |

| 20.2    | When I                     | Not Using Internal Power Supply Step-Down Circuit                 |     |  |  |  |  |  |

|         |                            |                                                                   |     |  |  |  |  |  |

| Sectio  | on 21                      | List of Registers                                                 |     |  |  |  |  |  |

| 21.1    | Registe                    | er Addresses (Address Order)                                      |     |  |  |  |  |  |

| 21.2    | Registe                    | er Bits                                                           |     |  |  |  |  |  |

| 21.3    | Registe                    | er States in Each Operating Mode                                  |     |  |  |  |  |  |

|         |                            |                                                                   |     |  |  |  |  |  |

| Section |                            | Electrical Characteristics                                        |     |  |  |  |  |  |

| 22.1    |                            | te Maximum Ratings                                                |     |  |  |  |  |  |

| 22.2    | Electri                    | cal Characteristics (F-ZTAT <sup>™</sup> Version)                 |     |  |  |  |  |  |

|         | 22.2.1                     | Power Supply Voltage and Operating Ranges                         |     |  |  |  |  |  |

|         | 22.2.2                     | DC Characteristics                                                |     |  |  |  |  |  |

|         | 22.2.3                     | AC Characteristics                                                |     |  |  |  |  |  |

|         | 22.2.4                     | A/D Converter Characteristics                                     | 456 |  |  |  |  |  |

|         | 22.2.5                     | Watchdog Timer Characteristics                                    |     |  |  |  |  |  |

|         | 22.2.6                     | Flash Memory Characteristics                                      |     |  |  |  |  |  |

|         | 22.2.7                     | Power-Supply-Voltage Detection Circuit Characteristics (Optional) |     |  |  |  |  |  |

|         | 22.2.8                     | Power-On Reset Circuit Characteristics (Optional)                 |     |  |  |  |  |  |

| 22.3    | Electri                    | cal Characteristics (Masked ROM Version)                          |     |  |  |  |  |  |

|         | 22.3.1                     | Power Supply Voltage and Operating Ranges                         |     |  |  |  |  |  |

|         | 22.3.2                     | DC Characteristics                                                |     |  |  |  |  |  |

|         | 22.3.3                     | AC Characteristics                                                |     |  |  |  |  |  |

|         | 22.3.4                     | A/D Converter Characteristics                                     |     |  |  |  |  |  |

|         | 22.3.5                     | Watchdog Timer Characteristics                                    |     |  |  |  |  |  |

|         | 22.3.6                     | Power-Supply-Voltage Detection Circuit Characteristics (Optional) | 477 |  |  |  |  |  |

|         | 22.3.7                     | Power-On Reset Circuit Characteristics (Optional)                 |     |  |  |  |  |  |

| 22.4    | Operat                     | ion Timing                                                        |     |  |  |  |  |  |

| 22.5    | Output                     | Load Condition                                                    |     |  |  |  |  |  |

|         |                            |                                                                   |     |  |  |  |  |  |

| Appe    | ndix A                     | Instruction Set                                                   |     |  |  |  |  |  |

| A.1     | Instruc                    | tion List                                                         |     |  |  |  |  |  |

| A.2     | Operat                     | ion Code Map                                                      | 502 |  |  |  |  |  |

| A.3     | Number of Execution States |                                                                   |     |  |  |  |  |  |

| A.4     | Combi                      | nations of Instructions and Addressing Modes                      |     |  |  |  |  |  |

|         |                            |                                                                   |     |  |  |  |  |  |

# Section 2 CPU

This LSI has an H8/300H CPU with an internal 32-bit architecture that is upward-compatible with the H8/300CPU, and supports only normal mode, which has a 64-kbyte address space.

- Upward-compatible with H8/300 CPUs

- Can execute H8/300 CPUs object programs

- Additional eight 16-bit extended registers

- 32-bit transfer and arithmetic and logic instructions are added

- Signed multiply and divide instructions are added.

- General-register architecture

- Sixteen 16-bit general registers also usable as sixteen 8-bit registers and eight 16-bit registers, or eight 32-bit registers

- Sixty-two basic instructions

- 8/16/32-bit data transfer and arithmetic and logic instructions

- Multiply and divide instructions

- Powerful bit-manipulation instructions

- Eight addressing modes

- Register direct [Rn]

- Register indirect [@ERn]

- Register indirect with displacement [@(d:16,ERn) or @(d:24,ERn)]

- Register indirect with post-increment or pre-decrement [@ERn+ or @-ERn]

- Absolute address [@aa:8, @aa:16, @aa:24]

- Immediate [#xx:8, #xx:16, or #xx:32]

- Program-counter relative [@(d:8,PC) or @(d:16,PC)]

- Memory indirect [@@aa:8]

- 64-kbyte address space

- High-speed operation

- All frequently-used instructions execute in one or two states

- 8/16/32-bit register-register add/subtract : 2 states

- -- 8 × 8-bit register-register multiply : 14 states

- $-16 \div 8$ -bit register-register divide : 14 states

- $-16 \times 16$ -bit register-register multiply : 22 states

- $-32 \div 16$ -bit register-register divide : 22 states

Section 2 CPU

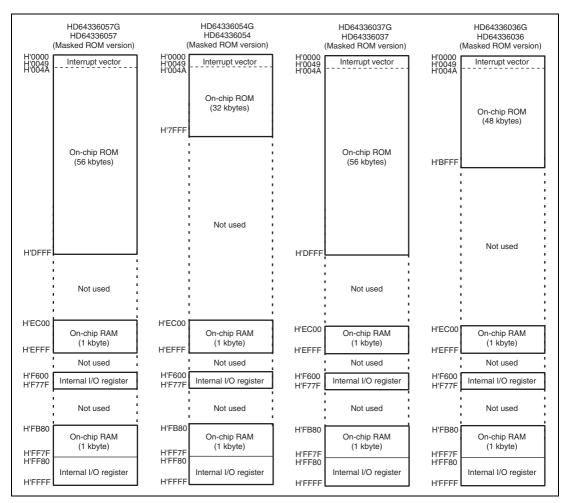

Figure 2.1 Memory Map (2)

#### 2.4.2 Basic Instruction Formats

H8/300H CPU instructions consist of 2-byte (1-word) units. An instruction consists of an operation field (op), a register field (r), an effective address extension (EA), and a condition field (cc).

Figure 2.7 shows examples of instruction formats.

Operation Field

Indicates the function of the instruction, the addressing mode, and the operation to be carried out on the operand. The operation field always includes the first four bits of the instruction. Some instructions have two operation fields.

• Register Field

Specifies a general register. Address registers are specified by 3 bits, and data registers by 3 bits or 4 bits. Some instructions have two register fields. Some have no register field.

• Effective Address Extension

8, 16, or 32 bits specifying immediate data, an absolute address, or a displacement. A24-bit address or displacement is treated as a 32-bit data in which the first 8 bits are 0 (H'00).

Condition Field

Specifies the branching condition of Bcc instructions.

| (1) Op                                                                | (1) Operation field only        |                 |                       |                    |  |  |  |  |

|-----------------------------------------------------------------------|---------------------------------|-----------------|-----------------------|--------------------|--|--|--|--|

| [                                                                     | C                               | p               |                       | NOP, RTS, etc.     |  |  |  |  |

| (2) Op                                                                | eration field and register fie  | lds             |                       |                    |  |  |  |  |

|                                                                       | ор                              | rn              | rm                    | ADD.B Rn, Rm, etc. |  |  |  |  |

| (3) Op                                                                | eration field, register fields, | and effective a | ddress extensi        | ion                |  |  |  |  |

| Γ                                                                     | ор                              | rn              | MOV.B @(d:16, Rn), Rm |                    |  |  |  |  |

|                                                                       | EA(                             | disp)           |                       |                    |  |  |  |  |

| (4) Operation field, effective address extension, and condition field |                                 |                 |                       |                    |  |  |  |  |

| [                                                                     | ор сс                           | EA(o            | BRA d:8               |                    |  |  |  |  |

Figure 2.7 Instruction Formats

# Section 3 Exception Handling

Exception handling may be caused by a reset, a trap instruction (TRAPA), or interrupts.

• Reset

A reset has the highest exception priority. Exception handling starts as soon as the reset is cleared by the  $\overline{\text{RES}}$  pin. The chip is also reset when the watchdog timer overflows, and exception handling starts. Exception handling is the same as exception handling by the  $\overline{\text{RES}}$  pin.

• Trap Instruction

Exception handling starts when a trap instruction (TRAPA) is executed. The TRAPA instruction generates a vector address corresponding to a vector number from 0 to 3, as specified in the instruction code. Exception handling can be executed at all times in the program execution state, regardless of the setting of the I bit in CCR.

• Interrupts

External interrupts other than NMI and internal interrupts other than address break are masked by the I bit in CCR, and kept masked while the I bit is set to 1. Exception handling starts when the current instruction or exception handling ends, if an interrupt request has been issued.

### • P22/TXD pin

| Register      | PMR1 | PCR2  |                |

|---------------|------|-------|----------------|

| Bit Name      | TXD  | PCR22 | Pin Function   |

| Setting Value | 0    | 0     | P22 input pin  |

|               |      | 1     | P22 output pin |

|               | 1    | Х     | TXD output pin |

## [Legend]

X: Don't care.

#### • P21/RXD pin

| Register      | SCR3 | PCR2  |                |

|---------------|------|-------|----------------|

| Bit Name      | RE   | PCR21 | Pin Function   |

| Setting Value | 0    | 0     | P21 input pin  |

|               |      | 1     | P21 output pin |

|               | 1    | Х     | RXD input pin  |

### [Legend]

X: Don't care.

#### • P20/SCK3 pin

| Register      | SCR3 |      | SMR | PCR2  |                 |

|---------------|------|------|-----|-------|-----------------|

| Bit Name      | CKE1 | CKE0 | СОМ | PCR20 | Pin Function    |

| Setting Value | 0    | 0    | 0   | 0     | P20 input pin   |

|               |      |      |     | 1     | P20 output pin  |

|               | 0    | 0    | 1   | Х     | SCK3 output pin |

|               | 0    | 1    | Х   | Х     | SCK3 output pin |

|               | 1    | Х    | Х   | Х     | SCK3 input pin  |

[Legend]

X: Don't care.

## • P52/WKP2 pin

| Register      | PMR5 | PCR5  |                |

|---------------|------|-------|----------------|

| Bit Name      | WKP2 | PCR52 | Pin Function   |

| Setting Value | 0    | 0     | P52 input pin  |

|               |      | 1     | P52 output pin |

|               | 1    | Х     | WKP2 input pin |

## [Legend]

X: Don't care.

## • P51/WKP1 pin

| Register      | PMR5 | PCR5  |                |

|---------------|------|-------|----------------|

| Bit Name      | WKP1 | PCR51 | Pin Function   |

| Setting Value | 0    | 0     | P51 input pin  |

|               |      | 1     | P51 output pin |

|               | 1    | Х     | WKP1 input pin |

|               |      |       |                |

[Legend]

X: Don't care.

## • P50/WKP0 pin

| Register      | PMR5 | PCR5  |                |

|---------------|------|-------|----------------|

| Bit Name      | WKP0 | PCR50 | Pin Function   |

| Setting Value | 0    | 0     | P50 input pin  |

|               |      | 1     | P50 output pin |

|               | 1    | Х     | WKP0 input pin |

[Legend]

X: Don't care.

### 9.5.1 Port Control Register 7 (PCR7)

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                             |

|-----|----------|------------------|-----|---------------------------------------------------------------------------------------------------------|

| 7   |          |                  |     | When each of the port 7 pins P76 to P74 and P72 to P70                                                  |

| 6   | PCR76    | 0                | W   | functions as a general I/O port, setting a PCR7 bit to 1                                                |

| 5   | PCR75    | 0                | W   | makes the corresponding pin an output port, while<br>clearing the bit to 0 makes the pin an input port. |

| 4   | PCR74    | 0                | W   | Bits 7 and 3 are reserved bits.                                                                         |

| 3   |          |                  |     |                                                                                                         |

| 2   | PCR72    | 0                | W   |                                                                                                         |

| 1   | PCR71    | 0                | W   |                                                                                                         |

| 0   | PCR70    | 0                | W   |                                                                                                         |

PCR7 selects inputs/outputs in bit units for pins to be used as general I/O ports of port 7.

### 9.5.2 Port Data Register 7 (PDR7)

PDR7 is a general I/O port data register of port 7.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                      |  |

|-----|----------|------------------|-----|----------------------------------------------------------------------------------|--|

| 7   | _        | 1                |     | Stores output data for port 7 pins.                                              |  |

| 6   | P76      | 0                | R/W | If PDR7 is read while PCR7 bits are set to 1, the value                          |  |

| 5   | P75      | 0                | R/W | W stored in PDR7 are read. If PDR7 is read while PCR7 bits                       |  |

| 4   | P74      | 0                | R/W | are cleared to 0, the pin states are read regardless of th value stored in PDR7. |  |

| 3   | —        | 1                |     | Bits 7 and 3 are reserved bits. These bits are always read                       |  |

| 2   | P72      | 0                | R/W | R/W as 1.                                                                        |  |

| 1   | P71      | 0                | R/W |                                                                                  |  |

| 0   | P70      | 0                | R/W |                                                                                  |  |

## **11.5** Timer V Application Examples

#### 11.5.1 Pulse Output with Arbitrary Duty Cycle

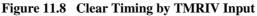

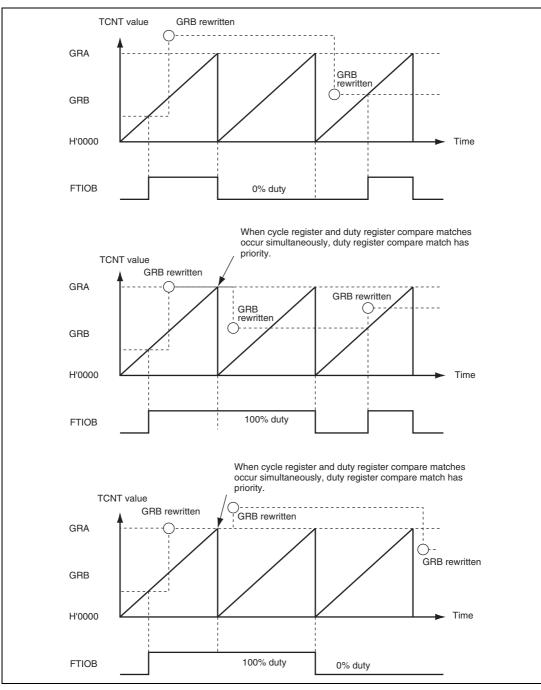

Figure 11.9 shows an example of output of pulses with an arbitrary duty cycle.

- 1. Set bits CCLR1 and CCLR0 in TCRV0 so that TCNTV will be cleared by compare match with TCORA.

- 2. Set bits OS3 to OS0 in TCSRV so that the output will go to 1 at compare match with TCORA and to 0 at compare match with TCORB.

- 3. Set bits CKS2 to CKS0 in TCRV0 and bit ICKS0 in TCRV1 to select the desired clock source.

- 4. With these settings, a waveform is output without further software intervention, with a period determined by TCORA and a pulse width determined by TCORB.

Figure 11.9 Pulse Output Example

- Eleven interrupt sources

- Four compare match/input capture interrupts and an overflow interrupt are available for each channel. An underflow interrupt can be set for channel 1.

| Item                                                   |          | Channel 0                                                          | Channel 1                                                          |  |

|--------------------------------------------------------|----------|--------------------------------------------------------------------|--------------------------------------------------------------------|--|

| Count clock                                            |          | Internal clocks: φ, φ/2, φ/4, φ/8<br>External clock: FTIOA0 (TCLK) |                                                                    |  |

| General registe<br>(output compare<br>capture register | e/input  | GRA_0, GRB_0, GRC_0, GRD_0                                         | GRA_1, GRB_1, GRC_1, GRD_1                                         |  |

| Buffer register                                        |          | GRC_0, GRD_0                                                       | GRC_1, GRD_1                                                       |  |

| I/O pins                                               |          | FTIOA0, FTIOB0, FTIOC0,<br>FTIOD0                                  | FTIOA1, FTIOB1, FTIOC1,<br>FTIOD1                                  |  |

| Counter clearing function                              |          | Compare match/input capture of GRA_0, GRB_0, GRC_0, or GRD_0       | Compare match/input capture of<br>GRA_1, GRB_1, GRC_1, or<br>GRD_1 |  |

| Compare                                                | 0 output | Yes                                                                | Yes                                                                |  |

| match output                                           | 1 output | Yes                                                                | Yes                                                                |  |

|                                                        | output   | Yes                                                                | Yes                                                                |  |

| Input capture fu                                       | nction   | Yes                                                                | Yes                                                                |  |

| Synchronous of                                         | peration | Yes                                                                | Yes                                                                |  |

| PWM mode                                               |          | Yes                                                                | Yes                                                                |  |

| Reset synchron mode                                    | ous PWM  | Yes                                                                | Yes                                                                |  |

| Complementary PWM mode                                 |          | Yes                                                                | Yes                                                                |  |

| Buffer function                                        |          | Yes                                                                | Yes                                                                |  |

| Interrupt source                                       |          |                                                                    | Compare match/input capture A1<br>to D1<br>Overflow<br>Underflow   |  |

### Table 12.1 Timer Z Functions

#### 14.3.7 Serial Status Register (SSR)

SSR is a register containing status flags of the SCI3 and multiprocessor bits for transfer. 1 cannot be written to flags TDRE, RDRF, OER, PER, and FER; they can only be cleared.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                            |

|-----|----------|------------------|-----|----------------------------------------------------------------------------------------|

| 7   | TDRE     | 1                | R/W | Transmit Data Register Empty                                                           |

|     |          |                  |     | Indicates whether TDR contains transmit data.                                          |

|     |          |                  |     | [Setting conditions]                                                                   |

|     |          |                  |     | • When the TE bit in SCR3 is 0                                                         |

|     |          |                  |     | When data is transferred from TDR to TSR                                               |

|     |          |                  |     | [Clearing conditions]                                                                  |

|     |          |                  |     | • When 0 is written to TDRE after reading TDRE = 1                                     |

|     |          |                  |     | When the transmit data is written to TDR                                               |

| 6   | RDRF     | 0                | R/W | Receive Data Register Full                                                             |

|     |          |                  |     | Indicates that the received data is stored in RDR.                                     |

|     |          |                  |     | [Setting condition]                                                                    |

|     |          |                  |     | When serial reception ends normally and receive data<br>is transferred from RSR to RDR |

|     |          |                  |     | [Clearing conditions]                                                                  |

|     |          |                  |     | • When 0 is written to RDRF after reading RDRF = 1                                     |

|     |          |                  |     | When data is read from RDR                                                             |

| 5   | OER      | 0                | R/W | Overrun Error                                                                          |

|     |          |                  |     | [Setting condition]                                                                    |

|     |          |                  |     | When an overrun error occurs in reception                                              |

|     |          |                  |     | [Clearing condition]                                                                   |

|     |          |                  |     | • When 0 is written to OER after reading OER = 1                                       |

| 4   | FER      | 0                | R/W | Framing Error                                                                          |

|     |          |                  |     | [Setting condition]                                                                    |

|     |          |                  |     | When a framing error occurs in reception                                               |

|     |          |                  |     | [Clearing condition]                                                                   |

|     |          |                  |     | • When 0 is written to FER after reading FER = 1                                       |

|                     |   | Ор  | erating Fre  | equency | /   |              |

|---------------------|---|-----|--------------|---------|-----|--------------|

|                     |   | 18  |              |         | 20  |              |

| Bit Rate<br>(bit/s) | n | N   | Error<br>(%) | n       | N   | Error<br>(%) |

| 110                 | 3 | 79  | -0.12        | 3       | 88  | -0.25        |

| 150                 | 2 | 233 | 0.14         | 3       | 64  | 0.14         |

| 300                 | 2 | 114 | 0.14         | 2       | 129 | 0.14         |

| 600                 | 1 | 233 | 0.14         | 2       | 64  | 0.14         |

| 1200                | 1 | 114 | 0.14         | 1       | 129 | 0.14         |

| 2400                | 0 | 233 | 0.14         | 1       | 64  | 0.14         |

| 4800                | 0 | 114 | 0.14         | 0       | 129 | 0.14         |

| 9600                | 0 | 58  | -0.96        | 0       | 64  | 0.14         |

| 19200               | 0 | 28  | 1.02         | 0       | 32  | -1.36        |

| 31250               | 0 | 17  | 0.00         | 0       | 19  | 0.00         |

| 38400               | 0 | 14  | -2.34        | 0       | 15  | 1.73         |

Operating Frequency  $\phi$  (MHz)

[Legend]

-: A setting is available but error occurs.

| Table 14.4 Maximum Bit Rate for Each Frequency (Asynchron |

|-----------------------------------------------------------|

|-----------------------------------------------------------|

| φ (MHz)  | Maximum Bit<br>Rate (bit/s) | n | N | φ (MHz) | Maximum Bit<br>Rate (bit/s) | n | N |

|----------|-----------------------------|---|---|---------|-----------------------------|---|---|

| 2        | 62500                       | 0 | 0 | 8       | 250000                      | 0 | 0 |

| 2.097152 | 65536                       | 0 | 0 | 9.8304  | 307200                      | 0 | 0 |

| 2.4576   | 76800                       | 0 | 0 | 10      | 312500                      | 0 | 0 |

| 3        | 93750                       | 0 | 0 | 12      | 375000                      | 0 | 0 |

| 3.6864   | 115200                      | 0 | 0 | 12.288  | 384000                      | 0 | 0 |

| 4        | 125000                      | 0 | 0 | 14      | 437500                      | 0 | 0 |

| 4.9152   | 153600                      | 0 | 0 | 14.7456 | 460800                      | 0 | 0 |

| 5        | 156250                      | 0 | 0 | 14      | 500000                      | 0 | 0 |

| 6        | 187500                      | 0 | 0 | 17.2032 | 537600                      | 0 | 0 |

| 6.144    | 192000                      | 0 | 0 | 18      | 562500                      | 0 | 0 |

| 7.3728   | 230400                      | 0 | 0 | 20      | 625000                      | 0 | 0 |

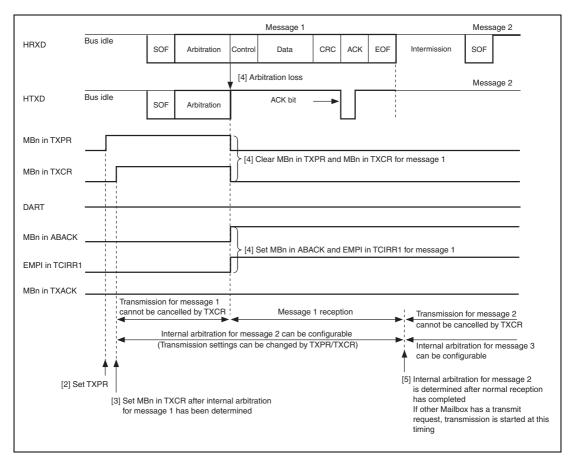

Figure 15.9 Internal Arbitration at Reception Caused by CAN Bus Arbitration Loss (MBn in TXCR = 1)

### 16.3.1 SS Control Register H (SSCRH)

SSCRH is a register that selects a master or a slave device, enables bidirectional mode, selects open-drain output of the serial data output pin, selects an output value of the serial data output pin, selects the SSCK pin, and selects the  $\overline{SCS}$  pin.

|     |          | Initial |     |                                                                                                                                                                                                                                                                                      |

|-----|----------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                                                                                                                                                                                                                                          |

| 7   | MSS      | 0       | R/W | Master/Slave Device Select                                                                                                                                                                                                                                                           |

|     |          |         |     | Selects whether this module is used as a master device<br>or a slave device. When this module is used as a master<br>device, transfer clock is output from the SSCK pin. When<br>the CE bit in SSSR is set, this bit is automatically cleared.                                       |

|     |          |         |     | 0: Operates as a slave device                                                                                                                                                                                                                                                        |

|     |          |         |     | 1: Operates as a master device                                                                                                                                                                                                                                                       |

| 6   | BIDE     | 0       | R/W | Bidirectional Mode Enable                                                                                                                                                                                                                                                            |

|     |          |         |     | Selects whether the serial data input pin and the output<br>pin are both used or only one pin is used. For details,<br>refer to section 16.4.3, Relationship between Data<br>Input/Output Pin and Shift Register. When the SSUMS bit<br>in SSCRL is 0, this setting is invalid.      |

|     |          |         |     | <ol> <li>Normal mode. Communication is performed by using two pins.</li> </ol>                                                                                                                                                                                                       |

|     |          |         |     | <ol> <li>Bidirectional mode. Communication is performed by<br/>using only one pin.</li> </ol>                                                                                                                                                                                        |

| 5   | SOOS     | 0       | R/W | Serial Data Open-Drain Output Select                                                                                                                                                                                                                                                 |

|     |          |         |     | Selects whether the serial data output pin is CMOS<br>output or NMOS open-drain output. The serial data output<br>pin is changed according to the register setting value. For<br>details, refer to section 16.4.3, Relationship between<br>Data Input/Output Pin and Shift Register. |

|     |          |         |     | 0: CMOS output                                                                                                                                                                                                                                                                       |

|     |          |         |     | 1: NMOS open-drain output                                                                                                                                                                                                                                                            |

|                                       |                     |                                               |                                                                                           |      | Value | es    |      |                                      |

|---------------------------------------|---------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------|------|-------|-------|------|--------------------------------------|

| ltem                                  | Symbol              | Applicable Pins                               | Test Condition                                                                            | Min. | Тур.  | Max.  | Unit | Notes                                |

| Pull-up<br>MOS                        | $-I_{p}$            | P10 to P12,<br>P14 to P17,P50 to              | $V_{cc} = 5.0 \text{ V},$<br>$V_{iN} = 0.0 \text{ V}$                                     | 50.0 | _     | 300.0 | μA   |                                      |

| current                               |                     | P55                                           | V <sub>cc</sub> = 3.0 V,<br>V <sub>IN</sub> = 0.0 V                                       | —    | 60.0  | _     |      | Reference value                      |

| Input<br>capaci-<br>tance             | C <sub>in</sub>     | All input pins<br>except power<br>supply pins | f = 1 MHz,<br>$V_{IN} = 0.0 V,$<br>$T_a = 25^{\circ}C$                                    | —    | _     | 15.0  | pF   |                                      |

| Active<br>mode<br>supply              | I <sub>OPE1</sub>   | V <sub>cc</sub>                               | Active mode 1<br>$V_{cc} = 5.0 V$ ,<br>$f_{osc} = 20 MHz$                                 | _    | 25.0  | 35.0  | mA   | *3                                   |

| current                               |                     |                                               | Active mode 1<br>$V_{cc} = 3.0 V$ ,<br>$f_{osc} = 10 MHz$                                 |      | 10.0  | _     |      | * <sup>3</sup><br>Reference<br>value |

|                                       | I <sub>OPE2</sub>   | V <sub>cc</sub>                               | Active mode 2<br>$V_{cc} = 5.0 V$ ,<br>$f_{osc} = 20 MHz$                                 | _    | 1.2   | 3.0   | mA   | *3                                   |

|                                       |                     |                                               | Active mode 2<br>$V_{cc} = 3.0 V$ ,<br>$f_{osc} = 10 MHz$                                 | _    | 0.8   | _     |      | *3<br>Reference<br>value             |

| Sleep<br>mode<br>supply               | I <sub>SLEEP1</sub> | V <sub>cc</sub>                               | Sleep mode 1<br>$V_{cc} = 5.0 V$ ,<br>$f_{osc} = 20 MHz$                                  | —    | 14.0  | 22.5  | mA   | *3                                   |

| current                               |                     |                                               | Sleep mode 1<br>$V_{cc} = 3.0 V$ ,<br>$f_{osc} = 10 MHz$                                  | —    | 6.3   | _     |      | * <sup>3</sup><br>Reference<br>value |

|                                       | I <sub>SLEEP2</sub> | V <sub>cc</sub>                               | Sleep mode 2<br>$V_{cc} = 5.0 V$ ,<br>$f_{osc} = 20 MHz$                                  | _    | 1.0   | 2.7   | mA   | *3                                   |

|                                       |                     |                                               | Sleep mode 2<br>$V_{cc} = 3.0 V$ ,<br>$f_{osc} = 10 MHz$                                  | —    | 0.7   | —     |      | * <sup>3</sup><br>Reference<br>value |

| Subactive mode                        | I <sub>sub</sub>    | V <sub>cc</sub>                               | $V_{\rm CC} = 5.0 \text{ V}$ $(\phi_{\rm SUB} = \phi_{\rm W}/2)$                          | —    | 60.0  | 100.0 | μA   | *3                                   |

| supply<br>current                     |                     |                                               | $\begin{array}{l} V_{_{CC}}=5.0 \ V \\ (\varphi_{_{SUB}}=\varphi_{_W}\!/\!8) \end{array}$ |      | 46.0  | _     |      | * <sup>3</sup><br>Reference<br>value |

| Subsleep<br>mode<br>supply<br>current | ISUBSP              | V <sub>cc</sub>                               | $V_{\rm CC} = 5.0 \text{ V}$ $(\phi_{\rm SUB} = \phi_{\rm W}/2)$                          | _    | 50.0  | 80.0  | μA   | *3                                   |

### 2. Arithmetic Instructions

|      |                   |              |     |    |      |           |             |     | le ai<br>(by |        | ) |                                          |   |     |       |      |                                                                                                                                                                                                                                                                                                                                                                                                                               |        | No<br>Stat | . of<br>es <sup>*1</sup> |

|------|-------------------|--------------|-----|----|------|-----------|-------------|-----|--------------|--------|---|------------------------------------------|---|-----|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|--------------------------|

|      | Mnemonic          | Operand Size | #xx | Rn | @ERn | @(d, ERn) | @-ERn/@ERn+ | @aa | @(d, PC)     | @ @ aa | 1 | Operation                                | 1 | Con | ditio | n Co | v     c       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1 | Normal | Advanced   |                          |

| ADD  | ADD.B #xx:8, Rd   | В            | 2   |    |      |           |             |     |              |        |   | $Rd8+#xx:8 \rightarrow Rd8$              | - | \$  | \$    | 1    | \$                                                                                                                                                                                                                                                                                                                                                                                                                            | \$     | 1          | 2                        |

|      | ADD.B Rs, Rd      | в            |     | 2  |      |           |             |     |              |        |   | $Rd8+Rs8 \rightarrow Rd8$                | - | \$  | \$    | \$   |                                                                                                                                                                                                                                                                                                                                                                                                                               | \$     | 1          | 2                        |

|      | ADD.W #xx:16, Rd  | w            | 4   |    |      |           |             |     |              |        |   | Rd16+#xx:16 $\rightarrow$ Rd16           | - | (1) | \$    | \$   | \$                                                                                                                                                                                                                                                                                                                                                                                                                            | \$     |            | 4                        |

|      | ADD.W Rs, Rd      | w            |     | 2  |      |           |             |     |              |        |   | Rd16+Rs16 $\rightarrow$ Rd16             | - | (1) | \$    | \$   | \$                                                                                                                                                                                                                                                                                                                                                                                                                            | \$     | 1          | 2                        |

|      | ADD.L #xx:32, ERd | L            | 6   |    |      |           |             |     |              |        |   | ERd32+#xx:32 →<br>ERd32                  | - | (2) | \$    | \$   | -                                                                                                                                                                                                                                                                                                                                                                                                                             | \$     | 6          | 6                        |

|      | ADD.L ERs, ERd    | L            |     | 2  |      |           |             |     |              |        |   | ERd32+ERs32 →<br>ERd32                   | - | (2) | \$    | \$   | \$                                                                                                                                                                                                                                                                                                                                                                                                                            | \$     | 2          | 2                        |

| ADDX | ADDX.B #xx:8, Rd  | в            | 2   |    |      |           |             |     |              |        |   | $Rd8+#xx:8 + C \rightarrow Rd8$          | - | \$  | \$    | (3)  | \$                                                                                                                                                                                                                                                                                                                                                                                                                            | \$     | 1          | 2                        |

|      | ADDX.B Rs, Rd     | в            |     | 2  |      |           |             |     |              |        |   | Rd8+Rs8 +C $\rightarrow$ Rd8             | - | \$  | \$    | (3)  | \$                                                                                                                                                                                                                                                                                                                                                                                                                            | \$     | 1          | 2                        |

| ADDS | ADDS.L #1, ERd    | L            |     | 2  |      |           |             |     |              |        |   | ERd32+1 $\rightarrow$ ERd32              | — | —   | —     | -    | _                                                                                                                                                                                                                                                                                                                                                                                                                             | —      | 1          | 2                        |

|      | ADDS.L #2, ERd    | L            |     | 2  |      |           |             |     |              |        |   | $ERd32+2 \rightarrow ERd32$              | - | _   | _     | -    | _                                                                                                                                                                                                                                                                                                                                                                                                                             | —      | 2          | 2                        |

|      | ADDS.L #4, ERd    | L            |     | 2  |      |           |             |     |              |        |   | $ERd32+4 \rightarrow ERd32$              | - | —   | _     | —    | _                                                                                                                                                                                                                                                                                                                                                                                                                             | —      | 2          | 2                        |

| INC  | INC.B Rd          | в            |     | 2  |      |           |             |     |              |        |   | $Rd8+1 \rightarrow Rd8$                  | - | —   | \$    | \$   | \$                                                                                                                                                                                                                                                                                                                                                                                                                            | —      | 2          | 2                        |

|      | INC.W #1, Rd      | W            |     | 2  |      |           |             |     |              |        |   | $Rd16+1 \rightarrow Rd16$                | - | —   | \$    | \$   | \$                                                                                                                                                                                                                                                                                                                                                                                                                            | —      | ć          | 2                        |

|      | INC.W #2, Rd      | W            |     | 2  |      |           |             |     |              |        |   | $Rd16+2 \rightarrow Rd16$                | - | —   | \$    | \$   | €                                                                                                                                                                                                                                                                                                                                                                                                                             | —      | ć          | 2                        |

|      | INC.L #1, ERd     | L            |     | 2  |      |           |             |     |              |        |   | $ERd32+1 \rightarrow ERd32$              | — | —   | \$    | \$   | \$                                                                                                                                                                                                                                                                                                                                                                                                                            | —      | 2          | 2                        |

|      | INC.L #2, ERd     | L            |     | 2  |      |           |             |     |              |        |   | $ERd32+2 \rightarrow ERd32$              | - | —   | \$    | \$   | \$                                                                                                                                                                                                                                                                                                                                                                                                                            | —      | 2          | 2                        |

| DAA  | DAA Rd            | В            |     | 2  |      |           |             |     |              |        |   | Rd8 decimal adjust $\rightarrow$ Rd8     | — | *   | \$    | \$   | *                                                                                                                                                                                                                                                                                                                                                                                                                             | \$     | 2          | 2                        |

| SUB  | SUB.B Rs, Rd      | В            |     | 2  |      |           |             |     |              |        |   | $Rd8-Rs8 \rightarrow Rd8$                | - | \$  | \$    | \$   | \$                                                                                                                                                                                                                                                                                                                                                                                                                            | \$     | 2          | 2                        |

|      | SUB.W #xx:16, Rd  | W            | 4   |    |      |           |             |     |              |        |   | Rd16–#xx:16 $\rightarrow$ Rd16           | - | (1) | \$    | \$   | \$                                                                                                                                                                                                                                                                                                                                                                                                                            | \$     | 4          | 4                        |

|      | SUB.W Rs, Rd      | W            |     | 2  |      |           |             |     |              |        |   | $Rd16-Rs16 \rightarrow Rd16$             | - | (1) | \$    | \$   | \$                                                                                                                                                                                                                                                                                                                                                                                                                            | \$     | 2          | 2                        |

|      | SUB.L #xx:32, ERd | L            | 6   |    |      |           |             |     |              |        |   | $ERd32\text{-}\#xx:32 \rightarrow ERd32$ | - | (2) | \$    | \$   | \$                                                                                                                                                                                                                                                                                                                                                                                                                            | \$     | 6          | 6                        |

|      | SUB.L ERs, ERd    | L            |     | 2  |      |           |             |     |              |        |   | $ERd32\text{-}ERs32 \rightarrow ERd32$   | - | (2) | \$    | \$   | €                                                                                                                                                                                                                                                                                                                                                                                                                             | \$     | 2          | 2                        |

| SUBX | SUBX.B #xx:8, Rd  | В            | 2   |    |      |           |             |     |              |        |   | $Rd8\text{-}\#xx:8\text{-}C\toRd8$       | - | \$  | \$    | (3)  | \$                                                                                                                                                                                                                                                                                                                                                                                                                            | \$     | í.         | 2                        |

|      | SUBX.B Rs, Rd     | В            |     | 2  |      |           |             |     |              |        |   | $Rd8\text{-}Rs8\text{-}C\toRd8$          | — | \$  | \$    | (3)  | €                                                                                                                                                                                                                                                                                                                                                                                                                             | \$     | ć          | 2                        |

| SUBS | SUBS.L #1, ERd    | L            |     | 2  |      |           |             |     |              |        |   | $ERd321\toERd32$                         | - | _   | —     | -    | —                                                                                                                                                                                                                                                                                                                                                                                                                             | _      | 2          | 2                        |

|      | SUBS.L #2, ERd    | L            |     | 2  |      |           |             |     |              |        |   | $ERd32-2 \to ERd32$                      | - | _   | —     | -    | —                                                                                                                                                                                                                                                                                                                                                                                                                             | _      | 2          | 2                        |

|      | SUBS.L #4, ERd    | L            |     | 2  |      |           |             |     |              |        |   | $ERd324 \to ERd32$                       | - | _   | —     | -    | —                                                                                                                                                                                                                                                                                                                                                                                                                             | _      | í          | 2                        |

| DEC  | DEC.B Rd          | В            |     | 2  |      |           |             |     |              |        |   | $Rd8-1 \rightarrow Rd8$                  | - | —   | \$    | \$   | \$                                                                                                                                                                                                                                                                                                                                                                                                                            | —      | ć          | 2                        |

|      | DEC.W #1, Rd      | W            |     | 2  |      |           |             |     |              |        |   | $Rd16-1 \rightarrow Rd16$                | - | —   | \$    | \$   | $\uparrow$                                                                                                                                                                                                                                                                                                                                                                                                                    | —      | 2          | 2                        |

|      | DEC.W #2, Rd      | W            |     | 2  |      |           |             |     |              |        |   | $Rd16-2 \rightarrow Rd16$                | - | _   | \$    | \$   | 1                                                                                                                                                                                                                                                                                                                                                                                                                             |        | 1          | 2                        |

Instruction code:

| byte  | BL |  |

|-------|----|--|

| 2nd   | BH |  |

| oyte  | AL |  |

| 1st l | ΥH |  |

| ш      | Table A.2<br>(3)            |     | INC  |     |      |      |       |       | EXTS |     | DEC  |          | BGT BLE |     |        |

|--------|-----------------------------|-----|------|-----|------|------|-------|-------|------|-----|------|----------|---------|-----|--------|

|        | ble A.2<br>(3)              |     | INC  |     |      |      |       |       | EXTS |     | DEC  |          | BLT B(  |     |        |

| 0      | Table A.2 Table A.2 (3) (3) | Δ   |      | >   |      |      |       |       |      | Ē   |      | <u>د</u> | BGE     |     |        |

| B      |                             | ADD |      | MOV | SHAL | SHAR | ROTL  | ROTR  | NEG  | SUB |      | CMP      | BMI     |     |        |

| A      |                             |     |      |     |      |      |       |       |      |     |      |          | BPL     |     |        |

| თ      |                             |     | ADDS |     | SHAL | SHAR | ROTL  | ROTR  | NEG  |     | SUB  |          | BVS     |     |        |

| œ      | SLEEP                       |     | AC   |     | Ś    | Ś    | Я     | RC    | z    |     | ō    |          | BVC     |     |        |

| 2      |                             |     | INC  |     |      |      |       |       | EXTU |     | DEC  |          | BEQ     |     |        |

| 9      |                             |     |      |     |      |      |       |       |      |     |      |          | BNE     | AND |        |

| ى<br>ا |                             |     | INC  |     |      |      |       |       | EXTU |     | DEC  |          | BCS     | XOR | aOX    |

| 4      | LDC/STC                     |     |      |     |      |      |       |       |      |     |      |          | BCC     | OR  | 6      |

| m      |                             |     |      |     | SHLL | SHLR | ROTXL | ROTXR | NOT  |     |      |          | BLS     | SUB | u<br>u |

| N      |                             |     |      |     |      |      |       |       |      |     |      |          | BHI     | CMP | dWC    |

| -      |                             |     |      |     | SHLL | SHLR | ROTXL | ROTXR | NOT  |     |      |          | BRN     | ADD |        |

| •      | MOV                         | INC | ADDS | DAA | ō    | ъ    | RC    | RC    | z    | DEC | SUBS | DAS      | BRA     | MOV | NOM    |

| AH AL  | 01                          | OA  | OB   | OF  | 10   | 1    | 12    | 13    | 17   | 1A  | 1B   | Ť        | 58      | 62  | ~~     |

#### Table A.2 **Operation Code Map (2)**

#### RenesasTechnologyCorp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

#### **RENESAS SALES OFFICES**

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

Renesas Technology America, Inc. 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd. Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7898

Renesas Technology Hong Kong Ltd. 7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852- 2265-6688, Fax: <852- 2730-6071

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

Renesas Technology Singapore Pte. Ltd. 1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65- 6213-0200, Fax: <65- 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603- 7955-9309, Fax: <603- 7955-9310

http://www.renesas.com