#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                    |

| Core Size                  | 16-Bit                                                                     |

| Speed                      | 20MHz                                                                      |

| Connectivity               | CANbus, SCI, SSU                                                           |

| Peripherals                | PWM, WDT                                                                   |

| Number of I/O              | 45                                                                         |

| Program Memory Size        | 56KB (56K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-BQFP                                                                    |

| Supplier Device Package    | 64-QFP (14x14)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36037hv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 6.2  | Mode 7   | Fransitions and States of LSI                            |     |

|------|----------|----------------------------------------------------------|-----|

|      | 6.2.1    | Sleep Mode                                               |     |

|      | 6.2.2    | Standby Mode                                             |     |

|      | 6.2.3    | Subsleep Mode                                            |     |

|      | 6.2.4    | Subactive Mode                                           |     |

| 6.3  | Operati  | ing Frequency in Active Mode                             |     |

| 6.4  | Direct 7 | Transition                                               |     |

|      | 6.4.1    | Direct Transition from Active Mode to Subactive Mode     |     |

|      | 6.4.2    | Direct Transition from Subactive Mode to Active Mode     |     |

| 6.5  | Module   | e Standby Function                                       |     |

| Sect | ion 7 R  | ROM                                                      |     |

| 7.1  | Block (  | Configuration                                            |     |

| 7.2  | Registe  | er Descriptions                                          |     |

|      | 7.2.1    | Flash Memory Control Register 1 (FLMCR1)                 |     |

|      | 7.2.2    | Flash Memory Control Register 2 (FLMCR2)                 |     |

|      | 7.2.3    | Erase Block Register 1 (EBR1)                            |     |

|      | 7.2.4    | Flash Memory Power Control Register (FLPWCR)             |     |

|      | 7.2.5    | Flash Memory Enable Register (FENR)                      |     |

| 7.3  | On-Boa   | ard Programming Modes                                    |     |

|      | 7.3.1    | Boot Mode                                                |     |

|      | 7.3.2    | Programming/Erasing in User Program Mode                 |     |

| 7.4  | Flash M  | Aemory Programming/Erasing                               |     |

|      | 7.4.1    | Program/Program-Verify                                   |     |

|      | 7.4.2    | Erase/Erase-Verify                                       |     |

|      | 7.4.3    | Interrupt Handling when Programming/Erasing Flash Memory |     |

| 7.5  | Program  | m/Erase Protection                                       |     |

|      | 7.5.1    | Hardware Protection                                      |     |

|      | 7.5.2    | Software Protection                                      |     |

|      | 7.5.3    | Error Protection                                         |     |

| 7.6  | Program  | mmer Mode                                                |     |

| 7.7  | Power-   | Down States for Flash Memory                             |     |

| Sect | ion 8 R  | RAM                                                      | 109 |

| Sect | ion 9 L  | /O Ports                                                 |     |

| 9.1  |          |                                                          |     |

|      | 9.1.1    | Port Mode Register 1 (PMR1)                              |     |

|      | 9.1.2    | Port Control Register 1 (PCR1)                           |     |

|      | 9.1.3    | Port Data Register 1 (PDR1)                              |     |

|      |          | $\mathcal{C}$ , ,                                        |     |

| Figure 15.15 Set Timing for Message Reception                |                            |

|--------------------------------------------------------------|----------------------------|

| Figure 15.16 RXPR/RFPR Set/Clear Timing when Overrun/C       | Overwrite Occurs           |

| Figure 15.17 Flowchart for Changing ID, MBCR, and LAFM       | of Receive Mailbox         |

| Figure 15.18 Flowchart for Transition between Active Mode    | and Standby Mode or Module |

| Standby Mode                                                 |                            |

| Figure 15.19 High-Speed CAN Bus Interface Using HA1372       | 1                          |

| Section 16 Synchronous Serial Communication Unit (SSU        | )                          |

| Figure 16.1 Block Diagram of SSU                             |                            |

| Figure 16.2 Relationship between Clock Polarity and Phase, a | and Data                   |

| Figure 16.3 Relationship between Data Input/Output Pin and   | Shift Register             |

| Figure 16.4 Initialization in Clocked Synchronous Communic   | ation Mode                 |

| Figure 16.5 Example of Operation in Data Transmission        |                            |

| Figure 16.6 Sample Serial Transmission Flowchart             |                            |

| Figure 16.7 Example of Operation in Data Reception (MSS =    | 1)                         |

| Figure 16.8 Sample Serial Reception Flowchart (MSS = 1)      |                            |

| Figure 16.9 Sample Flowchart for Serial Transmit and Receiv  | e Operations               |

| Figure 16.10 Initialization in Four-Line Bus Communication   | Mode                       |

| Figure 16.11 Example of Operation in Data Transmission (M    | SS = 1)                    |

| Figure 16.12 Example of Operation in Data Reception (MSS     | = 1)                       |

| Figure 16.13 Arbitration Check Timing                        |                            |

| Figure 16.14 Procedures when Changing Output Level of Ser    | ial Data                   |

| Section 17 Subsystem Timer (Subtimer)                        |                            |

| Figure 17.1 Block Diagram of Subtimer                        |                            |

| Figure 17.2 Timing for On-Chip Oscillator                    |                            |

| Figure 17.3 SBTPS Setting Flowchart                          |                            |

| Figure 17.4 Example of Subtimer Operation                    |                            |

| Figure 17.5 Count Operation Flowchart                        |                            |

| Section 18 A/D Converter                                     |                            |

| Figure 18.1 Block Diagram of A/D Converter                   |                            |

| Figure 18.2 A/D Conversion Timing                            |                            |

| Figure 18.3 External Trigger Input Timing                    |                            |

| Figure 18.4 A/D Conversion Accuracy Definitions (1)          |                            |

| Figure 18.5 A/D Conversion Accuracy Definitions (2)          |                            |

| Figure 18.6 Analog Input Circuit Example                     |                            |

| Section 19 Power-On Reset and Low-Voltage Detection C        | · · ·                      |

| Figure 19.1 Block Diagram of Power-On Reset Circuit and L    | •                          |

| Figure 19.2 Operational Timing of Power-On Reset Circuit     |                            |

| Figure 19.3 Operational Timing of LVDR Circuit               |                            |

## 2.2 Register Configuration

The H8/300H CPU has the internal registers shown in figure 2.2. There are two types of registers; general registers and control registers. The control registers are a 24-bit program counter (PC), and an 8-bit condition-code register (CCR).

| General Registers (ERn)         |                                                                                               |                                  |                                                                                    |                                          |  |  |

|---------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------|------------------------------------------------------------------------------------|------------------------------------------|--|--|

|                                 | 15                                                                                            | C                                | 0 7 0                                                                              | 7 0                                      |  |  |

| ER0                             | E0                                                                                            |                                  | R0H                                                                                | R0L                                      |  |  |

| ER1                             | E1                                                                                            |                                  | R1H                                                                                | R1L                                      |  |  |

| ER2                             | E2                                                                                            |                                  | R2H                                                                                | R2L                                      |  |  |

| ER3                             | E3                                                                                            |                                  | R3H                                                                                | R3L                                      |  |  |

| ER4                             | E4                                                                                            |                                  | R4H                                                                                | R4L                                      |  |  |

| ER5                             | E5                                                                                            |                                  | R5H                                                                                | R5L                                      |  |  |

| ER6                             | E6                                                                                            |                                  | R6H                                                                                | R6L                                      |  |  |

| ER7                             | E7                                                                                            | (                                | SP) R7H                                                                            | R7L                                      |  |  |

| Control Reg                     | isters (CR)<br>PC                                                                             |                                  | CCR                                                                                | 0<br>7 6 5 4 3 2 1 0<br>1 UI H U N Z V C |  |  |

| [Leger                          | nd]                                                                                           |                                  |                                                                                    |                                          |  |  |

| SP:<br>PC:<br>CCR:<br>I:<br>UI: | Stack pointer<br>Program counter<br>Condition-code register<br>Interrupt mask bit<br>User bit | U: Us<br>N: Ne<br>Z: Ze<br>V: Ov | alf-carry flag<br>ser bit<br>egative flag<br>ero flag<br>verflow flag<br>arry flag |                                          |  |  |

Figure 2.2 CPU Registers

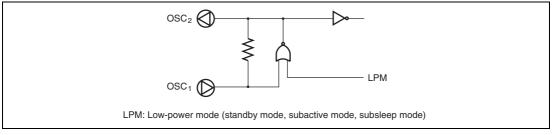

## 5.1 System Clock Generator

Clock pulses can be supplied to the system clock divider either by connecting a crystal or ceramic resonator, or by providing external clock input. Figure 5.2 shows a block diagram of the system clock generator.

Figure 5.2 Block Diagram of System Clock Generator

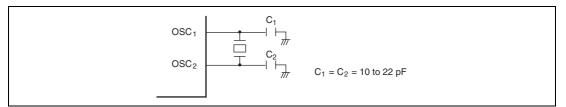

#### 5.1.1 Connecting Crystal Resonator

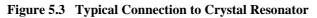

Figure 5.3 shows a typical method of connecting a crystal resonator. An AT-cut parallel-resonance crystal resonator should be used. Figure 5.4 shows the equivalent circuit of a crystal resonator. A resonator having the characteristics given in table 5.1 should be used.

Figure 5.4 Equivalent Circuit of Crystal Resonator

| l    | Bit Name |      |                |        | Operating Frequency |        |       |       |       |       |         |

|------|----------|------|----------------|--------|---------------------|--------|-------|-------|-------|-------|---------|

| STS2 | STS1     | STS0 | Waiting Time   | 20 MHz | 16 MHz              | 10 MHz | 8 MHz | 4 MHz | 2 MHz | 1 MHz | 0.5 MHz |

| 0    | 0        | 0    | 8,192 states   | 0.4    | 0.5                 | 0.8    | 1.0   | 2.0   | 4.1   | 8.1   | 16.4    |

|      |          | 1    | 16,384 states  | 0.8    | 1.0                 | 1.6    | 2.0   | 4.1   | 8.2   | 16.4  | 32.8    |

|      | 1        | 0    | 32,768 states  | 1.6    | 2.0                 | 3.3    | 4.1   | 8.2   | 16.4  | 32.8  | 65.5    |

|      |          | 1    | 65,536 states  | 3.3    | 4.1                 | 6.6    | 8.2   | 16.4  | 32.8  | 65.5  | 131.1   |

| 1    | 0        | 0    | 131,072 states | 6.6    | 8.2                 | 13.1   | 16.4  | 32.8  | 65.5  | 131.1 | 262.1   |

|      |          | 1    | 1,024 states   | 0.05   | 0.06                | 0.10   | 0.13  | 0.26  | 0.51  | 1.02  | 2.05    |

|      | 1        | 0    | 128 states     | 0.00   | 0.00                | 0.01   | 0.02  | 0.03  | 0.06  | 0.13  | 0.26    |

|      |          | 1    | 16 states      | 0.00   | 0.00                | 0.00   | 0.00  | 0.00  | 0.01  | 0.02  | 0.03    |

## Table 6.1 Operating Frequency and Waiting Time

Note: Time unit is ms.

#### 6.1.2 System Control Register 2 (SYSCR2)

SYSCR2 controls the power-down modes, as well as SYSCR1.

|     |          | Initial |     |                                                                                                                            |

|-----|----------|---------|-----|----------------------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                                                                                |

| 7   | SMSEL    | 0       | R/W | Sleep Mode Selection                                                                                                       |

| 6   | LSON     | 0       | R/W | Low Speed on Flag                                                                                                          |

| 5   | DTON     | 0       | R/W | Direct Transfer on Flag                                                                                                    |

|     |          |         |     | These bits select the mode to enter after the execution of a SLEEP instruction, as well as the SSBY bit in SYSCR1.         |

|     |          |         |     | For details, see table 6.2.                                                                                                |

| 4   | MA2      | 0       | R/W | Active Mode Clock Select 2 to 0                                                                                            |

| 3   | MA1      | 0       | R/W | These bits select the operating clock frequency in active                                                                  |

| 2   | MAO      | 0       | R/W | and sleep modes. The operating clock frequency<br>changes to the set frequency after the SLEEP instruction<br>is executed. |

|     |          |         |     | OXX: $\phi_{ m osc}$                                                                                                       |

|     |          |         |     | 100: φ <sub>osc</sub> /8                                                                                                   |

|     |          |         |     | 101: φ <sub>osc</sub> /16                                                                                                  |

|     |          |         |     | 110:                                                                                                                       |

|     |          |         |     | 111: \$\phi_{osc}\$/64                                                                                                     |

| • P16/IRQ2 pin |      |       |                |  |  |  |

|----------------|------|-------|----------------|--|--|--|

| Register       | PMR1 | PCR1  |                |  |  |  |

| Bit Name       | IRQ2 | PCR16 | Pin Function   |  |  |  |

| Setting value  | 0    | 0     | P16 input pin  |  |  |  |

|                |      | 1     | P16 output pin |  |  |  |

|                | 1    | Х     | IRQ2 input pin |  |  |  |

#### [Legend]

X: Don't care.

## • P15/IRQ1/TMIB1 pin

| Register      | PMR1 | PCR1  |                            |

|---------------|------|-------|----------------------------|

| Bit Name      | IRQ1 | PCR15 | Pin Function               |

| Setting value | 0    | 0     | P15 input pin              |

|               |      | 1     | P15 output pin             |

|               | 1    | Х     | IRQ1 input/TMIB1 input pin |

|               |      |       |                            |

[Legend]

X: Don't care.

## • P14/IRQ0 pin

| Register      | PMR1 | PCR1  |                |

|---------------|------|-------|----------------|

| Bit Name      | IRQ0 | PCR14 | Pin Function   |

| Setting value | 0    | 0     | P14 input pin  |

|               |      | 1     | P14 output pin |

|               | 1    | Х     | IRQ0 input pin |

## [Legend]

X: Don't care.

## • P12 pin

| Register      | PCR1  |                |  |

|---------------|-------|----------------|--|

| Bit Name      | PCR12 | Pin Function   |  |

| Setting value | 0     | P12 input pin  |  |

|               | 1     | P12 output pin |  |

## **11.5** Timer V Application Examples

#### 11.5.1 Pulse Output with Arbitrary Duty Cycle

Figure 11.9 shows an example of output of pulses with an arbitrary duty cycle.

- 1. Set bits CCLR1 and CCLR0 in TCRV0 so that TCNTV will be cleared by compare match with TCORA.

- 2. Set bits OS3 to OS0 in TCSRV so that the output will go to 1 at compare match with TCORA and to 0 at compare match with TCORB.

- 3. Set bits CKS2 to CKS0 in TCRV0 and bit ICKS0 in TCRV1 to select the desired clock source.

- 4. With these settings, a waveform is output without further software intervention, with a period determined by TCORA and a pulse width determined by TCORB.

Figure 11.9 Pulse Output Example

## 11.6 Usage Notes

The following types of contention or operation can occur in timer V operation.

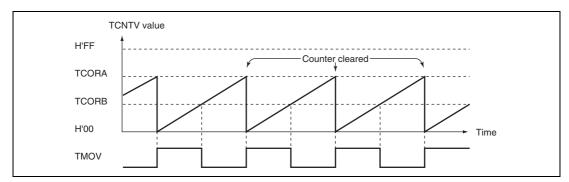

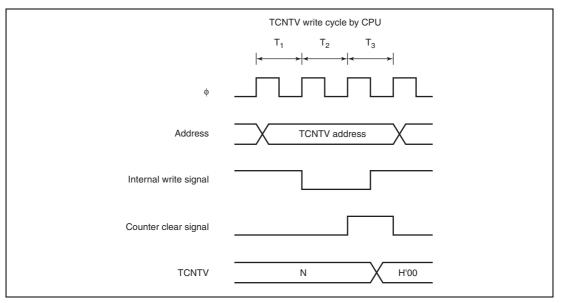

- 1. Writing to registers is performed in the T3 state of a TCNTV write cycle. If a TCNTV clear signal is generated in the T3 state of a TCNTV write cycle, as shown in figure 11.11, clearing takes precedence and the write to the counter is not carried out. If counting-up is generated in the T3 state of a TCNTV write cycle, writing takes precedence.

- 2. If a compare match is generated in the T3 state of a TCORA or TCORB write cycle, the write to TCORA or TCORB takes precedence and the compare match signal is inhibited. Figure 11.12 shows the timing.

- 3. If compare matches A and B occur simultaneously, any conflict between the output selections for compare match A and compare match B is resolved by the following priority: toggle output > output 1 > output 0.

- 4. Depending on the timing, TCNTV may be incremented by a switch between different internal clock sources. When TCNTV is internally clocked, an increment pulse is generated from the falling edge of an internal clock signal that is a divided system clock ( $\phi$ ). Therefore, as shown in figure 11.3 the switch is from a high clock signal to a low clock signal, the switchover is seen as a falling edge, causing TCNTV to increment. TCNTV can also be incremented by a switch between internal and external clocks.

Figure 11.11 Contention between TCNTV Write and Clear

## 12.3.2 Timer Mode Register (TMDR)

TMDR selects buffer operation settings and synchronized operation.

|        |          | Initial |     |                                                                                |

|--------|----------|---------|-----|--------------------------------------------------------------------------------|

| Bit    | Bit Name | Value   | R/W | Description                                                                    |

| 7      | BFD1     | 0       | R/W | Buffer Operation D1                                                            |

|        |          |         |     | 0: GRD_1 operates normally                                                     |

|        |          |         |     | 1: GRB_1 and GRD_1 are used together for buffer<br>operation                   |

| 6      | BFC1     | 0       | R/W | Buffer Operation C1                                                            |

|        |          |         |     | 0: GRC_1 operates normally                                                     |

|        |          |         |     | 1: GRA_1 and GRD_1 are used together for buffer<br>operation                   |

| 5      | BFD0     | 0       | R/W | Buffer Operation D0                                                            |

|        |          |         |     | 0: GRD_0 operates normally                                                     |

|        |          |         |     | <ol> <li>GRB_0 and GRD_0 are used together for buffer<br/>operation</li> </ol> |

| 4      | BFC0     | 0       | R/W | Buffer Operation C0                                                            |

|        |          |         |     | 0: GRC_0 operates normally                                                     |

|        |          |         |     | <ol> <li>GRA_0 and GRC_0 are used together for buffer<br/>operation</li> </ol> |

| 3 to 1 | _        | All 1   | _   | Reserved                                                                       |

|        |          |         |     | These bits are always read as 1 and cannot be modified.                        |

| 0      | SYNC     | 0       | R/W | Timer Synchronization                                                          |

|        |          |         |     | 0: TCNT_1 and TCNT_0 operate as a different timer                              |

|        |          |         |     | 1: TCNT_1 and TCNT_0 are synchronized                                          |

|        |          |         |     | TCNT_1 and TCNT_0 can be pre-set or cleared<br>synchronously                   |

#### **12.4.8** Buffer Operation

Buffer operation differs depending on whether GR has been designated for an input capture register or an output compare register, or in reset synchronous PWM mode or complementary PWM mode.

Table 12.8 shows the register combinations used in buffer operation.

Table 12.8

Register Combinations in Buffer Operation

| General Register | Buffer Register |

|------------------|-----------------|

| GRA              | GRC             |

| GRB              | GRD             |

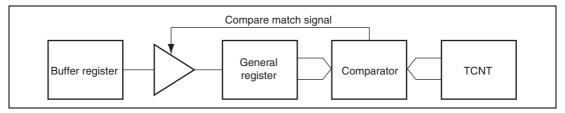

When GR is Output Compare Register: When a compare match occurs, the value in the buffer register of the corresponding channel is transferred to the general register.

This operation is illustrated in figure 12.35.

Figure 12.35 Compare Match Buffer Operation

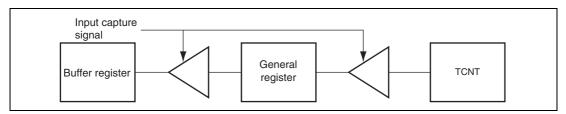

When GR is Input Capture Register: When an input capture occurs, the value in TCNT is transferred to the general register and the value previously stored in the general register is transferred to the buffer register.

This operation is illustrated in figure 12.36.

Figure 12.36 Input Capture Buffer Operation

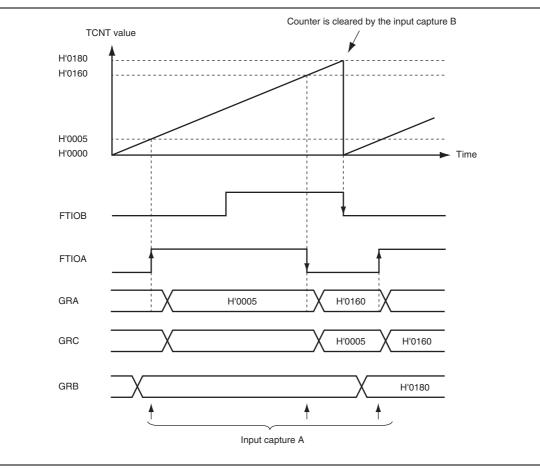

Figure 12.40 Example of Buffer Operation (2) (Buffer Operation for Input Capture Register)

# Section 13 Watchdog Timer

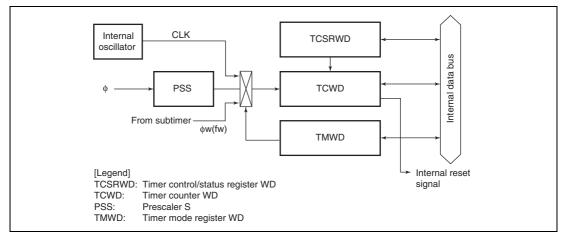

The watchdog timer is an 8-bit timer that can generate an internal reset signal for this LSI if a system crash prevents the CPU from writing to the timer counter, thus allowing it to overflow.

The block diagram of the watchdog timer is shown in figure 13.1.

Figure 13.1 Block Diagram of Watchdog Timer

## 13.1 Features

• Selectable from nine counter input clocks.

Eight internal clock sources ( $\phi/64$ ,  $\phi/128$ ,  $\phi/256$ ,  $\phi/512$ ,  $\phi/1024$ ,  $\phi/2048$ ,  $\phi/4096$ , and  $\phi/8192$ ) or the internal oscillator (WDT and SBT) can be selected as the timer-counter clock. When the internal oscillator is selected, it can operate as the watchdog timer in any operating mode.

• Reset signal generated on counter overflow An overflow period of 1 to 256 times the selected clock can be set.

[Legend] WDT: Watchdog timer SBT: Subtimer

# 13.3 Operation

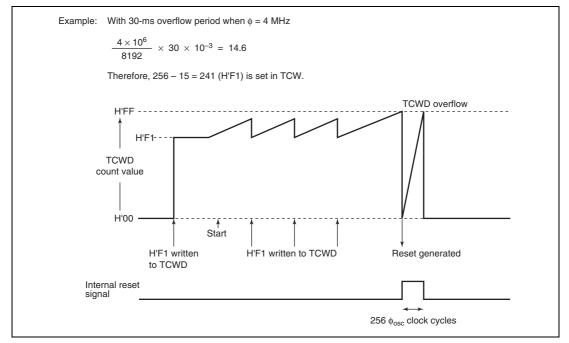

The watchdog timer is provided with an 8-bit counter. If 1 is written to WDON while writing 0 to B2WI when the TCSRWE bit in TCSRWD is set to 1, TCWD begins counting up. (To operate the watchdog timer, two write accesses to TCSRWD are required.) When a clock pulse is input after the TCWD count value has reached H'FF, the watchdog timer overflows and an internal reset signal is generated. The internal reset signal is output for a period of 256  $\phi_{osc}$  clock cycles. TCWD is a writable counter, and when a value is set in TCWD, the count-up starts from that value. An overflow period in the range of 1 to 256 input clock cycles can therefore be set, according to the TCWD set value.

Figure 13.2 shows an example of watchdog timer operation.

Figure 13.2 Watchdog Timer Operation Example

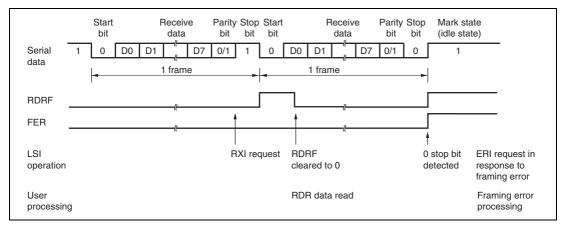

#### 14.4.4 Serial Data Reception

Figure 14.7 shows an example of operation for reception in asynchronous mode. In serial reception, the SCI3 operates as described below.

- 1. The SCI3 monitors the communication line. If a start bit is detected, the SCI3 performs internal synchronization, receives receive data in RSR, and checks the parity bit and stop bit.

- 2. If an overrun error occurs (when reception of the next data is completed while the RDRF flag is still set to 1), the OER bit in SSR is set to 1. If the RIE bit in SCR3 is set to 1 at this time, an ERI interrupt request is generated. Receive data is not transferred to RDR.

- 3. If a parity error is detected, the PER bit in SSR is set to 1 and receive data is transferred to RDR. If the RIE bit in SCR3 is set to 1 at this time, an ERI interrupt request is generated.

- 4. If a framing error is detected (when the stop bit is 0), the FER bit in SSR is set to 1 and receive data is transferred to RDR. If the RIE bit in SCR3 is set to 1 at this time, an ERI interrupt request is generated.

- 5. If reception is completed successfully, the RDRF bit in SSR is set to 1, and receive data is transferred to RDR. If the RIE bit in SCR3 is set to 1 at this time, an RXI interrupt request is generated. Continuous reception is possible because the RXI interrupt routine reads the receive data transferred to RDR before reception of the next receive data has been completed.

Figure 14.7 Example of SCI3 Reception in Asynchronous Mode (8-Bit Data, Parity, One Stop Bit)

#### 15.3.7 Transmit Pending Register (TXPR)

TXPR sets transmit pending (CAN bus arbitration wait) for the transmit message that is stored in a Mailbox. Setting the corresponding bit in TXPR to 1 enables a message to be transmitted. Writing 0 to the bit in TXPR is ignored.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                              |

|--------|----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 4 | _        | All 0            | _   | Reserved                                                                                                                                                                                                                                                                                                                                                                                 |

|        |          |                  |     | These bits are always read as 0.                                                                                                                                                                                                                                                                                                                                                         |

| 3      | MB3      | 0                | R/W | [Setting condition]                                                                                                                                                                                                                                                                                                                                                                      |

| 2      | MB2      | 0                | R/W | When the corresponding MBCR bit for a mailbox is 0, the                                                                                                                                                                                                                                                                                                                                  |

| 1      | MB1      | 0                | R/W | corresponding bit in TXPR is set to 1<br>(n = 3 to 1)                                                                                                                                                                                                                                                                                                                                    |

|        |          |                  |     | [Clearing conditions]                                                                                                                                                                                                                                                                                                                                                                    |

|        |          |                  |     | <ul> <li>When message transmission has completed<br/>successfully (TXACKn set)</li> </ul>                                                                                                                                                                                                                                                                                                |

|        |          |                  |     | <ul> <li>When transmission cancellation for an untransmitted<br/>message has finished (ABACKn set)</li> </ul>                                                                                                                                                                                                                                                                            |

|        |          |                  |     | <ul> <li>When a transmission cancellation request has<br/>occurred during message transmission, and an error<br/>occurs or arbitration is lost on the CAN bus (ABACKn<br/>set)</li> </ul>                                                                                                                                                                                                |

|        |          |                  |     | • When a transmit error or arbitration loss occurred with the corresponding DART bit for a message being transmitted set to 1                                                                                                                                                                                                                                                            |

|        |          |                  |     | If the message is not transmitted successfully, the MBn<br>bit is not cleared to 0. If any of these MB bits in TXPR are<br>cleared to 0, the EMPI bit in TCIRR1 is set to 1. The<br>TinyCAN automatically attempts retransmission as long<br>as the DART bit in the message control of the<br>corresponding Mailbox is not set to 1 or the<br>corresponding bit in TXCR is not set to 1. |

|        |          |                  |     | Note: When the MBn bit in MBCR is set to 1, the<br>TinyCAN does not transmit a message even if<br>the MBn bit in TXPR is set to 1. To clear the<br>MBn bit in TXPR to 0, set the MBn bit in TXCR<br>to 1 beforehand.                                                                                                                                                                     |

| 0      | _        | 0                | _   | Reserved                                                                                                                                                                                                                                                                                                                                                                                 |

|        |          |                  |     | This bit is always read as 0. This bit is relevant to the receive-only Mailbox, and its value cannot be changed.                                                                                                                                                                                                                                                                         |

## **19.2** Register Descriptions

The low-voltage detection circuit has the following registers.

- Low-voltage-detection control register (LVDCR)

- Low-voltage-detection status register (LVDSR)

#### 19.2.1 Low-Voltage-Detection Control Register (LVDCR)

LVDCR is used to enable or disable the low-voltage detection circuit, set the detection levels for the LVDR function, enable or disable the LVDR function, and enable or disable generation of an interrupt when the power-supply voltage rises above or falls below the respective levels.

Table 19.1 shows the relationship between the LVDCR settings and select functions. LVDCR should be set according to table 19.1.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                    |

|--------|----------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | LVDE     | 0*               | R/W | LVD Enable                                                                                                                                                                                                                     |

|        |          |                  |     | 0: The low-voltage detection circuit is not used (In standby mode)                                                                                                                                                             |

|        |          |                  |     | 1: The low-voltage detection circuit is used                                                                                                                                                                                   |

| 6 to 4 |          | All 1            |     | Reserved                                                                                                                                                                                                                       |

|        |          |                  |     | These bits are always read as 1 and cannot be modified.                                                                                                                                                                        |

| 3      | LVDSEL   | 0*               | R/W | LVDR Detection Level Select                                                                                                                                                                                                    |

|        |          |                  |     | 0: Reset detection voltage is 2.3 V (typ.)                                                                                                                                                                                     |

|        |          |                  |     | 1: Reset detection voltage is 3.6 V (typ.)                                                                                                                                                                                     |

|        |          |                  |     | When the falling or rising voltage detection interrupt is used, reset detection voltage of 2.3 V (typ.) should be used. When only a reset detection interrupt is used, reset detection voltage of 3.6 V (typ.) should be used. |

| 2      | LVDRE    | 0*               | R/W | LVDR Enable                                                                                                                                                                                                                    |

|        |          |                  |     | 0: Disables the LVDR function                                                                                                                                                                                                  |

|        |          |                  |     | 1: Enables the LVDR function                                                                                                                                                                                                   |

| 1      | LVDDE    | 0                | R/W | Voltage-Fall-Interrupt Enable                                                                                                                                                                                                  |

|        |          |                  |     | 0: Interrupt on the power-supply voltage falling below the<br>selected detection level disabled                                                                                                                                |

|        |          |                  |     | 1: Interrupt on the power-supply voltage falling below the selected detection level enabled                                                                                                                                    |

## 21.1 Register Addresses (Address Order)

The data-bus width column indicates the number of bits. The access-state column shows the number of states of the selected basic clock that is required for access to the register.

Note: Access to undefined or reserved addresses should not take place. Correct operation of the access itself or later operations is not guaranteed when such a register is accessed.

|                                   | Abbre-  |        |                     | Module  | Data<br>Bus | Access |  |

|-----------------------------------|---------|--------|---------------------|---------|-------------|--------|--|

| Register Name                     | viation | Bit No | Address             | Name    | Width       | State  |  |

| _                                 | —       |        | H'F000 to<br>H'F5FF | _       |             | —      |  |

| Master control register           | MCR     | 8      | H'F600              | TinyCAN | 8           | 4      |  |

| General status register           | GSR     | 8      | H'F601              | TinyCAN | 8           | 4      |  |

| Bit configuration register 1      | BCR1    | 8      | H'F602              | TinyCAN | 8           | 4      |  |

| Bit configuration register 0      | BCR0    | 8      | H'F603              | TinyCAN | 8           | 4      |  |

| Mailbox configuration register    | MBCR    | 8      | H'F604              | TinyCAN | 8           | 4      |  |

| TinyCAN module control register   | TCMR    | 8      | H'F605              | TinyCAN | 8           | 4      |  |

| Transmit pending register         | TXPR    | 8      | H'F606              | TinyCAN | 8           | 4      |  |

| Transmit pending cancel register  | TXCR    | 8      | H'F608              | TinyCAN | 8           | 4      |  |

| Transmit acknowledge register     | TXACK   | 8      | H'F60A              | TinyCAN | 8           | 4      |  |

| Abort acknowledge register        | ABACK   | 8      | H'F60C              | TinyCAN | 8           | 4      |  |

| Receive complete register         | RXPR    | 8      | H'F60E              | TinyCAN | 8           | 4      |  |

| Remote request register           | RFPR    | 8      | H'F610              | TinyCAN | 8           | 4      |  |

| TinyCAN interrupt register 1      | TCIRR1  | 8      | H'F612              | TinyCAN | 8           | 4      |  |

| TinyCAN interrupt register 0      | TCIRR0  | 8      | H'F613              | TinyCAN | 8           | 4      |  |

| Mailbox interrupt mask register   | MBIMR   | 8      | H'F614              | TinyCAN | 8           | 4      |  |

| TinyCAN interrupt mask register 1 | TCIMR1  | 8      | H'F616              | TinyCAN | 8           | 4      |  |

| TinyCAN interrupt mask register 0 | TCIMR0  | 8      | H'F617              | TinyCAN | 8           | 4      |  |

| Receive error counter             | REC     | 8      | H'F618              | TinyCAN | 8           | 4      |  |

| Transmit error counter            | TEC     | 8      | H'F619              | TinyCAN | 8           | 4      |  |

| Test control register             | TCR     | 8      | H'F61A              | TinyCAN | 8           | 4      |  |

| Unread message status register    | UMSR    | 8      | H'F61B              | TinyCAN | 8           | 4      |  |

| Message control 0 [0]             | MC0[0]  | 8      | H'F620              | TinyCAN | 8           | 4      |  |

| Register<br>Abbreviation | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | Module<br>Name |

|--------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------------|

| SSCRH                    | MSS      | BIDE     | SOOS     | SOL      | SOLP     | SCKS     | CSS1     | CSS0     | SSU            |

| SSCRL                    | MSTSSU   | SSUMS    | SRES     | SCKOS    | CSOS     | _        | _        | _        |                |

| SSMR                     | MLS      | CPOS     | CPHS     | _        | _        | CKS2     | CKS1     | CKS0     |                |

| SSER                     | TE       | RE       | RSSTP    | _        | TEIE     | TIE      | RIE      | CEIE     |                |

| SSSR                     | _        | ORER     | _        | _        | TEND     | TDRE     | RDRF     | CE       |                |

| SSRDR                    | SSRDR7   | SSRDR6   | SSRDR5   | SSRDR4   | SSRDR3   | SSRDR2   | SSRDR1   | SSRDR0   |                |

| SSTDR                    | SSTDR7   | SSTDR6   | SSTDR5   | SSTDR4   | SSTDR3   | SSTDR2   | SSTDR1   | SSTDR0   |                |

| SBTCTL                   | PCEF     | _        | _        | START    | OSCEB    | SYSCKS   | SBTIB    | SBTUF    | Subtimer       |

| SBTDCNT                  | SBTDCNT7 | SBTDCNT6 | SBTDCNT5 | SBTDCNT4 | SBTDCNT3 | SBTDCNT2 | SBTDCNT1 | SBTDCNT0 |                |

| ROPCR                    | ROPCR7   | ROPCR6   | ROPCR5   | ROPCR4   | ROPCR3   | ROPCR2   | ROPCR1   | ROPCR0   |                |

| TCR_0                    | CCLR2    | CCLR1    | CCLR0    | CKEG1    | CKEG0    | TPSC2    | TPSC1    | TPSC0    | Timer Z        |

| TIORA_0                  | _        | IOB2     | IOB1     | IOB0     | _        | IOA2     | IOA1     | IOA0     |                |

| TIORC_0                  | _        | IOD2     | IOD1     | IOD0     | _        | IOC2     | IOC1     | IOC0     |                |

| TSR_0                    | _        | _        | _        | OVF      | IMFD     | IMFC     | IMFB     | IMFA     |                |

| TIER_0                   | _        | _        | _        | OVIE     | IMIED    | IMIEC    | IMIEB    | IMIEA    |                |

| POCR_0                   | _        | _        | _        | _        | _        | POLD     | POLC     | POLB     |                |

| TCNT_0                   | TCNT0H7  | TCNT0H6  | TCNT0H5  | TCNT0H4  | TCNT0H3  | TCNT0H2  | TCNT0H1  | TCNT0H0  |                |

|                          | TCNT0L7  | TCNT0L6  | TCNT0L5  | TCNT0L4  | TCNT0L3  | TCNT0L2  | TCNT0L1  | TCNT0L0  |                |

| GRA_0                    | GRA0H7   | GRA0H6   | GRA0H5   | GRA0H4   | GRA0H3   | GRA0H2   | GRA0H1   | GRA0H0   |                |

|                          | GRA0L7   | GRA0L6   | GRA0L5   | GRA0L4   | GRA0L3   | GRA0L2   | GRA0L1   | GRA0L0   |                |

| GRB_0                    | GRB0H7   | GRB0H6   | GRB0H5   | GRB0H4   | GRB0H3   | GRB0H2   | GRB0H1   | GRB0H0   |                |

|                          | GRB0L7   | GRB0L6   | GRB0L5   | GRB0L4   | GRB0L3   | GRB0L2   | GRB0L1   | GRB0L0   |                |

| GRC_0                    | GRC0H7   | GRC0H6   | GRC0H5   | GRC0H4   | GRC0H3   | GRC0H2   | GRC0H1   | GRC0H0   |                |

|                          | GRC0L7   | GRC0L6   | GRC0L5   | GRC0L4   | GRC0L3   | GRC0L2   | GRC0L1   | GRC0L0   |                |

| GRD_0                    | GRD0H7   | GRD0H6   | GRD0H5   | GRD0H4   | GRD0H3   | GRD0H2   | GRD0H1   | GRD0H0   |                |

|                          | GRD0L7   | GRD0L6   | GRD0L5   | GRD0L4   | GRD0L3   | GRD0L2   | GRD0L1   | GRD0L0   |                |

| TCR_1                    | CCLR2    | CCLR1    | CCLR0    | CKEG1    | CKEG0    | TPSC2    | TPSC1    | TPSC0    |                |

| TIORA_1                  | _        | IOB2     | IOB1     | IOB0     | _        | IOA2     | IOA1     | IOA0     |                |

| TIORC_1                  | _        | IOD2     | IOD1     | IOD0     | _        | IOC2     | IOC1     | IOC0     |                |

| TSR_1                    | _        | _        | UDF      | OVF      | IMFD     | IMFC     | IMFB     | IMFA     |                |

| TIER_1                   | _        | _        | _        | OVIE     | IMIED    | IMIEC    | IMIEB    | IMIEA    |                |

| POCR_1                   | _        | _        | _        | _        | _        | POLD     | POLC     | POLB     |                |

## 22.3.3 AC Characteristics

#### Table 22.14 AC Characteristics

$V_{cc} = 2.7$  to 5.5 V,  $V_{ss} = 0.0$  V,  $T_a = -20$  to  $+75^{\circ}$ C (regular specifications) or  $T_a = -40$  to  $+85^{\circ}$ C (wide-range specifications), unless otherwise indicated.

|                                                          |                       | Applicable    |                                          |      | Value |       | Reference                               |             |

|----------------------------------------------------------|-----------------------|---------------|------------------------------------------|------|-------|-------|-----------------------------------------|-------------|

| Item                                                     | Symbol                | Pins          | Test Condition                           | Min. | Тур.  | Max.  | Unit                                    | Figure      |

| System clock                                             | f <sub>osc</sub>      | OSC1,         | VCC = 4.0 to 5.5 V                       | 2.0  | _     | 20.0  | MHz                                     | *1          |

| oscillation<br>frequency                                 |                       | OSC2          |                                          | 2.0  |       | 10.0  | _                                       |             |

| System clock (ø)                                         | t <sub>cyc</sub>      |               |                                          | 1    | —     | 64    | t <sub>osc</sub>                        | *2          |

| cycle time                                               |                       |               |                                          | —    | —     | 12.8  | μs                                      |             |

| Subclock oscillator<br>oscillation<br>frequency          | f <sub>ro</sub>       |               | V <sub>cc</sub> = 4.0 to 5.5 V           | 64.0 | —     | 850.0 | kHz                                     |             |

| Subclock oscillator<br>(\u00f6w) cycle time              | t <sub>RO</sub>       |               | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$ | 1.18 | —     | 15.6  | μs                                      |             |

| Subclock (øsub)<br>cycle time                            | $\mathbf{t}_{subcyc}$ |               | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$ | 2    | —     | 8     | φw                                      |             |

| Instruction cycle<br>time                                |                       |               |                                          | 2    | —     | _     | t <sub>cyc</sub><br>t <sub>subcyc</sub> |             |

| Oscillation<br>stabilization time<br>(crystal resonator) | t <sub>rc</sub>       | OSC1,<br>OSC2 |                                          | _    | _     | 10.0  | ms                                      |             |

| Oscillation<br>stabilization time<br>(ceramic resonator) | t <sub>rc</sub>       | OSC1,<br>OSC2 |                                          | _    | _     | 5.0   | ms                                      |             |

| External clock high                                      | t <sub>CPH</sub>      | OSC1          | $V_{\rm cc}$ = 4.0 to 5.5 V              | 20.0 | _     | _     | ns                                      | Figure 22.1 |

| width                                                    |                       |               |                                          | 40.0 | —     | —     | _                                       |             |

| External clock low                                       | t <sub>CPL</sub>      | OSC1          | $V_{\rm cc}$ = 4.0 to 5.5 V              | 20.0 | —     | —     | ns                                      | _           |

| width                                                    |                       |               |                                          | 40.0 | _     | _     | _                                       |             |

| External clock rise                                      | t <sub>CPr</sub>      | OSC1          | $V_{cc}$ = 4.0 to 5.5 V                  | _    | —     | 10.0  | ns                                      |             |

| time                                                     |                       |               |                                          | _    | _     | 15.0  |                                         | _           |

| External clock fall                                      | t <sub>CPf</sub>      | OSC1          | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$ | —    |       | 10.0  | ns                                      | _           |

| time                                                     |                       |               |                                          |      | —     | 15.0  |                                         |             |

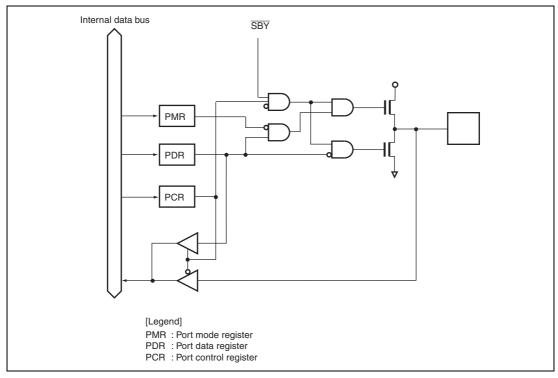

Figure B.9 Port 5 Block Diagram (P57, P56)