Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36054fzv |

|----------------------------|-----------------------------------------------------------------------------|

| Supplier Device Package    | -                                                                           |

| Package / Case             | -                                                                           |

| Mounting Type              | -                                                                           |

| Operating Temperature      | -                                                                           |

| Oscillator Type            | -                                                                           |

| Data Converters            | -                                                                           |

| Voltage - Supply (Vcc/Vdd) | -                                                                           |

| RAM Size                   | -                                                                           |

| EEPROM Size                | -                                                                           |

| Program Memory Type        | -                                                                           |

| Program Memory Size        | -                                                                           |

| Number of I/O              | -                                                                           |

| Peripherals                | -                                                                           |

| Connectivity               | -                                                                           |

| Speed                      | -                                                                           |

| Core Size                  | -                                                                           |

| Core Processor             | -                                                                           |

| Product Status             | Active                                                                      |

| Details                    |                                                                             |

| Appendix B I/O Port Block Diagrams           | 517 |

|----------------------------------------------|-----|

| B.1 I/O Port Block Diagrams                  | 517 |

| B.2 Port States in Each Operating State      | 544 |

| Appendix C Product Code Lineup               | 545 |

| Appendix D Package Dimensions                | 547 |

| Main Revisions and Additions in this Edition | 549 |

| Indov                                        | 553 |

# 2.4 Instruction Set

# 2.4.1 Table of Instructions Classified by Function

The H8/300H CPU has 62 instructions. Tables 2.2 to 2.9 summarize the instructions in each functional category. The notation used in tables 2.2 to 2.9 is defined below.

**Table 2.1 Operation Notation**

| Symbol        | Description                                            |

|---------------|--------------------------------------------------------|

| Rd            | General register (destination)*                        |

| Rs            | General register (source)*                             |

| Rn            | General register*                                      |

| ERn           | General register (32-bit register or address register) |

| (EAd)         | Destination operand                                    |

| (EAs)         | Source operand                                         |

| CCR           | Condition-code register                                |

| N             | N (negative) flag in CCR                               |

| Z             | Z (zero) flag in CCR                                   |

| V             | V (overflow) flag in CCR                               |

| С             | C (carry) flag in CCR                                  |

| PC            | Program counter                                        |

| SP            | Stack pointer                                          |

| #IMM          | Immediate data                                         |

| disp          | Displacement                                           |

| +             | Addition                                               |

| _             | Subtraction                                            |

| ×             | Multiplication                                         |

| ÷             | Division                                               |

| ٨             | Logical AND                                            |

| <u> </u>      | Logical OR                                             |

| $\oplus$      | Logical XOR                                            |

| $\rightarrow$ | Move                                                   |

| 7             | NOT (logical complement)                               |

| :3/:8/:16/:24 | 3-, 8-, 16-, or 24-bit length                          |

# 2.5 Addressing Modes and Effective Address Calculation

The following describes the H8/300H CPU. In this LSI, the upper eight bits are ignored in the generated 24-bit address, so the effective address is 16 bits.

#### 2.5.1 Addressing Modes

The H8/300H CPU supports the eight addressing modes listed in table 2.10. Each instruction uses a subset of these addressing modes. Addressing modes that can be used differ depending on the instruction. For details, refer to appendix A.4, Combinations of Instructions and Addressing Modes.

Arithmetic and logic instructions can use the register direct and immediate modes. Data transfer instructions can use all addressing modes except program-counter relative and memory indirect. Bit-manipulation instructions use register direct, register indirect, or the absolute addressing mode (@aa:8) to specify an operand, and register direct (BSET, BCLR, BNOT, and BTST instructions) or immediate (3-bit) addressing mode to specify a bit number in the operand.

**Table 2.10 Addressing Modes**

| No. | Addressing Mode                                                               | Symbol                  |

|-----|-------------------------------------------------------------------------------|-------------------------|

| 1   | Register direct                                                               | Rn                      |

| 2   | Register indirect                                                             | @ERn                    |

| 3   | Register indirect with displacement                                           | @(d:16,ERn)/@(d:24,ERn) |

| 4   | Register indirect with post-increment<br>Register indirect with pre-decrement | @ERn+<br>@-ERn          |

| 5   | Absolute address                                                              | @ aa:8/@ aa:16/@ aa:24  |

| 6   | Immediate                                                                     | #xx:8/#xx:16/#xx:32     |

| 7   | Program-counter relative                                                      | @(d:8,PC)/@(d:16,PC)    |

| 8   | Memory indirect                                                               | @@aa:8                  |

#### (1) Register Direct—Rn

The register field of the instruction specifies an 8-, 16-, or 32-bit general register containing the operand. R0H to R7H and R0L to R7L can be specified as 8-bit registers. R0 to R7 and E0 to E7 can be specified as 16-bit registers. ER0 to ER7 can be specified as 32-bit registers.

| Bit | Bit Name | Initial<br>Value | R/W | Description                    |  |  |  |

|-----|----------|------------------|-----|--------------------------------|--|--|--|

| 4   | TOA1     | 0                | R/W | Output Level Select A1         |  |  |  |

|     |          |                  |     | 0: 0 output at the FTIOA1 pin* |  |  |  |

|     |          |                  |     | 1: 1 output at the FTIOA1 pin* |  |  |  |

| 3   | TOD0     | 0                | R/W | Output Level Select D0         |  |  |  |

|     |          |                  |     | 0: 0 output at the FTIOD0 pin* |  |  |  |

|     |          |                  |     | 1: 1 output at the FTIOD0 pin* |  |  |  |

| 2   | TOC0     | 0                | R/W | Output Level Select C0         |  |  |  |

|     |          |                  |     | 0: 0 output at the FTIOC0 pin* |  |  |  |

|     |          |                  |     | 1: 1 output at the FTIOC0 pin* |  |  |  |

| 1   | TOB0     | 0                | R/W | Output Level Select B0         |  |  |  |

|     |          |                  |     | 0: 0 output at the FTIOB0 pin* |  |  |  |

|     |          |                  |     | 1: 1 output at the FTIOB0 pin* |  |  |  |

| 0   | TOA0     | 0                | R/W | Output Level Select A0         |  |  |  |

|     |          |                  |     | 0: 0 output at the FTIOA0 pin* |  |  |  |

|     |          |                  |     | 1: 1 output at the FTIOA0 pin* |  |  |  |

Note: \* The change of the setting is immediately reflected in the output value.

#### 12.3.7 Timer Counter (TCNT)

The timer Z has two TCNT counters (TCNT\_0 and TCNT\_1), one for each channel. The TCNT counters are 16-bit readable/writable registers that increment/decrement according to input clocks. Input clocks can be selected by bits TPSC2 to TPSC0 in TCR. TCNT0 and TCNT 1 increment/decrement in complementary PWM mode, while they only increment in other modes.

The TCNT counters are initialized to H'0000 by compare matches with corresponding GRA, GRB, GRC, or GRD, or input captures to GRA, GRB, GRC, or GRD (counter clearing function). When the TCNT counters overflow, an OVF flag in TSR for the corresponding channel is set to 1. When TCNT\_1 underflows, an UDF flag in TSR is set to 1. The TCNT counters cannot be accessed in 8-bit units; they must always be accessed as a 16-bit unit. TCNT is initialized to H'0000.

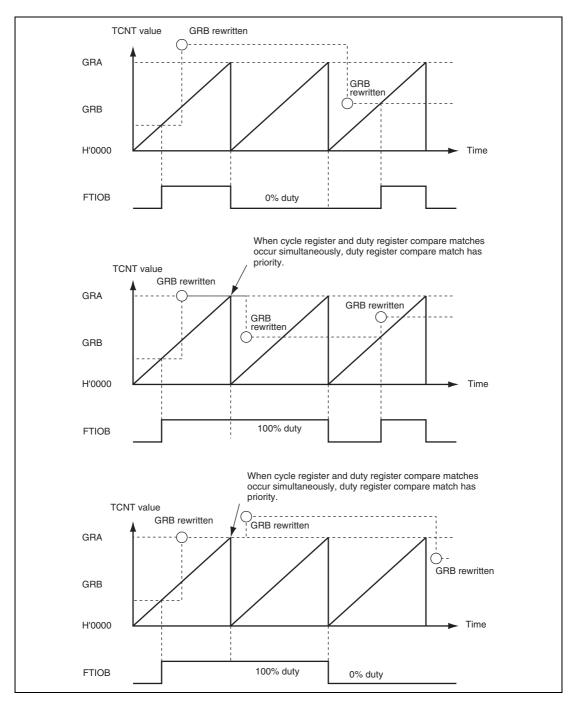

Figure 12.25 Example of PWM Mode Operation (4)

#### 12.4.6 Reset Synchronous PWM Mode

Three normal- and counter-phase PWM waveforms are output by combining channels 0 and 1 that one of changing points of waveforms will be common.

In reset synchronous PWM mode, the FTIOB0 to FTIOD0 and FTIOA1 to FTIOD1 pins become PWM-output pins automatically. TCNT\_0 performs an increment operation. Tables 12.4 and 12.5 show the PWM-output pins used and the register settings, respectively.

Figure 12.26 shows the example of reset synchronous PWM mode setting procedure.

Table 12.4 Output Pins in Reset Synchronous PWM Mode

| Channel | Pin Name | I/O    | Pin Function                                          |

|---------|----------|--------|-------------------------------------------------------|

| 0       | FTIOC0   | Output | Toggle output in synchronous with PWM cycle           |

| 0       | FTIOB0   | Output | PWM output 1                                          |

| 0       | FTIOD0   | Output | PWM output 1 (counter-phase waveform of PWM output 1) |

| 1       | FTIOA1   | Output | PWM output 2                                          |

| 1       | FTIOC1   | Output | PWM output 2 (counter-phase waveform of PWM output 2) |

| 1       | FTIOB1   | Output | PWM output 3                                          |

| 1       | FTIOD1   | Output | PWM output 3 (counter-phase waveform of PWM output 3) |

Table 12.5 Register Settings in Reset Synchronous PWM Mode

| Register | Description                                                                  |

|----------|------------------------------------------------------------------------------|

| TCNT_0   | Initial setting of H'0000                                                    |

| TCNT_1   | Not used (independently operates)                                            |

| GRA_0    | Sets counter cycle of TCNT_0                                                 |

| GRB_0    | Set a changing point of the PWM waveform output from pins FTIOB0 and FTIOD0. |

| GRA_1    | Set a changing point of the PWM waveform output from pins FTIOA1 and FTIOC1. |

| GRB_1    | Set a changing point of the PWM waveform output from pins FTIOB1 and FTIOD1. |

#### 14.5.5 Simultaneous Serial Data Transmission and Reception

Figure 14.14 shows a sample flowchart for simultaneous serial transmit and receive operations. The following procedure should be used for simultaneous serial data transmit and receive operations. To switch from transmit mode to simultaneous transmit and receive mode, after checking that the SCI3 has finished transmission and the TDRE and TEND flags are set to 1, clear TE to 0. Then simultaneously set TE and RE to 1 with a single instruction. To switch from receive mode to simultaneous transmit and receive mode, after checking that the SCI3 has finished reception, clear RE to 0. Then after checking that the RDRF and receive error flags (OER, FER, and PER) are cleared to 0, simultaneously set TE and RE to 1 with a single instruction.

# 15.3.5 Bit Configuration Registers 0, 1 (BCR0, BCR1)

BCR configures the CAN bit timing parameters and baud rate prescaler for the CDLC.

# • BCR0

|     |          | Initial |     |                                                            |  |  |  |

|-----|----------|---------|-----|------------------------------------------------------------|--|--|--|

| Bit | Bit Name | Value   | R/W | Description                                                |  |  |  |

| 7   | SJW1     | 0       | R/W | Re-Synchronization Jump Width                              |  |  |  |

| 6   | SJW0     | 0       | R/W | These bits set the maximum value of synchronization width. |  |  |  |

|     |          |         |     | 00: 1 time quantum                                         |  |  |  |

|     |          |         |     | 01: 2 time quanta                                          |  |  |  |

|     |          |         |     | 10: 3 time quanta                                          |  |  |  |

|     |          |         |     | 11: 4 time quanta                                          |  |  |  |

| 5   | BRP5     | 0       | R/W | Baud Rate Prescaler                                        |  |  |  |

| 4   | BRP4     | 0       | R/W | These bits set the clock used for time quanta.             |  |  |  |

| 3   | BRP3     | 0       | R/W | 000000: Setting prohibited                                 |  |  |  |

| 2   | BRP2     | 0       | R/W | 000001: 2 system clocks                                    |  |  |  |

| 1   | BRP1     | 0       | R/W | : : (BRP + 1) system clocks                                |  |  |  |

| 0   | BRP0     | 0       | R/W | 111111: 64 system clocks                                   |  |  |  |

#### • BCR1

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                       |

|-----|----------|------------------|-----|-------------------------------------------------------------------|

| 7   | _        | 0                | _   | Reserved                                                          |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0. |

# 15.4.2 Local Acceptance Filter Mask (LAFMHn1, LAFMHn0, LAFMLn1, LAFMLn0 [n = 0 to 3])

LAFM consists of four registers for one Mailbox. LAFM filters mask of bit-unit comparison between the message identifier of RXn (n=0 to 3) stored in the receive Mailbox and the receive message identifier. Since LAFM is in RAM, initial values are undefined after power-on. Be sure to initialize each bit by writing 0 or 1.

| Register                |        |                        |     |                                                                                                                                                              |

|-------------------------|--------|------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                    | Bit    | Bit Name               | R/W | Description                                                                                                                                                  |

| LAFMLn1                 | 7 to 0 | LAFMLn7 to             | R/W | Filter mask for bits 7 to 0 of the extended identifier.                                                                                                      |

| (n = 0 to 3)            |        | LAFMLn0                |     | Receive message is stored in RXn because the<br>RXn message identifier bits match the receive<br>message identifier bits                                     |

|                         |        |                        |     | Receive message is stored in RXn regardless of<br>whether the RXn message identifier bits match<br>the receive message identifier bits                       |

| LAFMLn0<br>(n = 0 to 3) | 7 to 0 | LAFMLn15 to<br>LAFMLn8 | R/W | Filter mask for bits 15 to 8 of the extended identifier.                                                                                                     |

|                         |        |                        |     | Receive message is stored in RXn because the<br>RXn message identifier bits match the receive<br>message identifier bits                                     |

|                         |        |                        |     | Receive message is stored in RXn regardless of<br>whether the RXn message identifier bits match<br>the receive message identifier bits                       |

| LAFMHn1                 | 7 to 5 | LAFMHn7 to             | R/W | Filter mask for bits 2 to 0 of the standard identifier.                                                                                                      |

| (n = 0 to 3)            |        | LAFMHn5                |     | Receive message is stored in RXn because the<br>RXn message identifier bits match the receive<br>message identifier bits                                     |

|                         |        |                        |     | <ol> <li>Receive message is stored in RXn regardless of<br/>whether the RXn message identifier bits match<br/>the receive message identifier bits</li> </ol> |

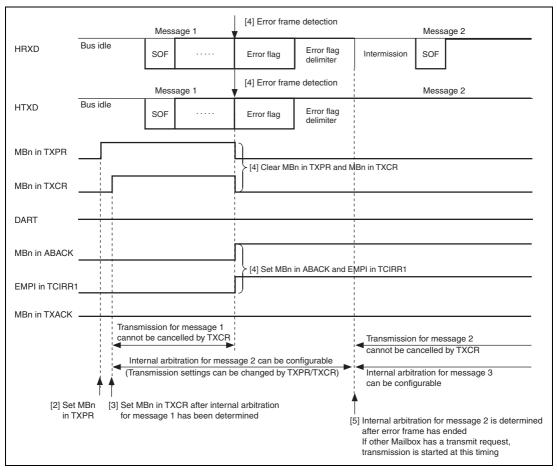

Figure 15.12 Internal Arbitration at Error Detection (MBn in TXCR = 1)

REJ09B0026-0400

#### 16.3.6 SS Receive Data Register (SSRDR)

SSRDR is an 8-bit register that stores received serial data. When the SSU has received one byte of serial data, it transfers the received serial data from SSTRSR and the data is stored. After this, SSTRSR is receive-enabled. As SSTRSR and SSRDR function as a double buffer in this way, continuous receive operations are possible. SSRDR is a read-only register and cannot be written to by the CPU. SSRDR is initialized to H'00.

#### 16.3.7 SS Transmit Data Register (SSTDR)

SSTDR is an 8-bit register that stores serial data for transmission. SSTDR can be read or written to by the CPU at all times. When the SSU detects that SSTRSR is empty, it transfers the transmit data written in SSTDR to SSTRSR and starts serial transmission. If the next transmit data has already been written to SSTDR during serial transmission, continuous serial transmission is possible. SSTDR is initialized to H'00.

#### 16.3.8 SS Shift Register (SSTRSR)

SSTRSR is a shift register that transmits and receives serial data. When transmit data is transferred from SSTDR to SSTRSR, bit 0 in SSTDR is transferred to bit 0 in SSTRSR while the MLS bit in SSMR is 0 (LSB-first transfer) and bit 7 in SSTDR is transferred to bit 0 in SSTRSR while the MLS bit in SSMR is 1 (MSB-first transfer). SSTRSR cannot be directly accessed by the CPU.

# 18.3.2 A/D Control/Status Register (ADCSR)

ADCSR consists of the control bits and conversion end status bits of the A/D converter.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                               |

|-----|----------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ADF      | 0                | R/W | A/D End Flag                                                                                                                                                                                                                                                                                                              |

|     |          |                  |     | [Setting conditions]                                                                                                                                                                                                                                                                                                      |

|     |          |                  |     | <ul> <li>When A/D conversion ends in single mode</li> </ul>                                                                                                                                                                                                                                                               |

|     |          |                  |     | <ul> <li>When A/D conversion ends once on all the channels<br/>selected in scan mode</li> </ul>                                                                                                                                                                                                                           |

|     |          |                  |     | [Clearing condition]                                                                                                                                                                                                                                                                                                      |

|     |          |                  |     | <ul> <li>When 0 is written after reading ADF = 1</li> </ul>                                                                                                                                                                                                                                                               |

| 6   | ADIE     | 0                | R/W | A/D Interrupt Enable                                                                                                                                                                                                                                                                                                      |

|     |          |                  |     | A/D conversion end interrupt request (ADI) is enabled by ADF when this bit is set to 1                                                                                                                                                                                                                                    |

| 5   | ADST     | 0                | R/W | A/D Start                                                                                                                                                                                                                                                                                                                 |

|     |          |                  |     | Setting this bit to 1 starts A/D conversion. In single mode, this bit is cleared to 0 automatically when conversion on the specified channel is complete. In scan mode, conversion continues sequentially on the specified channels until this bit is cleared to 0 by software, a reset, or a transition to standby mode. |

| 4   | SCAN     | 0                | R/W | Scan Mode                                                                                                                                                                                                                                                                                                                 |

|     |          |                  |     | Selects single mode or scan mode as the A/D conversion operating mode.                                                                                                                                                                                                                                                    |

|     |          |                  |     | 0: Single mode                                                                                                                                                                                                                                                                                                            |

|     |          |                  |     | 1: Scan mode                                                                                                                                                                                                                                                                                                              |

| 3   | CKS      | 0                | R/W | Clock Select                                                                                                                                                                                                                                                                                                              |

|     |          |                  |     | Selects the A/D conversions time.                                                                                                                                                                                                                                                                                         |

|     |          |                  |     | 0: Conversion time = 134 states (max.)                                                                                                                                                                                                                                                                                    |

|     |          |                  |     | 1: Conversion time = 70 states (max.)                                                                                                                                                                                                                                                                                     |

|     |          |                  |     | Clear the ADST bit to 0 before switching the conversion time.                                                                                                                                                                                                                                                             |

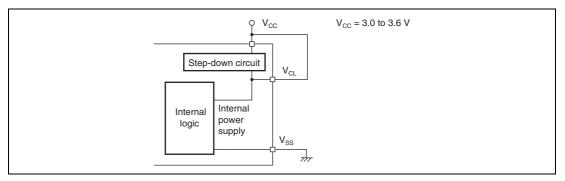

# 20.2 When Not Using Internal Power Supply Step-Down Circuit

When the internal power supply step-down circuit is not used, connect the external power supply to the  $V_{\text{cl.}}$  pin and  $V_{\text{cc}}$  pin, as shown in figure 20.2. The external power supply is then input directly to the internal power supply. The permissible range for the power supply voltage is 3.0 V to 3.6 V. Operation cannot be guaranteed if a voltage outside this range (less than 3.0 V or more than 3.6 V) is input.

Figure 20.2 Power Supply Connection when Internal Step-Down Circuit is Not Used

#### 22.3.3 AC Characteristics

#### **Table 22.14 AC Characteristics**

$V_{cc}$  = 2.7 to 5.5 V,  $V_{ss}$  = 0.0 V,  $T_a$  = -20 to +75°C (regular specifications) or  $T_a$  = -40 to +85°C (wide-range specifications), unless otherwise indicated.

|                                                          |                       | Applicable    |                                          |      | Value | s     | _                                       | Reference   |

|----------------------------------------------------------|-----------------------|---------------|------------------------------------------|------|-------|-------|-----------------------------------------|-------------|

| Item                                                     | Symbol                | Pins          | Test Condition                           | Min. | Тур.  | Max.  | Unit                                    | Figure      |

| System clock                                             | f <sub>osc</sub>      | OSC1,         | VCC = 4.0 to 5.5 V                       | 2.0  | _     | 20.0  | MHz                                     | *1          |

| oscillation frequency                                    |                       | OSC2          |                                          | 2.0  |       | 10.0  | _                                       |             |

| System clock (¢)                                         | t <sub>cyc</sub>      |               |                                          | 1    | _     | 64    | t <sub>osc</sub>                        | *2          |

| cycle time                                               |                       |               |                                          | _    | _     | 12.8  | μs                                      |             |

| Subclock oscillator oscillation frequency                | $f_{RO}$              |               | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$ | 64.0 | _     | 850.0 | kHz                                     |             |

| Subclock oscillator (φw) cycle time                      | t <sub>RO</sub>       |               | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$ | 1.18 | _     | 15.6  | μs                                      |             |

| Subclock (\psi sub) cycle time                           | t <sub>subcyc</sub>   |               | $V_{CC} = 4.0 \text{ to } 5.5 \text{ V}$ | 2    | _     | 8     | φw                                      |             |

| Instruction cycle time                                   |                       |               |                                          | 2    | _     | _     | t <sub>cyc</sub><br>t <sub>subcyc</sub> |             |

| Oscillation<br>stabilization time<br>(crystal resonator) | t <sub>rc</sub>       | OSC1,<br>OSC2 |                                          | _    | _     | 10.0  | ms                                      |             |

| Oscillation<br>stabilization time<br>(ceramic resonator) | t <sub>rc</sub>       | OSC1,<br>OSC2 |                                          | _    | _     | 5.0   | ms                                      |             |

| External clock high                                      | t <sub>CPH</sub>      | OSC1          | $V_{CC} = 4.0 \text{ to } 5.5 \text{ V}$ | 20.0 | _     | _     | ns                                      | Figure 22.1 |

| width                                                    |                       |               |                                          | 40.0 | _     | _     |                                         | _           |

| External clock low                                       | $t_{_{\mathrm{CPL}}}$ | OSC1          | $V_{CC} = 4.0 \text{ to } 5.5 \text{ V}$ | 20.0 | _     | _     | ns                                      |             |

| width                                                    |                       |               |                                          | 40.0 | _     | _     |                                         |             |

| External clock rise                                      | $t_{_{CPr}}$          | OSC1          | $V_{CC} = 4.0 \text{ to } 5.5 \text{ V}$ | _    | _     | 10.0  | ns                                      |             |

| time                                                     |                       |               |                                          | _    | _     | 15.0  |                                         | =           |

| External clock fall                                      | $\mathbf{t}_{CPf}$    | OSC1          | $V_{CC} = 4.0 \text{ to } 5.5 \text{ V}$ | _    | _     | 10.0  | ns                                      |             |

| time                                                     |                       |               |                                          | _    | _     | 15.0  |                                         |             |

#### 22.3.6 Power-Supply-Voltage Detection Circuit Characteristics (Optional)

#### Table 22.20 Power-Supply-Voltage Detection Circuit Characteristics

$V_{ss} = 0.0 \text{ V}$ ,  $T_a = -20 \text{ to } +75^{\circ}\text{C}$  (regular specifications) or  $T_a = -40 \text{ to } +85^{\circ}\text{C}$  (wide-range specifications), unless otherwise indicated.

|                                         |                                  | Test                                                      |      | Values | ;    | _    |

|-----------------------------------------|----------------------------------|-----------------------------------------------------------|------|--------|------|------|

| Item                                    | Symbol                           | Condition                                                 | Min. | Тур.   | Max. | Unit |

| Power-supply falling detection voltage  | Vint (D)                         | LVDSEL = 0                                                | 3.3  | 3.7    | _    | V    |

| Power-supply rising detection voltage   | Vint (U)                         | LVDSEL = 0                                                | _    | 4.0    | 4.5  | V    |

| Reset detection voltage 1*1             | Vreset1                          | LVDSEL = 0                                                | _    | 2.3    | 2.7  | V    |

| Reset detection voltage 2*2             | Vreset2                          | LVDSEL = 1                                                | 3.0  | 3.6    | 4.2  | V    |

| Lower-limit voltage of LVDR operation*3 | $V_{\scriptscriptstyle LVDRmin}$ |                                                           | 1.0  |        | _    | V    |

| LVD stabilization time                  | t <sub>lvdon</sub>               |                                                           | 50   |        | _    | μs   |

| Supply current in standby mode          | I <sub>STBY</sub>                | LVDE = 1,<br>Vcc = 5.0 V,<br>subtimer and<br>WDT not used | _    | _      | 350  | μА   |

Notes: 1. This voltage should be used when the falling and rising voltage detection function is used.

- 2. Select the low-voltage reset 2 when only the low-voltage detection reset is used.

- 3. When the power-supply voltage (Vcc) falls below  $V_{\text{\tiny LVDRmin}} = 1.0 \text{ V}$  and then rises, a reset may not occur. Therefore sufficient evaluation is required.

# 22.3.7 Power-On Reset Circuit Characteristics (Optional)

#### Table 22.21 Power-On Reset Circuit Characteristics

$V_{ss}$  = 0.0 V,  $T_a$  = -20 to +75°C (regular specifications) or  $T_a$  = -40 to +85°C (wide-range specifications), unless otherwise indicated.

|                               |                  | Test      | Values |      |      |      |

|-------------------------------|------------------|-----------|--------|------|------|------|

| Item                          | Symbol           | Condition | Min.   | Тур. | Max. | Unit |

| Pull-up resistance of RES pin | R <sub>RES</sub> |           | 100    | 150  | _    | kΩ   |

| Power-on reset start voltage* | $V_{por}$        |           | _      | _    | 100  | mV   |

Note: \* The power-supply voltage (Vcc) must fall below Vpor = 100 mV and then rise after charge of the RES pin is removed completely. In order to remove charge of the RES pin, it is recommended that the diode be placed in the Vcc side. If the power-supply voltage (Vcc) rises from the point over 100 mV, a power-on reset may not occur.

| Instruction | Mnemonic           | Instruction<br>Fetch | Branch<br>Addr. Read<br>J | Stack<br>Operation<br>K | Byte Data<br>Access<br>L | Word Data<br>Access<br>M | Internal<br>Operation<br>N |

|-------------|--------------------|----------------------|---------------------------|-------------------------|--------------------------|--------------------------|----------------------------|

| Всс         | BLT d:8            | 2                    |                           |                         |                          |                          |                            |

|             | BGT d:8            | 2                    |                           |                         |                          |                          |                            |

|             | BLE d:8            | 2                    |                           |                         |                          |                          |                            |

|             | BRA d:16(BT d:16)  | 2                    |                           |                         |                          |                          | 2                          |

|             | BRN d:16(BF d:16)  | 2                    |                           |                         |                          |                          | 2                          |

|             | BHI d:16           | 2                    |                           |                         |                          |                          | 2                          |

|             | BLS d:16           | 2                    |                           |                         |                          |                          | 2                          |

|             | BCC d:16(BHS d:16) | 2                    |                           |                         |                          |                          | 2                          |

|             | BCS d:16(BLO d:16) | 2                    |                           |                         |                          |                          | 2                          |

|             | BNE d:16           | 2                    |                           |                         |                          |                          | 2                          |

|             | BEQ d:16           | 2                    |                           |                         |                          |                          | 2                          |

|             | BVC d:16           | 2                    |                           |                         |                          |                          | 2                          |

|             | BVS d:16           | 2                    |                           |                         |                          |                          | 2                          |

|             | BPL d:16           | 2                    |                           |                         |                          |                          | 2                          |

|             | BMI d:16           | 2                    |                           |                         |                          |                          | 2                          |

|             | BGE d:16           | 2                    |                           |                         |                          |                          | 2                          |

|             | BLT d:16           | 2                    |                           |                         |                          |                          | 2                          |

|             | BGT d:16           | 2                    |                           |                         |                          |                          | 2                          |

|             | BLE d:16           | 2                    |                           |                         |                          |                          | 2                          |

| BCLR        | BCLR #xx:3, Rd     | 1                    |                           |                         |                          |                          |                            |

|             | BCLR #xx:3, @ERd   | 2                    |                           |                         | 2                        |                          |                            |

|             | BCLR #xx:3, @aa:8  | 2                    |                           |                         | 2                        |                          |                            |

|             | BCLR Rn, Rd        | 1                    |                           |                         |                          |                          |                            |

|             | BCLR Rn, @ERd      | 2                    |                           |                         | 2                        |                          |                            |

|             | BCLR Rn, @aa:8     | 2                    |                           |                         | 2                        |                          |                            |

| BIAND       | BIAND #xx:3, Rd    | 1                    |                           |                         |                          |                          |                            |

|             | BIAND #xx:3, @ERd  | 2                    |                           |                         | 1                        |                          |                            |

|             | BIAND #xx:3, @aa:8 | 2                    |                           |                         | 1                        |                          |                            |

| BILD        | BILD #xx:3, Rd     | 1                    |                           |                         |                          |                          |                            |

|             | BILD #xx:3, @ERd   | 2                    |                           |                         | 1                        |                          |                            |

|             | BILD #xx:3, @aa:8  | 2                    |                           |                         | 1                        |                          |                            |

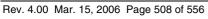

# Appendix D Package Dimensions

The package dimensions that are shown in the Renesas Semiconductor Packages Data Book have priority.

Figure D.1 FP-64K Package Dimensions

| Item                                                                              | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12.3.7 Timer Counter (TCNT)                                                       | 177  | Added                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                   |      | The TCNT counters cannot be accessed in 8-bit units; they must always be accessed as a 16-bit unit. TCNT is initialized to H'0000.                                                                                                                                                                                                                    |

| Figure 12.17 Example of Input<br>Capture Operation                                | 196  | Amended  Counter cleared by FTIOB input (falling edge)  Time                                                                                                                                                                                                                                                                                          |

|                                                                                   |      |                                                                                                                                                                                                                                                                                                                                                       |

| 12.4.4 Synchronous Operation                                                      | 199  | Added Figure 12.20 shows an example of synchronous operation. In this example, set for the channel 1 counter clearing source. In addition, the same input clock has been set as the counter input clock for channel 0 and channel 1. Two-phase PWM waveforms are                                                                                      |

| Figure 12.44 Example of Output<br>Disable Timing of Timer Z by<br>Writing to TOER | 229  | Address bus  TOER  Timer Z output pin  Timer Z output  Timer Z output |

# Index

| A                                        | Reset exception handling               | 59  |

|------------------------------------------|----------------------------------------|-----|

| A/D converter                            | Stack status                           | 63  |

| Sample-and-hold circuit                  | Trap instruction                       | 49  |

| Scan mode                                |                                        |     |

| Single mode                              |                                        |     |

| Address break                            | G                                      |     |

| Addressing modes                         | General registers                      | 15  |

| Absolute address                         | 5                                      |     |

| Immediate                                |                                        |     |

| Memory indirect34                        | I                                      |     |

| Program-counter relative34               | I/O ports                              | 111 |

| Register direct32                        | Instruction set                        |     |

| Register indirect33                      | Arithmetic operations instructions     |     |

| Register indirect with displacement 33   | Bit manipulation instructions          |     |

| Register indirect with post-increment 33 | Block data transfer instructions       |     |

| Register indirect with pre-decrement 33  | Branch instructions                    |     |

|                                          | Data transfer instructions             |     |

|                                          | Logic operations instructions          |     |

| C                                        | Shift instructions                     |     |

| Clock pulse generators                   | System control instructions            |     |

| Prescaler S                              | Internal power supply Step-down        | 2)  |

| System clock generator74                 | circuit                                | 413 |

| Condition field31                        | Interrupt                              |     |

| Condition-code register (CCR)            | Internal interrupts                    | 61  |

| Controller area network (TinyCAN) 295    | Interrupt response time                |     |

| Mailbox340                               | IRQ3 to IRQ0 interrupts                |     |

| Message reception                        | NMI interrupt                          |     |

| Message transmission 327                 | WKP5 to WKP0 interrupts                |     |

| Time Quanta 326                          | Interrupt mask bit                     |     |

| TinyCAN standby transition               | 1                                      |     |

| CPU9                                     |                                        |     |

|                                          | L                                      |     |

|                                          | Large current ports                    | 2   |

| E                                        | Low-voltage detection circuit          |     |

| Effective address                        | LVDI (interrupt by low voltage detect) |     |

| Effective address extension              | circuit                                |     |

| Exception handling                       | Circuit                                | 710 |

| т - г                                    |                                        |     |