#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                    |

| Core Size                  | 16-Bit                                                                     |

| Speed                      | 20MHz                                                                      |

| Connectivity               | CANbus, SCI, SSU                                                           |

| Peripherals                | PWM, WDT                                                                   |

| Number of I/O              | 45                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-BQFP                                                                    |

| Supplier Device Package    | 64-QFP (14x14)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36054hv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# 16 H8/36057Group, H8/36037Group

# Hardware Manual

Renesas 16-Bit Single-Chip Microcomputer H8 Family/H8/300H Tiny Series

| 1119/110/30011 |                         |

|----------------|-------------------------|

| H8/36057       | HD64F36057, HD64F36057G |

|                | HD64336057, HD64336057G |

| H8/36054       | HD64F36054, HD64F36054G |

|                | HD64336054, HD64336054G |

| H8/36037       | HD64F36037, HD64F36037G |

|                | HD64336037, HD64336037G |

| H8/36036       | HD64336036, HD64336036G |

| H8/36035       | HD64336035, HD64336035G |

| H8/36034       | HD64F36034, HD64F36034G |

|                | HD64336034, HD64336034G |

| H8/36033       | HD64336033, HD64336033G |

| H8/36032       | HD64336032, HD64336032G |

|                |                         |

## Renesas Electronics

Rev.4.00 2006.05

Rev. 4.00 Mar. 15, 2006 Page ii of xxxii

| Figure 5.6 Example of External Clock Input                                                                           | 75  |

|----------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.7 Example of Incorrect Board Design                                                                         | 76  |

| Section 6 Power-Down Modes                                                                                           |     |

| Figure 6.1 Mode Transition Diagram                                                                                   | 82  |

|                                                                                                                      |     |

| Section 7 ROM<br>Figure 7.1 Flash Memory Block Configuration                                                         | 00  |

| Figure 7.1 Prash Memory Block Configuration<br>Figure 7.2 Programming/Erasing Flowchart Example in User Program Mode |     |

| Figure 7.2 Program/Program-Verify Flowchart                                                                          |     |

| Figure 7.4 Erase/Erase-Verify Flowchart                                                                              |     |

|                                                                                                                      | 104 |

| Section 9 I/O Ports                                                                                                  |     |

| Figure 9.1 Port 1 Pin Configuration                                                                                  |     |

| Figure 9.2 Port 2 Pin Configuration                                                                                  |     |

| Figure 9.3 Port 5 Pin Configuration                                                                                  |     |

| Figure 9.4 Port 6 Pin Configuration                                                                                  |     |

| Figure 9.5 Port 7 Pin Configuration                                                                                  |     |

| Figure 9.6 Port 8 Pin Configuration                                                                                  |     |

| Figure 9.7 Port 9 Pin Configuration                                                                                  |     |

| Figure 9.8 Port B Pin Configuration                                                                                  | 141 |

| Section 10 Timer B1                                                                                                  |     |

| Figure 10.1 Block Diagram of Timer B1                                                                                | 143 |

| Section 11 Timer V                                                                                                   |     |

| Figure 11.1 Block Diagram of Timer V                                                                                 | 150 |

| Figure 11.2 Increment Timing with Internal Clock                                                                     |     |

| Figure 11.3 Increment Timing with External Clock                                                                     |     |

| Figure 11.4 OVF Set Timing                                                                                           |     |

| Figure 11.5 CMFA and CMFB Set Timing                                                                                 |     |

| Figure 11.6 TMOV Output Timing                                                                                       |     |

| Figure 11.7 Clear Timing by Compare Match                                                                            |     |

| Figure 11.8 Clear Timing by TMRIV Input                                                                              |     |

| Figure 11.9 Pulse Output Example                                                                                     |     |

| Figure 11.10 Example of Pulse Output Synchronized to TRGV Input                                                      |     |

| Figure 11.11 Contention between TCNTV Write and Clear                                                                |     |

| Figure 11.12 Contention between TCORA Write and Compare Match                                                        |     |

| Figure 11.13 Internal Clock Switching and TCNTV Operation                                                            | 162 |

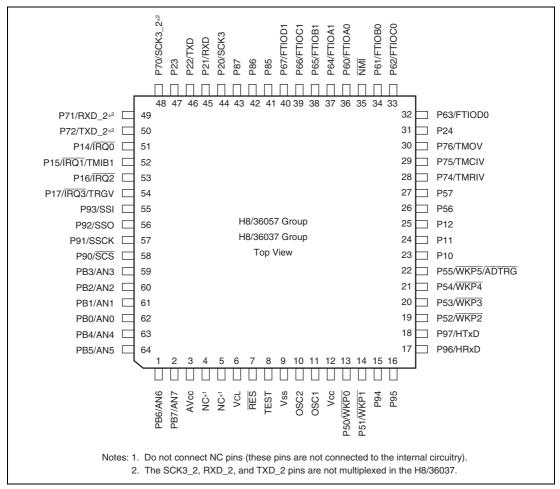

### **1.3** Pin Arrangement

Figure 1.2 Pin Arrangement of F-ZTAT<sup>™</sup> and Masked ROM Versions (FP-64K, FP-64A)

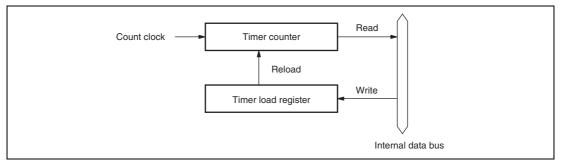

The timer is counting, so the value read is not necessarily the same as the value in the timer load register. As a result, bits other than the intended bit in the timer counter may be modified and the modified value may be written to the timer load register.

# Figure 2.13 Example of Timer Configuration with Two Registers Allocated to Same Address

#### Example 2: The BSET instruction is executed for port 5.

P57 and P56 are input pins, with a low-level signal input at P57 and a high-level signal input at P56. P55 to P50 are output pins and output low-level signals. An example to output a high-level signal at P50 with a BSET instruction is shown below.

|              | P57          | P56           | P55          | P54          | P53          | P52          | P51          | P50          |

|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Input/output | Input        | Input         | Output       | Output       | Output       | Output       | Output       | Output       |

| Pin state    | Low<br>level | High<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level |

| PCR5         | 0            | 0             | 1            | 1            | 1            | 1            | 1            | 1            |

| PDR5         | 1            | 0             | 0            | 0            | 0            | 0            | 0            | 0            |

• Prior to executing BSET instruction

• BSET instruction executed instruction

BSET #0, @PDR5

The BSET instruction is executed for port 5.

### 6.1.4 Module Standby Control Register 2 (MSTCR2)

MSTCR2 allows the on-chip peripheral modules to enter a standby state in module units.

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                                                     |

|------|----------|------------------|-----|---------------------------------------------------------------------------------|

| 7    | MSTS3_2  | 0                | R/W | SCI3_2 Module Standby                                                           |

|      |          |                  |     | The SCI3_2 enters standby mode when this bit is set to 1.                       |

|      |          |                  |     | Note: This bit is reserved in the H8/36037 Group. This bit is always read as 0. |

| 6, 5 | _        | All 0            |     | Reserved                                                                        |

|      |          |                  |     | These bits are always read as 0.                                                |

| 4    | MSTTB1   | 0                | R/W | Timer B1 Module Standby                                                         |

|      |          |                  |     | The timer B1 enters standby mode when this bit is set to 1.                     |

| 3, 2 | _        | All 0            |     | Reserved                                                                        |

|      |          |                  |     | These bits are always read as 0.                                                |

| 1    | MSTTZ    | 0                | R/W | Timer Z Module Standby                                                          |

|      |          |                  |     | The timer Z enters standby mode when this bit is set to 1.                      |

| 0    | _        | 0                |     | Reserved                                                                        |

|      |          |                  |     | This bit is always read as 0.                                                   |

• P72/TXD\_2\* pin

| Register      | PMR1* | PCR7  |                   |

|---------------|-------|-------|-------------------|

| Bit Name      | TXD2* | PCR72 | Pin Function      |

| Setting Value | 0     | 0     | P72 input pin     |

|               |       | 1     | P72 output pin    |

|               | 1     | Х     | TXD_2 output pin* |

### [Legend]

#### X: Don't care.

Note: \* The H8/36037 Group does not have this pin.

• P71/RXD\_2\* pin

| Register      | SCR3_2* | PCR7  |                  |

|---------------|---------|-------|------------------|

| Bit Name      | RE*     | PCR71 | Pin Function     |

| Setting Value | 0       | 0     | P71 input pin    |

|               |         | 1     | P71 output pin   |

|               | 1       | Х     | RXD_2 input pin* |

#### [Legend]

X: Don't care.

Note: \* The H8/36037 Group does not have this pin.

• P70/SCK3\_2\* pin

| Register      | SCR3_2 | <u>2</u> * | SMR2* | PCR7  |                    |

|---------------|--------|------------|-------|-------|--------------------|

| Bit Name      | CKE1*  | CKE0*      | COM*  | PCR70 | Pin Function       |

| Setting Value | 0      | 0          | 0     | 0     | P70 input pin      |

|               |        |            |       | 1     | P70 output pin     |

|               | 0      | 0          | 1     | Х     | SCK3_2 output pin* |

|               | 0      | 1          | Х     | Х     | SCK3_2 output pin* |

|               | 1      | Х          | Х     | Х     | SCK3_2 input pin*  |

[Legend]

X: Don't care.

Note: \* The H8/36037 Group does not have these pins.

RENESAS

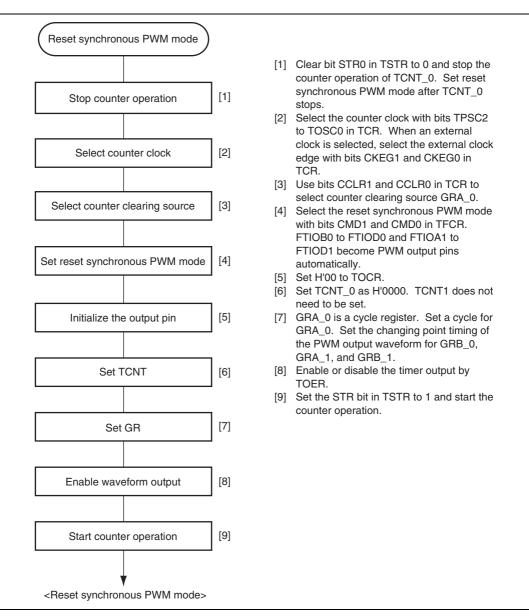

Section 12 Timer Z

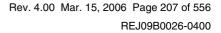

Figure 12.43 Buffer Operation (4) (Buffer Operation in Complementary PWM Mode CMD1 = CMD0 = 1)

|                     | Operating Frequency φ (MHz) |     |              |   |     |              |  |  |  |

|---------------------|-----------------------------|-----|--------------|---|-----|--------------|--|--|--|

|                     | 18                          |     |              |   |     |              |  |  |  |

| Bit Rate<br>(bit/s) | n                           | N   | Error<br>(%) | n | N   | Error<br>(%) |  |  |  |

| 110                 | 3                           | 79  | -0.12        | 3 | 88  | -0.25        |  |  |  |

| 150                 | 2                           | 233 | 0.14         | 3 | 64  | 0.14         |  |  |  |

| 300                 | 2                           | 114 | 0.14         | 2 | 129 | 0.14         |  |  |  |

| 600                 | 1                           | 233 | 0.14         | 2 | 64  | 0.14         |  |  |  |

| 1200                | 1                           | 114 | 0.14         | 1 | 129 | 0.14         |  |  |  |

| 2400                | 0                           | 233 | 0.14         | 1 | 64  | 0.14         |  |  |  |

| 4800                | 0                           | 114 | 0.14         | 0 | 129 | 0.14         |  |  |  |

| 9600                | 0                           | 58  | -0.96        | 0 | 64  | 0.14         |  |  |  |

| 19200               | 0                           | 28  | 1.02         | 0 | 32  | -1.36        |  |  |  |

| 31250               | 0                           | 17  | 0.00         | 0 | 19  | 0.00         |  |  |  |

| 38400               | 0                           | 14  | -2.34        | 0 | 15  | 1.73         |  |  |  |

Operating Frequency  $\phi$  (MHz)

[Legend]

-: A setting is available but error occurs.

| Table 14.4 Maximum Bit Rate for Each Frequency (Asynchronous Mo |

|-----------------------------------------------------------------|

|-----------------------------------------------------------------|

| φ (MHz)  | Maximum Bit<br>Rate (bit/s) | n | N | φ (MHz) | Maximum Bit<br>Rate (bit/s) | n | N |

|----------|-----------------------------|---|---|---------|-----------------------------|---|---|

| 2        | 62500                       | 0 | 0 | 8       | 250000                      | 0 | 0 |

| 2.097152 | 65536                       | 0 | 0 | 9.8304  | 307200                      | 0 | 0 |

| 2.4576   | 76800                       | 0 | 0 | 10      | 312500                      | 0 | 0 |

| 3        | 93750                       | 0 | 0 | 12      | 375000                      | 0 | 0 |

| 3.6864   | 115200                      | 0 | 0 | 12.288  | 384000                      | 0 | 0 |

| 4        | 125000                      | 0 | 0 | 14      | 437500                      | 0 | 0 |

| 4.9152   | 153600                      | 0 | 0 | 14.7456 | 460800                      | 0 | 0 |

| 5        | 156250                      | 0 | 0 | 14      | 500000                      | 0 | 0 |

| 6        | 187500                      | 0 | 0 | 17.2032 | 537600                      | 0 | 0 |

| 6.144    | 192000                      | 0 | 0 | 18      | 562500                      | 0 | 0 |

| 7.3728   | 230400                      | 0 | 0 | 20      | 625000                      | 0 | 0 |

RENESAS

# Table 14.5Examples of BRR Settings for Various Bit Rates (Clocked Synchronous Mode)<br/>(2)

|          | Operating Frequency φ (MF |     |    |     |  |  |  |

|----------|---------------------------|-----|----|-----|--|--|--|

| Bit Rate |                           | 18  | 20 |     |  |  |  |

| (bit/s)  | n                         | Ν   | n  | Ν   |  |  |  |

| 110      | _                         | _   | _  | _   |  |  |  |

| 250      | _                         | _   | _  | _   |  |  |  |

| 500      | 3                         | 140 | 3  | 155 |  |  |  |

| 1k       | 3                         | 69  | 3  | 77  |  |  |  |

| 2.5k     | 2                         | 112 | 2  | 124 |  |  |  |

| 5k       | 1                         | 224 | 1  | 249 |  |  |  |

| 10k      | 1                         | 112 | 1  | 124 |  |  |  |

| 25k      | 0                         | 179 | 0  | 199 |  |  |  |

| 50k      | 0                         | 89  | 0  | 99  |  |  |  |

| 100k     | 0                         | 44  | 0  | 49  |  |  |  |

| 250k     | 0                         | 17  | 0  | 19  |  |  |  |

| 500k     | 0                         | 8   | 0  | 9   |  |  |  |

| 1M       | 0                         | 4   | 0  | 4   |  |  |  |

| 2M       | _                         |     | _  | _   |  |  |  |

| 2.5M     | _                         | _   | 0  | 1   |  |  |  |

| 4M       | _                         | —   | —  | _   |  |  |  |

[Legend]

Blank: No setting is available.

-: A setting is available but error occurs.

\*: Continuous transfer is not possible.

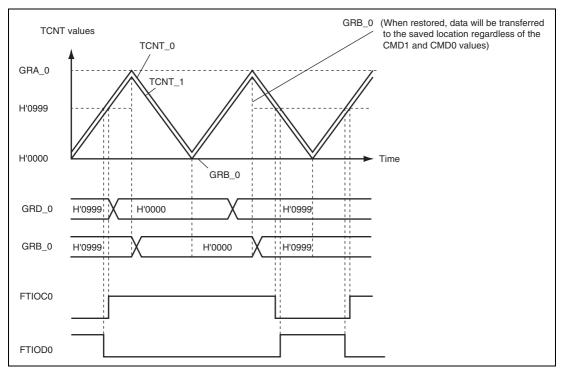

Figure 14.11 Sample Serial Transmission Flowchart (Clocked Synchronous Mode)

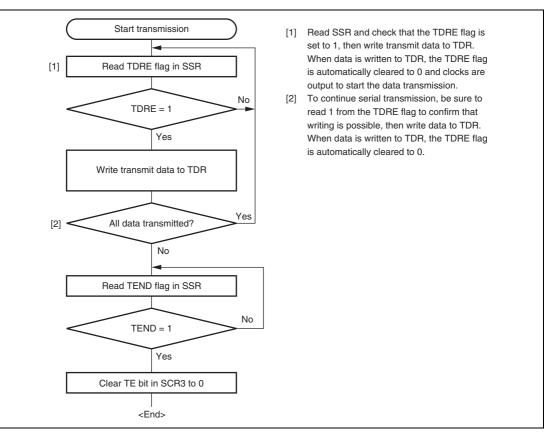

Figure 15.7 Internal Arbitration at Transmission Caused by TXCR/TXPR Setting

Arbitration Lost during Message Transmission: If an arbitration loss on the CAN bus occurs, the TinyCAN halts transmission, and starts message reception. If the DART bit for the transmission-requested message is cleared to 0, on the completion of reception, the transmission-requested message is retransmitted. However, if the DART bit is set to 1, it is not transmitted in frame 2. Figures 15.8 to 15.10 show the timings of the arbitration loss on the CAN bus. Procedure and operation are as follows.

- 1. Write data of a transmit message to MCn0, MCn4 to MCn7, and MDn0 to MDn7 [n = 1 to 3] before clearing the MBn bit in MBCR corresponding to the Mailbox of the transmit message to 0 (initial setting).

- 2. Set the corresponding MBn bit in TXPR to 1 (start condition issuance). Then, the start condition is generated.

- 3. The internal arbitration for message 1 is determined and the transmit message is transferred to the temporary buffer. After that, even if a transmit request cancellation is issued to the message being transmitted by the DART or MBn bit in TXCR, message 1 is transmitted continuously unless the TinyCAN detects an arbitration loss or error on the CAN bus.

|                                                                                                                                                                                                                                                |                                        | Data frame reception                         | Remote frame reception |         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------|------------------------|---------|

| MBn in RXPR                                                                                                                                                                                                                                    |                                        |                                              | jį                     |         |

| DFRI in TCIRR0                                                                                                                                                                                                                                 |                                        |                                              | ji                     |         |

| MBn in RFPR                                                                                                                                                                                                                                    |                                        |                                              |                        |         |

| RFRI in TCIRR0                                                                                                                                                                                                                                 |                                        |                                              | ſ                      |         |

| MBn in UMSR                                                                                                                                                                                                                                    |                                        |                                              |                        |         |

| OVRI in TCIRR1                                                                                                                                                                                                                                 |                                        |                                              |                        |         |

| RTR in MCn4                                                                                                                                                                                                                                    |                                        |                                              | ſ                      |         |

| CPU access                                                                                                                                                                                                                                     | Other module                           |                                              | •                      | TinyCAN |

| Case 2: Overwrite (NM                                                                                                                                                                                                                          | MC = 1, 1st: Remote Fi                 | rame, 2nd: Data Frame)                       |                        |         |

|                                                                                                                                                                                                                                                |                                        | Remote frame reception                       | Data frame reception   |         |

| MBn in RXPR                                                                                                                                                                                                                                    |                                        |                                              | r                      |         |

| DFRI in TCIRR0                                                                                                                                                                                                                                 |                                        |                                              | ſ                      |         |

| MBn in RFPR                                                                                                                                                                                                                                    |                                        |                                              | į į                    |         |

| RFRI in TCIRR0                                                                                                                                                                                                                                 |                                        |                                              | ii                     |         |

| MBn in UMSR                                                                                                                                                                                                                                    |                                        |                                              | ſ                      |         |

| OVRI in TCIRR1                                                                                                                                                                                                                                 |                                        |                                              | ſ                      |         |

| RTR in MCn4                                                                                                                                                                                                                                    |                                        |                                              | i i                    |         |

|                                                                                                                                                                                                                                                |                                        |                                              |                        |         |

|                                                                                                                                                                                                                                                | Other module<br>C = 0, 1st: Data Frame |                                              |                        | TinyCAN |

| Case 3: Overrun (NM                                                                                                                                                                                                                            |                                        | , 2nd: Remote Frame)<br>Data frame reception | Remote frame reception | TinyCAN |

| Case 3: Overrun (NM                                                                                                                                                                                                                            |                                        |                                              | Remote frame reception | TinyCAN |

| Case 3: Overrun (NM<br>MBn in RXPR<br>DFRI in TCIRR0                                                                                                                                                                                           |                                        |                                              | Remote frame reception | TinyCAN |

| Case 3: Overrun (NM<br>MBn in RXPR<br>DFRI in TCIRR0 _<br>MBn in RFPR                                                                                                                                                                          |                                        |                                              | Remote frame reception | TinyCAN |

| Case 3: Overrun (NM<br>MBn in RXPR<br>DFRI in TCIRR0<br>MBn in RFPR<br>RFRI in TCIRR0                                                                                                                                                          |                                        |                                              | Remote frame reception | TinyCAN |

| Case 3: Overrun (NM<br>MBn in RXPR<br>DFRI in TCIRR0<br>MBn in RFPR<br>RFRI in TCIRR0<br>MBn in UMSR                                                                                                                                           |                                        |                                              | Remote frame reception | TinyCAN |

| Case 3: Overrun (NMC<br>MBn in RXPR<br>DFRI in TCIRR0<br>MBn in RFPR<br>RFRI in TCIRR0<br>MBn in UMSR<br>OVRI in TCIRR1                                                                                                                        |                                        |                                              | Remote frame reception | TinyCAN |

| Case 3: Overrun (NMC<br>MBn in RXPR<br>DFRI in TCIRR0<br>MBn in RFPR<br>RFRI in TCIRR0<br>MBn in UMSR<br>OVRI in TCIRR1<br>RTR in MCn4                                                                                                         |                                        |                                              | Remote frame reception | TinyCAN |

| Case 3: Overrun (NMC<br>MBn in RXPR<br>DFRI in TCIRR0<br>MBn in RFPR<br>RFRI in TCIRR0<br>MBn in UMSR<br>OVRI in TCIRR1<br>RTR in MCn4<br>CPU access                                                                                           | C = 0, 1st: Data Frame                 | Data frame reception                         | Remote frame reception |         |

| Case 3: Overrun (NMC<br>MBn in RXPR<br>DFRI in TCIRR0<br>MBn in RFPR<br>RFRI in TCIRR0<br>MBn in UMSR<br>OVRI in TCIRR1<br>RTR in MCn4<br>CPU access                                                                                           | C = 0, 1st: Data Frame                 | Data frame reception                         | Remote frame reception |         |

| Case 3: Overrun (NMC<br>MBn in RXPR<br>DFRI in TCIRR0<br>MBn in RFPR<br>RFRI in TCIRR0<br>MBn in UMSR<br>OVRI in TCIRR1<br>RTR in MCn4<br>CPU access<br>Case 4: Overrun (NMC                                                                   | C = 0, 1st: Data Frame                 | Data frame reception                         |                        |         |

| Case 3: Overrun (NMC<br>MBn in RXPR<br>DFRI in TCIRR0<br>MBn in RFPR<br>RFRI in TCIRR0<br>MBn in UMSR<br>OVRI in TCIRR1<br>RTR in MCn4<br>CPU access<br>Case 4: Overrun (NMC<br>MBn in RXPR                                                    | C = 0, 1st: Data Frame                 | Data frame reception                         |                        |         |

| Case 3: Overrun (NMC<br>MBn in RXPR<br>DFRI in TCIRR0<br>MBn in RFPR<br>RFRI in TCIRR0<br>MBn in UMSR<br>OVRI in TCIRR1<br>CPU access<br>Case 4: Overrun (NMC<br>MBn in RXPR<br>DFRI in TCIRR0                                                 | C = 0, 1st: Data Frame                 | Data frame reception                         |                        |         |

| Case 3: Overrun (NMC<br>MBn in RXPR<br>DFRI in TCIRR0<br>MBn in RFPR<br>RFRI in TCIRR0<br>MBn in UMSR<br>OVRI in TCIRR1<br>CPU access<br>Case 4: Overrun (NMC<br>MBn in RXPR<br>DFRI in TCIRR0<br>MBn in RFPR                                  | C = 0, 1st: Data Frame                 | Data frame reception                         |                        |         |

| Case 3: Overrun (NMC<br>MBn in RXPR<br>DFRI in TCIRR0<br>MBn in RFPR<br>RFRI in TCIRR0<br>MBn in UMSR<br>OVRI in TCIRR1<br>CPU access<br>Case 4: Overrun (NMC<br>MBn in RXPR<br>DFRI in TCIRR0<br>MBn in RFPR<br>RFRI in TCIRR0                | C = 0, 1st: Data Frame                 | Data frame reception                         |                        |         |

| Case 3: Overrun (NMC<br>MBn in RXPR<br>DFRI in TCIRR0<br>MBn in RFPR<br>RFRI in TCIRR0<br>MBn in UMSR<br>OVRI in TCIRR1<br>CPU access<br>Case 4: Overrun (NMC<br>MBn in RXPR<br>DFRI in TCIRR0<br>MBn in RFPR<br>RFRI in TCIRR0<br>MBn in UMSR | C = 0, 1st: Data Frame                 | Data frame reception                         |                        |         |

| MBn in RXPR<br>DFRI in TCIRR0<br>MBn in RFPR<br>RFRI in TCIRR0<br>MBn in UMSR<br>OVRI in TCIRR1<br>RTR in MCn4<br>CPU access                                                                                                                   | C = 0, 1st: Data Frame                 | Data frame reception                         |                        |         |

Figure 15.16 RXPR/RFPR Set/Clear Timing when Overrun/Overwrite Occurs

### 16.3.6 SS Receive Data Register (SSRDR)

SSRDR is an 8-bit register that stores received serial data. When the SSU has received one byte of serial data, it transfers the received serial data from SSTRSR and the data is stored. After this, SSTRSR is receive-enabled. As SSTRSR and SSRDR function as a double buffer in this way, continuous receive operations are possible. SSRDR is a read-only register and cannot be written to by the CPU. SSRDR is initialized to H'00.

### 16.3.7 SS Transmit Data Register (SSTDR)

SSTDR is an 8-bit register that stores serial data for transmission. SSTDR can be read or written to by the CPU at all times. When the SSU detects that SSTRSR is empty, it transfers the transmit data written in SSTDR to SSTRSR and starts serial transmission. If the next transmit data has already been written to SSTDR during serial transmission, continuous serial transmission is possible. SSTDR is initialized to H'00.

### 16.3.8 SS Shift Register (SSTRSR)

SSTRSR is a shift register that transmits and receives serial data. When transmit data is transferred from SSTDR to SSTRSR, bit 0 in SSTDR is transferred to bit 0 in SSTRSR while the MLS bit in SSMR is 0 (LSB-first transfer) and bit 7 in SSTDR is transferred to bit 0 in SSTRSR while the MLS bit in SSMR is 1 (MSB-first transfer). SSTRSR cannot be directly accessed by the CPU.

Instruction code:

| byte  | BL |  |

|-------|----|--|

| 2nd   | BH |  |

| oyte  | AL |  |

| 1st l | ΥH |  |

| ш      | Table A.2<br>(3)            |     | INC  |     |      |      |       |       | EXTS |     | DEC  |          | BGT BLE |     |        |

|--------|-----------------------------|-----|------|-----|------|------|-------|-------|------|-----|------|----------|---------|-----|--------|

|        | ble A.2<br>(3)              |     | INC  |     |      |      |       |       | EXTS |     | DEC  |          | BLT B(  |     |        |

| O      | Table A.2 Table A.2 (3) (3) | Δ   |      | >   |      |      |       |       |      | Ē   |      | <u>د</u> | BGE     |     |        |

| ш      |                             | ADD |      | MOV | SHAL | SHAR | ROTL  | ROTR  | NEG  | SUB |      | CMP      | BMI     |     |        |

| A      |                             |     |      |     |      |      |       |       |      |     |      |          | BPL     |     |        |

| ര      |                             |     | ADDS |     | SHAL | SHAR | ROTL  | ROTR  | NEG  |     | SUB  |          | BVS     |     |        |

| œ      | SLEEP                       |     | AC   |     | Ś    | Ś    | Я     | RC    | z    |     | ō    |          | BVC     |     |        |

| 2      |                             |     | INC  |     |      |      |       |       | EXTU |     | DEC  |          | BEQ     |     |        |

| 9      |                             |     |      |     |      |      |       |       |      |     |      |          | BNE     | AND |        |

| ى<br>ا |                             |     | INC  |     |      |      |       |       | EXTU |     | DEC  |          | BCS     | XOR | aOX    |

| 4      | LDC/STC                     |     |      |     |      |      |       |       |      |     |      |          | BCC     | OR  | 6      |

| m      |                             |     |      |     | SHLL | SHLR | ROTXL | ROTXR | NOT  |     |      |          | BLS     | SUB | u<br>u |

| 7      |                             |     |      |     |      |      |       |       |      |     |      |          | BHI     | CMP | dWC    |

| -      |                             |     |      |     | SHLL | SHLR | ROTXL | ROTXR | NOT  |     |      |          | BRN     | ADD |        |

| 0      | MOV                         | INC | ADDS | DAA | ō    | ъ    | RC    | RC    | z    | DEC | SUBS | DAS      | BRA     | MOV | NOM    |

| AH AL  | 01                          | OA  | OB   | OF  | 10   | 1    | 12    | 13    | 17   | 1A  | 1B   | Ť        | 58      | 62  | ~~     |

#### Table A.2 **Operation Code Map (2)**

|       | •                  | Instruction<br>Fetch | Addr. Read |   | Byte Data<br>Access | Word Data<br>Access | Internal<br>Operation |

|-------|--------------------|----------------------|------------|---|---------------------|---------------------|-----------------------|

|       |                    | 1                    | J          | к | L                   | Μ                   | N                     |

| BIOR  | BIOR #xx:8, Rd     | 1                    |            |   | _                   |                     |                       |

|       | BIOR #xx:8, @ERd   | 2                    |            |   | 1                   |                     |                       |

|       | BIOR #xx:8, @aa:8  | 2                    |            |   | 1                   |                     |                       |

| BIST  | BIST #xx:3, Rd     | 1                    |            |   |                     |                     |                       |

|       | BIST #xx:3, @ERd   | 2                    |            |   | 2                   |                     |                       |

|       | BIST #xx:3, @aa:8  | 2                    |            |   | 2                   |                     |                       |

| BIXOR | BIXOR #xx:3, Rd    | 1                    |            |   |                     |                     |                       |

|       | BIXOR #xx:3, @ERd  | 2                    |            |   | 1                   |                     |                       |

|       | BIXOR #xx:3, @aa:8 | 2                    |            |   | 1                   |                     |                       |

| BLD   | BLD #xx:3, Rd      | 1                    |            |   |                     |                     |                       |

|       | BLD #xx:3, @ERd    | 2                    |            |   | 1                   |                     |                       |

|       | BLD #xx:3, @aa:8   | 2                    |            |   | 1                   |                     |                       |

| BNOT  | BNOT #xx:3, Rd     | 1                    |            |   |                     |                     |                       |

|       | BNOT #xx:3, @ERd   | 2                    |            |   | 2                   |                     |                       |

|       | BNOT #xx:3, @aa:8  | 2                    |            |   | 2                   |                     |                       |

|       | BNOT Rn, Rd        | 1                    |            |   |                     |                     |                       |

|       | BNOT Rn, @ERd      | 2                    |            |   | 2                   |                     |                       |

|       | BNOT Rn, @aa:8     | 2                    |            |   | 2                   |                     |                       |

| BOR   | BOR #xx:3, Rd      | 1                    |            |   |                     |                     |                       |

|       | BOR #xx:3, @ERd    | 2                    |            |   | 1                   |                     |                       |

|       | BOR #xx:3, @aa:8   | 2                    |            |   | 1                   |                     |                       |

| BSET  | BSET #xx:3, Rd     | 1                    |            |   |                     |                     |                       |

|       | BSET #xx:3, @ERd   | 2                    |            |   | 2                   |                     |                       |

|       | BSET #xx:3, @aa:8  | 2                    |            |   | 2                   |                     |                       |

|       | BSET Rn, Rd        | 1                    |            |   |                     |                     |                       |

|       | BSET Rn, @ERd      | 2                    |            |   | 2                   |                     |                       |

|       | BSET Rn, @aa:8     | 2                    |            |   | 2                   |                     |                       |

| BSR   | BSR d:8            | 2                    |            | 1 |                     |                     |                       |

|       | BSR d:16           | 2                    |            | 1 |                     |                     | 2                     |

| BST   | BST #xx:3, Rd      | 1                    |            |   |                     |                     |                       |

|       | BST #xx:3, @ERd    | 2                    |            |   | 2                   |                     |                       |

|       | BST #xx:3, @aa:8   | 2                    |            |   | 2                   |                     |                       |

|       |                    |                      |            |   |                     |                     |                       |

RENESAS

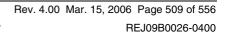

Figure B.4 Port 1 Block Diagram (P12, P11, P10)

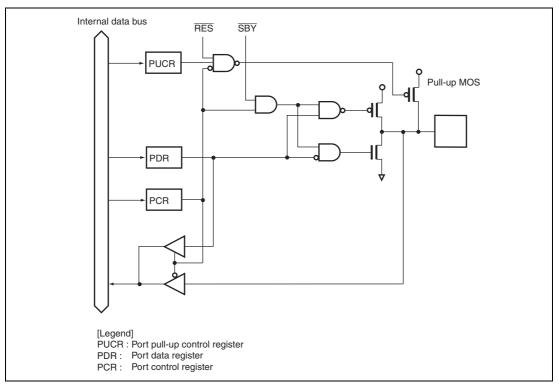

Figure B.5 Port 2 Block Diagram (P24, P23)

| Item                                                                                                                                                                                                         | Page             | Revision (See Manual for Details)                                                                                                                          |                 |                                        |                                                        |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------|--------------------------------------------------------|--|--|--|

| Table 22.2 DC Characteristics (1)                                                                                                                                                                            |                  |                                                                                                                                                            |                 |                                        |                                                        |  |  |  |

| Table 22.12 DC Characteristics (1)                                                                                                                                                                           | 468              | Note: 3. Pin states during current consumption<br>measurement are given below (excluding<br>current in the pull-up MOS transistors and<br>output buffers). |                 |                                        |                                                        |  |  |  |

|                                                                                                                                                                                                              |                  | Mode                                                                                                                                                       | RES Pin         | in Internal State                      |                                                        |  |  |  |

|                                                                                                                                                                                                              |                  | Active mode 1                                                                                                                                              | V <sub>cc</sub> | Operates                               |                                                        |  |  |  |

|                                                                                                                                                                                                              |                  | Active mode 2                                                                                                                                              | _               | Operates (¢                            | o <sub>osc</sub> /64)                                  |  |  |  |

|                                                                                                                                                                                                              |                  | Sleep mode 1                                                                                                                                               | V <sub>cc</sub> | Only timers                            | operate                                                |  |  |  |

|                                                                                                                                                                                                              |                  | Sleep mode 2                                                                                                                                               | _               | Only timers operate( $\phi_{osc}/64$ ) |                                                        |  |  |  |

|                                                                                                                                                                                                              |                  |                                                                                                                                                            |                 |                                        |                                                        |  |  |  |

| Figure 22.8 SSU Input/Output<br>Timing (Four-Line Bus<br>Communication Mode, Master,<br>CPHS = 1)<br>to<br>Figure 22.11 SSU Input/Output<br>Timing (Four-Line Bus<br>Communication Mode, Slave,<br>CPHS = 0) | 481<br>to<br>484 | t <sub>oн</sub> deleted                                                                                                                                    |                 |                                        |                                                        |  |  |  |

| Table A.1 Instruction Set                                                                                                                                                                                    | 491              | Amended                                                                                                                                                    |                 |                                        |                                                        |  |  |  |

| 2. Arithmetic Instructions                                                                                                                                                                                   |                  | Mnemonic                                                                                                                                                   | Operand Size    | lition Code                            | Vo. of<br>States <sup>*1</sup><br>Advanced<br>Advanced |  |  |  |

|                                                                                                                                                                                                              |                  | DAA DAA Rd                                                                                                                                                 | B - *           | \$ \$ * \$                             | 2                                                      |  |  |  |