#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

|                            | Obsolete          |

|----------------------------|-------------------|

| Coro Brocossor             |                   |

| COTE FIOCESSOI             | H8/300H           |

| Core Size                  | 16-Bit            |

| Speed                      | 20MHz             |

| Connectivity               | CANbus, SCI, SSU  |

| Peripherals                | PWM, WDT          |

| Number of I/O              | 45                |

| Program Memory Size        | 56KB (56K x 8)    |

| Program Memory Type        | FLASH             |

| EEPROM Size                | -                 |

| RAM Size                   | 3K x 8            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V         |

| Data Converters            | A/D 8x10b         |

| Oscillator Type            | Internal          |

| Operating Temperature      | -40°C ~ 85°C (TA) |

| Mounting Type              | Surface Mount     |

| Package / Case             | 64-BQFP           |

| Supplier Device Package    | 64-QFP (14x14)    |

|                            |                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Figures

| Section 1   | Overview                                                                         |    |

|-------------|----------------------------------------------------------------------------------|----|

| Figure 1.1  | Internal Block Diagram of F-ZTAT <sup>TM</sup> and Masked ROM Versions           | 3  |

| Figure 1.2  | Pin Arrangement of F-ZTAT <sup>TM</sup> and Masked ROM Versions (FP-64K, FP-64A) | 4  |

| Section 2   | СРИ                                                                              |    |

| Figure 2.1  | Memory Map (1)                                                                   | 11 |

| Figure 2.1  | Memory Map (2)                                                                   |    |

| Figure 2.1  | Memory Map (3)                                                                   | 13 |

| Figure 2.2  | CPU Registers                                                                    | 14 |

| Figure 2.3  | Usage of General Registers                                                       | 15 |

| Figure 2.4  | Relationship between Stack Pointer and Stack Area                                | 16 |

| Figure 2.5  | General Register Data Formats (1)                                                | 18 |

| Figure 2.5  | General Register Data Formats (2)                                                | 19 |

| Figure 2.6  | Memory Data Formats                                                              | 20 |

| Figure 2.7  | Instruction Formats                                                              | 31 |

| Figure 2.8  | Branch Address Specification in Memory Indirect Mode                             | 35 |

| Figure 2.9  | On-Chip Memory Access Cycle                                                      | 38 |

| Figure 2.10 | On-Chip Peripheral Module Access Cycle (3-State Access)                          | 39 |

| Figure 2.11 | CPU Operation States                                                             | 40 |

| Figure 2.12 | State Transitions                                                                | 41 |

| Figure 2.13 | Example of Timer Configuration with Two Registers Allocated to Same              |    |

|             | Address                                                                          | 43 |

| Section 3   | Exception Handling                                                               |    |

|             | Reset Sequence                                                                   | 61 |

| -           | Stack Status after Exception Handling                                            |    |

| Figure 3.3  | Interrupt Sequence                                                               | 64 |

| Figure 3.4  | Port Mode Register Setting and Interrupt Request Flag Clearing Procedure         | 65 |

| Section 4   | Address Break                                                                    |    |

| Figure 4.1  | Block Diagram of Address Break                                                   | 67 |

| Figure 4.2  | Address Break Interrupt Operation Example (1)                                    | 71 |

| -           | Address Break Interrupt Operation Example (2)                                    |    |

| Section 5   | Clock Pulse Generators                                                           |    |

| Figure 5.1  | Block Diagram of Clock Pulse Generators                                          | 73 |

| -           | Block Diagram of System Clock Generator                                          |    |

|             | Typical Connection to Crystal Resonator                                          |    |

| Figure 5.4  | Equivalent Circuit of Crystal Resonator                                          | 74 |

# RENESAS

#### 3.2.4 Interrupt Enable Register 2 (IENR2)

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                  |

|--------|----------|------------------|-----|--------------------------------------------------------------------------------------------------------------|

| 7, 6   | _        | All 0            | _   | Reserved                                                                                                     |

|        |          |                  |     | These bits are always read as 0.                                                                             |

| 5      | IENTB1   | 0                | R/W | Timer B1 Interrupt Enable<br>When this bit is set to 1, timer B1 overflow interrupt<br>requests are enabled. |

| 4 to 0 |          | All 1            | —   | Reserved                                                                                                     |

|        |          |                  |     | These bits are always read as 1.                                                                             |

IENR2 enables, timer B1 overflow interrupts.

When disabling interrupts by clearing bits in an interrupt enable register, or when clearing bits in an interrupt flag register, always do so while interrupts are masked (I = 1). If the above clear operations are performed while I = 0, and as a result a conflict arises between the clear instruction and an interrupt request, exception handling for the interrupt will be executed after the clear instruction has been executed.

#### 3.2.5 Interrupt Flag Register 1 (IRR1)

IRR1 is a status flag register for direct transition interrupts and IRQ3 to IRQ0 interrupt requests.

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                                                                       |

|------|----------|------------------|-----|---------------------------------------------------------------------------------------------------|

| 7    | IRRDT    | 0                | R/W | Direct Transfer Interrupt Request Flag                                                            |

|      |          |                  |     | [Setting condition]                                                                               |

|      |          |                  |     | When a direct transfer is made by executing a SLEEP instruction while DTON in SYSCR2 is set to 1. |

|      |          |                  |     | [Clearing condition]                                                                              |

|      |          |                  |     | When IRRDT is cleared by writing 0                                                                |

| 6    | _        | 0                |     | Reserved                                                                                          |

|      |          |                  |     | This bit is always read as 0.                                                                     |

| 5, 4 | _        | All 1            |     | Reserved                                                                                          |

|      |          |                  |     | These bits are always read as 1.                                                                  |

## Section 6 Power-Down Modes

This LSI has six modes of operation after a reset. These include a normal active mode and four power-down modes, in which power consumption is significantly reduced. Module standby mode reduces power consumption by selectively halting on-chip module functions.

Active mode

The CPU and all on-chip peripheral modules are operable on the system clock. The system clock frequency can be selected from  $\phi$ osc,  $\phi$ osc/8,  $\phi$ osc/16,  $\phi$ osc/32, and  $\phi$ osc/64.

Subactive mode

The CPU and all on-chip peripheral modules are operable on the subclock. The subclock frequency can be selected from  $\phi w/2$ ,  $\phi w/4$ , and  $\phi w/8$ .

• Sleep mode

The CPU halts. On-chip peripheral modules are operable on the system clock.

Subsleep mode

The CPU halts. On-chip peripheral modules are operable on the subclock.

• Standby mode

The CPU and all on-chip peripheral modules halt.

• Module standby mode

Independent of the above modes, power consumption can be reduced by halting on-chip peripheral modules that are not used in module units.

| Program Data | Verify Data | Reprogram Data | Comments                |

|--------------|-------------|----------------|-------------------------|

| 0            | 0           | 1              | Programming completed   |

| 0            | 1           | 0              | Reprogram bit           |

| 1            | 0           | 1              | _                       |

| 1            | 1           | 1              | Remains in erased state |

#### Table 7.4 Reprogram Data Computation Table

#### Table 7.5 Additional-Program Data Computation Table

| Reprogram Data | Verify Data | Additional-Program<br>Data | Comments                  |

|----------------|-------------|----------------------------|---------------------------|

| 0              | 0           | 0                          | Additional-program bit    |

| 0              | 1           | 1                          | No additional programming |

| 1              | 0           | 1                          | No additional programming |

| 1              | 1           | 1                          | No additional programming |

#### Table 7.6Programming Time

| n<br>(Number of Writes) | Programming<br>Time | In Additional<br>Programming | Comments |  |

|-------------------------|---------------------|------------------------------|----------|--|

| 1 to 6                  | 30                  | 10                           |          |  |

| 7 to 1,000              | 200                 | _                            |          |  |

Note: Time shown in  $\mu$ s.

| Section 9 I/O P | orts  |                |  |

|-----------------|-------|----------------|--|

|                 |       |                |  |

| • P11 pin       |       |                |  |

| Register        | PCR1  |                |  |

| Bit Name        | PCR11 | Pin Function   |  |

| Setting value   | 0     | P11 input pin  |  |

|                 | 1     | P11 output pin |  |

|                 |       |                |  |

| • P10 pin       |       |                |  |

| Register        | PCR1  |                |  |

| Bit Name        | PCR10 | Pin Function   |  |

| Setting value   | 0     | P10 input pin  |  |

|                 | 1     | P10 output pin |  |

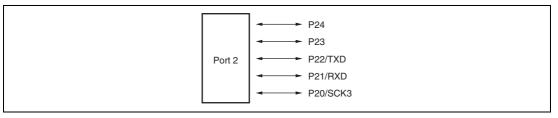

#### 9.2 Port 2

1/0

Port 2 is a general I/O port also functioning as SCI3 I/O pins. Each pin of the port 2 is shown in figure 9.2. The register settings of PMR1 and SCI3 have priority for functions of the pins for both uses.

Figure 9.2 Port 2 Pin Configuration

Port 2 has the following registers.

- Port control register 2 (PCR2)

- Port data register 2 (PDR2)

- Port mode register 3 (PMR3)

### • P62/FTIOC0 pin

| Register      | TOER | TFCR          | TPMR       | TIORC0          | PCR6  |                            |

|---------------|------|---------------|------------|-----------------|-------|----------------------------|

| Bit Name      | EC0  | CMD1,<br>CMD0 | PWMC0      | IOC2 to<br>IOC0 | PCR62 | -<br>Pin Function          |

| Setting Value | 1    | 00            | 0 000 or 0 |                 | 0     | P62 input/FTIOC0 input pin |

|               |      |               |            | 1XX             | 1     | P62 output pin             |

|               | 0    | 00            | 0          | 001 or<br>01X   | х     | FTIOC0 output pin          |

|               |      |               | 1          | XXX             | _     |                            |

|               |      | Other than 00 | Х          | XXX             | _     |                            |

#### [Legend]

X: Don't care.

• P61/FTIOB0 pin

| Register           | TOER | TFCR          | TPMR   | TIORA0          | PCR6                       |                   |

|--------------------|------|---------------|--------|-----------------|----------------------------|-------------------|

| Bit Name           | EB0  | CMD1,<br>CMD0 | PWMB0  | IOB2 to<br>IOB0 | PCR61                      | -<br>Pin Function |

| Setting Value 1 00 | 00   | 0             | 000 or | 0               | P61 input/FTIOB0 input pin |                   |

|                    |      |               |        | 1XX             | 1                          | P61 output pin    |

|                    | 0    | 00            | 0      | 001 or<br>01X   | Х                          | FTIOB0 output pin |

|                    |      |               | 1      | XXX             | _                          |                   |

|                    |      | Other than 00 | Х      | XXX             | -                          |                   |

## [Legend]

X: Don't care.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                    |

|-----|----------|------------------|-----|------------------------------------------------------------------------------------------------|

| 1   |          | 1                |     | Reserved                                                                                       |

|     |          |                  |     | This bit is always read as 1.                                                                  |

| 0   | ICKS0    | 0                | R/W | Internal Clock Select 0                                                                        |

|     |          |                  |     | This bit selects clock signals to input to TCNTV in<br>combination with CKS2 to CKS0 in TCRV0. |

|     |          |                  |     | Refer to table 11.2.                                                                           |

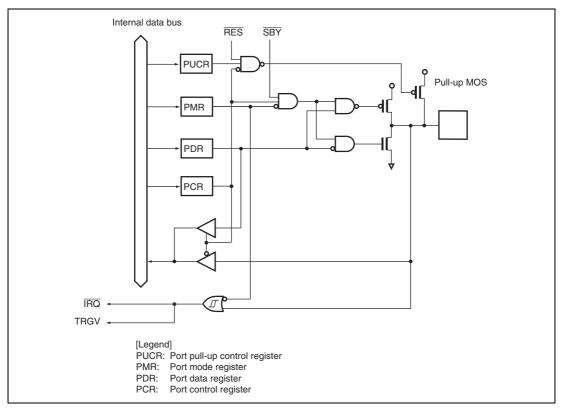

### 11.4 Operation

#### 11.4.1 Timer V Operation

- According to table 11.2, six internal/external clock signals output by prescaler S can be selected as the timer V operating clock signals. When the operating clock signal is selected, TCNTV starts counting-up. Figure 11.2 shows the count timing with an internal clock signal selected, and figure 11.3 shows the count timing with both edges of an external clock signal selected.

- 2. When TCNTV overflows (changes from H'FF to H'00), the overflow flag (OVF) in TCRV0 will be set. The timing at this time is shown in figure 11.4. An interrupt request is sent to the CPU when OVIE in TCRV0 is 1.

- 3. TCNTV is constantly compared with TCORA and TCORB. Compare match flag A or B (CMFA or CMFB) is set to 1 when TCNTV matches TCORA or TCORB, respectively. The compare-match signal is generated in the last state in which the values match. Figure 11.5 shows the timing. An interrupt request is generated for the CPU when CMIEA or CMIEB in TCRV0 is 1.

- 4. When a compare match A or B is generated, the TMOV responds with the output value selected by bits OS3 to OS0 in TCSRV. Figure 11.6 shows the timing when the output is toggled by compare match A.

- 5. When CCLR1 or CCLR0 in TCRV0 is 01 or 10, TCNTV can be cleared by the corresponding compare match. Figure 11.7 shows the timing.

- 6. When CCLR1 or CCLR0 in TCRV0 is 11, TCNTV can be cleared by the rising edge of the input of TMRIV pin. A TMRIV input pulse-width of at least 1.5 system clocks is necessary. Figure 11.8 shows the timing.

- 7. When a counter-clearing source is generated with TRGE in TCRV1 set to 1, the counting-up is halted as soon as TCNTV is cleared. TCNTV resumes counting-up when the edge selected by TVEG1 or TVEG0 in TCRV1 is input from the TGRV pin.

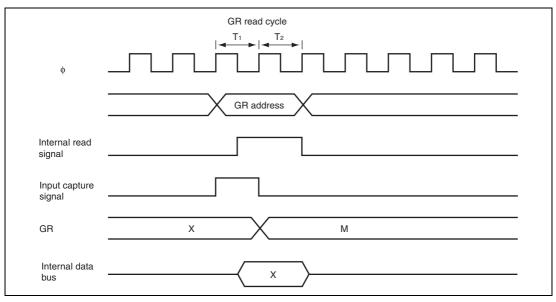

**Contention between GR Read and Input Capture:** If an input capture signal is generated in the  $T_1$  state of a GR read cycle, the data that is read will be transferred before input capture transfer. Figure 12.56 shows the timing in this case.

Figure 12.56 Contention between GR Read and Input Capture

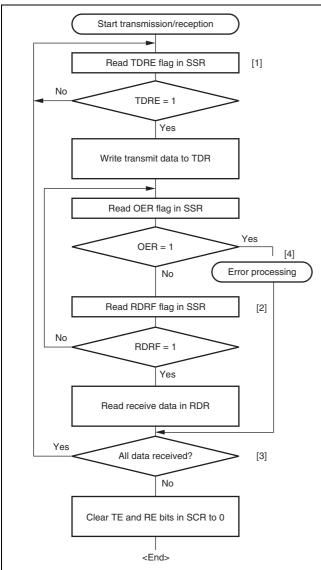

- Read SSR and check that the TDRE flag is set to 1, then write transmit data to TDR.

When data is written to TDR, the TDRE flag is automatically cleared to 0.

- Read SSR and check that the RDRF flag is set to 1, then read the receive data in RDR.

When data is read from RDR, the RDRF flag is automatically cleared to 0.

- [3] To continue serial transmission/ reception, before the MSB (bit 7) of the current frame is received, finish reading the RDRF flag, reading RDR. Also, before the MSB (bit 7) of the current frame is transmitted, read 1 from the TDRE flag to confirm that writing is possible. Then write data to TDR.

When data is written to TDR, the TDRE flag is automatically cleared to 0. When data is read from RDR, the RDRF flag is automatically cleared to 0.

[4] If an overrun error occurs, read the OER flag in SSR, and after performing the appropriate error processing, clear the OER flag to 0. Transmission/reception cannot be resumed if the OER flag is set to 1. For overrun error processing, see figure 14.13.

Figure 14.14 Sample Flowchart of Simultaneous Serial Transmit and Receive Operations (Clocked Synchronous Mode)

RENESAS

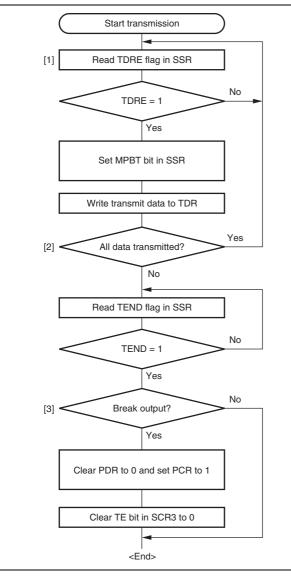

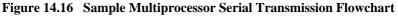

- Read SSR and check that the TDRE flag is set to 1, set the MPBT bit in SSR to 0 or 1, then write transmit data to TDR. When data is written to TDR, the TDRE flag is automatically cleared to 0.

- [2] To continue serial transmission, be sure to read 1 from the TDRE flag to confirm that writing is possible, then write data to TDR. When data is written to TDR, the TDRE flag is automatically cleared to 0.

- [3] To output a break in serial transmission, set the port PCR to 1, clear PDR to 0, then clear the TE bit in SCR3 to 0.

#### 14.6.2 Multiprocessor Serial Data Reception

Figure 14.17 shows a sample flowchart for multiprocessor serial data reception. If the MPIE bit in SCR3 is set to 1, data is skipped until data with a 1 multiprocessor bit is sent. On receiving data with a 1 multiprocessor bit, the receive data is transferred to RDR. An RXI interrupt request is

RENESAS

### 15.3.5 Bit Configuration Registers 0, 1 (BCR0, BCR1)

BCR configures the CAN bit timing parameters and baud rate prescaler for the CDLC.

• BCR0

| <b>D</b> :/ | Dichleme | Initial | D 444 | Description                                                |

|-------------|----------|---------|-------|------------------------------------------------------------|

| Bit         | Bit Name | Value   | R/W   | Description                                                |

| 7           | SJW1     | 0       | R/W   | Re-Synchronization Jump Width                              |

| 6           | SJW0     | 0       | R/W   | These bits set the maximum value of synchronization width. |

|             |          |         |       | 00: 1 time quantum                                         |

|             |          |         |       | 01: 2 time quanta                                          |

|             |          |         |       | 10: 3 time quanta                                          |

|             |          |         |       | 11: 4 time quanta                                          |

| 5           | BRP5     | 0       | R/W   | Baud Rate Prescaler                                        |

| 4           | BRP4     | 0       | R/W   | These bits set the clock used for time quanta.             |

| 3           | BRP3     | 0       | R/W   | 000000: Setting prohibited                                 |

| 2           | BRP2     | 0       | R/W   | 000001: 2 system clocks                                    |

| 1           | BRP1     | 0       | R/W   | : : (BRP + 1) system clocks                                |

| 0           | BRP0     | 0       | R/W   | 111111: 64 system clocks                                   |

#### • BCR1

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                       |

|-----|----------|------------------|-----|-------------------------------------------------------------------|

| 7   | —        | 0                | —   | Reserved                                                          |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0. |

| Register               |        |                 |     |                                                                                                                                                               |

|------------------------|--------|-----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                   | Bit    | Bit Name        | R/W | Description                                                                                                                                                   |

| MCn[0]<br>(n = 0 to 3) | 7      | DART            | R/W | Automatic Retransmission Disable                                                                                                                              |

| (n = 0  to  3)         |        |                 |     | When this bit is set to 1, the message disables to be retransmitted in the event of an error on CAN bus or an arbitration lost on CAN bus.                    |

|                        |        |                 |     | 0: Automatic retransmission is carried out                                                                                                                    |

|                        |        |                 |     | 1: Automatic retransmission is prohibited                                                                                                                     |

|                        | 6      | NMC             | R/W | New Message Control                                                                                                                                           |

|                        |        |                 |     | When a Mailbox with an unread message receives a<br>new message, this bit selects whether to overrun or<br>overwrite the unread message with the new message. |

|                        |        |                 |     | 0: The new receive message is ignored and the<br>unread message is saved, and the corresponding<br>UMSR bit is set to 1 (overrun)                             |

|                        |        |                 |     | 1: The unread message is lost by being overwritten<br>with the new receive message, and the<br>corresponding UMSR bit is set to 1 (overwrite)                 |

|                        | 5, 4   |                 | —   | Reserved                                                                                                                                                      |

|                        |        |                 |     | These bits are always read as 0.                                                                                                                              |

|                        | 3 to 0 | DLC3 to<br>DLC0 | R/W | Data Length Code                                                                                                                                              |

|                        |        |                 |     | These bits set the transmit data length of data frames<br>and data length requested by remote frames. These<br>bits are stipulated in Bosch 2.0B active.      |

|                        |        |                 |     | 0000: 0 bytes                                                                                                                                                 |

|                        |        |                 |     | 0001: 1 byte                                                                                                                                                  |

|                        |        |                 |     | 0010: 2 bytes                                                                                                                                                 |

|                        |        |                 |     | 0011: 3 bytes                                                                                                                                                 |

|                        |        |                 |     | 0100: 4 bytes                                                                                                                                                 |

|                        |        |                 |     | 0101: 5 bytes                                                                                                                                                 |

|                        |        |                 |     | 0110: 6 bytes                                                                                                                                                 |

|                        |        |                 |     | 0111: 7 bytes                                                                                                                                                 |

|                        |        |                 |     | 1xxx: 8 bytes                                                                                                                                                 |

| MCn[4]<br>(n = 0 to 3) | 7 to 5 | ID20 to<br>ID18 | R/W | These bits set bits 2 to 0 in the standard identifier of data frames and remote frames.                                                                       |

Figure 16.6 Sample Serial Transmission Flowchart

# Section 17 Subsystem Timer (Subtimer)

The subtimer is a timer for controlling subsystem which has an on-chip oscillator for supplying system clocks in subactive and subsleep modes and an on-chip 8-bit down counter. Since the subtimer has a prescaler that can set the division ratio by software, it can supply a clock with any frequency. This LSI has an on-chip single-channel subtimer.

### 17.1 Features

- On-chip oscillator

Oscillation frequency: 64 kHz to 850 kHz

Temperature characteristic: Source clock ± 10% (typ.)

- Counter: two

8-bit readable/writable down counter

8-bit counter for measuring oscillation frequency of the on-chip oscillator

• CPU interrupt source

Underflow (interrupt interval: 731 µsec to 67.4 msec)

- Subtimer clock supply operating modes: Subactive mode

Subsleep mode

- On-chip oscillator

The on-chip oscillator supplies three kinds of clocks:

Subactive or subsleep mode  $(\phi_{w})$

Subtimer down counter (input clock)

Watchdog timer (input clock)

• Subtimer prescaler (SBTPS)

The subtimer prescaler is a divider which controls input clocks to the counter which measures oscillation cycle of the on-chip oscillator and the down counter for the subtimer.

| Register<br>Abbreviation | Reset | Active | Sleep | Subactive | Subsleep | Standby | Module  |

|--------------------------|-------|--------|-------|-----------|----------|---------|---------|

| MC1[4]                   | _     | _      | _     | _         | _        | _       | TinyCAN |

| MC1[5]                   | _     | _      | _     | —         | _        | _       | —       |

| MC2[1]                   | -     | _      | _     | _         | _        | _       | —       |

| MC2[2]                   | _     | _      | _     | —         | _        | _       | _       |

| MC2[3]                   | _     | _      | _     | _         | _        | _       | _       |

| MC2[4]                   | —     | —      | —     | —         | _        | —       |         |

| MC2[5]                   | _     | _      | _     | _         | _        | _       |         |

| MC3[1]                   | _     | _      | _     | _         | _        | _       | _       |

| MC3[2]                   | _     | _      | _     | _         | _        | _       | _       |

| MC3[3]                   | —     | —      | —     | —         | —        | —       | _       |

| MC3[4]                   | _     | _      | _     | _         | _        | _       | _       |

| MC3[5]                   | —     | —      | —     | —         | _        | —       |         |

| MD0[1]                   | _     | _      | _     | _         | _        | _       |         |

| MD0[2]                   | _     | —      | —     | —         | _        | _       | _       |

| MD0[3]                   | _     | _      | _     | _         | _        | _       | _       |

| MD0[4]                   | _     | _      | _     | —         | _        | _       | _       |

| MD0[5]                   | _     | _      | _     | _         | _        | _       | _       |

| MD0[6]                   | _     | _      | _     | _         | _        | _       | _       |

| MD0[7]                   | —     | —      | —     | —         | —        | —       | _       |

| MD0[8]                   | _     | —      | —     | —         | _        | _       | _       |

| MD1[1]                   | _     | _      | _     | _         | _        | _       | _       |

| MD1[2]                   | _     | _      | _     | _         | _        | _       |         |

| MD1[3]                   | _     | _      | _     | _         | _        | _       |         |

| MD1[4]                   | _     | _      | _     | _         | _        | _       | _       |

| MD1[5]                   | _     | _      | _     | _         | _        | _       |         |

| MD1[6]                   | _     | —      | —     | —         | _        | _       | _       |

| MD1[7]                   | _     | _      | _     | _         | _        | _       | _       |

| MD1[8]                   | _     | _      | _     | _         | _        | _       |         |

| MD2[1]                   | _     |        | _     | _         | _        | _       | _       |

| MD2[2]                   | _     | _      | _     | _         | _        | _       | —       |

| MD2[3]                   |       | _      |       | _         | _        | _       |         |

|                                        |                 |                                                                                                                                                                                                     |                                                                        | Values |      |      |            |

|----------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------|------|------|------------|

| Item                                   | Symbol          | Applicable Pins                                                                                                                                                                                     | Test Condition                                                         | Min.   | Тур. | Max. | Unit Notes |

| Output<br>low<br>voltage               | V <sub>ol</sub> | P10 to P12,<br>P14 to P17,<br>P20 to P24,<br>P50 to P57,                                                                                                                                            | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$<br>$I_{oL} = 1.6 \text{ mA}$  | _      | _    | 0.6  | V          |

|                                        |                 | P70 to P72,<br>P74 to P76,<br>P85 to P87<br>P90 to P97                                                                                                                                              | I <sub>oL</sub> = 0.4 mA                                               | _      | _    | 0.4  |            |

|                                        |                 | P60 to P67                                                                                                                                                                                          | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$<br>$I_{oL} = 20.0 \text{ mA}$ | _      | _    | 1.5  | V          |

|                                        |                 |                                                                                                                                                                                                     | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$<br>$I_{oL} = 10.0 \text{ mA}$ | _      | _    | 1.0  |            |

|                                        |                 |                                                                                                                                                                                                     | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$<br>$I_{oL} = 1.6 \text{ mA}$  | -      | —    | 0.4  |            |

|                                        |                 |                                                                                                                                                                                                     | I <sub>oL</sub> = 0.4 mA                                               | _      | _    | 0.4  |            |

| Input/<br>output<br>leakage<br>current | I <sub>IL</sub> | OSC1, RES, NMI,<br>WKP0 to WKP5,<br>IRQ0 to IRQ3,<br>ADTRG, TRGV,<br>TMRIV, TMCIV,<br>FTIOA0 to<br>FTIOD0, FTIOA1<br>to FTIOD1, RXD,<br>SCK3, RXD_2* <sup>1</sup> , SSCK,<br>SCS, SSI, SSO,<br>HRXD | higher<br>(V <sub>cc</sub> – 0.5 V)                                    |        | _    | 1.0  | μA         |

|                                        |                 | P10 to P12,<br>P14 to P17,<br>P20 to P24,<br>P50 to P57,<br>P60 to P67,<br>P70 to P72,<br>P74 to P76,<br>P85 to P87,<br>P90 to P97                                                                  | V <sub>IN</sub> = 0.5 V or<br>higher<br>(V <sub>CC</sub> − 0.5 V)      | _      | _    | 1.0  | μΑ         |

|                                        |                 | PB0 to PB7                                                                                                                                                                                          | $V_{IN} = 0.5 V \text{ or}$<br>higher<br>$(AV_{CC} - 0.5 V)$           | _      | _    | 1.0  | μΑ         |

#### Table 22.13 DC Characteristics (2)

$V_{cc} = 2.7$  to 5.5 V,  $V_{ss} = 0.0$  V,  $T_a = -20$  to  $+75^{\circ}C$  (regular specifications) or  $T_a = -40$  to  $+85^{\circ}C$  (wide-range specifications), unless otherwise indicated.

|                                        |                           |                              |                             | Values |      |      |      |

|----------------------------------------|---------------------------|------------------------------|-----------------------------|--------|------|------|------|

| Item                                   | Symbol                    | Applicable Pins              | Test Condition              | Min.   | Тур. | Max. | Unit |

| Allowable output low current (per pin) | I <sub>ol</sub>           | Output pins<br>except port 6 | $V_{\rm cc}$ = 4.0 to 5.5 V | _      | _    | 2.0  | mA   |

|                                        |                           | Port 6                       | -                           | _      | _    | 20.0 | _    |

|                                        |                           | Output pins<br>except port 6 |                             | _      | _    | 0.5  | _    |

|                                        |                           | Port 6                       | -                           | _      | —    | 10.0 | _    |

| Allowable output low current (total)   | $\Sigma {\rm I}_{\rm OL}$ | Output pins<br>except port 6 | $V_{cc}$ = 4.0 to 5.5 V     | _      | _    | 40.0 | mA   |

|                                        |                           | Port 6                       | -                           | _      | _    | 80.0 |      |

|                                        |                           | Output pins<br>except port 6 |                             | _      | _    | 20.0 | _    |

|                                        |                           | Port 6                       | -                           | _      | —    | 40.0 | _    |

| Allowable output high                  | -I <sub>он</sub>          | All output pins              | $V_{\rm cc}$ = 4.0 to 5.5 V | —      | —    | 2.0  | mA   |

| current (per pin)                      |                           |                              |                             | _      | _    | 0.2  | _    |

| Allowable output high                  | $\Sigma  -I_{OH} $        | All output pins              | $V_{\rm cc}$ = 4.0 to 5.5 V | _      | _    | 30.0 | mA   |

| current (total)                        |                           |                              |                             |        |      | 8.0  |      |

# Appendix B I/O Port Block Diagrams

### B.1 I/O Port Block Diagrams

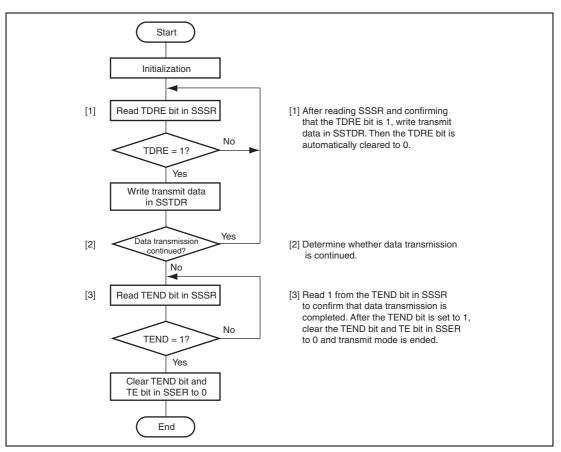

$\overline{\text{RES}}$  goes low in a reset, and  $\overline{\text{SBY}}$  goes low at reset and in standby mode.

Figure B.1 Port 1 Block Diagram (P17)

Figure B.13 Port 7 Block Diagram (P76)