Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 48MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                     |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                                |

| Number of I/O              | 37                                                                       |

| Program Memory Size        | 16KB (16K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 4K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                |

| Data Converters            | A/D 10x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 48-LQFP                                                                  |

| Supplier Device Package    | 48-LQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f102c4t6atr |

# List of tables

| Table 1.  | Device summary                                                                        | 1  |

|-----------|---------------------------------------------------------------------------------------|----|

| Table 2.  | STM32F102x4 and STM32F102x6 low-density USB access line features                      |    |

|           | and peripheral counts                                                                 | 9  |

| Table 3.  | STM32F102xx USB access line family                                                    | 12 |

| Table 4.  | Low-density STM32F102xx pin definitions                                               | 20 |

| Table 5.  | Voltage characteristics                                                               | 26 |

| Table 6.  | Current characteristics                                                               | 27 |

| Table 7.  | Thermal characteristics                                                               | 27 |

| Table 8.  | General operating conditions                                                          | 28 |

| Table 9.  | Operating conditions at power-up / power-down                                         | 28 |

| Table 10. | Embedded reset and power control block characteristics                                | 29 |

| Table 11. | Embedded internal reference voltage                                                   | 30 |

| Table 12. | Maximum current consumption in Run mode, code with data processing running from Flash | 31 |

| Table 13. | Maximum current consumption in Run mode, code with data processing running from RAM   |    |

| Table 14. | Maximum current consumption in Sleep mode, code running from Flash or RAM             |    |

| Table 15. | Typical and maximum current consumptions in Stop and Standby modes                    |    |

| Table 16. | Typical current consumption in Run mode, code with data processing                    | 00 |

| 14510 10. | running from Flash                                                                    | 36 |

| Table 17. | Typical current consumption in Sleep mode, code running from Flash or RAM             |    |

| Table 18. | Peripheral current consumption                                                        |    |

| Table 19. | High-speed external user clock characteristics.                                       |    |

| Table 20. | Low-speed external user clock characteristics                                         |    |

| Table 21. | HSE 4-16 MHz oscillator characteristics                                               |    |

| Table 22. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)                        |    |

| Table 23. | HSI oscillator characteristics                                                        |    |

| Table 24. | LSI oscillator characteristics                                                        | 44 |

| Table 25. | Low-power mode wakeup timings                                                         | 44 |

| Table 26. | PLL characteristics                                                                   |    |

| Table 27. | Flash memory characteristics                                                          | 45 |

| Table 28. | Flash memory endurance and data retention                                             | 45 |

| Table 29. | EMS characteristics                                                                   |    |

| Table 30. | EMI characteristics                                                                   | 47 |

| Table 31. | ESD absolute maximum ratings                                                          | 47 |

| Table 32. | Electrical sensitivities                                                              | 47 |

| Table 33. | I/O current injection susceptibility                                                  | 48 |

| Table 34. | I/O static characteristics                                                            | 49 |

| Table 35. | Output voltage characteristics                                                        |    |

| Table 36. | I/O AC characteristics                                                                | 53 |

| Table 37. | NRST pin characteristics                                                              | 54 |

| Table 38. | TIMx characteristics                                                                  |    |

| Table 39. | I <sup>2</sup> C characteristics                                                      | 57 |

| Table 40. | SCL frequency (f <sub>PCLK1</sub> = 36 MHz, V <sub>DD_I2C</sub> = 3.3 V)              |    |

| Table 41. | SPI characteristics                                                                   | 59 |

| Table 42. | USB startup time                                                                      |    |

| Table 43. | USB DC electrical characteristics                                                     |    |

| Table 44  | USB: Full speed electrical characteristics of the driver                              | 62 |

| Table 45. | ADC characteristics                                     | 63 |

|-----------|---------------------------------------------------------|----|

| Table 46. | $R_{AIN}$ max for $f_{ADC}$ = 12 MHz                    | 64 |

| Table 47. | ADC accuracy - limited test conditions                  | 64 |

| Table 48. | ADC accuracy                                            | 64 |

| Table 49. | TS characteristics                                      | 66 |

| Table 50. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat       |    |

|           | package mechanical data                                 | 67 |

| Table 51. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package |    |

|           | mechanical data                                         | 71 |

| Table 52. | Package thermal characteristics                         | 73 |

| Table 53. | Ordering information scheme                             | 75 |

| Table 54. | Document revision history                               | 76 |

|           |                                                         |    |

## 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of STM32F102x4 and STM32F102x6 low-density USB access line microcontrollers. For more details on the whole STMicroelectronics STM32F102xx family. please refer to Section 2.2: Full compatibility throughout the family.

The medium-density STM32F102xx datasheet should be read in conjunction with the low-, medium- and high-density STM32F10xxx reference manual.

For information on programming, erasing and protection of the internal Flash memory please refer to the *STM32F10xxx Flash programming manual*.

The reference and Flash programming manuals are both available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M3 core please refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the ARM<sup>®</sup> website.

577

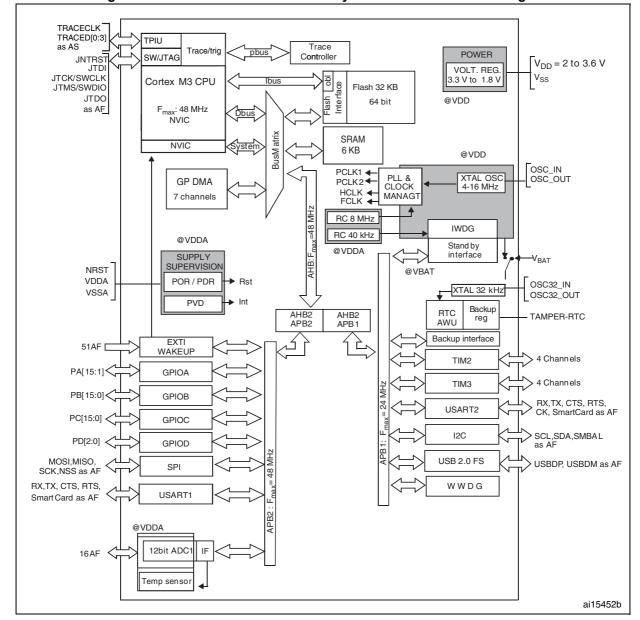

Figure 1. STM32F102T8 medium-density USB access line block diagram

- 1. AF = alternate function on I/O port pin.

- 2.  $T_A = -40$  °C to +85 °C (junction temperature up to 105 °C).

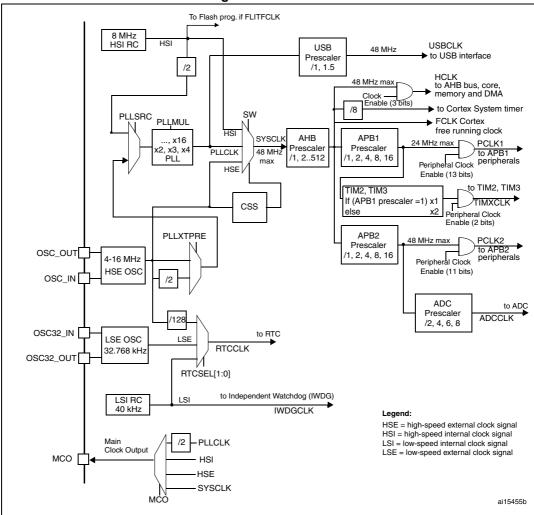

Figure 2. Clock tree

- For the USB function to be available, both HSE and PLL must be enabled, with the USB clock output (USBCLK) at 48 MHz.

- 2. To have an ADC conversion time of 1.2 μs, APB2 must be at 12 MHz, 24 MHz or 48 MHz.

- 3. The Flash memory programming interface clock (FLITFCLK) is always the HSI clock.

57/

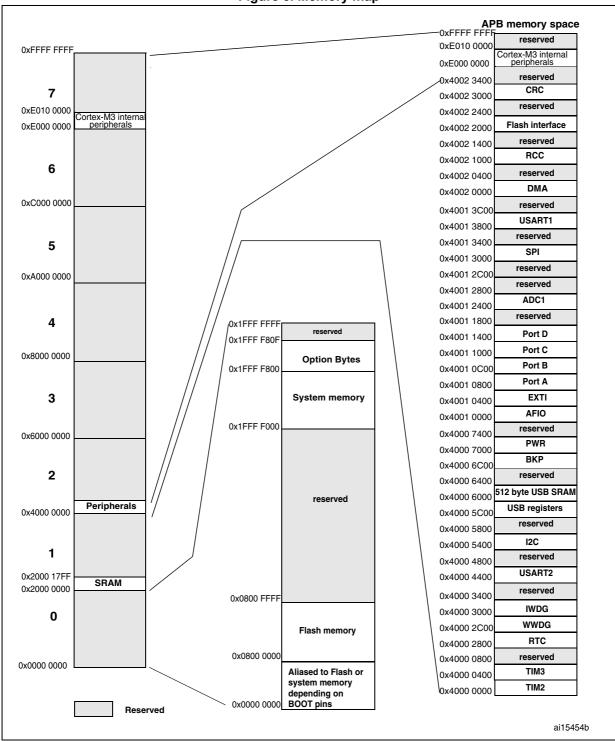

## 4 Memory mapping

The memory map is shown in Figure 5.

Figure 5. Memory map

## 5.3 Operating conditions

## 5.3.1 General operating conditions

Table 8. General operating conditions

| Symbol                          | Parameter                                                  | Co                                   | onditions                     | Min             | Max                      | Unit  |

|---------------------------------|------------------------------------------------------------|--------------------------------------|-------------------------------|-----------------|--------------------------|-------|

| f <sub>HCLK</sub>               | Internal AHB clock frequency                               |                                      | 0                             | 48              |                          |       |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency                              |                                      | -                             | 0               | 24                       | MHz   |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency                              |                                      | -                             | 0               | 48                       |       |

| V <sub>DD</sub>                 | Standard operating voltage                                 |                                      | -                             | 2               | 3.6                      | V     |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage (ADC not used)                    | Must be the s                        | 2                             | 3.6             |                          |       |

| VDDA'                           | Analog operating voltage (ADC used)                        | as V <sub>DD</sub> <sup>(2)</sup>    |                               | 2.4             | 3.6                      |       |

|                                 |                                                            | Standard IO                          |                               | -0.3            | V <sub>DD</sub> +<br>0.3 | V     |

| V <sub>IN</sub>                 | I/O input voltage                                          | FTIO <sup>(3)</sup>                  | 2 V < V <sub>DD</sub> ≤ 3.6 V | -0.3            | 5.5                      |       |

|                                 |                                                            | FIIO.                                | V <sub>DD</sub> = 2 V         | -0.3            | 5.2                      |       |

|                                 |                                                            | воото                                |                               | 0               | 5.5                      |       |

| P <sub>D</sub>                  | Power dissipation at T <sub>A</sub> = 85 °C <sup>(4)</sup> | LQFP48                               |                               | -               | 363                      | mW    |

| r <sub>D</sub>                  | Power dissipation at 1 <sub>A</sub> = 65°C.7               | LQFP64                               |                               | -               | 444                      | IIIVV |

| TA                              | Ambient temperature                                        | Maximum power dissipation            |                               | -40             | 85                       | °C    |

| IA                              | Ambient temperature                                        | Low power dissipation <sup>(5)</sup> |                               | <del>-4</del> 0 | 105                      | °C    |

| TJ                              | Junction temperature range                                 |                                      |                               | -40             | 105                      | °C    |

<sup>1.</sup> When the ADC is used, refer to *Table 45: ADC characteristics*.

## 5.3.2 Operating conditions at power-up / power-down

Subject to general operating conditions for T<sub>A</sub>.

Table 9. Operating conditions at power-up / power-down

| Symbol           | Parameter                      | Conditions | Min | Max | Unit  |

|------------------|--------------------------------|------------|-----|-----|-------|

| +                | V <sub>DD</sub> rise time rate |            | 0   | ∞   | μs/V  |

| t <sub>VDD</sub> | V <sub>DD</sub> fall time rate | -          | 20  | 8   | μ5/ ν |

<sup>2.</sup> It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and operation.

<sup>3.</sup> To sustain a voltage higher than  $V_{DD}$ +0.3 V, the internal pull-up/pull-down resistors must be disabled.

If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub>max (see Section 6.3: Thermal characteristics).

In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>J</sub>max (see Section 6.3: Thermal characteristics).

Table 14. Maximum current consumption in Sleep mode, code running from Flash or RAM

| Symbol          | Domonoton         | Conditions                                              | £                 | Max <sup>(1)</sup>     | Unit       |    |

|-----------------|-------------------|---------------------------------------------------------|-------------------|------------------------|------------|----|

| Symbol          | Parameter         | Conditions                                              | f <sub>HCLK</sub> | T <sub>A</sub> = 85 °C | Unit       |    |

|                 |                   |                                                         | 48 MHz            | 17                     |            |    |

|                 |                   | (2)                                                     | 36 MHz            | 14                     |            |    |

|                 |                   | External clock <sup>(2)</sup> , all peripherals enabled | 24 MHz            | 10                     |            |    |

|                 |                   | Supply current in                                       | 16 MHz            | 7                      |            |    |

|                 | Supply current in |                                                         | 8 MHz             | 4                      | <b>~</b> ∧ |    |

| I <sub>DD</sub> | Sleep mode        |                                                         |                   | 48 MHz                 | 6          | mA |

|                 |                   |                                                         | 36 MHz            | 5                      |            |    |

|                 |                   |                                                         | 24 MHz            | 4.5                    |            |    |

|                 |                   | , , , , , , , , , , , , , , , , , , ,                   | 16 MHz            | 4                      |            |    |

|                 |                   |                                                         | 8 MHz             | 3                      |            |    |

<sup>1.</sup> Based on characterization, tested in production at  $V_{DD}$  max and  $f_{HCLK}$  max with peripherals enabled.

Table 15. Typical and maximum current consumptions in Stop and Standby modes

|                      |                                                     |                                                                                                                                                   |                                                  | Typ <sup>(1)</sup>                           |                                              |                           |      |

|----------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------|----------------------------------------------|---------------------------|------|

| Symbol               | Parameter                                           | Conditions                                                                                                                                        | V <sub>DD</sub> /<br>V <sub>BAT</sub> =<br>2.4 V | V <sub>DD</sub> /V <sub>BAT</sub><br>= 3.3 V | V <sub>DD</sub> /V <sub>BAT</sub><br>= 2.0 V | T <sub>A</sub> =<br>85 °C | Unit |

| I <sub>DD</sub>      | Supply current                                      | Regulator in Run mode. Low-speed and high-speed internal RC oscillators and high-speed oscillator OFF (no independent watchdog)                   | 21.3                                             | 21.7                                         | -                                            | 160                       |      |

|                      | in Stop mode                                        | Regulator in Low Power mode.<br>Low-speed and high-speed internal<br>RC oscillators and high-speed<br>oscillator OFF (no independent<br>watchdog) | 11.3                                             | 11.7                                         | -                                            | 145                       |      |

|                      | Supply current<br>in Standby<br>mode <sup>(2)</sup> | Low-speed internal RC oscillator and independent watchdog ON                                                                                      | 2.75                                             | 3.4                                          | -                                            | -                         | μA   |

|                      |                                                     | Low-speed internal RC oscillator ON, independent watchdog OFF                                                                                     | 2.55                                             | 3.2                                          | -                                            | ı                         |      |

|                      |                                                     | Low-speed internal RC oscillator and independent watchdog OFF, low-speed oscillator and RTC OFF                                                   | 1.55                                             | 1.9                                          | -                                            | 3.2                       |      |

| I <sub>DD_VBAT</sub> | Backup<br>domain supply<br>current                  | Low-speed oscillator and RTC ON                                                                                                                   | 1.1                                              | 1.4                                          | 0.9                                          | 1.9 <sup>(3)</sup>        |      |

<sup>1.</sup> Typical values are measured at  $T_A$  = 25 °C.

<sup>2.</sup> External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

Table 17. Typical current consumption in Sleep mode, code running from Flash or RAM

|                 |                                    |                                |                   | Typ <sup>(1)</sup>                        | Typ <sup>(1)</sup>       |      |  |

|-----------------|------------------------------------|--------------------------------|-------------------|-------------------------------------------|--------------------------|------|--|

| Symbol          | Parameter                          | Conditions                     | f <sub>HCLK</sub> | All peripherals<br>enabled <sup>(2)</sup> | All peripherals disabled | Unit |  |

|                 |                                    |                                | 48 MHz            | 8.7                                       | 3.8                      |      |  |

|                 |                                    |                                | 36 MHz            | 6.7                                       | 3.1                      |      |  |

|                 |                                    |                                | 24 MHz            | 4.8                                       | 2.3                      |      |  |

|                 |                                    |                                | 16 MHz            | 3.4                                       | 1.8                      |      |  |

|                 |                                    | External clock <sup>(3)</sup>  | 8 MHz             | 2                                         | 1.2                      |      |  |

|                 |                                    | External clock                 | 4 MHz             | 1.5                                       | 1.1                      |      |  |

|                 | Supply<br>current in<br>Sleep mode |                                |                   | 2 MHz                                     | 1.25                     | 1    |  |

|                 |                                    |                                |                   | 1 MHz                                     | 1.1                      | 0.98 |  |

|                 |                                    |                                | 500 kHz           | 1.05                                      | 0.96                     |      |  |

| 1               |                                    |                                | 125 kHz           | 1                                         | 0.95                     | mA   |  |

| I <sub>DD</sub> |                                    |                                | 48 MHz            | 8.1                                       | 3.2                      | шА   |  |

|                 |                                    |                                | 36 MHz            | 6.1                                       | 2.5                      |      |  |

|                 |                                    |                                | 24 MHz            | 4.2                                       | 1.7                      |      |  |

|                 |                                    | Running on High Speed Internal | 16 MHz            | 2.8                                       | 1.2                      |      |  |

|                 |                                    | RC (HSI), AHB                  | 8 MHz             | 1.4                                       | 0.55                     |      |  |

|                 |                                    | prescaler used to reduce the   | 4 MHz             | 0.9                                       | 0.5                      |      |  |

|                 |                                    | frequency                      | 2 MHz             | 0.7                                       | 0.45                     |      |  |

|                 |                                    |                                | 1 MHz             | 0.55                                      | 0.42                     |      |  |

|                 |                                    |                                | 500 kHz           | 0.48                                      | 0.4                      |      |  |

|                 |                                    |                                | 125 kHz           | 0.4                                       | 0.38                     |      |  |

<sup>1.</sup> Typical values are measures at  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V.

<sup>2.</sup> Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

<sup>3.</sup> External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

#### On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in *Table 18*. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature and V<sub>DD</sub> supply voltage conditions as summarized in Table 5.

Table 18. Peripheral current consumption<sup>(1)</sup>

|                         | Peripheral               | μ <b>A</b> /MHz |

|-------------------------|--------------------------|-----------------|

|                         | DMA1                     | 15.97           |

| AHB (up to 48 MHz)      | CRC                      | 1.67            |

|                         | BusMatrix <sup>(2)</sup> | 8.33            |

|                         | APB1-Bridge              | 7.22            |

|                         | TIM2                     | 33.33           |

|                         | TIM3                     | 33.61           |

|                         | USART2                   | 12.78           |

| APB1 (up to 24 MHz)     | I2C1                     | 10.83           |

| A  B  (up to 24 Wil i2) | USB                      | 16.94           |

|                         | WWDG                     | 3.33            |

|                         | PWR                      | 1.94            |

|                         | ВКР                      | 2.78            |

|                         | IWDG                     | 1.39            |

|                         | APB2-Bridge              | 3.33            |

|                         | GPIOA                    | 7.50            |

|                         | GPIOB                    | 6.81            |

| ADD2 (up to 48 MHz)     | GPIOC                    | 7.22            |

|                         | GPIOD                    | 6.94            |

|                         | SPI1                     | 4.86            |

|                         | USART1                   | 12.78           |

| APB2 (up to 48 MHz)     | ADC1 <sup>(3)</sup> (4)  | 15.54           |

- 1.  $f_{HCLK}$  = 48 MHz,  $f_{APB1}$  =  $f_{HCLK}/2$ ,  $f_{APB2}$  =  $f_{HCLK}$ , default prescaler value for each peripheral.

- 2. The BusMatrix is automatically active when at least one master is ON.

- 3. Specific conditions for ADC:  $f_{HCLK}$  = 48 MHz,  $f_{APB1}$  =  $f_{HCLK}/2$ ,  $f_{APB2}$  =  $f_{HCLK}$ ,  $f_{ADCCLK}$  =  $f_{APB2}/4$ .

- 4. When ADON bit in the ADC\_CR2 register is set to 1, there is an additional current consumption of 0, 68 mA. When we enable the ADC, there is an additional current consumption of 0, 06 mA.

#### 5.3.6 External clock source characteristics

#### High-speed external user clock generated from an external source

The characteristics given in *Table 19* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 8*.

| Table 10. High speed external aser clock dilatacteristics |                                                     |                                |                    |     |                    |      |  |

|-----------------------------------------------------------|-----------------------------------------------------|--------------------------------|--------------------|-----|--------------------|------|--|

| Symbol                                                    | Parameter                                           | Conditions                     | Min                | Тур | Max                | Unit |  |

| f <sub>HSE_ext</sub>                                      | User external clock source frequency <sup>(1)</sup> |                                | 1                  | 8   | 25                 | MHz  |  |

| V <sub>HSEH</sub>                                         | OSC_IN input pin high level voltage                 |                                | 0.7V <sub>DD</sub> | -   | $V_{DD}$           | V    |  |

| V <sub>HSEL</sub>                                         | OSC_IN input pin low level voltage                  |                                | V <sub>SS</sub>    | -   | 0.3V <sub>DD</sub> | V    |  |

| $t_{w(HSE)} \ t_{w(HSE)}$                                 | OSC_IN high or low time <sup>(1)</sup>              | -                              | 5                  | -   | -                  | ns   |  |

| $t_{r(HSE)} \ t_{f(HSE)}$                                 | OSC_IN rise or fall time <sup>(1)</sup>             |                                | -                  | -   | 20                 | 115  |  |

| C <sub>in(HSE)</sub>                                      | OSC_IN input capacitance <sup>(1)</sup>             |                                | -                  | 5   |                    | pF   |  |

| DuCy <sub>(HSE)</sub>                                     | Duty cycle                                          |                                | 45                 | -   | 55                 | %    |  |

| ΙL                                                        | OSC_IN Input leakage current                        | $V_{SS} \le V_{IN} \le V_{DD}$ |                    | -   | ±1                 | μA   |  |

Table 19. High-speed external user clock characteristics

#### Low-speed external user clock generated from an external source

The characteristics given in *Table 21* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 8*.

| Table 201 2011 opena external acor clock characteristics |                                                     |                                |                    |        |                    |      |  |

|----------------------------------------------------------|-----------------------------------------------------|--------------------------------|--------------------|--------|--------------------|------|--|

| Symbol                                                   | Parameter                                           | Conditions                     | Min                | Тур    | Max                | Unit |  |

| f <sub>LSE_ext</sub>                                     | User external clock source frequency <sup>(1)</sup> |                                | -                  | 32.768 | 1000               | kHz  |  |

| V <sub>LSEH</sub>                                        | OSC32_IN input pin high level voltage               |                                | 0.7V <sub>DD</sub> | -      | $V_{DD}$           | V    |  |

| V <sub>LSEL</sub>                                        | OSC32_IN input pin low level voltage                |                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | v    |  |

| $t_{w(LSE)} \ t_{w(LSE)}$                                | OSC32_IN high or low time <sup>(1)</sup>            | -                              | 450                | -      | -                  | ns   |  |

| $t_{r(LSE)} \ t_{f(LSE)}$                                | OSC32_IN rise or fall time <sup>(1)</sup>           |                                | -                  | -      | 50                 | 113  |  |

| C <sub>in(LSE)</sub>                                     | OSC32_IN input capacitance <sup>(1)</sup>           |                                | -                  | 5      | -                  | pF   |  |

| DuCy <sub>(LSE)</sub>                                    | Duty cycle                                          |                                | 30                 | -      | 70                 | %    |  |

| ΙL                                                       | OSC32_IN Input leakage current                      | $V_{SS} \le V_{IN} \le V_{DD}$ | -                  | -      | ±1                 | μA   |  |

Table 20. Low-speed external user clock characteristics

<sup>1.</sup> Guaranteed by design, not tested in production.

<sup>1.</sup> Guaranteed by design, not tested in production.

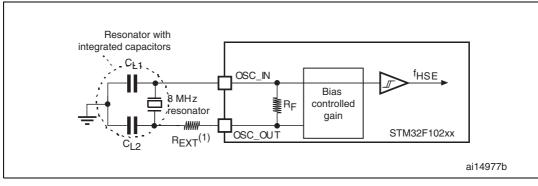

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 16 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 21*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                                                                                                        | Conditions                                              | Min | Тур | Max | Unit |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----|-----|-----|------|

| f <sub>OSC_IN</sub>                 | Oscillator frequency                                                                                             | -                                                       | 4   | 8   | 16  | MHz  |

| R <sub>F</sub>                      | Feedback resistor                                                                                                | -                                                       | -   | 200 | -   | kΩ   |

| С                                   | Recommended load capacitance versus equivalent serial resistance of the crystal (R <sub>S</sub> ) <sup>(3)</sup> | R <sub>S</sub> = 30 Ω                                   | -   | 30  | -   | pF   |

| i <sub>2</sub>                      | HSE driving current                                                                                              | $V_{DD}$ = 3.3 V<br>$V_{IN}$ = $V_{SS}$ with 30 pF load | 1   | ı   | 1   | mA   |

| 9 <sub>m</sub>                      | Oscillator transconductance                                                                                      | Startup                                                 | 25  | -   | -   | mA/V |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                                                                                                     | V <sub>DD</sub> is stabilized                           | -   | 2   | -   | ms   |

Table 21. HSE 4-16 MHz oscillator characteristics<sup>(1)(2)</sup>

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 18*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ . Refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website *www.st.com*.

<sup>1.</sup> Resonator characteristics given by the crystal/ceramic resonator manufacturer.

<sup>2.</sup> Based on characterization results, not tested in production.

The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

<sup>4.</sup> t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

Figure 18. Typical application with an 8 MHz crystal

1. R<sub>EXT</sub> value depends on the crystal characteristics.

### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 22*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Table 22. LSE oscillator characteristics ( | $f_{LSE} = 32.768 \text{ kHz}$ |

|--------------------------------------------|--------------------------------|

|--------------------------------------------|--------------------------------|

| Symbol                              | Parameter                                                                                         | Conditions                                                   |                         |   | Тур  | Max | Unit      |

|-------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------|---|------|-----|-----------|

| R <sub>F</sub>                      | Feedback resistor                                                                                 | -                                                            |                         |   | 5    | -   | $M\Omega$ |

| C <sup>(1)</sup>                    | Recommended load capacitance versus equivalent serial resistance of the crystal (R <sub>S</sub> ) | R <sub>S</sub> = 30 kΩ                                       |                         |   | -    | 15  | pF        |

| l <sub>2</sub>                      | LSE driving current                                                                               | V <sub>DD</sub> = 3.3 V<br>V <sub>IN</sub> = V <sub>SS</sub> |                         | - | -    | 1.4 | μΑ        |

| g <sub>m</sub>                      | Oscillator transconductance                                                                       | -                                                            |                         | 5 | -    | -   | μA/V      |

|                                     | Startup time                                                                                      | V <sub>DD</sub> is stabilized                                | T <sub>A</sub> = 50 °C  | - | 1.5  | -   |           |

|                                     |                                                                                                   |                                                              | T <sub>A</sub> = 25 °C  | - | 2.5  | -   |           |

|                                     |                                                                                                   |                                                              | T <sub>A</sub> = 10 °C  | - | 4.0  | -   |           |

| + (2)                               |                                                                                                   |                                                              | T <sub>A</sub> = 0 °C   | - | 6.0  | -   |           |

| t <sub>SU(LSE)</sub> <sup>(2)</sup> |                                                                                                   |                                                              | T <sub>A</sub> = -10 °C | - | 10.0 | -   | S         |

|                                     |                                                                                                   |                                                              | T <sub>A</sub> = -20 °C | - | 17.0 | -   |           |

|                                     |                                                                                                   |                                                              | T <sub>A</sub> = -30 °C | - | 32.0 | -   |           |

|                                     |                                                                                                   |                                                              | T <sub>A</sub> = -40 °C | - | 60.0 | -   |           |

Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled by software to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and can vary significantly with the crystal manufacturer, PCB layout and humidity.

- Refer to application note AN2868 "STM32F10xxx internal RC oscillator (HSI) calibration" available from the ST website www.st.com.

- 3. Guaranteed by design, not tested in production.

- 4. Based on characterization, not tested in production.

- The actual frequency of HSI oscillator may be impacted by a reflow, but does not drift out of the specified range.

#### Low-speed internal (LSI) RC oscillator

Table 24. LSI oscillator characteristics (1)

| Symbol                              | Parameter                        | Min <sup>(2)</sup> | Тур  | Max | Unit |

|-------------------------------------|----------------------------------|--------------------|------|-----|------|

| f <sub>LSI</sub>                    | Frequency                        | 30                 | 40   | 60  | kHz  |

| t <sub>su(LSI)</sub> (3)            | LSI oscillator startup time      | -                  | -    | 85  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -                  | 0.65 | 1.2 | μA   |

- 1.  $V_{DD}$  = 3 V,  $T_A$  = -40 to 85 °C unless otherwise specified.

- 2. Based on characterization, not tested in production.

- 3. Guaranteed by design, not tested in production.

#### Wakeup time from low-power mode

The wakeup times given in *Table 25* is measured on a wakeup phase with a 8-MHz HSI RC oscillator. The clock source used to wake up the device depends from the current operating mode:

- Stop or Standby mode: the clock source is the RC oscillator

- Sleep mode: the clock source is the clock that was set before entering Sleep mode.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

Table 25. Low-power mode wakeup timings

| Symbol                   | Parameter                                           | Тур | Unit |

|--------------------------|-----------------------------------------------------|-----|------|

| t <sub>WUSLEEP</sub> (1) | Wakeup from Sleep mode                              | 1.8 | μs   |

|                          | Wakeup from Stop mode (regulator in run mode)       | 3.6 |      |

| t <sub>wustop</sub> (1)  | Wakeup from Stop mode (regulator in low-power mode) | 5.4 | μs   |

| t <sub>WUSTDBY</sub> (1) | Wakeup from Standby mode                            | 50  | μs   |

The wakeup times are measured from the wakeup event to the point at which the user application code reads the first instruction.

#### 5.3.8 PLL characteristics

The parameters given in *Table 26* are derived from tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 8*.

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device is monitored while a simple application is executed (toggling 2 LEDs through the I/O ports), This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

Max vs. [f<sub>HSE</sub>/f<sub>HCLK</sub>] Monitored Symbol **Parameter Conditions** Unit frequency band 8/48 MHz 0.1 MHz to 30 MHz 7 8 30 MHz to 130 MHz dBµV  $S_{EMI}$ Peak level  $V_{DD} = 3.3 \text{ V}, T_A = 25 ^{\circ}\text{C}.$ 130 MHz to 1GHz 13 SAE EMI Level 3.5

Table 30. EMI characteristics

## 5.3.11 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts × (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

**Maximum Symbol Ratings Conditions** Class Unit value<sup>(1)</sup>  $T_A = +25$  °C, conforming Electrostatic discharge voltage 2 2000 V<sub>ESD(HBM)</sub> (human body model) to JESD22-A114 ٧ Electrostatic discharge voltage  $T_A = +25$  °C, conforming Ш 500 V<sub>ESD(CDM)</sub> to ANSI/ESD STM5.3.1 (charge device model)

Table 31. ESD absolute maximum ratings

#### Static latch-up

47/78

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78 IC latch-up standard.

Table 32. Electrical sensitivities

| Symbol | Parameter             | Parameter Conditions                           |            |

|--------|-----------------------|------------------------------------------------|------------|

| LU     | Static latch-up class | T <sub>A</sub> = +105 °C conforming to JESD78A | II level A |

<sup>1.</sup> Based on characterization results, not tested in production.

Table 34. I/O static characteristics

| Symbol           | Parameter                                                           | Conditions                                          | Min                                              | Тур | Мах                                              | Unit  |  |

|------------------|---------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------|-----|--------------------------------------------------|-------|--|

|                  |                                                                     | Standard IO<br>input low level<br>voltage           | -                                                | -   | 0.28*(V <sub>DD</sub> -2 V)+0.8 V <sup>(1)</sup> |       |  |

| V <sub>IL</sub>  | Low level input voltage                                             | IO FT <sup>(3)</sup> input low level voltage        | -                                                | -   | 0.32*(V <sub>DD</sub> -2V)+0.75 V <sup>(1)</sup> |       |  |

|                  |                                                                     | All I/Os except<br>BOOT0                            | -                                                | -   | 0.35V <sub>DD</sub> <sup>(2)</sup>               |       |  |

|                  |                                                                     | Standard IO<br>input high level<br>voltage          | 0.41*(V <sub>DD</sub> -2 V)+1.3 V <sup>(1)</sup> | -   | -                                                | V     |  |

|                  | High level input voltage                                            | IO FT <sup>(3)</sup> input<br>high level<br>voltage | 0.42*(V <sub>DD</sub> -2 V)+1 V <sup>(1)</sup>   | -   | -                                                |       |  |

|                  |                                                                     | All I/Os except<br>BOOT0                            | 0.65V <sub>DD</sub> <sup>(2)</sup>               | -   | -                                                |       |  |

| $V_{hys}$        | Standard IO Schmitt<br>trigger voltage<br>hysteresis <sup>(4)</sup> | -                                                   | 200                                              | -   | -                                                | mV    |  |

|                  | IO FT Schmitt trigger voltage hysteresis <sup>(4)</sup>             | -                                                   | 5% V <sub>DD</sub> <sup>(5)</sup>                | -   | -                                                |       |  |

| I                | Input leakage current                                               | $V_{SS} \le V_{IN} \le V_{DD}$<br>Standard I/Os     | -                                                | -   | ±1                                               | μA    |  |

| l <sub>lkg</sub> | (6)                                                                 | V <sub>IN</sub> = 5 V<br>I/O FT                     | -                                                | -   | 3                                                | μΛ    |  |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(7)</sup>                     |                                                     |                                                  | 40  | 50                                               | kΩ    |  |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(7)</sup>                   | $V_{IN} = V_{DD}$                                   | 30                                               | 40  | 50                                               | — K22 |  |

| C <sub>IO</sub>  | I/O pin capacitance                                                 | -                                                   | -                                                | 5   | -                                                | pF    |  |

- 1. Data based on design simulation.

- 2. Tested in production.

- 3. FT = Five-volt tolerant, In order to sustain a voltage higher than V<sub>DD</sub>+0.3 the internal pull-up/pull-down resistors must be disabled.

- 4. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization, not tested in production.

- 5. With a minimum of 100 mV.

- 6. Leakage could be higher than max, if negative current is injected on adjacent pins.

- Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimum (~10% order).

## Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 24* and *Table 36*, respectively.

Unless otherwise specified, the parameters given in *Table 36* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

Table 36. I/O AC characteristics<sup>(1)</sup>

| MODEx<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                             | Parameter                                                       | Conditions                                                      | Max                | Unit |

|--------------------------------------------|------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|--------------------|------|

|                                            | f <sub>max(IO)out</sub>            | Maximum frequency <sup>(2)</sup>                                | $C_L = 50 \text{ pF}, V_{DD} = 2 \text{ V to } 3.6 \text{ V}$   | 2                  | MHz  |

| 10 t <sub>f(IO)out</sub>                   | t <sub>f(IO)out</sub>              | Output high to low level fall time                              | · C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V        | 125 <sup>(3)</sup> | 2    |

|                                            | t <sub>r(IO)out</sub>              | Output low to high level rise time                              | - C <sub>L</sub> – 50 рг, v <sub>DD</sub> – 2 v to 3.6 v        | 125 <sup>(3)</sup> | ns   |

|                                            | f <sub>max(IO)out</sub>            | Maximum frequency <sup>(2)</sup>                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V          | 10                 | MHz  |

| 01                                         | t <sub>f(IO)out</sub>              | Output high to low level fall time                              | C = 50 pF V = 2 V/to 2 6 V                                      | 25 <sup>(3)</sup>  | 20   |

| t <sub>r(IC</sub>                          | t <sub>r(IO)out</sub>              | Output low to high level rise time                              | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V          |                    | ns   |

|                                            |                                    |                                                                 | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V                        | 50                 | MHz  |

|                                            | F <sub>max(IO)out</sub>            |                                                                 | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ | 30                 | MHz  |

|                                            |                                    |                                                                 | $C_L = 50 \text{ pF}, V_{DD} = 2 \text{ V to } 2.7 \text{ V}$   | 20                 | MHz  |

|                                            |                                    |                                                                 | $C_L = 30 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ | 5 <sup>(3)</sup>   |      |

| 11                                         | Output high to low level fall time | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ | 8 <sup>(3)</sup>                                                |                    |      |

|                                            |                                    |                                                                 | $C_L = 50 \text{ pF}, V_{DD} = 2 \text{ V to } 2.7 \text{ V}$   | 12 <sup>(3)</sup>  | ns   |

|                                            | t <sub>r(IO)out</sub> Outputime    |                                                                 | $C_L = 30 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ | 5 <sup>(3)</sup>   | 113  |

|                                            |                                    | lume                                                            | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ | 8 <sup>(3)</sup>   |      |

|                                            |                                    |                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 2.7 V          | 12 <sup>(3)</sup>  |      |

| -                                          | t <sub>EXTIPW</sub>                | Pulse width of external signals detected by the EXTI controller | -                                                               | 10                 | ns   |

The I/O speed is configured using the MODEx[1:0] bits. Refer to the STM32F10xxx reference manual for a description of GPIO Port configuration register.

53/78

DocID15057 Rev 5

<sup>2.</sup> The maximum frequency is defined in Figure 24.

<sup>3.</sup> Guaranteed by design, not tested in production.

Table 39. I<sup>2</sup>C characteristics

| Symbol                    | Parameter                                                      | Standard m | ode I <sup>2</sup> C <sup>(1)(2)</sup> | Fast mode | Unit               |      |

|---------------------------|----------------------------------------------------------------|------------|----------------------------------------|-----------|--------------------|------|

| Symbol                    |                                                                | Min        | Max                                    | Min       | Max                | Oill |

| t <sub>w(SCLL)</sub>      | SCL clock low time                                             | 4.7        | -                                      | 1.3       | -                  | μs   |

| t <sub>w(SCLH)</sub>      | SCL clock high time                                            | 4.0        | -                                      | 0.6       | -                  | μδ   |

| t <sub>su(SDA)</sub>      | SDA setup time                                                 | 250        | -                                      | 100       | -                  |      |

| t <sub>h(SDA)</sub>       | SDA data hold time                                             | -          | 3450 <sup>(3)</sup>                    | -         | 900 <sup>(3)</sup> |      |

| t <sub>r(SDA)</sub>       | SDA and SCL rise time                                          | -          | 1000                                   | -         | 300                | ns   |

| $t_{f(SDA)} \ t_{f(SCL)}$ | SDA and SCL fall time                                          | -          | 300                                    | -         | 300                |      |

| t <sub>h(STA)</sub>       | Start condition hold time                                      | 4.0        | -                                      | 0.6       | -                  |      |

| t <sub>su(STA)</sub>      | Repeated Start condition setup time                            | 4.7        | -                                      | 0.6       | -                  | μs   |

| t <sub>su(STO)</sub>      | Stop condition setup time                                      | 4.0        | -                                      | 0.6       | -                  | μs   |

| t <sub>w(STO:STA)</sub>   | Stop to Start condition time (bus free)                        | 4.7        | -                                      | 1.3       | -                  | μs   |

| t <sub>SP</sub>           | Pulse width of spikes that are suppressed by the analog filter | 0          | 50 <sup>(4)</sup>                      | 0         | 50 <sup>(4)</sup>  | ns   |

| C <sub>b</sub>            | Capacitive load for each bus line                              | -          | 400                                    | -         | 400                | pF   |

<sup>1.</sup> Values guaranteed by design, not tested in production.

577

f<sub>PCLK1</sub> must be at least 2 MHz to achieve standard mode I<sup>2</sup>C frequencies. It must be at least 4 MHz to achieve fast mode I<sup>2</sup>C frequencies. It must be a multiple of 10 MHz to reach the 400 kHz maximum I2C fast mode clock.

The maximum Data hold time has only to be met if the interface does not stretch the low period of the SCL signal.

<sup>4.</sup> The analog filter minimum filtered spikes is above  $t_{SP(max)}$  to ensure that spikes width up to  $t_{SP(max)}$  are filtered.

## General PCB design guidelines

Power supply decoupling should be performed as shown in *Figure 33*. The 10 nF capacitors should be ceramic (good quality). They should be placed as close as possible to the chip.

STM32F102xx

V<sub>DDA</sub>

1 μF // 10 nF

V<sub>SSA</sub>

Figure 33. Power supply and reference decoupling

## 5.3.18 Temperature sensor characteristics

**Parameter** Unit **Symbol** Min Max Тур T<sub>L</sub><sup>(1)</sup> V<sub>SENSE</sub> linearity with temperature °C ±1.5 mV/°C Avg\_Slope<sup>(1)</sup> Average slope 4.35 V<sub>25</sub><sup>(1)</sup> Voltage at 25°C 1.42 V t<sub>START</sub>(2) Startup time 4 10 μs T<sub>S\_temp</sub>(3)(2) ADC sampling time when reading the 17.1 μs temperature

Table 49. TS characteristics

- 1. Guaranteed by characterization, not tested in production.

- 2. Data guaranteed by design, not tested in production.

- 3. Shortest sampling time can be determined in the application by multiple iterations.

Table 54. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02-Aug-2013 | 4        | Figure 2: Clock tree: added FLITFCLK and Note 3., and modified Note 1 Removed sentence in "Unless otherwise specified the parameters" in I2C interface characteristics section.  Added V <sub>IN</sub> in Table 8: General operating conditions.  Added note 5 in Table 23: HSI oscillator characteristics  Added DuCy <sub>(HSI)</sub> in Table 23: HSI oscillator characteristics  Table 24: LSI oscillator characteristics: removed note 2 related to oscillator selection, updated Note 2., and t <sub>SU(LSE)</sub> specified for various ambient temperature values.  Modified charge device model in Table 33: I/O current injection susceptibility.  Updated 'V <sub>IL</sub> ' and 'V <sub>IH</sub> ' in Table 34: I/O static characteristics.  Added notes to Figure 20: Standard I/O input characteristics - CMOS port, Figure 21: Standard I/O input characteristics - TTL port, Figure 22: 5 V tolerant I/O input characteristics - TTL port  Table 37: Output voltage characteristics: updated V <sub>OL</sub> and V <sub>OH</sub> conditions for TTL and CMOS outputs and added Note 2.  Updated Figure 24: I/O AC characteristics definition  Updated Figure 25: Recommended NRST pin protection  Updated Figure 26: I2C bus AC waveforms and measurement circuit(1)  Updated Figure 26: I2C bus AC waveforms and measurement circuit(1)  Updated Figure 26: I2C bus AC waveforms and measurement circuit(1)  Updated Table 40: SCL frequency (f <sub>PCLK1</sub> = 36 MHz, V <sub>DD_I2C</sub> = 3.3 V)  In Table 43: SPI characteristics, removed note 1 related to SPI1 remapped characteristics.  Updated Table 47: ADC characteristics  Updated Table 47: ADC characteristics |

| 14-May-2015 | 5        | Updated Table 18: Peripheral current consumption and Table 39: I2C characteristics.  Updated Section 6: Package characteristics.  Updated Section 6.1: LQFP64 package information with addition of Device marking for LQFP64 and Figure 36.  Updated Section 6.2: LQFP48 package information with addition of Device marking for LQFP48 and Figure 39.  Updated Disclaimer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |