Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |  |

|----------------------------|------------------------------------------------------------------------|--|

| Product Status             | Active                                                                 |  |

| Core Processor             | ARM® Cortex®-M3                                                        |  |

| Core Size                  | 32-Bit Single-Core                                                     |  |

| Speed                      | 48MHz                                                                  |  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                   |  |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                              |  |

| Number of I/O              | 51                                                                     |  |

| Program Memory Size        | 16KB (16K x 8)                                                         |  |

| Program Memory Type        | FLASH                                                                  |  |

| EEPROM Size                | -                                                                      |  |

| RAM Size                   | 4K x 8                                                                 |  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                              |  |

| Data Converters            | A/D 16x12b                                                             |  |

| Oscillator Type            | Internal                                                               |  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |  |

| Mounting Type              | Surface Mount                                                          |  |

| Package / Case             | 64-LQFP                                                                |  |

| Supplier Device Package    | -                                                                      |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f102r4t6a |  |

# List of tables

| Table 1.  | Device summary                                                                        | 1  |

|-----------|---------------------------------------------------------------------------------------|----|

| Table 2.  | STM32F102x4 and STM32F102x6 low-density USB access line features                      |    |

|           | and peripheral counts                                                                 | 9  |

| Table 3.  | STM32F102xx USB access line family                                                    | 12 |

| Table 4.  | Low-density STM32F102xx pin definitions                                               | 20 |

| Table 5.  | Voltage characteristics                                                               | 26 |

| Table 6.  | Current characteristics                                                               | 27 |

| Table 7.  | Thermal characteristics                                                               | 27 |

| Table 8.  | General operating conditions                                                          | 28 |

| Table 9.  | Operating conditions at power-up / power-down                                         | 28 |

| Table 10. | Embedded reset and power control block characteristics                                | 29 |

| Table 11. | Embedded internal reference voltage                                                   | 30 |

| Table 12. | Maximum current consumption in Run mode, code with data processing running from Flash | 31 |

| Table 13. | Maximum current consumption in Run mode, code with data processing running from RAM   |    |

| Table 14. | Maximum current consumption in Sleep mode, code running from Flash or RAM             |    |

| Table 15. | Typical and maximum current consumptions in Stop and Standby modes                    |    |

| Table 16. | Typical current consumption in Run mode, code with data processing                    | 00 |

| 14510 10. | running from Flash                                                                    | 36 |

| Table 17. | Typical current consumption in Sleep mode, code running from Flash or RAM             |    |

| Table 18. | Peripheral current consumption                                                        |    |

| Table 19. | High-speed external user clock characteristics.                                       |    |

| Table 20. | Low-speed external user clock characteristics                                         |    |

| Table 21. | HSE 4-16 MHz oscillator characteristics                                               |    |

| Table 22. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)                        |    |

| Table 23. | HSI oscillator characteristics                                                        |    |

| Table 24. | LSI oscillator characteristics                                                        | 44 |

| Table 25. | Low-power mode wakeup timings                                                         | 44 |

| Table 26. | PLL characteristics                                                                   |    |

| Table 27. | Flash memory characteristics                                                          | 45 |

| Table 28. | Flash memory endurance and data retention                                             | 45 |

| Table 29. | EMS characteristics                                                                   |    |

| Table 30. | EMI characteristics                                                                   | 47 |

| Table 31. | ESD absolute maximum ratings                                                          | 47 |

| Table 32. | Electrical sensitivities                                                              | 47 |

| Table 33. | I/O current injection susceptibility                                                  | 48 |

| Table 34. | I/O static characteristics                                                            | 49 |

| Table 35. | Output voltage characteristics                                                        |    |

| Table 36. | I/O AC characteristics                                                                | 53 |

| Table 37. | NRST pin characteristics                                                              | 54 |

| Table 38. | TIMx characteristics                                                                  |    |

| Table 39. | I <sup>2</sup> C characteristics                                                      | 57 |

| Table 40. | SCL frequency (f <sub>PCLK1</sub> = 36 MHz, V <sub>DD_I2C</sub> = 3.3 V)              |    |

| Table 41. | SPI characteristics                                                                   | 59 |

| Table 42. | USB startup time                                                                      |    |

| Table 43. | USB DC electrical characteristics                                                     |    |

| Table 44  | USB: Full speed electrical characteristics of the driver                              | 62 |

| Table 45. | ADC characteristics                                     | 63 |

|-----------|---------------------------------------------------------|----|

| Table 46. | $R_{AIN}$ max for $f_{ADC}$ = 12 MHz                    | 64 |

| Table 47. | ADC accuracy - limited test conditions                  | 64 |

| Table 48. | ADC accuracy                                            | 64 |

| Table 49. | TS characteristics                                      | 66 |

| Table 50. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat       |    |

|           | package mechanical data                                 | 67 |

| Table 51. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package |    |

|           | mechanical data                                         | 71 |

| Table 52. | Package thermal characteristics                         | 73 |

| Table 53. | Ordering information scheme                             | 75 |

| Table 54. | Document revision history                               | 76 |

|           |                                                         |    |

# List of figures

| Figure 1.  | STM32F102T8 medium-density USB access line block diagram                                    | . 10 |

|------------|---------------------------------------------------------------------------------------------|------|

| Figure 2.  | Clock tree                                                                                  | . 11 |

| Figure 3.  | STM32F102xx medium-density USB access line LQFP48 pinout                                    | . 19 |

| Figure 4.  | STM32F102xx medium-density USB access line LQFP64 pinout                                    | . 19 |

| Figure 5.  | Memory map                                                                                  | . 23 |

| Figure 6.  | Pin loading conditions                                                                      | . 25 |

| Figure 7.  | Pin input voltage                                                                           | . 25 |

| Figure 8.  | Power supply scheme                                                                         |      |

| Figure 9.  | Current consumption measurement scheme                                                      | . 26 |

| Figure 10. | Typical current consumption in Run mode versus temperature (at 3.6 V) -                     |      |

| J          | code with data processing running from RAM, peripherals enabled                             | . 32 |

| Figure 11. | Typical current consumption in Run mode versus temperature (at 3.6 V) -                     |      |

| J          |                                                                                             | . 32 |

| Figure 12. | Typical current consumption on V <sub>BAT</sub> with RTC on versus temperature at different |      |

|            |                                                                                             | . 34 |

| Figure 13. | Typical current consumption in Stop mode with regulator in Run mode versus                  |      |

|            | temperature at V <sub>DD</sub> = 3.3 V and 3.6 V                                            | . 34 |

| Figure 14. | Typical current consumption in Stop mode with regulator in Low-power mode versus            |      |

|            |                                                                                             | . 35 |

| Figure 15. | Typical current consumption in Standby mode versus temperature at $V_{DD}$ = 3.3 V and      |      |

|            | 3.6 V                                                                                       |      |

| Figure 16. | High-speed external clock source AC timing diagram                                          |      |

| Figure 17. | Low-speed external clock source AC timing diagram                                           |      |

| Figure 18. | Typical application with an 8 MHz crystal                                                   |      |

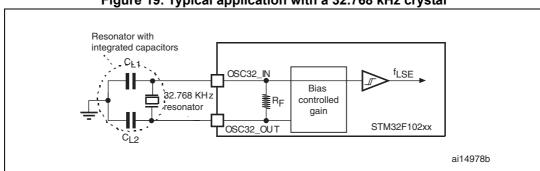

| Figure 19. | Typical application with a 32.768 kHz crystal                                               |      |

| Figure 20. | Standard I/O input characteristics - CMOS port                                              |      |

| Figure 21. | Standard I/O input characteristics - TTL port                                               |      |

| Figure 22. | 5 V tolerant I/O input characteristics - CMOS port                                          |      |

| Figure 23. | 5 V tolerant I/O input characteristics - TTL port                                           |      |

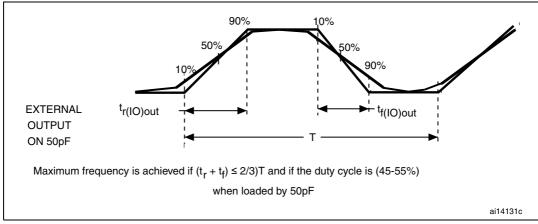

| Figure 24. | I/O AC characteristics definition                                                           |      |

| Figure 25. | Recommended NRST pin protection                                                             |      |

| Figure 26. | I <sup>2</sup> C bus AC waveforms and measurement circuit <sup>(1)</sup>                    |      |

| Figure 27. | SPI timing diagram - slave mode and CPHA=0                                                  | . 60 |

| Figure 28. | SPI timing diagram - slave mode and CPHA=1 <sup>(1)</sup>                                   | . 60 |

| Figure 29. | SPI timing diagram - master mode <sup>(1)</sup>                                             | . 61 |

| Figure 30. | USB timings: definition of data signal rise and fall time                                   | . 62 |

| Figure 31. | ADC accuracy characteristics                                                                | . 65 |

| Figure 32. | Typical connection diagram using the ADC                                                    | . 65 |

| Figure 33. | Power supply and reference decoupling                                                       |      |

| Figure 34. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline                           | . 67 |

| Figure 35. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package                                   |      |

|            | recommended footprint                                                                       | . 68 |

| Figure 36. | LQFP64 marking example (package top view)                                                   | . 69 |

| Figure 37. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline                             | . 70 |

| Figure 38. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                                     |      |

| -          | recommended footprint                                                                       | . 72 |

| Figure 39. | LQFP48 marking example (package top view)                                                   | . 72 |

| Figure 40. | LQFP64 P <sub>D</sub> max vs. T <sub>A</sub>                                                |      |

## 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of STM32F102x4 and STM32F102x6 low-density USB access line microcontrollers. For more details on the whole STMicroelectronics STM32F102xx family. please refer to Section 2.2: Full compatibility throughout the family.

The medium-density STM32F102xx datasheet should be read in conjunction with the low-, medium- and high-density STM32F10xxx reference manual.

For information on programming, erasing and protection of the internal Flash memory please refer to the *STM32F10xxx Flash programming manual*.

The reference and Flash programming manuals are both available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M3 core please refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the ARM<sup>®</sup> website.

577

## 2.1 Device overview

Table 2. STM32F102x4 and STM32F102x6 low-density USB access line features and peripheral counts

| Per                    | ipheral          | STM32F102Cx                                                                                                         |    | STM32F102Rx      |     |  |

|------------------------|------------------|---------------------------------------------------------------------------------------------------------------------|----|------------------|-----|--|

| Flash - Kbytes         |                  | 16                                                                                                                  | 32 | 16               | 32  |  |

| SRAM - Kbytes          |                  | 4                                                                                                                   | 6  | 4                | 6   |  |

| Timers                 | General-purpose  | 2                                                                                                                   | 2  | 2                | 2   |  |

|                        | SPI              | 1                                                                                                                   | 1  | 1                | 1   |  |

| Communication          | I <sup>2</sup> C | 1                                                                                                                   | 1  | 1                | 1   |  |

| interfaces             | USART            | 2                                                                                                                   | 2  | 2                | 2   |  |

|                        | USB              | 1                                                                                                                   | 1  | 1                | 1   |  |

| 12-bit synchronize     |                  | 1<br>10 channels                                                                                                    |    | 1<br>16 channels |     |  |

| GPIOs                  | 513              | 37 51                                                                                                               |    |                  |     |  |

| CPU frequency          |                  | 48 MHz                                                                                                              |    |                  |     |  |

| Operating voltage      |                  | 2.0 to 3.6 V                                                                                                        |    |                  |     |  |

| Operating temperatures |                  | Ambient temperature: -40 to +85 °C (see <i>Table 8</i> ) Junction temperature: -40 to +105 °C (see <i>Table 8</i> ) |    |                  |     |  |

| Packages               |                  | LQFP48 LQFP64                                                                                                       |    |                  | P64 |  |

## 2.2 Full compatibility throughout the family

The STM32F102xx is a complete family whose members are fully pin-to-pin, software and feature compatible. In the reference manual, the STM32F102x4 and STM32F102x6 are referred to as low-density devices and the STM32F102x8 and STM32F102xB are referred to as medium-density devices.

Low-density devices are an extension of the STM32F102x8/B devices, they are specified in the STM32F102x4/6 datasheet. Low-density devices feature lower Flash memory and RAM capacities, a timer and a few communication interfaces less.

The STM32F102x4 and STM32F102x6 are a drop-in replacement for the STM32F102x8/B medium-density devices, allowing the user to try different memory densities and providing a greater degree of freedom during the development cycle.

Moreover the STM32F102xx family is fully compatible with all existing STM32F101xx access line and STM32F103xx performance line devices.

|        | Low-density STM                    | 32F102xx devices | Medium-density STM32F102xx devices                                       |              |  |  |

|--------|------------------------------------|------------------|--------------------------------------------------------------------------|--------------|--|--|

| Pinout | 16 KB Flash 32 KB Flash            |                  | 64 KB Flash                                                              | 128 KB Flash |  |  |

|        | 4 KB RAM 6 KB RAM                  |                  | 10 KB RAM 16 KB RAM                                                      |              |  |  |

| 64     | 2 × USARTs, 2 × 16                 |                  | 3 × USARTs, 3 × 16-bit timers                                            |              |  |  |

| 48     | 1 × SPI, 1 × I <sup>2</sup> C, 1 × | × ADC, 1 × USB   | 2 × SPIs, 2 × I2Cs, 1 × ADC, 1 × USB                                     |              |  |  |

| 36     | -                                  | -                | 2 × USARTs, 3 × 16-<br>bit timers<br>1× SPI, 1× I2C, 1 ×<br>ADC, 1 × USB | -            |  |  |

Table 3. STM32F102xx USB access line family

#### 2.3 Overview

#### ARM® Cortex®-M3 core with embedded Flash and SRAM

The ARM® Cortex®-M3 processor is the latest generation of ARM® processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM® Cortex®-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM® core in the memory size usually associated with 8- and 16-bit devices.

The STM32F102xx medium-density USB access line having an embedded ARM<sup>®</sup> core is therefore compatible with all ARM<sup>®</sup> tools and software.

#### **Embedded Flash memory**

16 or 32 Kbytes of embedded Flash is available for storing programs and data.

For orderable part numbers that do not show the A internal code after the temperature range code (6), the

reference datasheet for electrical characteristics is that of the STM32F102x8/B medium-density devices.

Table 4. Low-density STM32F102xx pin definitions

| Pi     | ns     |                                |                     | 2)                       |                                                  | Alternate functions <sup>(3) (4)</sup>                       |                    |

|--------|--------|--------------------------------|---------------------|--------------------------|--------------------------------------------------|--------------------------------------------------------------|--------------------|

| LQFP48 | LQFP64 | Pin name                       | Type <sup>(1)</sup> | / O  evel <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                      | Remap              |

| 1      | 1      | $V_{BAT}$                      | S                   | ı                        | $V_{BAT}$                                        | -                                                            | -                  |

| 2      | 2      | PC13-TAMPER-RTC <sup>(5)</sup> | I/O                 | -                        | PC13 <sup>(6)</sup>                              | TAMPER-RTC                                                   | -                  |

| 3      | 3      | PC14-OSC32_IN <sup>(5)</sup>   | I/O                 | -                        | PC14 <sup>(6)</sup>                              | OSC32_IN                                                     | -                  |

| 4      | 4      | PC15-OSC32_OUT <sup>(5)</sup>  | I/O                 | ı                        | PC15 <sup>(6)</sup>                              | OSC32_OUT                                                    | 1                  |

| 5      | 5      | OSC_IN                         | I/O                 | FT                       | OSC_IN                                           | -                                                            | PD0 <sup>(7)</sup> |

| 6      | 6      | OSC_OUT                        | I/O                 | FT                       | OSC_OUT                                          | -                                                            | PD1 <sup>(7)</sup> |

| 7      | 7      | NRST                           | I/O                 | -                        | NRST                                             | -                                                            | -                  |

| -      | 8      | PC0                            | I/O                 | -                        | PC0                                              | ADC_IN10                                                     | -                  |

| -      | 9      | PC1                            | I/O                 | -                        | PC1                                              | ADC_IN11                                                     | -                  |

| -      | 10     | PC2                            | I/O                 | -                        | PC2                                              | ADC_IN12                                                     | -                  |

| -      | 11     | PC3                            | I/O                 | -                        | PC3                                              | ADC_IN13                                                     | -                  |

| 8      | 12     | V <sub>SSA</sub>               | S                   | -                        | V <sub>SSA</sub>                                 | -                                                            | -                  |

| 9      | 13     | $V_{DDA}$                      | S                   | -                        | $V_{DDA}$                                        | -                                                            | -                  |

| 10     | 14     | PA0-WKUP                       | I/O                 | -                        | PA0                                              | WKUP/USART2_CTS/<br>ADC_IN0/<br>TIM2_CH1_ETR <sup>(8)</sup>  | -                  |

| 11     | 15     | PA1                            | I/O                 | -                        | PA1                                              | USART2_RTS/<br>ADC_IN1/TIM2_CH2 <sup>(8)</sup>               | -                  |

| 12     | 16     | PA2                            | I/O                 | -                        | PA2                                              | USART2_TX/<br>ADC_IN2/TIM2_CH3 <sup>(8)</sup>                | -                  |

| 13     | 17     | PA3                            | I/O                 | -                        | PA3                                              | USART2_RX/<br>ADC_IN3/TIM2_CH4 <sup>(8)</sup>                | -                  |

| -      | 18     | V <sub>SS_4</sub>              | S                   | -                        | V <sub>SS_4</sub>                                | -                                                            | -                  |

| -      | 19     | $V_{DD\_4}$                    | S                   | -                        | $V_{DD\_4}$                                      | -                                                            | -                  |

| 14     | 20     | PA4                            | I/O                 | -                        | PA4                                              | SPI_NSS <sup>(8)</sup> /ADC_IN4<br>USART2_CK/                | -                  |

| 15     | 21     | PA5                            | I/O                 | -                        | PA5                                              | SPI_SCK <sup>(8)</sup> /ADC_IN5                              | -                  |

| 16     | 22     | PA6                            | I/O                 | -                        | PA6                                              | SPI_MISO <sup>(8)</sup> /ADC_IN6/<br>TIM3_CH1 <sup>(8)</sup> | -                  |

| 17     | 23     | PA7                            | I/O                 | -                        | PA7                                              | SPI_MOSI <sup>(8)</sup> /ADC_IN7/<br>TIM3_CH2 <sup>(8)</sup> | -                  |

| -      | 24     | PC4                            | I/O                 | -                        | PC4                                              | ADC_IN14                                                     | -                  |

| -      | 25     | PC5                            | I/O                 | -                        | PC5                                              | ADC_IN15                                                     | -                  |

| 18     | 26     | PB0                            | I/O                 | -                        | PB0                                              | ADC_IN8/TIM3_CH3 <sup>(8)</sup>                              | -                  |

| 19     | 27     | PB1                            | I/O                 | -                        | PB1                                              | ADC_IN9/TIM3_CH4 <sup>(8)</sup>                              | -                  |

**Table 6. Current characteristics**

| Symbol                               | Ratings                                                                                  | Max.  | Unit |

|--------------------------------------|------------------------------------------------------------------------------------------|-------|------|

| I <sub>VDD</sub>                     | Total current into V <sub>DD</sub> /V <sub>DDA</sub> power lines (source) <sup>(1)</sup> | 150   |      |

| l <sub>vss</sub>                     | Total current out of V <sub>SS</sub> ground lines (sink) <sup>(1)</sup>                  | 150   |      |

|                                      | Output current sunk by any I/O and control pin                                           | 25    |      |

| I <sub>IO</sub>                      | Output current source by any I/Os and control pin                                        | -25   | mA   |

| (2)                                  | Injected current five volt tolerant pins <sup>(3)</sup>                                  | -5/+0 |      |

| I <sub>INJ(PIN)</sub> <sup>(2)</sup> | Injected current on any other pin <sup>(4)</sup>                                         | ± 5   |      |

| Σl <sub>INJ(PIN)</sub>               | Total injected current (sum of all I/O and control pins) <sup>(5)</sup>                  | ± 25  |      |

- All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

- 2. Negative injection disturbs the analog performance of the device.

- 3. Positive injection is not possible on these I/Os. A negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 5* for maximum allowed input voltage values.

- 4. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 5* for maximum allowed input voltage values.

- When several inputs are submitted to a current injection, the maximum ΣI<sub>INJ(PIN)</sub> is the absolute sum of the

positive and negative injected currents (instantaneous values).

**Table 7. Thermal characteristics**

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |

| T <sub>J</sub>   | Maximum junction temperature | 150         | °C   |

| Symbol                             | Parameter                                                     | Conditions                       | Min  | Тур  | Max                 | Unit       |

|------------------------------------|---------------------------------------------------------------|----------------------------------|------|------|---------------------|------------|

| V <sub>REFINT</sub>                | Internal reference voltage                                    | -40 °C < T <sub>A</sub> < +85 °C | 1.16 | 1.20 | 1.24                | V          |

| T <sub>S_vrefint</sub> (1)         | ADC sampling time when reading the internal reference voltage | -                                | -    | 5.1  | 17.1 <sup>(2)</sup> | μs         |

| V <sub>RERINT</sub> <sup>(2)</sup> | Internal reference voltage spread over the temperature range  | V <sub>DD</sub> = 3 V ±10 mV     | -    | -    | 10                  | mV         |

| T <sub>Coeff</sub> <sup>(2)</sup>  | Temperature coefficient                                       | -                                | -    | -    | 100                 | ppm/<br>°C |

Table 11. Embedded internal reference voltage

## 5.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 9: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to Dhrystone 2.1 code.

#### **Maximum current consumption**

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled except if it is explicitly mentioned

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz)

- Prefetch in on (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled f<sub>PCLK1</sub> = f<sub>HCLK/2</sub>, f<sub>PCLK2</sub> = f<sub>HCLK</sub>

The parameters given in *Table 12* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

<sup>1.</sup> Shortest sampling time can be determined in the application by multiple iterations.

<sup>2.</sup> Guaranteed by design, not tested in production.

Table 14. Maximum current consumption in Sleep mode, code running from Flash or RAM

| Symbol          | Parameter                    | Conditions                                               | £                 | Max <sup>(1)</sup>     | Unit       |  |

|-----------------|------------------------------|----------------------------------------------------------|-------------------|------------------------|------------|--|

|                 |                              | Conditions                                               | f <sub>HCLK</sub> | T <sub>A</sub> = 85 °C | Unit       |  |

|                 |                              |                                                          | 48 MHz            | 17                     |            |  |

|                 |                              | (2)                                                      | 36 MHz            | 14                     |            |  |

|                 | Supply current in Sleep mode | External clock <sup>(2)</sup> , all peripherals enabled  | 24 MHz            | 10                     |            |  |

|                 |                              |                                                          | 16 MHz            | 7                      |            |  |

|                 |                              |                                                          | 8 MHz             | 4                      | <b>~</b> ∧ |  |

| I <sub>DD</sub> |                              |                                                          | 48 MHz            | 6                      | mA         |  |

|                 |                              |                                                          | 36 MHz            | 5                      |            |  |

|                 |                              | External clock <sup>(2)</sup> , all peripherals disabled | 24 MHz            | 4.5                    |            |  |

|                 |                              | , , , , , , , , , , , , , , , , , , ,                    | 16 MHz            | 4                      | 1          |  |

|                 |                              |                                                          | 8 MHz             | 3                      |            |  |

<sup>1.</sup> Based on characterization, tested in production at  $V_{DD}$  max and  $f_{HCLK}$  max with peripherals enabled.

Table 15. Typical and maximum current consumptions in Stop and Standby modes

|                      |                                                     |                                                                                                                                                   |                                                  |                                              | Max                                          |                           |      |

|----------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------|----------------------------------------------|---------------------------|------|

| Symbol               | Parameter                                           | Conditions                                                                                                                                        | V <sub>DD</sub> /<br>V <sub>BAT</sub> =<br>2.4 V | V <sub>DD</sub> /V <sub>BAT</sub><br>= 3.3 V | V <sub>DD</sub> /V <sub>BAT</sub><br>= 2.0 V | T <sub>A</sub> =<br>85 °C | Unit |

|                      | Supply current                                      | Regulator in Run mode. Low-speed and high-speed internal RC oscillators and high-speed oscillator OFF (no independent watchdog)                   | 21.3                                             | 21.7                                         | -                                            | 160                       |      |

| I <sub>DD</sub>      | in Stop mode                                        | Regulator in Low Power mode.<br>Low-speed and high-speed internal<br>RC oscillators and high-speed<br>oscillator OFF (no independent<br>watchdog) | 11.3                                             | 11.7                                         | -                                            | 145                       |      |

|                      | Supply current<br>in Standby<br>mode <sup>(2)</sup> | Low-speed internal RC oscillator and independent watchdog ON                                                                                      | 2.75                                             | 3.4                                          | -                                            | -                         | μA   |

|                      |                                                     | Low-speed internal RC oscillator ON, independent watchdog OFF                                                                                     | 2.55                                             | 3.2                                          | -                                            | ı                         |      |

|                      |                                                     | Low-speed internal RC oscillator and independent watchdog OFF, low-speed oscillator and RTC OFF                                                   | 1.55                                             | 1.9                                          | -                                            | 3.2                       |      |

| I <sub>DD_VBAT</sub> | Backup<br>domain supply<br>current                  | Low-speed oscillator and RTC ON                                                                                                                   | 1.1                                              | 1.4                                          | 0.9                                          | 1.9 <sup>(3)</sup>        |      |

<sup>1.</sup> Typical values are measured at  $T_A$  = 25 °C.

33/78 DocID15057 Rev 5

<sup>2.</sup> External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

#### On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in *Table 18*. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature and V<sub>DD</sub> supply voltage conditions as summarized in Table 5.

Table 18. Peripheral current consumption<sup>(1)</sup>

|                         | Peripheral               | μ <b>A</b> /MHz |

|-------------------------|--------------------------|-----------------|

|                         | DMA1                     | 15.97           |

| AHB (up to 48 MHz)      | CRC                      | 1.67            |

|                         | BusMatrix <sup>(2)</sup> | 8.33            |

|                         | APB1-Bridge              | 7.22            |

|                         | TIM2                     | 33.33           |

|                         | TIM3                     | 33.61           |

|                         | USART2                   | 12.78           |

| APB1 (up to 24 MHz)     | I2C1                     | 10.83           |

| A  B  (up to 24 Wil i2) | USB                      | 16.94           |

|                         | WWDG                     | 3.33            |

|                         | PWR                      | 1.94            |

|                         | ВКР                      | 2.78            |

|                         | IWDG                     | 1.39            |

|                         | APB2-Bridge              | 3.33            |

|                         | GPIOA                    | 7.50            |

|                         | GPIOB                    | 6.81            |

| ADD2 (up to 48 MHz)     | GPIOC                    | 7.22            |

| APB2 (up to 48 MHz)     | GPIOD                    | 6.94            |

|                         | SPI1                     | 4.86            |

|                         | USART1                   | 12.78           |

|                         | ADC1 <sup>(3)</sup> (4)  | 15.54           |

- 1.  $f_{HCLK}$  = 48 MHz,  $f_{APB1}$  =  $f_{HCLK}$ /2,  $f_{APB2}$  =  $f_{HCLK}$ , default prescaler value for each peripheral.

- 2. The BusMatrix is automatically active when at least one master is ON.

- 3. Specific conditions for ADC:  $f_{HCLK}$  = 48 MHz,  $f_{APB1}$  =  $f_{HCLK}/2$ ,  $f_{APB2}$  =  $f_{HCLK}$ ,  $f_{ADCCLK}$  =  $f_{APB2}/4$ .

- 4. When ADON bit in the ADC\_CR2 register is set to 1, there is an additional current consumption of 0, 68 mA. When we enable the ADC, there is an additional current consumption of 0, 06 mA.

Note:

For CL1 and CL2 it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator. CL1 and CL2 are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of CL1 and CL2.

Load capacitance CL has the following formula:  $CL = CL1 \times CL2 / (CL1 + CL2) + C_{stray}$  where  $C_{stray}$  is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

Caution:

To avoid exceeding the maximum value of CL1 and CL2 (15 pF) it is strongly recommended to use a resonator with a load capacitance CL  $\leq$ 7 pF. Never use a resonator with a load capacitance of 12.5 pF.

Example: if you choose a resonator with a load capacitance of CL = 6 pF, and Cstray = 2 pF, then CL1 = CL2 = 8 pF.

Figure 19. Typical application with a 32.768 kHz crystal

#### 5.3.7 Internal clock source characteristics

The parameters given in *Table 23* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

#### High-speed internal (HSI) RC oscillator

Table 23. HSI oscillator characteristics<sup>(1)</sup>

Parameter Conditions Mi

| Symbol                              | Parameter                        | Conditions                                           |                                              |      | Тур | Max              | Unit |

|-------------------------------------|----------------------------------|------------------------------------------------------|----------------------------------------------|------|-----|------------------|------|

| f <sub>HSI</sub>                    | Frequency                        |                                                      | -                                            | -    | 8   | -                | MHz  |

| DuCy <sub>(HSI)</sub>               | Duty cycle                       |                                                      | -                                            | 45   | ı   | 55               | %    |

|                                     |                                  | User-trimmed with the RCC_CR register <sup>(2)</sup> |                                              | -    | -   | 1 <sup>(3)</sup> | %    |

| Accuracy of t                       | Accuracy of the HSI              | Factory-<br>calibrated <sup>(4)(5)</sup>             | $T_A = -40 \text{ to } 105 ^{\circ}\text{C}$ | -2.0 | -   | 2.5              | %    |

| ACC <sub>HSI</sub>                  | oscillator                       |                                                      | $T_A = -10 \text{ to } 85 ^{\circ}\text{C}$  | -1.5 | -   | 2.2              | %    |

|                                     |                                  |                                                      | T <sub>A</sub> = 0 to 70 °C                  | -1.3 | ı   | 2                | %    |

|                                     |                                  | T <sub>A</sub> = 25 °C                               |                                              | -1.1 | ı   | 1.8              | %    |

| t <sub>su(HSI)</sub> <sup>(4)</sup> | HSI oscillator startup time      | -                                                    |                                              | 1    | -   | 2                | μs   |

| I <sub>DD(HSI)</sub> <sup>(4)</sup> | HSI oscillator power consumption | -                                                    |                                              | -    | 80  | 100              | μA   |

<sup>1.</sup>  $V_{DD}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

#### 5.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (Electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports), the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 29*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                                       | Conditions                                                                                                                                  | Level/Class |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                                  | $\begin{split} &V_{DD}=3.3 \text{ V, T}_{A}=+25 \text{ °C,} \\ &f_{HCLK}\!=48 \text{ MHz} \\ &\text{conforms to IEC 61000-4-2} \end{split}$ | 2B          |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on V <sub>DD</sub> and V <sub>SS</sub> pins to induce a functional disturbance | $V_{DD} = 3.3 \text{ V, } T_{A} = +25 ^{\circ}\text{C,}$<br>$f_{HCLK} = 48 \text{ MHz}$<br>conforms to IEC 61000-4-4                        | 4A          |

Table 29. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and pre qualification tests in relation with the EMC level requested for his application.

**Software recommendations:** the software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers, etc.)

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second. To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

Figure 24. I/O AC characteristics definition

## 5.3.14 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub> (see *Table 34*).

Unless otherwise specified, the parameters given in *Table 37* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

| Symbol                               | Parameter                                       | Conditions        | Min  | Тур | Max                  | Unit  |

|--------------------------------------|-------------------------------------------------|-------------------|------|-----|----------------------|-------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup> | NRST Input low level voltage                    | -                 | -0.5 | -   | 0.8                  | V     |

| V <sub>IH(NRST)</sub> <sup>(1)</sup> | NRST Input high level voltage                   | -                 | 2    | -   | V <sub>DD</sub> +0.5 | \ \ \ |

| V <sub>hys(NRST)</sub>               | NRST Schmitt trigger voltage hysteresis         | -                 | -    | 200 | -                    | mV    |

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(2)</sup> | $V_{IN} = V_{SS}$ | 30   | 40  | 50                   | kΩ    |

| V <sub>F(NRST)</sub> <sup>(1)</sup>  | NRST Input filtered pulse                       | -                 | -    | -   | 100                  | ns    |

| V <sub>NF(NRST)</sub> <sup>(1)</sup> | NRST Input not filtered pulse                   | -                 | 300  | -   | -                    | ns    |

Table 37. NRST pin characteristics

<sup>1.</sup> Guaranteed by design, not tested in production.

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order).

Table 39. I<sup>2</sup>C characteristics

| Symbol                    | Parameter                                                      | Standard m | ode I <sup>2</sup> C <sup>(1)(2)</sup> | Fast mode | e I <sup>2</sup> C <sup>(1)(2)</sup> | Unit |

|---------------------------|----------------------------------------------------------------|------------|----------------------------------------|-----------|--------------------------------------|------|

| Cymbol                    | raiainetei                                                     | Min        | Max                                    | Min       | Max                                  | Oill |

| t <sub>w(SCLL)</sub>      | SCL clock low time                                             | 4.7        | -                                      | 1.3       | -                                    | μs   |

| t <sub>w(SCLH)</sub>      | SCL clock high time                                            | 4.0        | -                                      | 0.6       | -                                    | μδ   |

| t <sub>su(SDA)</sub>      | SDA setup time                                                 | 250        | -                                      | 100       | -                                    |      |

| t <sub>h(SDA)</sub>       | SDA data hold time                                             | -          | 3450 <sup>(3)</sup>                    | -         | 900 <sup>(3)</sup>                   |      |

| t <sub>r(SDA)</sub>       | SDA and SCL rise time                                          | -          | 1000                                   | -         | 300                                  | ns   |

| $t_{f(SDA)} \ t_{f(SCL)}$ | SDA and SCL fall time                                          | -          | 300                                    | -         | 300                                  |      |

| t <sub>h(STA)</sub>       | Start condition hold time                                      | 4.0        | -                                      | 0.6       | -                                    |      |

| t <sub>su(STA)</sub>      | Repeated Start condition setup time                            | 4.7        | -                                      | 0.6       | -                                    | μs   |

| t <sub>su(STO)</sub>      | Stop condition setup time                                      | 4.0        | -                                      | 0.6       | -                                    | μs   |

| t <sub>w(STO:STA)</sub>   | Stop to Start condition time (bus free)                        | 4.7        | -                                      | 1.3       | -                                    | μs   |

| t <sub>SP</sub>           | Pulse width of spikes that are suppressed by the analog filter | 0          | 50 <sup>(4)</sup>                      | 0         | 50 <sup>(4)</sup>                    | ns   |

| C <sub>b</sub>            | Capacitive load for each bus line                              | -          | 400                                    | -         | 400                                  | pF   |

<sup>1.</sup> Values guaranteed by design, not tested in production.

577

f<sub>PCLK1</sub> must be at least 2 MHz to achieve standard mode I<sup>2</sup>C frequencies. It must be at least 4 MHz to achieve fast mode I<sup>2</sup>C frequencies. It must be a multiple of 10 MHz to reach the 400 kHz maximum I2C fast mode clock.

The maximum Data hold time has only to be met if the interface does not stretch the low period of the SCL signal.

<sup>4.</sup> The analog filter minimum filtered spikes is above  $t_{SP(max)}$  to ensure that spikes width up to  $t_{SP(max)}$  are filtered.

| Syn    | Symbol Parameter Co            |                                        | Conditions                               | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |

|--------|--------------------------------|----------------------------------------|------------------------------------------|---------------------|---------------------|------|

|        | $V_{DD}$                       | USB operating voltage <sup>(2)</sup> - |                                          | 3.0 <sup>(3)</sup>  | 3.6                 | V    |

| Input  | $V_{DI}^{(4)}$                 | Differential input sensitivity         | 0.2                                      | -                   |                     |      |

| levels | V <sub>CM</sub> <sup>(4)</sup> | Differential common mode range         | Includes V <sub>DI</sub> range           | 8.0                 | 2.5                 | V    |

|        | V <sub>SE</sub> <sup>(4)</sup> | Single ended receiver threshold        | -                                        | 1.3                 | 2.0                 |      |

| Output | $V_{OL}$                       | Static output level low                | $R_L$ of 1.5 k $\Omega$ to 3.6 $V^{(5)}$ | -                   | 0.3                 | V    |

| levels | V <sub>OH</sub>                | Static output level high               | $R_L$ of 15 kΩ to $V_{SS}^{(5)}$         | 2.8                 | 3.6                 | v    |

Table 43. USB DC electrical characteristics

- 1. All the voltages are measured from the local ground potential.

- 2. To be compliant with the USB 2.0 full-speed electrical specification, the USB\_DP (D+) pin should be pulled up with a 1.5 k $\Omega$  resistor to a 3.0-to-3.6 V voltage range.

- 3. The STM32F102xx USB functionality is ensured down to 2.7 V but not the full USB electrical characteristics which are degraded in the 2.7-to-3.0 V  $\rm V_{DD}$  voltage range.

- 4. Guaranteed by design, not tested in production.

- 5. RI is the load connected on the USB drivers

Differential Data Lines

VCRS

VSS

tf

tr

ai14137

Figure 30. USB timings: definition of data signal rise and fall time

Table 44. USB: Full speed electrical characteristics of the driver<sup>(1)</sup>

| Symbol           | Parameter                       | Conditions                      | Min | Max | Unit |

|------------------|---------------------------------|---------------------------------|-----|-----|------|

| t <sub>r</sub>   | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF          | 4   | 20  | ns   |

| t <sub>f</sub>   | Fall time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF          | 4   | 20  | ns   |

| t <sub>rfm</sub> | Rise/ fall time matching        | t <sub>r</sub> / t <sub>f</sub> | 90  | 110 | %    |

| V <sub>CRS</sub> | Output signal crossover voltage | -                               | 1.3 | 2.0 | V    |

- 1. Guaranteed by design, not tested in production.

- Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

#### 5.3.17 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 45* are derived from tests performed under ambient temperature, f<sub>PCLK2</sub> frequency and V<sub>DDA</sub> supply voltage conditions summarized in *Table 8*.

Note: It is recommended to perform a calibration after each power-up.

### General PCB design guidelines

Power supply decoupling should be performed as shown in *Figure 33*. The 10 nF capacitors should be ceramic (good quality). They should be placed as close as possible to the chip.

STM32F102xx

V<sub>DDA</sub>

1 μF // 10 nF

V<sub>SSA</sub>

Figure 33. Power supply and reference decoupling

## 5.3.18 Temperature sensor characteristics

**Parameter** Unit **Symbol** Min Max Тур T<sub>L</sub><sup>(1)</sup> V<sub>SENSE</sub> linearity with temperature °C ±1.5 mV/°C Avg\_Slope<sup>(1)</sup> Average slope 4.35 V<sub>25</sub><sup>(1)</sup> Voltage at 25°C 1.42 V t<sub>START</sub>(2) Startup time 4 10 μs T<sub>S\_temp</sub>(3)(2) ADC sampling time when reading the 17.1 μs temperature

Table 49. TS characteristics

- 1. Guaranteed by characterization, not tested in production.

- 2. Data guaranteed by design, not tested in production.

- 3. Shortest sampling time can be determined in the application by multiple iterations.

Table 51. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package mechanical data

| Cumbal | Symbol millimeters |       |       |        | inches <sup>(1)</sup> |        |

|--------|--------------------|-------|-------|--------|-----------------------|--------|

| Symbol | Min                | Тур   | Max   | Min    | Тур                   | Max    |

| Α      | -                  | -     | 1.600 | -      | -                     | 0.0630 |

| A1     | 0.050              | -     | 0.150 | 0.0020 | -                     | 0.0059 |

| A2     | 1.350              | 1.400 | 1.450 | 0.0531 | 0.0551                | 0.0571 |

| b      | 0.170              | 0.220 | 0.270 | 0.0067 | 0.0087                | 0.0106 |

| С      | 0.090              | -     | 0.200 | 0.0035 | -                     | 0.0079 |

| D      | 8.800              | 9.000 | 9.200 | 0.3465 | 0.3543                | 0.3622 |

| D1     | 6.800              | 7.000 | 7.200 | 0.2677 | 0.2756                | 0.2835 |

| D3     | -                  | 5.500 | -     | -      | 0.2165                | -      |

| E      | 8.800              | 9.000 | 9.200 | 0.3465 | 0.3543                | 0.3622 |

| E1     | 6.800              | 7.000 | 7.200 | 0.2677 | 0.2756                | 0.2835 |

| E3     | -                  | 5.500 | -     | -      | 0.2165                | -      |

| е      | -                  | 0.500 | -     | -      | 0.0197                | -      |

| L      | 0.450              | 0.600 | 0.750 | 0.0177 | 0.0236                | 0.0295 |

| L1     | -                  | 1.000 | -     | -      | 0.0394                | -      |

| k      | 0°                 | 3.5°  | 7°    | 0°     | 3.5°                  | 7°     |

| ccc    | -                  | -     | 0.080 | -      | -                     | 0.0031 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

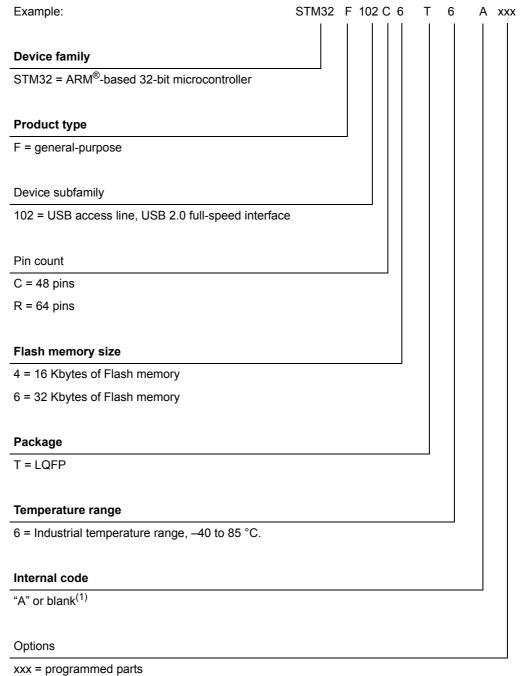

## 7 Ordering information scheme

Table 53. Ordering information scheme

zaar programmed parte

TR = tape and reel

For STM32F102x6 devices with a blank Internal code, please refer to the STM32F103x8/B datasheet available from the ST website: www.st.com.

75/78 DocID15057 Rev 5

Table 54. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02-Aug-2013 | 4        | Figure 2: Clock tree: added FLITFCLK and Note 3., and modified Note 1 Removed sentence in "Unless otherwise specified the parameters" in I2C interface characteristics section.  Added V <sub>IN</sub> in Table 8: General operating conditions.  Added note 5 in Table 23: HSI oscillator characteristics  Added DuCy(HSI) in Table 23: HSI oscillator characteristics  Table 24: LSI oscillator characteristics: removed note 2 related to oscillator selection, updated Note 2., and t <sub>SU(LSE)</sub> specified for various ambient temperature values.  Modified charge device model in Table 33: I/O current injection susceptibility.  Updated 'V <sub>IL</sub> ' and 'V <sub>IH</sub> ' in Table 34: I/O static characteristics - CMOS port, Figure 21: Standard I/O input characteristics - TTL port, Figure 22: 5 V tolerant I/O input characteristics - CMOS port and Figure 23: 5 V tolerant I/O input characteristics - TTL port  Table 37: Output voltage characteristics: updated V <sub>OL</sub> and V <sub>OH</sub> conditions for TTL and CMOS outputs and added Note 2.  Updated Figure 24: I/O AC characteristics definition  Updated Figure 25: Recommended NRST pin protection  Updated Figure 26: I2C bus AC waveforms and measurement circuit(1)  Updated Figure 26: I2C bus AC waveforms and measurement circuit(1)  Updated Table 40: SCL frequency (f <sub>PCLK1</sub> = 36 MHz, V <sub>DD_I2C</sub> = 3.3 V)  In Table 43: SPI characteristics, removed note 1 related to SPI1 remapped characteristics.  Updated Table 47: ADC characteristics |

| 14-May-2015 | 5        | Updated Table 18: Peripheral current consumption and Table 39: I2C characteristics.  Updated Section 6: Package characteristics.  Updated Section 6.1: LQFP64 package information with addition of Device marking for LQFP64 and Figure 36.  Updated Section 6.2: LQFP48 package information with addition of Device marking for LQFP48 and Figure 39.  Updated Disclaimer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |