# E·XFL

Welcome to E-XFL.COM

Infineon Technologies - CY8CLED16P01-28PVXI Datasheet

#### Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

## Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application enacific microcontrollars are analyzared to

## Details

| Details                 |                                                                                |

|-------------------------|--------------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                       |

| Applications            | Powerline Communication                                                        |

| Core Processor          | M8C                                                                            |

| Program Memory Type     | FLASH (32KB)                                                                   |

| Controller Series       | CY8CLED                                                                        |

| RAM Size                | 2K x 8                                                                         |

| Interface               | I²C, IrDA, SPI, UART/USART                                                     |

| Number of I/O           | 24                                                                             |

| Voltage - Supply        | 4.75V ~ 5.25V                                                                  |

| Operating Temperature   | -40°C ~ 85°C                                                                   |

| Mounting Type           | Surface Mount                                                                  |

| Package / Case          | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package | 28-SSOP                                                                        |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cy8cled16p01-28pvxi |

|                         |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.2.3 Coupling Circuit Reference Design

The coupling circuit couples low voltage signals from the CY8CLED16P01 to the powerline. The topology of this circuit is determined by the voltage on the powerline and design constraints mandated by powerline usage regulations.

Cypress provides reference designs for a range of powerline voltages including 110V/240V AC and 12V/24V AC/DC. The CY8CLED16P01 is capable of data communication over other AC/DC Powerlines as well with the appropriate external coupling circuit. The 110V AC and 240V AC designs are compliant to the following powerline usage regulations:

- FCC Part 15 for North America

- EN 50065-1:2001 for Europe

#### **1.3 Network Protocol**

Cypress's powerline optimized network protocol performs the functions of the data link, network, and transport layers in an ISO/OSI-equivalent model.

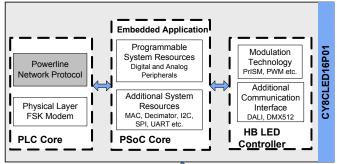

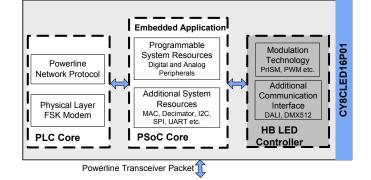

#### Figure 1-3. Powerline Network Protocol

Powerline Communication Solution

Powerline Transceiver Packet

The network protocol implemented on the CY8CLED16P01 supports the following features:

- Bidirectional half duplex communication

- Master-slave or peer-to-peer network topologies

- Multiple masters on powerline network

- 8-bit logical addressing supports up to 256 powerline nodes

- 16-bit extended logical addressing supports up to 65536 powerline nodes

- 64-bit physical addressing supports up to 2<sup>64</sup> powerline nodes

- Individual, broadcast or group mode addressing

- Carrier Sense Multiple Access (CSMA)

- Full control over transmission parameters

- Acknowledged

- Unacknowledged

- Repeated Transmit

#### 1.3.1 CSMA and Timing Parameters

- CSMA The protocol provides the random selection of a period between 85 and 115 ms (out of seven possible values in this range). Within this period, the Band-In-Use (BIU) detector must indicate that the line is not in use, before attempting a transmission.

- BIU A Band-In-Use detector, as defined under CENELEC EN 50065-1, is active whenever a signal that exceeds 86 dBµVrms anywhere in the range 131.5 kHz to 133.5 kHz is present for at least 4 ms. This threshold can be configured for different end-system applications not requiring CENELEC compliance. The modem tries to retransmit after every 85 to 115 ms when the band is in use. The transmitter times out after 1.1 seconds to 3 seconds (depending on the noise on the Powerline) and generates an interrupt to indicate that the transmitter was unable to acquire the powerline.

#### 1.3.2 Powerline Transceiver Packet

The powerline network protocol defines a Powerline Transceiver (PLT) packet structure, which is used for data transfers between nodes across the powerline. Packet formation and data transmission across the powerline network is implemented internally in the CY8CLED16P01.

A PLT packet is divided into a variable length header (minimum 6 bytes to maximum 20 bytes, depending on address type), variable length payload (minimum 0 bytes to maximum 31 bytes), and a packet CRC byte.

This packet (preceded by a one byte preamble "0xAB") is then transmitted by the powerline modem PHY and the external coupling circuit across the powerline.

The format of the PLT packet is shown in the following table.

## Table 1-1. Powerline Transceiver (PLT) Packet Structure

| Byte<br>Offset |                                                                               | Bit Offset                                                                         |       |                 |         |          |            |       |  |  |  |  |

|----------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------|-----------------|---------|----------|------------|-------|--|--|--|--|

|                | 7                                                                             | 6                                                                                  | 5     | 4               | 3       | 2        | 1          | 0     |  |  |  |  |

| 0x00           | SA<br>Type                                                                    | DA                                                                                 | Туре  | Service<br>Type | RSVD    | RSVD     | Response   | RSVD  |  |  |  |  |

| 0x01           | (8-Bi                                                                         | Destination Address<br>(8-Bit Logical, 16-Bit Extended Logical or 64-Bit Physical) |       |                 |         |          |            |       |  |  |  |  |

| 0x02           | Source Address<br>(8-Bit Logical, 16-Bit Extended Logical or 64-Bit Physical) |                                                                                    |       |                 |         |          |            |       |  |  |  |  |

| 0x03           |                                                                               |                                                                                    |       | С               | omman   | d        |            |       |  |  |  |  |

| 0x04           | F                                                                             | RSVD                                                                               |       |                 | Pa      | iyload L | ength      |       |  |  |  |  |

| 0x05           |                                                                               | Sec                                                                                | ן Num |                 | Powe    | rline Pa | cket Heade | r CRC |  |  |  |  |

| 0x06           | Payload (0 to 31 Bytes)                                                       |                                                                                    |       |                 |         |          |            |       |  |  |  |  |

|                |                                                                               |                                                                                    | Powe  | erline Tra      | nsceive | r Packe  | t CRC      |       |  |  |  |  |

# 2. High Brightness (HB) LED Controller

Powerline Communication Solution

## Figure 2-1. CY8CLED16P01: HB LED Controller

The HB LED Controller is based on Cypress's EZ-Color™ technology. EZ-Color offers the ideal control solution for high brightness (HB) LED applications requiring intelligent dimming control. EZ-Color devices combine the power and flexibility of PSoC (Programmable System-on-Chip) with Cypress's PrISM™ (Precise Illumination Signal Modulation) modulation technology providing lighting designers a fully customizable and integrated lighting solution platform.

The CY8CLED16P01 supports up to 16 independent LED channels with up to 32 bits of resolution per channel, giving lighting designers the flexibility to choose the LED array size and color quality. PSoC Designer software, with lighting-specific user modules, significantly cuts development time and simplifies implementation of fixed color points through temperature and LED binning compensation. EZ-Color's virtually limitless analog and digital customization enable simple integration of features in addition to intelligent lighting, such as battery charging, image stabilization, and motor control during the development process. These features, along with Cypress's best-in-class quality and design support, make EZ-Color the ideal choice for intelligent HB LED control applications.

The list of functions that EZ-Color devices implement are:

- LED Dimming Modulation

- Pulse Density Modulation Techniques

DMX512

DALI

- Digital Communication for Lighting

- LED Temperature Compensation

- 3- and 4-Channel Color Mixing

Including LED Binning Compensation

- Optical Feedback Algorithms

## 2.1 LED Dimming Modulation

The LED Dimming modulators are an important part of any HB LED application. All EZ-Color controllers are capable of three primary types of LED dimming modulations. These are:

- Pulse Width Modulation (PWM)

- Precise Illumination Signal Modulation (PrISM)

- Delta Sigma Modulated PWM (DSPWM)

PWM is among the most commonly used and conventional methods of modulation. It is straightforward to use and effective in practice. There are two additional techniques of modulation supported by EZ-Color that are superior to using the PWM alone:

- PrISM is a modulation technique that is developed and patented by Cypress. It results in reduced EMI as compared to the PWM technique while still providing adequate dimming control for LEDs.

- The Delta Sigma Modulated PWM technique provides higher resolution while using the same hardware resources as a conventional PWM.

LED dimming modulators use digital block resources. Digital blocks are configurable 8-bit digital peripherals. There are two types of digital blocks in the CY8CLED16P01: basic and communication. Usually, there are equal numbers of each. Any communication functions must be implemented using communication blocks but basic, noncommunication functions are implemented using either kind of block.

PWM and DSPWM modulators can have a dimming resolution of up to 16 bits. A PrISM modulator can theoretically have a dimming resolution of up to 32 bits, but the maximum recommended resolution for these modulators is 13 bits. This is because the output signal of a PrISM modulator has a frequency output range that increases with the resolution of the modulator. This increase in frequency output range is undesirable as it goes beyond the switching frequency of the current driver. Therefore, a resolution of 13 bits or lower is recommended for a PrISM modulator. Refer to application note AN47372, *PrISM Technology for LED Dimming* on http://www.cypress.com, for details.

To determine the number of digital blocks used by one PWM or PrISM modulator, use Equation 1. Note that a partial digital block cannot be used, so the result must always be rounded up. In Equation 1, n is the dimming resolution of the modulator. The resolution of dimming is determined by the color accuracy needed for the end application.

Equation 1

$$DigBlocks_{PWM,PRISM} = \frac{n}{8}$$

Document Number: 001-49263 Rev. \*E

# 3. PSoC Core

The CY8CLED16P01 is based on the Cypress PSoC<sup>®</sup> 1 architecture. The PSoC platform consists of many *Programmable System-on-chip Controller* devices. These devices are designed to replace multiple traditional MCU-based system components with one, low cost single-chip programmable device. PSoC devices include configurable blocks of analog and digital logic, and programmable interconnects. This architecture enables the user to create customized peripheral configurations that match the requirements of each individual application. Additionally, a fast CPU, Flash program memory, SRAM data memory, and configurable I/Os are included in a range of convenient pinouts and packages.

The PSoC architecture, as shown in Figure 3-1., consists of four main areas: PSoC Core, Digital System, Analog System, and System Resources. Configurable global busing enables all the device resources to be combined into a complete custom system. The CY8CLED16P01 family can have up to five I/O ports that connect to the global digital and analog interconnects, providing access to 16 digital blocks and 12 analog blocks.

The PSoC Core is a powerful engine that supports a rich feature set. The core includes a CPU, memory, clocks, and configurable GPIO (General Purpose I/O).

#### Analog Port 7 Port 6 Port 5 Port 4 Port 3 Port 2 Port 1 Port 0 Drivers YSTEM BUS Global Digital Interconnect Global Analog Interconned SRAM **PSoC CORE** SROM Flash 32K 2K CPU Core (M8C) Sleep and Interrupt Watchdog Controller Multiple Clock Sources (Includes IMO, ILO, PLL, and ECO) DIGITAL SYSTEM ANALOG SYSTEM Analog Ref. Digital Analog Block Block Arrav Arrav Analog Input Muxing POR and LVD Internal Two Digital Multiply Decimator I<sup>2</sup>C Voltage Clocks System Resets Accums. Ref. SYSTEM RESOURCES

#### Figure 3-1. PSoC Architecture

The M8C CPU core is a powerful processor with speeds up to 24 MHz, providing a 4 MIPS 8-bit Harvard architecture microprocessor. The CPU uses an interrupt controller with 25 vectors, to simplify programming of realtime embedded events. Program execution is timed and protected using the included Sleep and Watchdog timers (WDT).

Memory encompasses 32 KB of Flash for program storage, 2 KB of SRAM for data storage, and up to 2 KB of EEPROM emulated using Flash. Program Flash uses four protection levels on blocks of 64 bytes, enabling customized software IP protection.

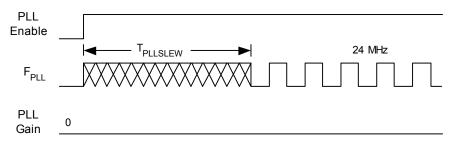

The PSoC device incorporates flexible internal clock generators, including a 24 MHz IMO (internal main oscillator) accurate to 2.5 percent over temperature and voltage. The 24 MHz IMO can also be doubled to 48 MHz for the digital system use. A low power 32 kHz ILO (internal low speed oscillator) is provided for the sleep timer and WDT. If crystal accuracy is desired, the ECO (32.768 kHz external crystal oscillator) is available for use as a Real Time Clock (RTC) and can optionally generate a crystal-accurate 24 MHz system clock using a PLL. When operating the Powerline Transceiver (PLT) user module, the ECO must be selected to ensure accurate protocol timing. The clocks, together with programmable clock dividers (as a System Resource), provide the flexibility to integrate almost any timing requirement into the PSoC device.

PSoC GPIOs provide connection to the CPU, digital, and analog resources of the device. Each pin's drive mode may be selected from eight options, enabling great flexibility in external interfacing. Every pin also has the capability to generate a system interrupt on high level, low level, and change from last read.

# 5. Development Tools

PSoC Designer is a Microsoft<sup>®</sup> Windows-based, integrated development environment for the Programmable System-on-Chip (PSoC) devices. The PSoC Designer IDE runs on Windows XP or Windows Vista.

This system provides design database management by project, an integrated debugger with In-Circuit Emulator, in-system programming support, and built in support for third party assemblers and C compilers.

PSoC Designer also supports C language compilers developed specifically for the devices in the PSoC family.

## 5.1 PSoC Designer Software Subsystems

#### 5.1.1 System-Level View

A drag-and-drop visual embedded system design environment based on PSoC Express. In the system level view you create a model of your system inputs, outputs, and communication interfaces. You define when and how an output device changes state based upon any or all other system devices. Based upon the design, PSoC Designer automatically selects one or more PSoC Programmable System-on-Chip Controllers that match your system requirements.

PSoC Designer generates all embedded code, then compiles and links it into a programming file for a specific PSoC device.

#### 5.1.2 Chip-Level View

The chip-level view is a more traditional integrated development environment (IDE) based on PSoC Designer 4.4. Choose a base device to work with and then select different onboard analog and digital components called user modules that use the PSoC blocks. Examples of user modules are ADCs, DACs, Amplifiers, and Filters. Configure the user modules for your chosen application and connect them to each other and to the proper pins. Then generate your project. This prepopulates your project with APIs and libraries that you can use to program your application.

The device editor also supports easy development of multiple configurations and dynamic reconfiguration. Dynamic configuration allows for changing configurations at run time.

#### 5.1.3 Hybrid Designs

You can begin in the system-level view, allow it to choose and configure your user modules, routing, and generate code, then switch to the chip-level view to gain complete control over on-chip resources. All views of the project share a common code editor, builder, and common debug, emulation, and programming tools.

#### 5.1.4 Code Generation Tools

PSoC Designer supports multiple third party C compilers and assemblers. The code generation tools work seamlessly within the PSoC Designer interface and have been tested with a full range of debugging tools. The choice is yours.

**Assemblers.** The assemblers allow assembly code to merge seamlessly with C code. Link libraries automatically use absolute addressing or are compiled in relative mode, and linked with other software modules to get absolute addressing.

**C Language Compilers.** C language compilers are available that support the PSoC family of devices. The products allow you to create complete C programs for the PSoC family devices.

The optimizing C compilers provide all the features of C tailored to the PSoC architecture. They come complete with embedded libraries providing port and bus operations, standard keypad and display support, and extended math functionality.

#### 5.1.5 Debugger

The PSoC Designer Debugger subsystem provides hardware in-circuit emulation, allowing you to test the program in a physical system while providing an internal view of the PSoC device. Debugger commands allow the designer to read and program and read and write data memory, read and write IO registers, read and write CPU registers, set and clear breakpoints, and provide program run, halt, and step control. The debugger also allows the designer to create a trace buffer of registers and memory locations of interest.

#### 5.1.6 Online Help System

The online help system displays online, context-sensitive help for the user. Designed for procedural and quick reference, each functional subsystem has its own context-sensitive help. This system also provides tutorials and links to FAQs and an Online Support Forum to aid the designer in getting started.

## 5.2 In-Circuit Emulator (ICE)

A low cost, high functionality In-Circuit Emulator (ICE) is available for development support. This hardware has the capability to program single devices.

The emulator consists of a base unit that connects to the PC by way of a USB port. The base unit is universal and operates with all PSoC devices. Emulation pods for each device family are available separately. The emulation pod takes the place of the PSoC device in the target board and performs full speed (24 MHz) operation.

# 7. Document Conventions

## 7.1 Acronyms Used

This table lists the acronyms used in this data sheet.

## Table 7-1. Acronyms

| Acronym           | Description                                         |  |  |  |  |  |  |

|-------------------|-----------------------------------------------------|--|--|--|--|--|--|

| AC                | alternating current                                 |  |  |  |  |  |  |

| ADC               | analog-to-digital converter                         |  |  |  |  |  |  |

| API               | application programming interface                   |  |  |  |  |  |  |

| CPU               | central processing unit                             |  |  |  |  |  |  |

| СТ                | continuous time                                     |  |  |  |  |  |  |

| DAC               | digital-to-analog converter                         |  |  |  |  |  |  |

| DC                | direct current                                      |  |  |  |  |  |  |

| EEPROM            | electrically erasable programmable read-only memory |  |  |  |  |  |  |

| FSR               | full scale range                                    |  |  |  |  |  |  |

| GPIO              | general purpose IO                                  |  |  |  |  |  |  |

| ICE               | in-circuit emulator                                 |  |  |  |  |  |  |

| IDE               | integrated development environment                  |  |  |  |  |  |  |

| 10                | input/output                                        |  |  |  |  |  |  |

| ISSP              | in-system serial programming                        |  |  |  |  |  |  |

| IPOR              | imprecise power on reset                            |  |  |  |  |  |  |

| LSb               | least-significant bit                               |  |  |  |  |  |  |

| LVD               | low voltage detect                                  |  |  |  |  |  |  |

| MSb               | most-significant bit                                |  |  |  |  |  |  |

| PC                | program counter                                     |  |  |  |  |  |  |

| PGA               | programmable gain amplifier                         |  |  |  |  |  |  |

| POR               | power on reset                                      |  |  |  |  |  |  |

| PPOR              | precision power on reset                            |  |  |  |  |  |  |

| PSoC <sup>®</sup> | Programmable System-on-Chip                         |  |  |  |  |  |  |

| PWM               | pulse width modulator                               |  |  |  |  |  |  |

| ROM               | read only memory                                    |  |  |  |  |  |  |

| SC                | switched capacitor                                  |  |  |  |  |  |  |

| SRAM              | static random access memory                         |  |  |  |  |  |  |

## 7.2 Units of Measure

A units of measure table is located in the section Electrical Specifications on page 25.

## 7.3 Numeric Naming

Hexadecimal numbers are represented with all letters in uppercase with an appended lowercase 'h' (for example, '14h' or '3Ah'). Hexadecimal numbers may also be represented by a '0x' prefix, the C coding convention. Binary numbers have an appended lowercase 'b' (for example, 01010100b' or '01000011b'). Numbers not indicated by an 'h', 'b', or 0x are decimal.

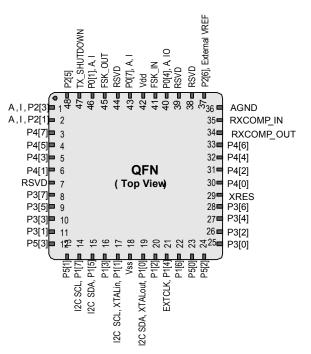

## 8.1 48-Pin Part Pinout

#### Table 8-2. 48-Pin Part Pinout (QFN)<sup>[3]</sup>

|         | Ту       | rpe    | Din Norra       | Description                                                                                                                                                  |  |  |  |  |

|---------|----------|--------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin No. | Digital  | Analog | Pin Name        | Description                                                                                                                                                  |  |  |  |  |

| 1       | 10       | I      | P2[3]           | Direct switched capacitor block input                                                                                                                        |  |  |  |  |

| 2       | 10       | I      | P2[1]           | Direct switched capacitor block input                                                                                                                        |  |  |  |  |

| 3       | 10       |        | P4[7]           |                                                                                                                                                              |  |  |  |  |

| 4       | 10       |        | P4[5]           |                                                                                                                                                              |  |  |  |  |

| 5       | 10       |        | P4[3]           |                                                                                                                                                              |  |  |  |  |

| 6       | 10       |        | P4[1]           |                                                                                                                                                              |  |  |  |  |

| 7       | Rese     | erved  | RSVD            | Reserved                                                                                                                                                     |  |  |  |  |

| 8       | 10       |        | P3[7]           |                                                                                                                                                              |  |  |  |  |

| 9       | 10       |        | P3[5]           |                                                                                                                                                              |  |  |  |  |

| 10      | 10       |        | P3[3]           |                                                                                                                                                              |  |  |  |  |

| 11      | 10       |        | P3[1]           |                                                                                                                                                              |  |  |  |  |

| 12      | 10       |        | P5[3]           |                                                                                                                                                              |  |  |  |  |

| 13      | 10       |        | P5[1]           |                                                                                                                                                              |  |  |  |  |

| 14      | 10       |        | P1[7]           | I2C Serial Clock (SCL)                                                                                                                                       |  |  |  |  |

| 15      | 10       |        | P1[5]           | I2C Serial Data (SDA)                                                                                                                                        |  |  |  |  |

| 16      | 10       |        | P1[3]           | XTAL STABILITY. Connect a 0.1 uF                                                                                                                             |  |  |  |  |

|         | -        |        |                 | capacitor between the pin and VSS.                                                                                                                           |  |  |  |  |

| 17      | IO       |        | P1[1]           | Crystal (XTALin) <sup>[2]</sup> , I2C Serial Clock (SCL),<br>ISSP-SCLK <sup>[1]</sup>                                                                        |  |  |  |  |

| 18      |          | wer    | Vss             | Ground connection.                                                                                                                                           |  |  |  |  |

| 19      | IO       |        | P1[0]           | Crystal (XTALout) <sup>[2]</sup> , I2C Serial Data (SDA), ISSP-SDATA <sup>[1]</sup>                                                                          |  |  |  |  |

| 20      | 10       |        | P1[2]           |                                                                                                                                                              |  |  |  |  |

| 21      | 10       |        | P1[4]           | Optional External Clock Input (EXTCLK) <sup>[2]</sup>                                                                                                        |  |  |  |  |

| 22      | 10       |        | P1[6]           |                                                                                                                                                              |  |  |  |  |

| 23      | 10       |        | P5[0]           |                                                                                                                                                              |  |  |  |  |

| 24      | 10       |        | P5[2]           |                                                                                                                                                              |  |  |  |  |

| 25      | 10       |        | P3[0]           |                                                                                                                                                              |  |  |  |  |

| 26      | IO       |        | P3[2]           |                                                                                                                                                              |  |  |  |  |

| 27      | 10       |        | P3[4]           |                                                                                                                                                              |  |  |  |  |

| 28      | 10       |        | P3[6]           |                                                                                                                                                              |  |  |  |  |

| 29      | In       | put    | XRES            | Active high external reset with internal pull down                                                                                                           |  |  |  |  |

| 30      | 10       |        | P4[0]           |                                                                                                                                                              |  |  |  |  |

| 31      | 10       |        | P4[2]           |                                                                                                                                                              |  |  |  |  |

| 32      | 10       |        | P4[4]           |                                                                                                                                                              |  |  |  |  |

| 33      | 10       |        | P4[6]           |                                                                                                                                                              |  |  |  |  |

| 34      |          | 0      | RXCOMP          | Analog Output to external Low Pass Filter                                                                                                                    |  |  |  |  |

| 35      |          | -      | _OUT            | Circuitry<br>Analog Input from external Low Pass Filter                                                                                                      |  |  |  |  |

|         | <b>A</b> | •      | _IN             | Circuitry                                                                                                                                                    |  |  |  |  |

| 36      | 0        | Ground | AGND            | Analog Ground                                                                                                                                                |  |  |  |  |

| 37      | 10       |        | P2[6]           | External Voltage Reference (VREF)                                                                                                                            |  |  |  |  |

| 38      |          | erved  | RSVD            | Reserved                                                                                                                                                     |  |  |  |  |

| 39      |          | erved  | RSVD            | Reserved                                                                                                                                                     |  |  |  |  |

| 40      | 10       | 10     | P0[4]           | Analog column mux input and column output                                                                                                                    |  |  |  |  |

| 41      |          | I      | FSK_IN          | Analog FSK Input                                                                                                                                             |  |  |  |  |

| 42      |          | wer    | Vdd             | Supply Voltage                                                                                                                                               |  |  |  |  |

| 43      | 10       | I      | P0[7]           | Analog column mux input                                                                                                                                      |  |  |  |  |

| 44      | Rese     | erved  | RSVD            | Reserved                                                                                                                                                     |  |  |  |  |

| 45      |          | 0      | FSK_OUT<br>]    | Analog FSK Output                                                                                                                                            |  |  |  |  |

| 46      | 10       | I      | P0[1]           | Analog column mux input                                                                                                                                      |  |  |  |  |

| 47      | 0        |        | TX_SHUT<br>DOWN | Output to disable transmit circuitry in receive<br>mode<br>Logic '0' - When the Modem is transmitting<br>Logic '1' - When the Modem is not trans-<br>mitting |  |  |  |  |

| 48      | 10       |        | P2[5]           | PSV/D - Reserved (should be left upconnected                                                                                                                 |  |  |  |  |

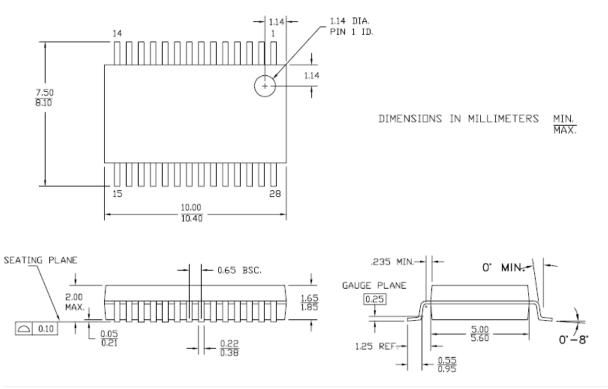

Figure 8-2. CY8CLED16P01 48-Pin PLC Device

#### Note

3. The QFN package has a center pad that must be connected to ground (Vss).

LEGEND: A = Analog, I = Input, O = Output, and RSVD = Reserved (should be left unconnected).

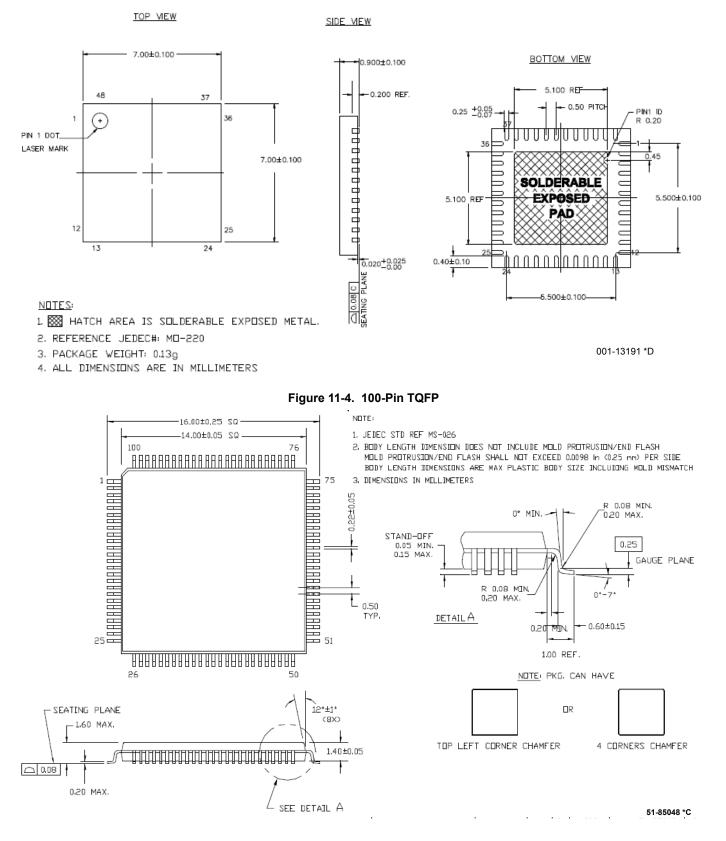

## 8.1 100-Pin Part Pinout (On-Chip Debug)

The 100-pin TQFP part is for the CY8CLED16P01-OCD On-Chip Debug PLC device. Note that the OCD parts are only used for in-circuit debugging. OCD parts are not available for production.

## Table 8-3. 100-Pin OCD Part Pinout (TQFP)

| Pin<br>No. | Digital  | Analog | Name           | Description                                                                                                                                               | Pin<br>No. | Digital | Analog        | Name           | Description                                                         |

|------------|----------|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------|---------------|----------------|---------------------------------------------------------------------|

| 1          |          |        | NC             | No Connection                                                                                                                                             | 51         |         |               | NC             | No Connection                                                       |

| 2          |          |        | NC             | No Connection                                                                                                                                             | 52         | 10      |               | P5[0]          |                                                                     |

| 3          | 10       |        | P0[1]          | Analog Column Mux Input                                                                                                                                   | 53         | 10      |               | P5[2]          |                                                                     |

| 4          | 0        |        | TX_SHUTD       | Output to disable transmit circuitry in receive                                                                                                           | 54         | 10      |               | P5[4]          |                                                                     |

|            |          |        | OŴN            | mode<br>Logic '0' - When the Modem is transmitting<br>Logic '1' - When the Modem is not transmitting                                                      |            |         |               |                |                                                                     |

| 5          | 10       |        | P2[5]          |                                                                                                                                                           | 55         | 10      |               | P5[6]          |                                                                     |

| 6          | 10       |        | P2[3]          | Direct switched capacitor block input                                                                                                                     | 56         | 10      |               | P3[0]          |                                                                     |

| 7          | 10       |        | P2[1]          | Direct switched capacitor block input                                                                                                                     | 57         | 10      |               | P3[2]          |                                                                     |

| 8          | 10       |        | P4[7]          |                                                                                                                                                           | 58         | 10      |               | P3[4]          |                                                                     |

| 9          | 10       |        | P4[5]          |                                                                                                                                                           | 59         | 10      |               | P3[6]          |                                                                     |

| 10         | 10       |        | P4[3]          |                                                                                                                                                           | 60         |         |               | HCLK           | OCD high speed clock output                                         |

| 11         | 10       |        | P4[1]          |                                                                                                                                                           | 61         |         |               | CCLK           | OCD CPU clock output                                                |

| 12         |          |        | OCDE           | OCD even data I/O                                                                                                                                         | 62         |         | iput          | XRES           | Active high pin reset with internal pull down                       |

| 13         |          |        | OCDO           | OCD odd data output                                                                                                                                       | 63         | 10      |               | P4[0]          |                                                                     |

| 14         | Rese     |        | RSVD           | Reserved                                                                                                                                                  | 64         | 10      |               | P4[2]          |                                                                     |

| 15         | Pov      | ver    | Vss            | Ground Connection                                                                                                                                         | 65         |         | wer           | Vss            | Ground Connection                                                   |

| 16         | 10       |        | P3[7]          |                                                                                                                                                           | 66         | 10      |               | P4[4]          |                                                                     |

| 17         | 10       |        | P3[5]          |                                                                                                                                                           | 67         | 10      |               | P4[6]          |                                                                     |

| 18         | 10       |        | P3[3]          |                                                                                                                                                           | 68         |         | 0             | RXCOMP_OUT     | Analog Output to external Low Pass Filter<br>Circuitry              |

| 19         | 10       |        | P3[1]          |                                                                                                                                                           | 69<br>70   |         |               | RXCOMP_IN      | Analog Input from external Low Pass Filter<br>Circuitry             |

| 20         | 10       |        | P5[7]          |                                                                                                                                                           | 70         |         |               | AGND           | Analog Ground                                                       |

| 21         | 10       |        | P5[5]          |                                                                                                                                                           | 71         |         | 1             | NC             | No Connection                                                       |

| 22         | 10       |        | P5[3]          |                                                                                                                                                           | 72         | 10      |               | P2[6]          | External Voltage Reference (VREF) input                             |

| 23         | 10       |        | P5[1]          |                                                                                                                                                           | 73         | - D     |               | NC             | No Connection                                                       |

| 24         | 10       |        | P1[7]          | I2C Serial Clock (SCL)                                                                                                                                    | 74         | Res     | erved         | RSVD           | Reserved                                                            |

| 25         |          |        | NC             | No Connection                                                                                                                                             | 75         |         |               | NC             | No Connection                                                       |

| 26         |          |        | NC             | No Connection                                                                                                                                             | 76         |         |               | NC             | No Connection                                                       |

| 27         |          |        | NC             | No Connection                                                                                                                                             | 77         | Res     | Reserved RSVD |                | Reserved                                                            |

| 28<br>29   | 10<br>10 |        | P1[5]          | I2C Serial Data (SDA)                                                                                                                                     | 78<br>79   |         |               | NC             | No Connection                                                       |

| 29<br>30   | 10       |        | P1[3]          | I <sub>FMTEST</sub> , XTAL_STABILITY. Connect a 0.1 uF<br>capacitor between the pin and VSS.<br>Crystal (XTALin) <sup>[2]</sup> , I2C Serial Clock (SCL), | 80         | 10      | IO            | P0[4]<br>NC    | Analog column mux input and column output,<br>VREF<br>No Connection |

| 30         | 10       |        | P1[1]*<br>NC   | TC SCLK<br>No Connection                                                                                                                                  | 81         |         |               |                |                                                                     |

| 31         | Pov      | Nor    | Vdd            |                                                                                                                                                           | 81<br>82   | Da      | wer           | FSK_IN<br>Vdd  | Analog FSK Input                                                    |

| 32         | POV      | vei    | NC             | Supply Voltage<br>No Connection                                                                                                                           | 82<br>83   | -       | ower          | Vdd<br>Vdd     | Supply Voltage Supply Voltage                                       |

| 33         | Pov      | Nor    | Vss            | Ground Connection                                                                                                                                         | 83<br>84   | -       | ower          | Vaa<br>Vss     | Ground Connection                                                   |

| 34         | FU       |        | NC             | No Connection                                                                                                                                             | 85         |         | wer           | Vss<br>Vss     | Ground Connection                                                   |

| 35         | 10       |        | P7[7]          |                                                                                                                                                           | 86         | 10      |               | P6[0]          |                                                                     |

| 36         | 10       |        | P7[7]<br>P7[6] |                                                                                                                                                           | 87         | 10      |               | P6[0]<br>P6[1] |                                                                     |

| 37         | 10       |        | P7[0]          |                                                                                                                                                           | 88         | 10      |               | P6[2]          |                                                                     |

| 38         | 10       |        | P7[5]          |                                                                                                                                                           | 89         | 10      |               | P6[2]          |                                                                     |

| 40         | 10       |        | P7[3]          |                                                                                                                                                           | 89<br>90   | 10      |               | P6[3]          |                                                                     |

| 40         | 10       |        | P7[3]          |                                                                                                                                                           | 90<br>91   | 10      |               | P6[5]          |                                                                     |

| 41         | 10       |        | P7[1]          |                                                                                                                                                           | 91         | 10      |               | P6[6]          |                                                                     |

| 42         | 10       |        | P7[1]<br>P7[0] |                                                                                                                                                           | 92<br>93   | 10      |               | P6[0]<br>P6[7] |                                                                     |

| 43         | 10       |        | P1[0]*         | Crystal (XTALout) <sup>[2]</sup> , I2C Serial Data (SDA),<br>TC SDATA                                                                                     | 93<br>94   | 10      | 1             | NC             | No Connection                                                       |

| 45         | 10       |        | P1[2]          | V <sub>FMTEST</sub>                                                                                                                                       | 95         | 10      |               | P0[7]          | Analog Column Mux Input                                             |

| 46         | 10       |        | P1[4]          | Optional External Clock Input (EXTCLK) <sup>[2]</sup>                                                                                                     | 96         |         | · ·           | NC             | No Connection                                                       |

| 47         | 10       |        | P1[6]          |                                                                                                                                                           | 97         | Res     | erved         | RSVD           | Reserved                                                            |

| 48         | 10       |        | NC             | No Connection                                                                                                                                             | 97<br>98   | 1103    | Giveu         | NC             | No Connection                                                       |

| 49         |          |        | NC             | No Connection                                                                                                                                             | 99         |         | 0             | FSK OUT        | Analog FSK Output                                                   |

| 50         |          |        | NC             | No Connection                                                                                                                                             | 100        |         | Ŭ             | NC             | No Connection                                                       |

|            |          |        | ···•           |                                                                                                                                                           |            |         |               |                |                                                                     |

LEGEND A = Analog, I = Input, O = Output, NC = No Connection, TC/TM: Test, TC/TM: Test, RSVD = Reserved (should be left unconnected).

## 9. Register Reference

This section lists the registers of the CY8CLED16P01 PLC device. For detailed register information, refer to the *PLC Technical Reference Manual*.

#### 9.1 Register Conventions

The register conventions specific to this section are listed in the following table.

| Convention | Description                  |  |  |  |  |

|------------|------------------------------|--|--|--|--|

| R          | Read register or bit(s)      |  |  |  |  |

| W          | Write register or bit(s)     |  |  |  |  |

| L          | Logical register or bit(s)   |  |  |  |  |

| С          | Clearable register or bit(s) |  |  |  |  |

| #          | Access is bit specific       |  |  |  |  |

## 9.2 Register Mapping Tables

The CY8CLEDP01 device has a total register address space of 512 bytes. The register space is referred to as I/O space and is divided into two banks. The XOI bit in the Flag register (CPU\_F) determines which bank the user is currently in. When the XOI bit is set the user is in Bank 1.

**Note** In the following register mapping tables, blank fields are reserved and should not be accessed.

| Table 9-1. | <b>Register Ma</b> | o Bank 0 | Table: | User Space |

|------------|--------------------|----------|--------|------------|

| 10010 0 11 | regiotor ma        |          |        | 000. 00000 |

| Name     | Addr<br>(0,Hex) | Access |          | Addr<br>(0,Hex) | Access | Name     | Addr<br>(0,Hex) | Access | Name     | Addr<br>(0,Hex) | Access |

|----------|-----------------|--------|----------|-----------------|--------|----------|-----------------|--------|----------|-----------------|--------|

| PRTODR   | 00              | RW     | DBB20DR0 | 40              | #      | ASC10CR0 | 80              | RW     | RDI2RI   | C0              | RW     |

| PRTOIE   | 01              | RW     | DBB20DR1 | 41              | W      | ASC10CR1 | 81              | RW     | RDI2SYN  | C1              | RW     |

| PRT0GS   | 02              | RW     | DBB20DR2 | 42              | RW     | ASC10CR2 | 82              | RW     | RDI2IS   | C2              | RW     |

| PRT0DM2  | 03              | RW     | DBB20CR0 | 43              | #      | ASC10CR3 | 83              | RW     | RDI2LT0  | C3              | RW     |

| PRT1DR   | 04              | RW     | DBB21DR0 | 44              | #      | ASD11CR0 | 84              | RW     | RDI2LT1  | C4              | RW     |

| PRT1IE   | 05              | RW     | DBB21DR1 | 45              | W      | ASD11CR1 | 85              | RW     | RDI2RO0  | C5              | RW     |

| PRT1GS   | 06              | RW     | DBB21DR2 | 46              | RW     | ASD11CR2 | 86              | RW     | RDI2RO1  | C6              | RW     |

| PRT1DM2  | 07              | RW     | DBB21CR0 | 47              | #      | ASD11CR3 | 87              | RW     |          | C7              |        |

| PRT2DR   | 08              | RW     | DCB22DR0 | 48              | #      | ASC12CR0 | 88              | RW     | RDI3RI   | C8              | RW     |

| PRT2IE   | 09              | RW     | DCB22DR1 | 49              | W      | ASC12CR1 | 89              | RW     | RDI3SYN  | C9              | RW     |

| PRT2GS   | 0A              | RW     | DCB22DR2 | 4A              | RW     | ASC12CR2 | 8A              | RW     | RDI3IS   | CA              | RW     |

| PRT2DM2  | 0B              | RW     | DCB22CR0 | 4B              | #      | ASC12CR3 | 8B              | RW     | RDI3LT0  | СВ              | RW     |

| PRT3DR   | 0C              | RW     | DCB23DR0 | 4C              | #      | ASD13CR0 | 8C              | RW     | RDI3LT1  | CC              | RW     |

| PRT3IE   | 0D              | RW     | DCB23DR1 | 4D              | W      | ASD13CR1 | 8D              | RW     | RDI3RO0  | CD              | RW     |

| PRT3GS   | 0E              | RW     | DCB23DR2 | 4E              | RW     | ASD13CR2 | 8E              | RW     | RDI3RO1  | CE              | RW     |

| PRT3DM2  | 0F              | RW     | DCB23CR0 | 4F              | #      | ASD13CR3 | 8F              | RW     |          | CF              |        |

| PRT4DR   | 10              | RW     | DBB30DR0 | 50              | #      | ASD20CR0 | 90              | RW     | CUR_PP   | D0              | RW     |

| PRT4IE   | 11              | RW     | DBB30DR1 | 51              | W      | ASD20CR1 | 91              | RW     | STK_PP   | D1              | RW     |

| PRT4GS   | 12              | RW     | DBB30DR2 | 52              | RW     | ASD20CR2 | 92              | RW     |          | D2              |        |

| PRT4DM2  | 13              | RW     | DBB30CR0 | 53              | #      | ASD20CR3 | 93              | RW     | IDX_PP   | D3              | RW     |

| PRT5DR   | 14              | RW     | DBB31DR0 | 54              | #      | ASC21CR0 | 94              | RW     | MVR_PP   | D4              | RW     |

| PRT5IE   | 15              | RW     | DBB31DR1 | 55              | W      | ASC21CR1 | 95              | RW     | MVW_PP   | D5              | RW     |

| PRT5GS   | 16              | RW     | DBB31DR2 | 56              | RW     | ASC21CR2 | 96              | RW     | I2C_CFG  | D6              | RW     |

| PRT5DM2  | 17              | RW     | DBB31CR0 | 57              | #      | ASC21CR3 | 97              | RW     | I2C_SCR  | D7              | #      |

| PRT6DR   | 18              | RW     | DCB32DR0 | 58              | #      | ASD22CR0 | 98              | RW     | I2C_DR   | D8              | RW     |

| PRT6IE   | 19              | RW     | DCB32DR1 | 59              | W      | ASD22CR1 | 99              | RW     | I2C_MSCR | D9              | #      |

| PRT6GS   | 1A              | RW     | DCB32DR2 | 5A              | RW     | ASD22CR2 | 9A              | RW     | INT_CLR0 | DA              | RW     |

| PRT6DM2  | 1B              | RW     | DCB32CR0 | 5B              | #      | ASD22CR3 | 9B              | RW     | INT_CLR1 | DB              | RW     |

| PRT7DR   | 1C              | RW     | DCB33DR0 | 5C              | #      | ASC23CR0 | 9C              | RW     | INT_CLR2 | DC              | RW     |

| PRT7IE   | 1D              | RW     | DCB33DR1 | 5D              | W      | ASC23CR1 | 9D              | RW     | INT_CLR3 | DD              | RW     |

| PRT7GS   | 1E              | RW     | DCB33DR2 | 5E              | RW     | ASC23CR2 | 9E              | RW     | INT_MSK3 | DE              | RW     |

| PRT7DM2  | 1F              | RW     | DCB33CR0 | 5F              | #      | ASC23CR3 | 9F              | RW     | INT_MSK2 | DF              | RW     |

| DBB00DR0 | 20              | #      | AMX_IN   | 60              | RW     |          | A0              |        | INT_MSK0 | E0              | RW     |

| DBB00DR1 | 21              | W      |          | 61              |        |          | A1              |        | INT_MSK1 | E1              | RW     |

| DBB00DR2 | 22              | RW     |          | 62              |        |          | A2              |        | INT_VC   | E2              | RC     |

| DBB00CR0 | 23              | #      | ARF_CR   | 63              | RW     |          | A3              |        | RES_WDT  | E3              | W      |

| DBB01DR0 | 24              | #      | CMP_CR0  | 64              | #      |          | A4              | 1      | DEC_DH   | E4              | RC     |

| DBB01DR1 | 25              | W      | ASY_CR   | 65              | #      |          | A5              | 1      | DEC_DL   | E5              | RC     |

| DBB01DR2 | 26              | RW     | CMP_CR1  | 66              | RW     |          | A6              |        | DEC_CR0  | E6              | RW     |

| DBB01CR0 | 27              | #      |          | 67              |        |          | A7              |        | DEC_CR1  | E7              | RW     |

| DCB02DR0 | 28              | #      |          | 68              |        | MUL1_X   | A8              | W      | MULO_X   | E8              | W      |

| DCB02DR1 | 29              | W      |          | 69              | 1      | MUL1 Y   | A9              | W      | MUL0_Y   | E9              | W      |

# Access is bit specific.

# **10. Electrical Specifications**

This section presents the DC and AC electrical specifications of the CY8CLED16P01 device. For the most up to date electrical specifications, confirm that you have the most recent data sheet by going to the web at http://www.cypress.com.

Specifications are valid for -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C and T<sub>J</sub>  $\leq$  100°C, except where noted.

The following table lists the units of measure that are used in this section.

## Table 10-1. Units of Measure

| Symbol | Unit of Measure             | Symbol | Unit of Measure               |

|--------|-----------------------------|--------|-------------------------------|

| °C     | degrees Celsius             | μW     | microwatts                    |

| dB     | decibels                    | mA     | milliamperes                  |

| fF     | femtofarads                 | ms     | milliseconds                  |

| Hz     | hertz                       | mV     | millivolts                    |

| KB     | 1024 bytes                  | nA     | nanoamperes                   |

| Kbit   | 1024 bits                   | ns     | nanoseconds                   |

| kHz    | kilohertz                   | nV     | nanovolts                     |

| kΩ     | kilohms                     | Ω      | ohms                          |

| MHz    | megahertz                   | pА     | picoamperes                   |

| MΩ     | megaohms                    | pF     | picofarads                    |

| μA     | microamperes                | рр     | peak-to-peak                  |

| μF     | microfarads                 | ppm    | parts per million             |

| μH     | microhenrys                 | ps     | picoseconds                   |

| μS     | microseconds                | sps    | samples per second            |

| μV     | microvolts                  | σ      | sigma: one standard deviation |

| μVrms  | microvolts root-mean-square | V      | volts                         |

## **10.1 Absolute Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested.

## Table 10-2. Absolute Maximum Ratings

| Symbol            | Description                                                      | Min          | Тур | Max          | Units | Notes                                                                                                                                                                                         |

|-------------------|------------------------------------------------------------------|--------------|-----|--------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>STG</sub>  | Storage Temperature                                              | -55          | 25  | +100         | °C    | Higher storage temperatures reduce<br>data retention time. Recommended<br>storage temperature is +25°C ± 25°C.<br>Extended duration storage tempera-<br>tures above 65°C degrade reliability. |

| T <sub>A</sub>    | Ambient Temperature with Power<br>Applied                        | -40          | -   | +85          | °C    |                                                                                                                                                                                               |

| Vdd               | Supply Voltage on Vdd Relative to Vss                            | -0.5         | -   | +6.0         | V     |                                                                                                                                                                                               |

| V <sub>IO</sub>   | DC Input Voltage                                                 | Vss -<br>0.5 | -   | Vdd +<br>0.5 | V     |                                                                                                                                                                                               |

| V <sub>IOZ</sub>  | DC Voltage Applied to Tri-state                                  | Vss -<br>0.5 | -   | Vdd +<br>0.5 | V     |                                                                                                                                                                                               |

| I <sub>MIO</sub>  | Maximum Current into any Port Pin                                | -25          | _   | +50          | mA    |                                                                                                                                                                                               |

| I <sub>MAIO</sub> | Maximum Current into any Port Pin<br>Configured as Analog Driver | -50          | _   | +50          | mA    |                                                                                                                                                                                               |

| ESD               | Electro Static Discharge Voltage                                 | 2000         | -   | -            | V     | Human Body Model ESD                                                                                                                                                                          |

| LU                | Latch-up Current                                                 | _            | _   | 200          | mA    |                                                                                                                                                                                               |

## 10.2 Operating Temperature

#### Table 10-3. Operating Temperature

| Symbol         | Description          | Min | Тур | Max  | Units | Notes                                                                                                                                                                            |

|----------------|----------------------|-----|-----|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>A</sub> | Ambient Temperature  | -40 | -   | +85  | °C    |                                                                                                                                                                                  |

| Tj             | Junction Temperature | -40 | -   | +100 | °C    | The temperature rise from ambient to junction is package specific. See Thermal Impedances on page 41. The user must limit the power consumption to comply with this requirement. |

## **10.3 DC Electrical Characteristics**

## 10.3.1 DC Chip-Level Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V and -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C. Typical parameters apply to 5V at 25°C and are for design guidance only.

## Table 10-4. DC Chip-Level Specifications

| Symbol           | Description                 | Min  | Тур | Max  | Units | Notes                                                                                                                                      |

|------------------|-----------------------------|------|-----|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Vdd              | Supply Voltage              | 4.75 | -   | 5.25 | V     |                                                                                                                                            |

| I <sub>DD</sub>  | Supply Current              | -    | 8   | 14   | mA    | Conditions are 5.0V, $T_A = 25^{\circ}C$ ,<br>CPU = 3 MHz, SYSCLK doubler disabled,<br>VC1 = 1.5 MHz, VC2 = 93.75 kHz,<br>VC3 = 0.366 kHz. |

| V <sub>REF</sub> | Reference Voltage (Bandgap) | 1.28 | 1.3 | 1.32 | V     | Trimmed for appropriate Vdd.                                                                                                               |

#### 10.3.2 DC General Purpose IO Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature range: 4.75V to 5.25V and  $-40^{\circ}C \le T_{A} \le 85^{\circ}C$ . Typical parameters apply to 5V at 25°C and are for design guidance only.

#### Table 10-5. DC GPIO Specifications

| Symbol           | Description                       | Min          | Тур | Max  | Units | Notes                                                                                                                                                                       |

|------------------|-----------------------------------|--------------|-----|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R <sub>PU</sub>  | Pull Up Resistor                  | 4            | 5.6 | 8    | kΩ    |                                                                                                                                                                             |

| R <sub>PD</sub>  | Pull Down Resistor                | 4            | 5.6 | 8    | kΩ    |                                                                                                                                                                             |

| V <sub>OH</sub>  | High Output Level                 | Vdd -<br>1.0 | -   | -    | V     | IOH = 10 mA, (8 total loads, 4 on even port<br>pins (for example, P0[2], P1[4]), 4 on odd<br>port pins (for example, P0[3], P1[5])). 80<br>mA maximum combined IOH budget.  |

| V <sub>OL</sub>  | Low Output Level                  | -            | -   | 0.75 | V     | IOL = 25 mA, (8 total loads, 4 on even port<br>pins (for example, P0[2], P1[4]), 4 on odd<br>port pins (for example, P0[3], P1[5])). 150<br>mA maximum combined IOL budget. |

| I <sub>ОН</sub>  | High Level Source Current         | 10           | -   | -    | mA    | VOH = Vdd-1.0V, see the limitations of the total current in the note for VOH                                                                                                |

| I <sub>OL</sub>  | Low Level Source Current          | 25           | -   | -    | mA    | VOL = 0.75V, see the limitations of the total<br>current in the note for VOL                                                                                                |

| V <sub>IL</sub>  | Input Low Level                   | _            | _   | 0.8  | V     |                                                                                                                                                                             |

| V <sub>IH</sub>  | Input High Level                  | 2.1          | _   |      | V     |                                                                                                                                                                             |

| V <sub>H</sub>   | Input Hysterisis                  | -            | 60  | _    | mV    |                                                                                                                                                                             |

| IIL              | Input Leakage (Absolute Value)    | _            | 1   | -    | nA    | Gross tested to 1 µA.                                                                                                                                                       |

| C <sub>IN</sub>  | Capacitive Load on Pins as Input  | -            | 3.5 | 10   | pF    | Package and pin dependent. Temp = $25^{\circ}$ C.                                                                                                                           |

| C <sub>OUT</sub> | Capacitive Load on Pins as Output | _            | 3.5 | 10   | pF    | Package and pin dependent. Temp = $25^{\circ}$ C.                                                                                                                           |

#### 10.3.3 DC Operational Amplifier Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V and -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C. Typical parameters apply to 5V at 25°C and are for design guidance only.

The Operational Amplifier is a component of both the Analog Continuous Time PSoC blocks and the Analog Switched Capacitor PSoC blocks. The guaranteed specifications are measured in the Analog Continuous Time PSoC block. Typical parameters apply to 5V at 25°C and are for design guidance only.

| Symbol               | Description                                                                                                                                                                                                                                                           | Min                   | Тур                                       | Max                                       | Units                      | Notes                                                                                                                        |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------------------------|-------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------|

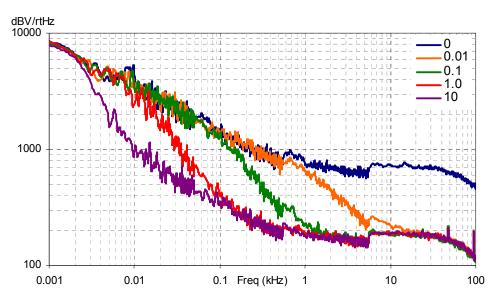

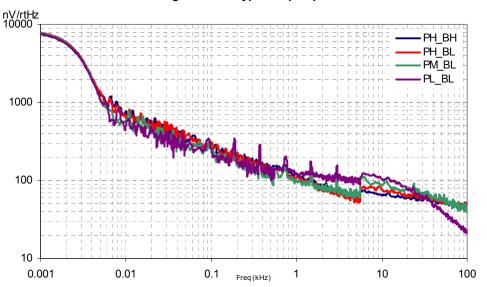

| V <sub>OSOA</sub>    | Input Offset Voltage (Absolute Value)<br>Power = Low, Opamp Bias = High<br>Power = Medium, Opamp Bias = High<br>Power = High, Opamp Bias = High                                                                                                                       | _<br>_<br>_           | 1.6<br>1.3<br>1.2                         | 10<br>8<br>7.5                            | mV<br>mV<br>mV             |                                                                                                                              |