Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Last Time Buy                                                                          |

|----------------------------|----------------------------------------------------------------------------------------|

| Core Processor             | 8051                                                                                   |

| Core Size                  | 8-Bit                                                                                  |

| Speed                      | 40MHz                                                                                  |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                             |

| Number of I/O              | 32                                                                                     |

| Program Memory Size        | 64KB (64K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 1.25К х 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                            |

| Data Converters            | -                                                                                      |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Through Hole                                                                           |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                               |

| Supplier Device Package    | · · · · · · · · · · · · · · · · · · ·                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/n78e366adg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

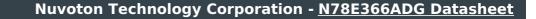

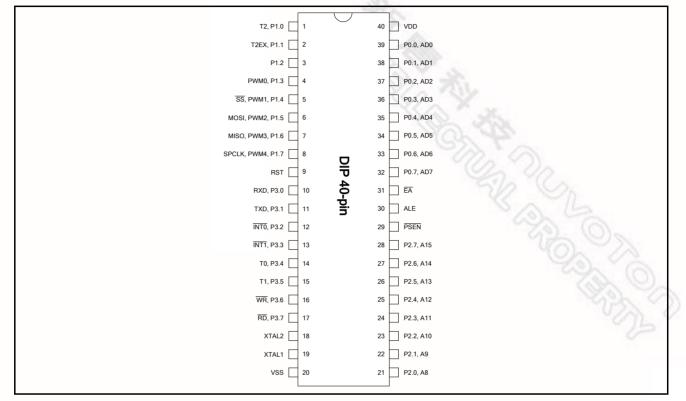

# 4. PIN CONFIGURATIONS

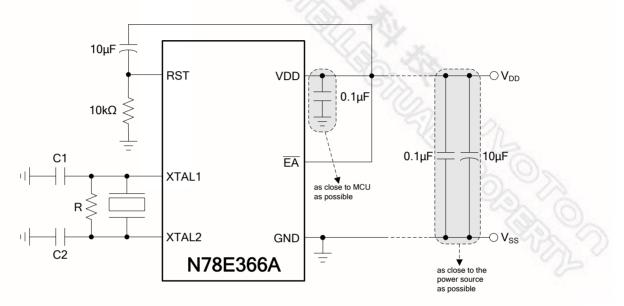

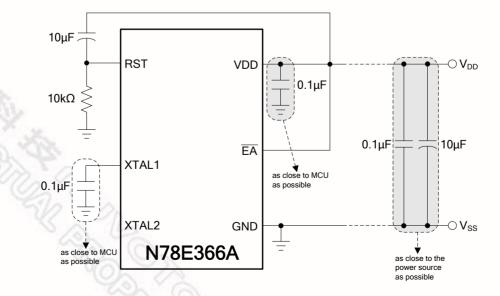

The application circuit is shown below. The user is recommended follow the circuit enclosed by gray blocks to achieve the most stable and reliable operation of MCU especially in a noisy power environment for a healthy EMS immunity. If internal RC oscillator is used as the system clock, a 0.1µF capacitor should be added to gain a precise RC frequency.

Figure 4–5. Application Circuit for Execution of Internal Program Code with External Crystal

| <b>Crystal Frequency</b> | R        | C1 C2            |         |

|--------------------------|----------|------------------|---------|

| 4MHz~33MHz               | Without  | Depend on crysta |         |

| 33MHZ~40MHz              | 5kΩ~10kΩ | specifi          | cations |

# 8. AUXILIARY RAM (XRAM)

N78E366A provides additional on-chip 1k-byte RAM called XRAM to enlarge the RAM space. It occupies the address space from 000H through 3FFH. The XRAM is enabled after all resets. The 1024 bytes of XRAM are indirectly accessed by move external instruction MOVX @DPTR or MOVX @Ri along with XRAMAH. (If XRAM is enabled, MOVX @Ri cannot be used to access external RAM anymore.) This block of XRAM shares the same logic address of 000H through 3FFH with the external RAM. A DPTR value given larger than 03FFH will map to the external RAM no matter of the value of bit XRAMEN (CHPCON.4). If the user would like to access contents within 000H to 3FFH address of the off-chip external XRAM, the XRAMEN bit should be cleared as logic 0. (Note that CHPCON is a TA writing protected SFR.) When the XRAM is accessed, the address fetching signal will not emit via P0, P2, WR, and RD. Note that the stack pointer cannot locate in any part of XRAM.

### CHPCON – Chip Control (TA protected)

| 7            | 6    | 5      | 4             | 3          | 2           | 1              | 0            |

|--------------|------|--------|---------------|------------|-------------|----------------|--------------|

| SWRST        | ISPF | LDUEN  | XRAMEN        | -          | -           | BS             | ISPEN        |

| w            | r/w  | r/w    | r/w           | -          | -           | r/w            | r/w          |

| Addrose: OEU |      | rocoty | alua: cao Tab | 0 6 2 N78E | REA SED Dog | corintions and | Pocot Valuos |

Address: 9FH

reset value: see Table 6–2. N78E366A SFR Descriptions and Reset Values

| Bit | Name   | Description                                                                                                                                 |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | XRAMEN | <ul> <li>XRAM enable.</li> <li>0 = Disable on-chip XRAM.</li> <li>1 = Enable on-chip XRAM. (The default value after all resets.)</li> </ul> |

#### XRAMAH – XRAM Address High Byte

A,#5AH

@RO,A

XRAMA

R0,#2

A,@R0

| 7            | 6 | 5 | 4 | 3 | 2 | 1           | 0            |

|--------------|---|---|---|---|---|-------------|--------------|

| -            | - | - | - | - | - | XRAMAH.1    | XRAMAH.0     |

| -            | - | - | - | - | - | r/w         | r/w          |

| Addrose: A1L | 1 |   |   |   |   | recet value | · 0000 0000h |

Address: A1F

MOV

MOV

MOV

MOVX

MOVX

reset value: 0000 0000b

|      | Bit        | Name                   | Description                                                                                                                                           |

|------|------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 7:2        | -                      | Reserved.                                                                                                                                             |

|      | 1:0        | XRAMAH[1:0]            | XRAM address high byte.<br>To set the XRAM high byte address. This setting works along with MOV @Ri<br>instructions. The demo codes are listed below. |

| XRAN | 1 demo co  | de:                    |                                                                                                                                                       |

|      | MOV<br>MOV | XRAMAH,#01H<br>R0,#23H | ;write #5AH to XRAM with address @0123H.                                                                                                              |

| AH,#01H<br>23H<br>) | ;read | from | XRAM | with | address | @0123H. |  |

|---------------------|-------|------|------|------|---------|---------|--|

|                     |       |      |      |      |         |         |  |

# 9. I/O PORT STRUCTURE AND OPERATION

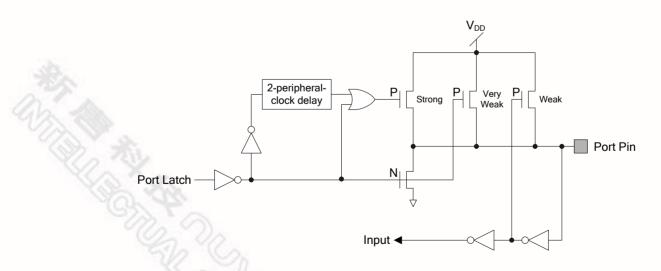

N78E366A has maximum five 8-bit width, bit-addressable ports P0~P4. The configuration of P1~P4 is the quasi bi-directional I/O. This type rules as both input and output. When the port outputs a logic high, it is weakly driven, allowing an external device to pull the pin low. When the pin is pulled low, it is driven strongly and able to sink a large current. In the quasi bi-directional I/O structure, there are three pull-up transistors. Each of them serves different purposes. One of these pull-ups, called the "very weak" pull-up, is turned on whenever the port latch contains a logic 1. The "very weak" pull-up sources a very small current that will pull the pin high if it is left floating.

A second pull-up, called the "weak" pull-up, is turned on when the outside port pin itself is at a logic 1 level. This pull-up provides the primary source current for a quasi bi-directional pin that is outputting a 1. If a pin that has a logic 1 on it is pulled low by an external device, the "weak" pull-up turns off, and only the "very weak" pull-up remains on. In order to pull the pin low under these conditions, the external device has to sink enough current (larger than  $I_{TL}$ ) to overcome the "weak" pull-up and make the voltage on the port pin below its input threshold (lower than  $V_{IL}$ ).

The third pull-up is the "strong" pull-up. This pull-up is used to speed up low-to-high transitions on a quasi bidirectional port pin when the port latch changes from a logic 0 to a logic 1. When this occurs, the strong pull-up turns on for two-peripheral-clock time in order to pull the port pin high quickly. Then it turns off and "weak: pullup continues remaining the port pin high. The quasi bi-directional port structure is shown as below.

Figure 9–1. Quasi Bi-direction I/O Structure

The default configuration of P0 is open-drain structure. To serve as an I/O port the external pull-up resistor is always necessary. N78E366A also provide an internal P0 pull-up resistors for each pins. Via setting P0UP (P0OR.0) P0 will switch on its weak pull-up internally and behave the same as the quasi bi-directional I/O pins.

| Bit | Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

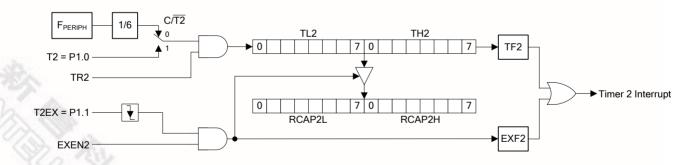

| 3   | EXEN2  | <ul> <li>Timer 2 external enable.</li> <li>This bit enables 1-to-0 transitions on T2EX trigger.</li> <li>0 = 1-to-0 transitions on T2EX is ignored.</li> <li>1 = 1-to-0 transitions on T2EX will set EXF2 logic 1. If Timer 2 is configured in capture or auto-reload mode, the 1-to-0 transitions on T2EX will cause capture or reload event.</li> </ul>                                                                                                           |

| 2   | TR2    | <ul> <li>Timer 2 run control.</li> <li>0 = Timer 2 is halted. Clearing this bit will halt Timer 2 and the current count will be preserved in TH2 and TL2.</li> <li>1 = Timer 2 is enabled.</li> </ul>                                                                                                                                                                                                                                                               |

| 1   | C/T2   | <b>Timer 2 Counter/Timer select.</b><br>0 = Timer 2 is incremented by internal peripheral clocks.<br>1 = Timer 2 is incremented by the falling edge of the external pin T2.<br>If Timer 2 would like to be set in clock-out mode, $C/\overline{T2}$ must be 0.                                                                                                                                                                                                      |

| 0   | CP/RL2 | <b>Timer 2 Capture or Reload select.</b><br>This bit selects whether Timer 2 functions in capture or auto-reload mode. EXEN2<br>must be logic 1 for 1-to-0 transitions on T2EX to be recognized and used to trigger<br>captures or reloads. If RCLK or TCLK is set, this bit is ignored and Timer 2 will<br>function in auto-reload mode.<br>0 = Auto-reload on Timer 2 overflow or 1-to-0 transition on T2EX pin.<br>1 = Capture on 1-to-0 transition at T2EX pin. |

### T2MOD – Timer 2 Mode

| 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0 |

|---|---|---|---|---|---|------|---|

| - | - | - | - | - | - | T2OE | - |

| - | - | - | - | - | - | r/w  | - |

Address: C9H

reset value: 0000 0000b

|   | Bit | Name | Description                                                                                                                                                                                                                                                                                  |

|---|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - | 7:2 | -    | Reserved.                                                                                                                                                                                                                                                                                    |

|   | 1   | T2OE | <ul> <li>Timer 2 clock-out enable.</li> <li>0 = Disable Timer 2 clock-out function. T2 pin functions either as a standard port pin or as a counter input for Timer 2.</li> <li>1 = Enable Timer 2 clock-out function. Timer 2 will drive T2 pin with a clock output if C/T2 is 0.</li> </ul> |

| 8 | 0   | -    | Reserved.                                                                                                                                                                                                                                                                                    |

### RCAP2L – Timer 2 Reload/Capture Low Byte

| 7 | 6         | 5 | 4    | 3       | 2 | 1 | 0 |

|---|-----------|---|------|---------|---|---|---|

| 5 | all       |   | RCAP | 2L[7:0] |   |   |   |

| 9 | (n. ~ 2). |   | r/   | /w      |   |   |   |

|   |           |   |      |         |   |   |   |

Address: CAH

reset value: 0000 0000b

| Bit | Name        | Description                                                                                                                                                                                                                                                                           |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | RCAP2L[7:0] | <b>Timer 2 reload/capture low byte.</b><br>This register captures and stores the low byte of Timer 2 when Timer 2 is con-<br>figured in capture mode. When Timer 2 is in auto-reload mode, baud rate<br>generator mode, or clock-out mode, it holds the low byte of the reload value. |

Table 10–1. Timer 2 Operating Modes

| Timer 2 Mode                  | RCLK (T2CON.5)<br>or<br>TCLK (T2CON.4) | CP/RL2 (T2CON.0) | T2OE (T2MOD.1) |  |

|-------------------------------|----------------------------------------|------------------|----------------|--|

| 16-bit capture <sup>[1]</sup> | 0                                      | 1                | 0              |  |

| 16-bit auto-reload            | 0                                      | 0                | 0              |  |

| Baud rate generator           | 1                                      | Х                | 0              |  |

| Clock-out <sup>[2]</sup>      | 0                                      | 0                | Gi to          |  |

[1] The capture is valid while EXEN2 (T2CON.3) is a 1. Or Timer/Counter 2 behaves just like a 16-bit timer/counter.

[2] C/T2 (T2CON.1) must be 0.

### 10.2.1 Capture Mode

The capture mode is enabled by setting the CP/RL2 bit in the T2CON register to 1. In the capture mode, Timer/Counter 2 serves as a 16 bit up counter. When the counter rolls over from FFFFH to 0000H, the TF2 bit is set, which will generate an Timer 2 interrupt request. If the EXEN2 bit is set, then a negative transition of T2EX pin (alternative function of P1.1) will cause the value in the TL2 and TH2 register to be captured by the RCAP2L and RCAP2H registers. The TH2 and TL2 keeps on counting while this capture event occurs. This capture action also causes the EXF2 (T2CON.6) bit set, which will also generate an Timer 2 interrupt. If Timer 2 interrupt enabled, both TF2 and EXF2 flags will generate interrupt vectoring to the same location. The user should check which one triggers the Timer 2 interrupt in the interrupt service routine.

Figure 10–5. Timer/Counter 2 in Capture Mode

## 10.2.2 Auto-reload Mode

The auto-reload mode is enabled by clearing the CP/RL2 bit in the T2CON register. In this mode, Timer/Counter 2 is a 16 bit up counter. When the counter rolls over from FFFFH, TF2 (T2CON.7) is set as 1 and a reload is generated that causes the contents of the RCAP2L and RCAP2H registers to be reloaded into the TL2 and TH2 registers respectively. If the EXEN2 bit is set, then a negative transition on T2EX pin will also cause a reload. This action also sets the EXF2 bit in T2CON.

| Bit | Name    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | DISMODF | <ul> <li>Disable Mode Fault error detection.</li> <li>This bit is used in combination with the SSOE (SPCR.7) bit to determine the feature of SS pin as shown in <u>Table 14–1. Slave Select Pin Configurations</u>.</li> <li>DISMODF affects only in Master mode (MSTR = 1).</li> <li>0 = Mode Fault detection is not disabled. SS serves as input pin for Mode Fault detection disregard of SSOE.</li> <li>1 = Mode Fault detection is disabled. The feature of SS follows SSOE bit.</li> </ul> |

| 2:0 | -       | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

### SPDR – Serial Peripheral Data Register

| 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|---|---|---|---|---|---|---|

| SPDR[7:0] |   |   |   |   |   |   |   |

| r/w       |   |   |   |   |   |   |   |

Address: F5H

reset value: 0000 0000b

| Bit | Name      | Description                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7:0 | SPDR[7:0] | Serial peripheral data.<br>This byte is used of transmitting or receiving data on SPI bus. A write of this byte<br>is a write to the shift register. A read of this byte is actually a read of the read<br>data buffer. In Master mode, a write to this register initiates transmission and<br>reception of a byte simultaneously. |  |  |  |  |

## 14.4 Operating Modes

### 14.4.1 Master mode

The SPI can operate in Master mode while MSTR (SPCR.4) is set as 1. Only one Master SPI device can initiate transmissions. A transmission always begins by Master through writing to SPDR. The byte written to SPDR begins shifting out on MOSI pin under the control of SPCLK. Simultaneously, another byte shifts in from the Slave on the MISO pin. After 8-bit data transfer complete, SPIF (SPSR.7) will automatically set via hardware to indicate one byte data transfer complete. At the same time, the data received from the Slave is also transferred in SPDR. The user can clear SPIF and read data out of SPDR.

### 14.4.2 Slave Mode

When MSTR is 0, the SPI operates in Slave mode. The SPCLK pin becomes input and it will be clocked by another Master SPI device. The  $\overline{SS}$  pin also becomes input. The Master device cannot exchange data with the Slave device until the  $\overline{SS}$  pin of the Slave device is externally pulled low. Before data transmissions occurs, the  $\overline{SS}$  of the Slave device must be pulled and remain low until the transmission is complete. If  $\overline{SS}$  goes

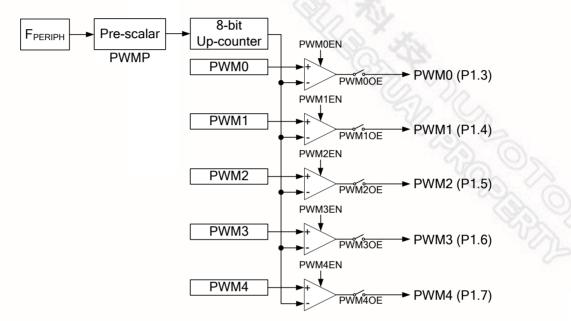

This gives a repetition frequency range of 122Hz to 31.25kHz (F<sub>PERIPH</sub> = 16MHz). By loading the PWMx registers with either 00H or FFH, the PWM channels will generate a constant low or high level output, respectively.

When a compare register PWMx is loaded with a new value, the associated output updated immediately. It does not have to wait until the end of the current counter period.

#### PWM demo code,

| MOV<br>MOV<br>MOV<br>MOV<br>MOV<br>ORL<br>ORL<br>ORL | <pre>PWMP,#128 PWM0,#0H PWM1,#40H PWM2,#80H PWM3,#0C0H PWM4,#0FFH PWMCON0,#00110011b PWMCON1,#0000001b PWMCON1,#1001100b PWMCON1,#0000010b</pre> | <pre>;determine PWM period<br/>;duty = 0%<br/>;duty = 25%<br/>;duty = 50%<br/>;duty = 75%<br/>;duty = 100%<br/>;enable PWM0~3<br/>;enable PWM4<br/>;output enable PWM0~3<br/>;output enable PWM4</pre> |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                      |                                                                                                                                                  |                                                                                                                                                                                                        |

|                                                      |                                                                                                                                                  | Publica Publica                                                                                                                                                                                        |

RETI instruction, but it would not inform the Interrupt controller that the interrupt service routine is completed. RET would leave the controller still thinking that the service routine is underway, making future interrupts impossible.

## 17.2 Interrupt Latency

The response time for each interrupt source depends on several factors, such as the nature of the interrupt and the instruction underway. In the case of external interrupts INTO and INT1, they are sampled at every machine-cycle and then their corresponding interrupt flags IE0 or IE1 will be set or reset. The value are not actually polled by the circuit until the next machine-cycle. If a request is active and all three previous conditions are met, then the hardware generated LCALL is executed. This LCALL itself takes 2 machine-cycles to be completed. Thus there is a minimum time of 3 machine-cycles between the interrupt flag being set and the interrupt service routine being executed.

A longer response time should be anticipated if any of the three conditions are not met. If a higher or equal priority is being serviced, then the interrupt latency time obviously depends on the nature of the service routine currently being executed. If the polling cycle is not the last machine-cycle of the instruction being executed, then an additional delay is introduced. The maximum response time (if no other interrupt is in service) occurs if the device is performing a write to IE, IP and then executes a MUL or DIV instruction. From the time an interrupt source is activated, the longest reaction time is 9 machine-cycles. This includes 1 machine-cycle to detect the interrupt, 2 machine-cycles to complete the IE, EIE, IP, IPH, EIP, or EIPH access, 4 machine-cycles to complete the MUL or DIV instruction and 2 machine-cycles to complete the hardware LCALL to the interrupt vector location.

Thus in a single-interrupt system the interrupt response time will always be more than 3 machine-cycles and not more than 9 machine-cycles.

CJNE A, B, Program CONFIG Verify Error RET Program\_CONFIG\_Verify\_Error: CALL Disable\_ISP mov P0,#00h SJMP \$ \*\*\*\*\*\*\* ++++++ APROM code ; \*\*\*\*\*\* \*\*\*\*\* ; AP code: DB 75h, 90h, 55h ;OPCODEs of "mov P1,#55h" ;OPCODEs of "mov P2,#0aah" ;OPCODEs of "sjmp \$" DB 75h,0A0h,0AAh DB 80h,0FEh END Publication Release Date: March 11, 2011 - 97 -Revision: V2.0

| Bit | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | -    | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0   | BOS  | <b>Brown-out status.</b><br>This bit indicates the $V_{DD}$ voltage level comparing with $V_{BOD}$ while Brown-out circuit is enabled. It is helpful to tell a Brown-out event or power resuming event occurrence. This bit is read-only and keeps 0 if Brown-out detection is not enabled.<br>0 = $V_{DD}$ voltage level is higher than $V_{BOD}$ .<br>1 = $V_{DD}$ voltage level is lower than $V_{BOD}$ . |

[1] BODEN and BORST will be directly loaded from CONFIG2 bit 7 and bit 4 after all resets.

#### Table 21–1. BOF Reset Value

| Reset source    | CBODEN (CONFIG2.7) | CBORST (CONFIG2.4) | V <sub>DD</sub> stable level | BOF |

|-----------------|--------------------|--------------------|------------------------------|-----|

| Brown-out reset | 1                  | 1                  | > V <sub>BOD</sub> always    | 1-1 |

|                 | 1                  | 1                  | > V <sub>BOD</sub> always    | 1   |

| Other resets    | 1                  | 0                  | > V <sub>BOD</sub>           | 21  |

|                 | 1                  | 0                  | < V <sub>BOD</sub>           | 0   |

|                 | 0                  | Х                  | Х                            | 0   |

Note that if BOF is 1 after chip reset, it is strongly recommended to initialize the user's program by clearing BOF.

### **PCON – Power Control**

| 7            | 6 | 5       | 4              | 3             | 2            | 1              | 0            |

|--------------|---|---------|----------------|---------------|--------------|----------------|--------------|

| SMOD         | - | -       | POF            | GF1           | GF0          | PD             | IDL          |

| r/w          | - | -       | r/w            | r/w           | r/w          | r/w            | r/w          |

| Address: 87H |   | reset v | /alue: see Tab | le 6–2. N78E3 | 366A SFR Des | scriptions and | Reset Values |

| Bit | Name | Description                                                                                                                                                                                                                                           |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | POF  | <b>Power-on reset flag.</b><br>This bit will be set as 1 after a power-on reset. It indicates a cold reset, a power-<br>on reset complete. This bit remains its value after any other resets. This flag is<br>recommended to be cleared via software. |

|     | ñs.  |                                                                                                                                                                                                                                                       |

|     |      |                                                                                                                                                                                                                                                       |

|     |      |                                                                                                                                                                                                                                                       |

|     |      |                                                                                                                                                                                                                                                       |

|     |      |                                                                                                                                                                                                                                                       |

|     |      | Publication Release Date: March 11,                                                                                                                                                                                                                   |

### CHPCON – Chip Control (TA protected)

| 7                                                                                  | 6    | 5     | 4      | 3    | 2   | 1   | 0     |

|------------------------------------------------------------------------------------|------|-------|--------|------|-----|-----|-------|

| SWRST                                                                              | ISPF | LDUEN | XRAMEN | TEX. | -   | BS  | ISPEN |

| w                                                                                  | r/w  | r/w   | r/w    | m- n | - 0 | r/w | r/w   |

| Address: 9FH reset value: see Table 6–2 N78E366A SER Descriptions and Reset Values |      |       |        |      |     |     |       |

Address: 9FH

|   | Bit | Name  | Description                                                                                                                                                |

|---|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - | 7   | SWRST | <b>Software reset.</b><br>To set this bit as a logic 1 will cause a software reset. It will automatically be cleared via hardware after reset in finished. |

### The software demo code are listed below.

| MOV TA,#0AAh      | ;TA protection.          |

|-------------------|--------------------------|

| MOV TA,#55h       | ;                        |

| ANL CHPCON, #0FDh | ;BS = 0, reset to APROM. |

| MOV TA,#0AAh      |                          |

| MOV TA,#55h       |                          |

| ORL CHPCON, #80h  | ;Software reset          |

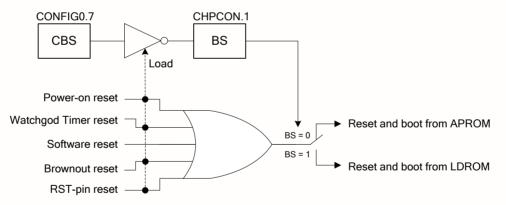

## 22.6 Boot Select

N78E366A provides users a flexible boot selection for variant application. The SFR bit BS in CHPCON.1 determines CPU booting from APROM or LDROM after any source of reset. If reset occurs and BS is 0, CPU will reboot from APPROM. Else, the CPU will reboot from LDROM.

# 23. AUXILIARY FEATURES

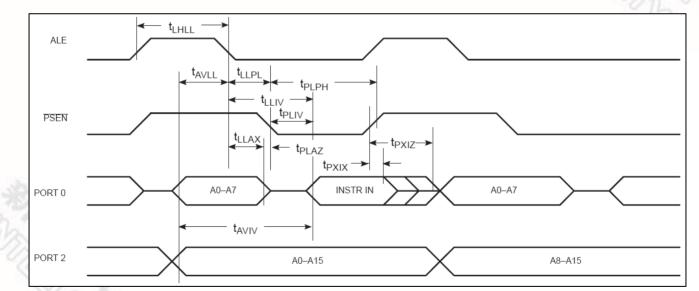

ALE is used to enable the address latch that separates the address from the data on Port 0. ALE runs at 1/6 of the Fosc in 12T mode. An ALE pulse is omitted always. The user can turn ALE signal off via setting ALEOFF to reduce EMI. ALEOFF enable will just make ALE activating during external memory access through a MOVC or MOVX instruction. ALE will stay high in other conditions.

### AUXR - Auxiliary Register

| 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0      |

|---|---|---|---|---|---|------|--------|

| - | - | - | - | - | 5 | a Ca | ALEOFF |

| - | - | - | - | - |   |      | r/w    |

Address: 8EH

reset value: 0000 0000b

| Bit | Name   | Description                                                                                                                                                                                |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | -      | Reserved.                                                                                                                                                                                  |

| 0   | ALEOFF | <ul> <li>ALE output off.</li> <li>0 = ALE is emitted always.</li> <li>1 = ALE is off normally and active only during external memory access through a MOVX or MOVC instruction.</li> </ul> |

# 24. CONFIG BYTES

N78E366A has several hardware configuration bytes, called CONFIG bytes, those are used to configure the hardware options such as the security bits, system clock source, and so on. These hardware options can be re-configured through the Programmer/Writer or ISP modes. N78E366A has three CONFIG bytes those are CONFIG0, 2 and 3. Several functions which are defined by certain CONFIG bits are also available to be re-configured by certain SFR bits. Therefore, there is a need to load such CONFIG bits into respective SFR bits. Such loading will occurs after resets. (Software reset will reload all CONFIG bytes except CBS bit in CONFIG0.) These SFR bits can be continuously controlled via user's software.

### Note that CONFIG bits marked as "-" should always keep unprogrammed.

#### CONFIG0

| 7   | 6 | 5 | 4 | 3 | 2     | 1    | 0     |  |  |

|-----|---|---|---|---|-------|------|-------|--|--|

| CBS | - | - | - | - | MOVCL | LOCK | 8 NO  |  |  |

| r/w | - | - | - | - | r/w   | r/w  | SPACE |  |  |

unprogrammed value: 1111 1111b

| Bit | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CBS   | <ul> <li>CONFIG boot select.</li> <li>This bit defines from which block MCU boots after all resets except software reset.</li> <li>1 = MCU will boot from APROM after all resets except software reset.</li> <li>0 = MCU will boot from LDROM after all resets except software reset.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6:3 | -     | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2   | MOVCL | <ul> <li>MOVC lock enable.</li> <li>This bit determines MOVC instruction is inhibited or not when reading internal Program Memory by executing on the external Program Memory. This mechanism is for data security.</li> <li>1 = MOVC has no restriction.</li> <li>0 = MOVC is restricted. The external Program Memory code is inhibited to read internal APROM or LDROM contents through MOVC instruction.</li> </ul>                                                                                                                                                                                                                                                                                                                       |

|     | LOCK  | <ul> <li>Chip lock enable.</li> <li>1 = Chip is unlocked. All of APROM and LDROM are not locked. Their contents can be read out through a parallel Programmer/Writer.</li> <li>0 = Chip is locked. APROM and LDROM are locked. Their contents read through parallel Programmer/Writer will become FFH.</li> <li>Note that CONFIG bytes are always unlocked and can be read. Hence, once the chip is locked, the CONFIG bytes cannot be erased or programmed individually. The only way to disable chip lock is to use the whole chip erase mode. However, all data within APROM, LDROM, and other CONFIG bits will be erased when this procedure is executed.</li> <li>If the chip is locked, it does not alter the ISP function.</li> </ul> |

| 0   | - 21  | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

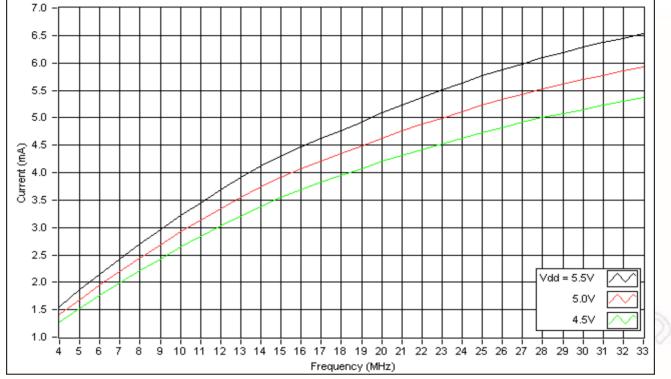

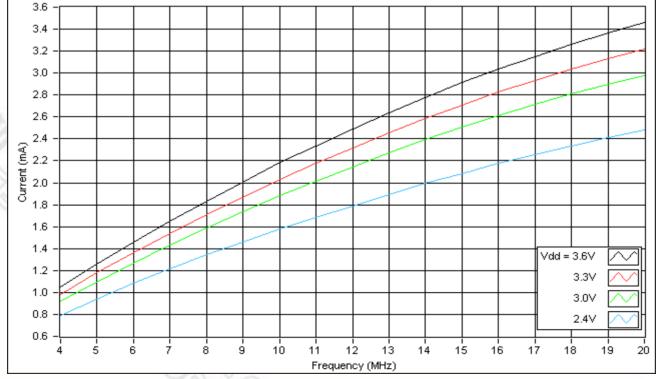

Figure 26–7. Idle Mode Current Under 6T Mode, External Clock (1)

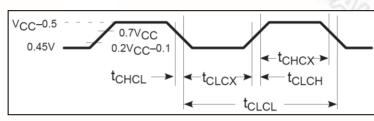

# **26.3 AC Electrical Characteristics**

### Table 26–2. AC Characteristics

| Sympol               | P                                  | 12T                     | mode                    | 6T n                      | node                      | 11     |

|----------------------|------------------------------------|-------------------------|-------------------------|---------------------------|---------------------------|--------|

| Symbol               | Parameter                          | Min.                    | Max.                    | Min.                      | Max.                      | Uni    |

| External             | Clock                              |                         | N/A                     | Xx                        |                           |        |

| A / 1                | External clock input frequency     | 0                       | 40                      | 0                         | 33                        | N AL I |

| 1/ t <sub>CLCL</sub> | Crystal/resonator frequency        | 4                       | 40                      | 4                         | 33                        | MH     |

| t <sub>CHCX</sub>    | High time                          | 12                      |                         | 15                        | 2.                        | ns     |

| t <sub>CLCX</sub>    | Low time                           | 12                      |                         | 15                        | Sh-                       | ns     |

| t <sub>CLCH</sub>    | Rise time                          |                         | 8                       | 63                        | 5                         | ns     |

| $\mathbf{t}_{CHCL}$  | Fall time                          |                         | 8                       |                           | 5                         | ns     |

| Program              | Memory                             | _                       |                         |                           | YON Y                     | á      |

| t <sub>LHLL</sub>    | ALE pulse width                    | 2 t <sub>CLCL</sub> -15 |                         | t <sub>CLCL</sub> -15     | (2)                       | ns     |

| t <sub>AVLL</sub>    | Address valid to ALE low           | t <sub>CLCL</sub> -15   |                         | 0.5 t <sub>CLCL</sub> -15 | -12                       | ns     |

| t <sub>LLAX</sub>    | Address hold after ALE low         | t <sub>CLCL</sub> -15   |                         | 0.5 t <sub>CLCL</sub> -15 |                           | ns     |

| t <sub>LLIV</sub>    | ALE low to valid instruction in    |                         | 4 t <sub>CLCL</sub> -45 |                           | 2 t <sub>CLCL</sub> -45   | ns     |

| t <sub>LLPL</sub>    | ALE low to PSEN low                | t <sub>CLCL</sub> -15   |                         | 0.5 t <sub>CLCL</sub> -15 |                           | ns     |

| t <sub>PLPH</sub>    | PSEN pulse width                   | 3 t <sub>CLCL</sub> -15 |                         | 1.5 t <sub>CLCL</sub> -15 |                           | ns     |

| t <sub>PLIV</sub>    | PSEN low to valid instruction in   |                         | 3 t <sub>CLCL</sub> -50 |                           | 1.5 t <sub>CLCL</sub> -50 | ns     |

| t <sub>PXIX</sub>    | Input instruction hold after PSEN  | 0                       |                         | 0                         |                           | ns     |

| t <sub>PXIZ</sub>    | Input instruction float after PSEN |                         | t <sub>CLCL</sub> -15   |                           | 0.5 t <sub>CLCL</sub> -15 | n      |

| t <sub>AVIV</sub>    | Address to valid instruction in    |                         | 5 t <sub>CLCL</sub> -60 |                           | 2.5 t <sub>CLCL</sub> -60 | n      |

| t <sub>PLAZ</sub>    | PSEN low to address float          |                         | 10                      |                           | 10                        | ns     |

| Data Mei             | mory                               |                         |                         |                           |                           |        |

| t <sub>RLRH</sub>    | RD pulse width                     | 6 t <sub>CLCL</sub> -30 |                         | 3 t <sub>CLCL</sub> -30   |                           | ns     |

| t <sub>WLWH</sub>    | WR pulse width                     | 6 t <sub>CLCL</sub> -30 |                         | 3 t <sub>CLCL</sub> -30   |                           | ns     |

| t <sub>RLDV</sub>    | RD low to valid data in            |                         | 5 t <sub>CLCL</sub> -50 |                           | 2.5 t <sub>CLCL</sub> -50 | n      |

| t <sub>RHDX</sub>    | Data hold after $\overline{RD}$    | 0                       |                         | 0                         |                           | ns     |

| t <sub>RHDZ</sub>    | Data float after RD                |                         | 2 t <sub>CLCL</sub> -12 |                           | t <sub>CLCL</sub> -12     | ns     |

| t <sub>LLDV</sub>    | ALE low to valid data in           |                         | 8 t <sub>CLCL</sub> -50 |                           | 4 t <sub>CLCL</sub> -50   | ns     |

| t <sub>AVDV</sub>    | Address to valid data in           |                         | 9 t <sub>CLCL</sub> -75 |                           | 4.5 t <sub>CLCL</sub> -75 | ns     |

| t <sub>LLWL</sub>    | ALE low to RD or WR low            | 3 t <sub>CLCL</sub> -15 | 3 t <sub>CLCL</sub> +15 | 1.5 t <sub>CLCL</sub> -15 | 1.5 t <sub>CLCL</sub> +15 | ns     |

| Symbol            | Devenueter                                                        | 12T                     | mode                  | 6T n                      | Unit                      |      |

|-------------------|-------------------------------------------------------------------|-------------------------|-----------------------|---------------------------|---------------------------|------|

|                   | Parameter                                                         | Min.                    | Max.                  | Min.                      | Max.                      | Unit |

| t <sub>AVWL</sub> | Address valid to $\overline{WR}$ low or $\overline{RD}$ low       | 4 t <sub>CLCL</sub> -30 | 1 A                   | 2 t <sub>CLCL</sub> -30   |                           | ns   |

| t <sub>QVWX</sub> | Data valid to $\overline{WR}$ transition                          | t <sub>CLCL</sub> -20   |                       | 0.5 t <sub>CLCL</sub> -20 |                           | ns   |

| t <sub>WHQX</sub> | Data hold after $\overline{WR}$                                   | t <sub>CLCL</sub> -15   | Stor 3                | 0.5 t <sub>CLCL</sub> -15 |                           | ns   |

| t <sub>RLAZ</sub> | RD low to address float                                           |                         | 0                     | N. Star                   | 0                         | ns   |

| t <sub>WHLH</sub> | $\overline{\text{RD}}$ or $\overline{\text{WR}}$ high to ALE high | t <sub>CLCL</sub> -15   | t <sub>CLCL</sub> +15 | 0.5 t <sub>CLCL</sub> -15 | 0.5 t <sub>CLCL</sub> +15 | ns   |

Figure 26–9. External Clock Input Timing

Figure 26–10. External Program Memory Read Cycle

### Table 26–3. Characteristics of On-chip RC Oscillators

| Symbol | Parameter                                                   | Condition           | Frequency<br>Deviation | Min.    | Тур.    | Max.    | Unit |

|--------|-------------------------------------------------------------|---------------------|------------------------|---------|---------|---------|------|

| FIHRC  | System 22.1184MHz RC oscillator frequency <sup>[1][2]</sup> | <b>25</b> ℃         | 1%                     | 21.8972 | 22.1184 | 22.3396 | MHz  |

|        |                                                             | <b>-40°C ~85°</b> ℃ | 3%                     | 21.4548 | 22.1184 | 22.7820 | MHz  |

| FILRC  | WDT and PDT 10kHz RC oscillator frequency                   |                     | 30%                    | 7       | 10      | 13      | kHz  |

[1] Internal 11.0592MHz is not listed for the same frequency deviation due to directly divided by 2 from 22.1184MHz source.

[2] A 0.1µF capacitor is recommended to be added on XTAL1 pin to gain the more precise frequency of the internal RC oscillator frequency if it is selected as the system clock source.

#### Table 26-4. Characteristics of Brown-out Detection

| Symbol             | Parameter                      | Condition          | Min. | Тур. | Max. | Unit |

|--------------------|--------------------------------|--------------------|------|------|------|------|

| T <sub>BOD</sub>   | Brown-out detect pulse width   | $V_{DD} < V_{BOD}$ | 600  | - 70 | 200  | μs   |

| T <sub>BODRD</sub> | Brown-out release delay period | $V_{DD} > V_{BOD}$ | 5.6  | 8    | 10.4 | ms   |

More product details and update information, please visit our website: **WWW.NUVOTON.COM**

### Headquarter-Taiwan

Nuvoton Technology Corp. No. 4, Creation Rd. III, Hsinchu Science Park, 300 Taiwan TEL: 886-3-5770066

## **Worldwide Sales Offices**

Taipei Sales Office 8F, No. 480, Rueiguang Rd., Neihu Chiu, Taipei, 114 Taiwan TEL: 886-2-26588066

### Nuvoton Electronics Tech. (Shenzhen) Limited

Unit 1501, New World Center, 6009 Yitian Road, Futian, Shenzhen, P.R.China 518026 TEL: 86-755-83515350

### Nuvoton Technology Corp. America

2727 N. First Street, San Jose, CA 95134, U.S.A. TEL: 1-408-544-1718

### Nuvoton Electronics Tech. (H.K.) Limited

Unit 9-11, 22F, Millennium City 2, 378 Kwun Tong Road, Kowloon, Hong Kong TEL: 852-27513100

## **Important Notice**

Nuvoton Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, "Insecure Usage".

Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, the control or operation of dynamic, brake or safety systems designed for vehicular use, traffic signal instruments, all types of safety devices, and other applications intended to support or sustain life.

All Insecure Usage shall be made at customer's risk, and in the event that third parties lay claims to Nuvoton as a result of customer's Insecure Usage, customer shall indemnify the damages and liabilities thus incurred by Nuvoton.

Please note that all data and specifications are subject to change without notice. All the trademarks of products and companies mentioned in this datasheet belong to their respective owners.