## NXP USA Inc. - P89LPC972FN,129 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 8051                                                                    |

| Core Size                  | 8-Bit                                                                   |

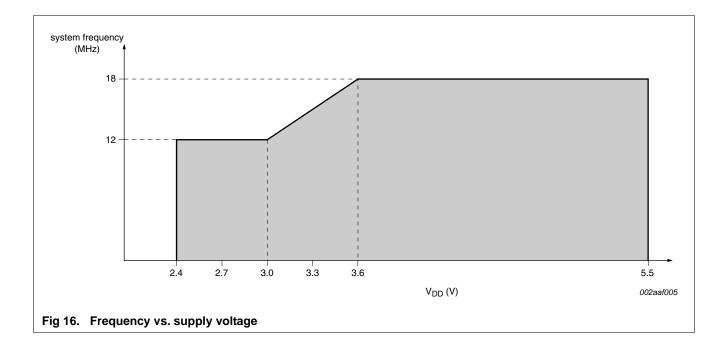

| Speed                      | 18MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 18                                                                      |

| Program Memory Size        | 8KB (8K x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | ·                                                                       |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                             |

| Data Converters            |                                                                         |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 20-DIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p89lpc972fn-129 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 6.2 Pin description

| Symbol              | Pin               | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|-------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | DIP20,<br>TSSOP20 |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P0.0 to P0.7        |                   | I/O  | <b>Port 0:</b> Port 0 is an 8-bit I/O port with a user-configurable output type. During reset Port 0 latches are configured in the input-only mode with the internal pull-up disabled. The operation of Port 0 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to <u>Section</u> 7.16.1 "Port configurations" and <u>Table 11 "Static characteristics"</u> for details. |

|                     |                   |      | The Keypad Interrupt feature operates with Port 0 pins.                                                                                                                                                                                                                                                                                                                                                                                           |

|                     |                   |      | All pins have Schmitt trigger inputs.                                                                                                                                                                                                                                                                                                                                                                                                             |

|                     |                   |      | Port 0 also provides various special functions as described below:                                                                                                                                                                                                                                                                                                                                                                                |

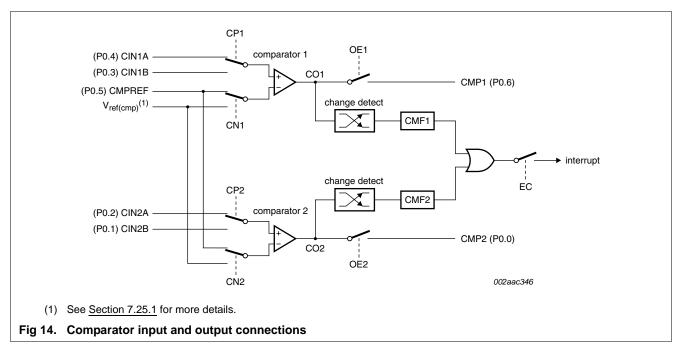

| P0.0/CMP2/KBI0/     | 1                 | I/O  | <b>P0.0</b> — Port 0 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SPICLK              |                   | 0    | CMP2 — Comparator 2 output                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                     |                   | I    | KBI0 — Keyboard input 0.                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                     |                   | I/O  | <b>SPICLK</b> — SPI clock. When configured as master, this pin is output; when configured as slave, this pin is input (pin remap).                                                                                                                                                                                                                                                                                                                |

| P0.1/CIN2B/<br>KBI1 | 20                | I/O  | <b>P0.1</b> — Port 0 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                     |                   | I    | CIN2B — Comparator 2 positive input B.                                                                                                                                                                                                                                                                                                                                                                                                            |

|                     |                   | I    | KBI1 — Keyboard input 1.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P0.2/CIN2A/         | 19                | I/O  | <b>P0.2</b> — Port 0 bit 2.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| KBI2                |                   | I    | <b>CIN2A</b> — Comparator 2 positive input A.                                                                                                                                                                                                                                                                                                                                                                                                     |

|                     |                   | I    | KBI2 — Keyboard input 2.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P0.3/CIN1B/         | 18                | I/O  | P0.3 — Port 0 bit 3. High current source.                                                                                                                                                                                                                                                                                                                                                                                                         |

| KBI3/T2             |                   | I    | CIN1B — Comparator 1 positive input B.                                                                                                                                                                                                                                                                                                                                                                                                            |

|                     |                   | I    | KBI3 — Keyboard input 3.                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                     |                   | I/O  | T2 — Timer/counter 2 external count input or overflow output.                                                                                                                                                                                                                                                                                                                                                                                     |

| P0.4/CIN1A/         | 17                | I/O  | P0.4 — Port 0 bit 4. High current source.                                                                                                                                                                                                                                                                                                                                                                                                         |

| KBI4                |                   | I    | CIN1A — Comparator 1 positive input A.                                                                                                                                                                                                                                                                                                                                                                                                            |

|                     |                   | I    | KBI4 — Keyboard input 4.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P0.5/CMPREF/        | 16                | I/O  | P0.5 — Port 0 bit 5. High current source.                                                                                                                                                                                                                                                                                                                                                                                                         |

| KBI5/T3             |                   | I    | <b>CMPREF</b> — Comparator reference (negative) input.                                                                                                                                                                                                                                                                                                                                                                                            |

|                     |                   | I    | KBI5 — Keyboard input 5.                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                     |                   | I/O  | T3 — Timer/counter 3 external count input or overflow output.                                                                                                                                                                                                                                                                                                                                                                                     |

#### Table 4.Special function registers ...continued\* indicates SFRs that are bit addressable. P89LPC9

| Name       | Description                                     | SFR         | Bit function | ons and ad | dresses |         |         |         |         |       | Reset         | value         |

|------------|-------------------------------------------------|-------------|--------------|------------|---------|---------|---------|---------|---------|-------|---------------|---------------|

|            |                                                 | addr.       | MSB          |            |         |         |         |         |         | LSB   | Hex           | Binary        |

| PCON       | Power control register                          | 87H         | SMOD1        | SMOD0      | -       | BOI     | GF1     | GF0     | PMOD1   | PMOD0 | 00            | 0000 000<br>0 |

| PCONA      | Power control<br>register A                     | B5H         | RTCPD        | -          | VCPD    | -       | I2PD    | SPPD    | SPD     | -     | 00 <u>[2]</u> | 0000 000<br>0 |

| PINCON     | pin remap<br>control register                   | CFH         | -            | -          | -       | -       | -       | -       | SPI     | -     | 00 <u>[2]</u> | 0000 000<br>0 |

| PMUCO<br>N | Power<br>Management<br>Unit control<br>register | FAH         | LPMOD        | -          | -       | -       | -       | -       | -       | HCOK  |               | 0xxx xxx      |

|            |                                                 | Bit address | D7           | D6         | D5      | D4      | D3      | D2      | D1      | D0    |               |               |

| PSW*       | Program status<br>word                          | D0H         | CY           | AC         | F0      | RS1     | RS0     | OV      | F1      | Р     | 00            | 0000 000<br>0 |

| PT0AD      | Port 0 digital input disable                    | F6H         | -            | -          | PT0AD.5 | PT0AD.4 | PT0AD.3 | PT0AD.2 | PT0AD.1 | -     | 00            | xx00 000      |

| PWMD2<br>H | PWM Free<br>Cycle register 2<br>high byte       | AEH         |              |            |         |         |         |         |         |       | 00            | 0000 000      |

| PWMD2      | L PWM Free<br>Cycle register 2<br>low byte      | AFH         |              |            |         |         |         |         |         |       | 00            | 0000 000      |

| PWMD3<br>H | PWM Free<br>Cycle register 3<br>high byte       | E9H         |              |            |         |         |         |         |         |       | 00            | 0000 000      |

| PWMD3      | L PWM Free<br>Cycle register 3<br>low byte      | EAH         |              |            |         |         |         |         |         |       | 00            | 0000 000      |

| PWMD4<br>H | PWM Free<br>Cycle register 4<br>high byte       | AAH         |              |            |         |         |         |         |         |       | 00            | 0000 000      |

| PWMD4      | L PWM Free<br>Cycle register 4<br>low byte      | ABH         |              |            |         |         |         |         |         |       | 00            | 0000 000      |

| RCAP2H     | Capture register<br>2 high byte                 | r FCH       |              |            |         |         |         |         |         |       | 00            | 0000 000      |

**NXP Semiconductors**

#### 8-bit microcontroller with accelerated two-clock 80C51 core

# 7.10 CCLK wake-up delay

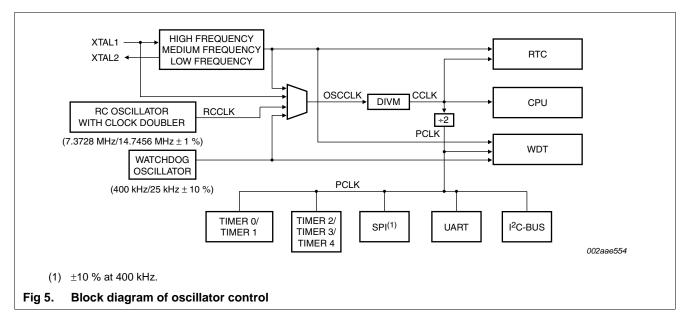

The P89LPC970/971/972 has an internal wake-up timer that delays the clock until it stabilizes depending on the clock source used. If the clock source is any of the three crystal selections (low, medium and high frequencies) the delay is 1024 OSCCLK cycles plus 60  $\mu$ s to 100  $\mu$ s. If the clock source is the internal RC oscillator, the delay is 200  $\mu$ s to 300  $\mu$ s. If the clock source is watchdog oscillator or external clock, the delay is 32 OSCCLK cycles.

# 7.11 CCLK modification: DIVM register

The OSCCLK frequency can be divided down up to 510 times by configuring a dividing register, DIVM, to generate CCLK. This feature makes it possible to temporarily run the CPU at a lower rate, reducing power consumption. By dividing the clock, the CPU can retain the ability to respond to events that would not exit Idle mode by executing its normal program at a lower rate. This can also allow bypassing the oscillator start-up time in cases where Power-down mode would otherwise be used. The value of DIVM may be changed by the program at any time without interrupting code execution.

## 7.12 Low power select

The P89LPC970/971/972 is designed to run at 18 MHz (CCLK) maximum. However, if CCLK is 8 MHz or slower, the CLKLP SFR bit (AUXR1.7) can be set to logic 1 to lower the power consumption further. On any reset, CLKLP is logic 0 allowing highest performance access. This bit can then be set in software if CCLK is running at 8 MHz or slower.

not by another interrupt of the same or lower priority. The highest priority interrupt service cannot be interrupted by any other interrupt source. If two requests of different priority levels are pending at the start of an instruction, the request of higher priority level is serviced.

If requests of the same priority level are pending at the start of an instruction, an internal polling sequence determines which request is serviced. This is called the arbitration ranking. Note that the arbitration ranking is only used to resolve pending requests of the same priority level.

## 7.15.1 External interrupt inputs

The P89LPC970/971/972 has two external interrupt inputs as well as the Keypad Interrupt function. The two interrupt inputs are identical to those present on the standard 80C51 microcontrollers.

These external interrupts can be programmed to be level-triggered or edge-triggered by setting or clearing bit IT1 or IT0 in Register TCON.

In edge-triggered mode, if successive samples of the INTn pin show a HIGH in one cycle and a LOW in the next cycle, the interrupt request flag IEn in TCON is set, causing an interrupt request.

If an external interrupt is enabled when the P89LPC970/971/972 is put into Power-down or Idle mode, the interrupt will cause the processor to wake-up and resume operation. Refer to <u>Section 7.17.3 "Power reduction modes"</u> for details.

# 7.18 Reset

The P1.5/RST pin can function as either a LOW-active reset input or as a digital input, P1.5. The Reset Pin Enable (RPE) bit in UCFG1, when set to logic 1, enables the external reset input function on P1.5. When cleared, P1.5 may be used as an input pin.

**Remark:** During a power-up sequence, the RPE selection is overridden and this pin always functions as a reset input. **An external circuit connected to this pin should not hold this pin LOW during a power-on sequence as this will keep the device in reset.** After power-up this pin will function as defined by the RPE bit. Only a power-up reset will temporarily override the selection defined by RPE bit. Other sources of reset will not override the RPE bit.

Reset can be triggered from the following sources:

- External reset pin (during power-up or if user configured via UCFG1)

- Power-on detect

- Brownout detect

- Watchdog timer

- Software reset

- UART break character detect reset

For every reset source, there is a flag in the Reset Register, RSTSRC. The user can read this register to determine the most recent reset source. These flag bits can be cleared in software by writing a logic 0 to the corresponding bit. More than one flag bit may be set:

- During a power-on reset, both POF and BOF are set but the other flag bits are cleared.

- A Watchdog reset is similar to a power-on reset, both POF and BOF are set but the other flag bits are cleared.

- For any other reset, previously set flag bits that have not been cleared will remain set.

#### 7.18.1 Reset vector

Following reset, the P89LPC970/971/972 will fetch instructions from either address 0000H or the Boot address. The Boot address is formed by using the boot vector as the high byte of the address and the low byte of the address = 00H.

The boot address will be used if a UART break reset occurs, or the non-volatile boot status bit (BOOTSTAT.0) = 1, or the device is forced into ISP mode during power-on (see *P89LPC970/971/972 User manual*). Otherwise, instructions will be fetched from address 0000H.

# 7.19 Timers/counters 0 and 1

The P89LPC970/971/972 has two general purpose counter/timers which are upward compatible with the standard 80C51 Timer 0 and Timer 1. Both can be configured to operate either as timers or event counters. An option to automatically toggle the T0 or T1 pins upon timer overflow has been added.

In the 'Timer' function, the register is incremented every machine cycle.

In the 'Counter' function, the register is incremented in response to a 1-to-0 transition at its corresponding count input pin, T0 or T1. In this function, the count input is sampled once during every machine cycle.

Timer 0 and Timer 1 have five operating modes (Modes 0, 1, 2, 3 and 6). Modes 0, 1, 2 and 6 are the same for both Timers/Counters. Mode 3 is different.

#### 7.19.1 Mode 0

Putting either Timer into Mode 0 makes it look like an 8048 Timer, which is an 8-bit Counter with a divide-by-32 prescaler. In this mode, the Timer register is configured as a 13-bit register. Mode 0 operation is the same for Timer 0 and Timer 1.

#### 7.19.2 Mode 1

Mode 1 is the same as Mode 0, except that all 16 bits of the timer register are used.

#### 7.19.3 Mode 2

Mode 2 configures the Timer register as an 8-bit Counter with automatic reload. Mode 2 operation is the same for Timer 0 and Timer 1.

#### 7.19.3.1 Mode 3

When Timer 1 is in Mode 3 it is stopped. Timer 0 in Mode 3 forms two separate 8-bit counters and is provided for applications that require an extra 8-bit timer. When Timer 1 is in Mode 3 it can still be used by the serial port as a baud rate generator.

#### 7.19.3.2 Mode 6

In this mode, the corresponding timer can be changed to a PWM with a full period of 256 timer clocks.

## 7.19.4 Timer overflow toggle output

Timers 0 and 1 can be configured to automatically toggle a port output whenever a timer overflow occurs. The same device pins that are used for the T0 and T1 count inputs are also used for the timer toggle outputs. The port outputs will be a logic 1 prior to the first timer overflow when this mode is turned on.

## 7.20 Timers/counters 2, 3 and 4

The P89LPC970/971/972 has three external 16-bit timer/counters. All can be configured to operate either as timers or event counters. An option to automatically toggle pin Tx (x = 2, 3 or 4) upon timer overflow has been added.

In the 'Timer' function, the register is incremented every PCLK.

In the 'Counter' function, the register is incremented in response to a 1-to-0 transition at its corresponding count input pin (T2/T3 /T4). In this function, the count input is sampled once during every machine cycle.

Only external Timer 2/3/4 has the external input pin TxEX (x = 2, 3 or 4). A 1-to-0 transition on this pin can trigger a reload or capture event.

Timer 2, Timer 3 and Timer 4 have three operating modes (Modes 0, 1 and 2).

#### 7.20.1 Mode 0: 16-bit timer/counter with auto-reload

Mode 0 configures the timer register as an 16-bit Timer/counter with automatic reload. An overflow upon the timer or a 1-to-0 transition at TxEX pin can cause the reload event.

#### 7.20.2 Mode 1: 16-bit timer/counter with input capture

Mode 1 configures the timer register as an 16-bit Timer/counter with input capture. A 1-to-0 transition at TxEX pin can cause the capture event.

#### 7.20.3 Mode 2: 16-bit PWM mode

In this mode, the corresponding timer can be changed to a 16-bit PWM generator with adjustable duty cycle. In this mode, the corresponding timer can be changed to a 16-bit PWM generator with adjustable duty cycle and adjustable full period (from 0, theoretically, to 131072).

## 7.20.4 Timer overflow toggle output

Timers 2, 3 and 4 can be configured to automatically toggle a port output whenever a timer overflow occurs. The same device pins that are used for the T2, T3 and T4 count inputs are also used for the timer toggle outputs. The port outputs will be a logic 1 prior to the first timer overflow when this mode is turned on.

# 7.21 RTC/system timer

The P89LPC970/971/972 has a simple RTC that allows a user to continue running an accurate timer while the rest of the device is powered down. The RTC can be a wake-up or an interrupt source. The RTC is a 23-bit down counter comprised of a 7-bit prescaler and a 16-bit loadable down counter. When it reaches all logic 0s, the counter will be reloaded again and the RTCF flag will be set. The clock source for this counter can be either the CPU clock (CCLK) or the XTAL oscillator. Only power-on reset and watchdog reset will reset the RTC and its associated SFRs to the default state.

The 16-bit loadable counter portion of the RTC is readable by reading the RTCDATL and RTCDATH registers.

## 7.22 UART

The P89LPC970/971/972 has an enhanced UART that is compatible with the conventional 80C51 UART except that Timer 2 overflow cannot be used as a baud rate source. The P89LPC970/971/972 does include an independent baud rate generator. The baud rate can be selected from the oscillator (divided by a constant), Timer 1 overflow, or the independent baud rate generator. In addition to the baud rate generation, enhancements over the standard 80C51 UART include Framing Error detection, automatic address recognition, selectable double buffering and several interrupt options. The UART can be operated in four modes: shift register, 8-bit UART, 9-bit UART, and CPU clock/32 or CPU clock/16.

## 7.22.1 Mode 0

Serial data enters and exits through RXD. TXD outputs the shift clock. 8 bits are transmitted or received, LSB first. The baud rate is fixed at  $\frac{1}{16}$  of the CPU clock frequency.

#### 8-bit microcontroller with accelerated two-clock 80C51 core

## **NXP Semiconductors**

# P89LPC970/971/972

#### 8-bit microcontroller with accelerated two-clock 80C51 core

#### 7.25.1 Selectable internal reference voltage

An internal reference voltage generator may be used to supply a default reference when a single comparator input pin is used. The user may program one of eight different values for the internal reference voltage using the Comparator Reference register (CMPREF). Each of the two comparators may use a different reference voltage.

## 7.25.2 Comparator interrupt

Each comparator has an interrupt flag contained in its configuration register. This flag is set whenever the comparator output changes state. The flag may be polled by software or may be used to generate an interrupt. The two comparators use one common interrupt vector. If both comparators enable interrupts, after entering the interrupt service routine, the user needs to read the flags to determine which comparator caused the interrupt.

## 7.25.3 Comparators and power reduction modes

Either or both comparators may remain enabled when Power-down or Idle mode is activated, but both comparators are disabled automatically in Total Power-down mode.

If a comparator interrupt is enabled (except in Total Power-down mode), a change of the comparator output state will generate an interrupt and wake-up the processor. If the comparator output to a pin is enabled, the pin should be configured in the push-pull mode in order to obtain fast switching times while in Power-down mode. The reason is that with the **oscillator** stopped, the temporary strong pull-up that normally occurs during switching on a quasi-bidirectional port pin does not take place.

Comparators consume power in Power-down and Idle modes, as well as in the normal operating mode. This fact should be taken into account when system power consumption is an issue. To minimize power consumption, the user can disable the comparators via PCONA.5, or put the device in Total Power-down mode.

#### 7.29.6 ICP

ICP is performed without removing the microcontroller from the system. The ICP facility consists of internal hardware resources to facilitate remote programming of the P89LPC970/971/972 through a two-wire serial interface. The NXP ICP facility has made in-circuit programming in an embedded application - using commercially available programmers - possible with a minimum of additional expense in components and circuit board area. The ICP function uses five pins. Only a small connector needs to be available to interface your application to a commercial programmer in order to use this feature. Additional details may be found in the *P89LPC970/971/972 User manual*.

## 7.29.7 IAP

IAP is performed in the application under the control of the microcontroller's firmware. The IAP facility consists of internal hardware resources to facilitate programming and erasing. The NXP IAP has made in-application programming in an embedded application possible without additional components. Two methods are available to accomplish IAP. A set of predefined IAP functions are provided in a Boot ROM and can be called through a common interface, PGM\_MTP. Several IAP calls are available for use by an application program to permit selective erasing and programming of flash sectors, pages, security bits, configuration bytes, and device ID. These functions are selected by setting up the microcontroller's registers before making a call to PGM\_MTP at FF03H. The Boot ROM occupies the program memory space at the top of the address space from FF00H to FEFFH, thereby not conflicting with the user program memory space.

In addition, IAP operations can be accomplished through the use of four SFRs consisting of a control/status register, a data register, and two address registers. Additional details may be found in the *P89LPC970/971/972 User manual*.

## 7.29.8 ISP

ISP is performed without removing the microcontroller from the system. The ISP facility consists of a series of internal hardware resources coupled with internal firmware to facilitate remote programming of the P89LPC970/971/972 through the serial port. This firmware is provided by NXP and embedded within each P89LPC970/971/972 device. The NXP ISP facility has made in-system programming in an embedded application possible with a minimum of additional expense in components and circuit board area. The ISP function uses five pins ( $V_{DD}$ ,  $V_{SS}$ , TXD, RXD, and RST). Only a small connector needs to be available to interface your application to an external circuit in order to use this feature.

## 7.29.9 Power-on reset code execution

The P89LPC970/971/972 contains two special flash elements: the Boot Vector and the Boot Status bit. Following reset, the P89LPC970/971/972 examines the contents of the Boot Status bit. If the Boot Status bit is set to zero, power-up execution starts at location 0000H, which is the normal start address of the user's application code. When the Boot Status bit is set to a value other than zero, the contents of the Boot Vector are used as the high byte of the execution address and the low byte is set to 00H.

<u>Table 9</u> shows the factory default Boot Vector setting for these devices. A factory-provided bootloader is pre-programmed into the address space indicated and uses the indicated bootloader entry point to perform ISP functions. This code can be erased by the user.

# **NXP Semiconductors**

# P89LPC970/971/972

## 8-bit microcontroller with accelerated two-clock 80C51 core

## 8-bit microcontroller with accelerated two-clock 80C51 core

#### Table 11. Static characteristics ...continued

$V_{DD}$  = 2.4 V to 5.5 V unless otherwise specified.

$T_{amb} = -40$  °C to +85 °C for industrial applications, unless otherwise specified.

| Symbol                  | Parameter                                    | Conditions                      | Min  | Typ[1] | Max  | Unit |

|-------------------------|----------------------------------------------|---------------------------------|------|--------|------|------|

| R <sub>RST_N(int)</sub> | internal pull-up<br>resistance on pin<br>RST | pin RST                         | 30   | -      | 120  | kΩ   |

| BOD inter               | rupt                                         |                                 |      |        |      |      |

| V <sub>trip</sub>       | trip voltage                                 | falling stage                   |      |        |      |      |

|                         |                                              | BOICFG2, BOICFG1, BOICFG0 = 010 | 2.45 | -      | 2.65 | V    |

|                         |                                              | BOICFG2, BOICFG1, BOICFG0 = 011 | 2.75 | -      | 2.95 | V    |

|                         |                                              | BOICFG2, BOICFG1, BOICFG0 = 100 | 2.90 | -      | 3.10 | V    |

|                         |                                              | BOICFG2, BOICFG1, BOICFG0 = 101 | 3.35 | -      | 3.55 | V    |

|                         |                                              | BOICFG2, BOICFG1, BOICFG0 = 110 | 4.10 | -      | 4.30 | V    |

|                         |                                              | BOICFG2, BOICFG1, BOICFG0 = 111 | 4.25 | -      | 4.45 | V    |

|                         |                                              | rising stage                    |      |        |      |      |

|                         |                                              | BOICFG2, BOICFG1, BOICFG0 = 010 | 2.60 | -      | 2.80 | V    |

|                         |                                              | BOICFG2, BOICFG1, BOICFG0 = 011 | 2.90 | -      | 3.10 | V    |

|                         |                                              | BOICFG2, BOICFG1, BOICFG0 = 100 | 3.05 | -      | 3.25 | V    |

|                         |                                              | BOICFG2, BOICFG1, BOICFG0 = 101 | 3.50 | -      | 3.70 | V    |

|                         |                                              | BOICFG2, BOICFG1, BOICFG0 = 110 | 4.15 | -      | 4.35 | V    |

|                         |                                              | BOICFG2, BOICFG1, BOICFG0 = 111 | 4.35 | -      | 4.55 | V    |

#### 8-bit microcontroller with accelerated two-clock 80C51 core

#### Table 11. Static characteristics ...continued

$V_{DD} = 2.4$  V to 5.5 V unless otherwise specified.

$T_{amb} = -40 \text{ }^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$  for industrial applications, unless otherwise specified.

| Symbol               | Parameter                              | Conditions             | Min  | Typ <u>[1]</u> | Max                                                                                                                               | Unit       |

|----------------------|----------------------------------------|------------------------|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------|------------|

| BOD res              | et                                     |                        |      |                |                                                                                                                                   |            |

| V <sub>trip</sub>    | trip voltage                           | falling stage          |      |                |                                                                                                                                   |            |

|                      |                                        | BOE2, BOE1, BOE0 = 010 | 2.15 | -              | Max<br>2.35<br>2.65<br>2.95<br>3.25<br>3.95<br>4.15<br>2.50<br>2.80<br>3.10<br>3.40<br>4.05<br>4.25<br>2.55<br>2.65<br>1.27<br>20 | V          |

|                      |                                        | BOE2, BOE1, BOE0 = 011 | 2.45 | -              |                                                                                                                                   | V          |

|                      |                                        | BOE2, BOE1, BOE0 = 100 | 2.75 | -              |                                                                                                                                   | V          |

|                      |                                        | BOE2, BOE1, BOE0 = 101 | 3.05 | -              | 3.25                                                                                                                              | V          |

|                      |                                        | BOE2, BOE1, BOE0 = 110 | 3.75 | -              | 3.95                                                                                                                              | V          |

|                      |                                        | BOE2, BOE1, BOE0 = 111 | 3.95 | -              | 4.15                                                                                                                              | V          |

|                      |                                        | rising stage           |      |                |                                                                                                                                   |            |

|                      |                                        | BOE2, BOE1, BOE0 = 010 | 2.30 | -              | 2.50                                                                                                                              | V          |

|                      |                                        | BOE2, BOE1, BOE0 = 011 | 2.60 | -              | 2.80                                                                                                                              | V          |

|                      |                                        | BOE2, BOE1, BOE0 = 100 | 2.90 | -              | 3.10                                                                                                                              | V          |

|                      |                                        | BOE2, BOE1, BOE0 = 101 | 3.20 | -              | 3.40                                                                                                                              | V          |

|                      |                                        | BOE2, BOE1, BOE0 = 110 | 3.85 | -              | 4.05                                                                                                                              | V          |

|                      |                                        | BOE2, BOE1, BOE0 = 111 | 4.05 | -              | 4.25                                                                                                                              | V          |

| BOD flas             | h                                      |                        |      |                |                                                                                                                                   |            |

| V <sub>trip</sub>    | trip voltage                           | falling stage          | 2.30 | -              | 2.55                                                                                                                              | V          |

|                      |                                        | rising stage           | 2.40 | -              | 2.65                                                                                                                              | V          |

| V <sub>ref(bg)</sub> | band gap<br>reference voltage          |                        | 1.19 | 1.23           | 1.27                                                                                                                              | V          |

| ГС <sub>bg</sub>     | band gap<br>temperature<br>coefficient |                        | -    | 10             | 20                                                                                                                                | ppm/<br>°C |

[1] Typical ratings are not guaranteed. The values listed are at room temperature, 3 V.

[2] The I<sub>DD(oper)</sub> and I<sub>DD(idle)</sub> specifications are measured using an external clock with the following functions disabled: comparators, real-time clock, and watchdog timer.

[3] The I<sub>DD(pd)</sub> and I<sub>DD(tpd)</sub> specification is measured using an external clock with the following functions disabled: comparators, real-time clock, brownout detect, and watchdog timer.

- [4] See Section 8 "Limiting values" for steady state (non-transient) limits on I<sub>OL</sub> or I<sub>OH</sub>. If I<sub>OL</sub>/I<sub>OH</sub> exceeds the test condition, V<sub>OL</sub>/V<sub>OH</sub> may exceed the related specification.

- [5] This specification can be applied to pins which have A/D input or analog comparator input functions when the pin is not being used for those analog functions. When the pin is being used as an analog input pin, the maximum voltage on the pin must be limited to 4.0 V with respect to V<sub>SS</sub>.

- [6] Pin capacitance is characterized but not tested.

- [7] Measured with port in quasi-bidirectional mode.

- [8] Measured with port in high-impedance mode.

- [9] Port pins source a transition current when used in quasi-bidirectional mode and externally driven from logic 1 to logic 0. This current is highest when V<sub>1</sub> is approximately 2 V.

#### 8-bit microcontroller with accelerated two-clock 80C51 core

# 10. Dynamic characteristics

#### Table 12. Dynamic characteristics (12 MHz)

$V_{DD} = 2.4$  V to 5.5 V unless otherwise specified.

$T_{amb} = -40$  °C to +85 °C for industrial applications, unless otherwise specified. [1][2]

| Symbol               | Parameter                                        | Conditions                                                                                                                | Varia                  | able clock               | f <sub>osc</sub> = ' | 12 MHz | Unit |

|----------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------|----------------------|--------|------|

|                      |                                                  |                                                                                                                           | Min                    | Max                      | Min                  | Max    |      |

| f <sub>osc(RC)</sub> | internal RC oscillator<br>frequency              | nominal f = 7.3728 MHz<br>trimmed to $\pm$ 1 % at<br>T <sub>amb</sub> = 25 °C; clock<br>doubler option = OFF<br>(default) | 7.189                  | 7.557                    | 7.189                | 7.557  | MHz  |

|                      |                                                  | nominal f = 14.7456 MHz;<br>clock doubler option = ON,<br>$V_{DD}$ = 2.7 V to 5.5 V                                       | 14.378                 | 15.114                   | 14.378               | Max    | MHz  |

| f <sub>osc(WD)</sub> | internal watchdog<br>oscillator frequency        |                                                                                                                           | 360                    | 440                      | 360                  | 440    | kHz  |

| f <sub>osc</sub>     | oscillator frequency                             |                                                                                                                           | 0                      | 12                       | -                    | -      | MHz  |

| T <sub>cy(clk)</sub> | clock cycle time                                 | see Figure 17                                                                                                             | 83                     | -                        | -                    | -      | ns   |

| f <sub>CLKLP</sub>   | low-power select clock<br>frequency              |                                                                                                                           | 0                      | 8                        | -                    | -      | MHz  |

| Glitch filte         | er                                               |                                                                                                                           |                        |                          |                      |        |      |

| t <sub>gr</sub>      | glitch rejection time                            | P1.5/RST pin                                                                                                              | -                      | 50                       | -                    | 50     | ns   |

|                      |                                                  | any pin except P1.5/RST                                                                                                   | -                      | 15                       | -                    | 15     | ns   |

| t <sub>sa</sub>      | signal acceptance time                           | P1.5/RST pin                                                                                                              | 125                    | -                        | 125                  | -      | ns   |

|                      |                                                  | any pin except P1.5/RST                                                                                                   | 50                     | -                        | 50                   | -      | ns   |

| External c           | lock                                             |                                                                                                                           |                        |                          |                      |        |      |

| t <sub>CHCX</sub>    | clock HIGH time                                  | see Figure 17                                                                                                             | 33                     | $T_{cy(clk)} - t_{CLCX}$ | 33                   | -      | ns   |

| t <sub>CLCX</sub>    | clock LOW time                                   | see Figure 17                                                                                                             | 33                     | $T_{cy(clk)} - t_{CHCX}$ | 33                   | -      | ns   |

| t <sub>CLCH</sub>    | clock rise time                                  | see Figure 17                                                                                                             | -                      | 8                        | -                    | 8      | ns   |

| t <sub>CHCL</sub>    | clock fall time                                  | see <u>Figure 17</u>                                                                                                      | -                      | 8                        | -                    | 8      | ns   |

| Shift regis          | ster (UART mode 0)                               |                                                                                                                           |                        |                          |                      |        |      |

| T <sub>XLXL</sub>    | serial port clock cycle<br>time                  | see <u>Figure 18</u>                                                                                                      | 16T <sub>cy(clk)</sub> | -                        | 1333                 | -      | ns   |

| t <sub>QVXH</sub>    | output data set-up to<br>clock rising edge time  | see Figure 18                                                                                                             | 13T <sub>cy(clk)</sub> | -                        | 1083                 | -      | ns   |

| t <sub>XHQX</sub>    | output data hold after<br>clock rising edge time | see Figure 18                                                                                                             | -                      | $T_{cy(clk)}$ + 20       | -                    | 103    | ns   |

| t <sub>XHDX</sub>    | input data hold after<br>clock rising edge time  | see Figure 18                                                                                                             | -                      | 0                        | -                    | 0      | ns   |

| t <sub>XHDV</sub>    | input data valid to clock rising edge time       | see Figure 18                                                                                                             | 150                    | -                        | 150                  | -      | ns   |

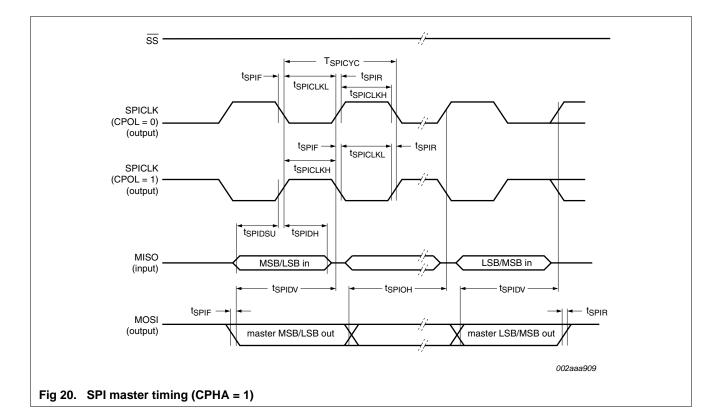

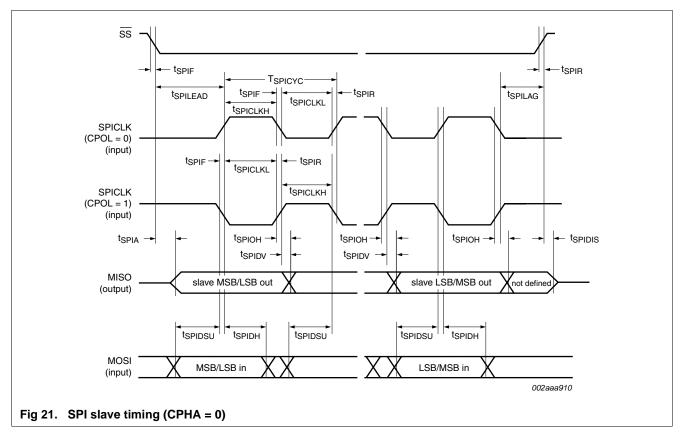

| SPI interfa          | ace                                              |                                                                                                                           |                        |                          |                      |        |      |

| f <sub>SPI</sub>     | SPI operating frequency                          |                                                                                                                           |                        |                          |                      |        |      |

|                      | slave                                            |                                                                                                                           | 0                      | CCLK/6                   | 0                    | 2.0    | MHz  |

|                      | master                                           |                                                                                                                           | -                      | CCLK                     | -                    | 3.0    | MHz  |

## 8-bit microcontroller with accelerated two-clock 80C51 core

#### Table 13. Dynamic characteristics (18 MHz)

$V_{DD} = 3.6 \text{ V to } 5.5 \text{ V unless otherwise specified.}$  $T_{amb} = -40 \text{ }^{\circ}\text{C} \text{ to } +85 \text{ }^{\circ}\text{C} \text{ for industrial applications, unless otherwise specified.}$

| Symbol               | Parameter                                        | Conditions                                                                                                                | Varia                          | f <sub>osc</sub> = 1     | Unit   |        |     |

|----------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------|--------|--------|-----|

|                      |                                                  |                                                                                                                           | Min                            | Max                      | Min    | Max    |     |

| osc(RC)              | internal RC oscillator<br>frequency              | nominal f = 7.3728 MHz<br>trimmed to $\pm$ 1 % at<br>T <sub>amb</sub> = 25 °C; clock<br>doubler option = OFF<br>(default) | 7.189                          | 7.557                    | 7.189  | 7.557  | MHz |

|                      |                                                  | nominal f = $14.7456$ MHz;<br>clock doubler option = ON                                                                   | 14.378                         | 15.114                   | 14.378 | 15.114 | MHz |

| osc(WD)              | internal watchdog<br>oscillator frequency        |                                                                                                                           | 360                            | 440                      | 360    | 440    | kHz |

| f <sub>osc</sub>     | oscillator frequency                             |                                                                                                                           | 0                              | 18                       | -      | -      | MHz |

| T <sub>cy(clk)</sub> | clock cycle time                                 | see Figure 17                                                                                                             | 55                             | -                        | -      | -      | ns  |

| fCLKLP               | low-power select clock<br>frequency              |                                                                                                                           | 0                              | 8                        | -      | -      | MHz |

| Glitch fil           | ter                                              |                                                                                                                           |                                |                          |        |        |     |

| t <sub>gr</sub>      | glitch rejection time                            | P1.5/RST pin                                                                                                              | -                              | 50                       | -      | 50     | ns  |

|                      |                                                  | any pin except P1.5/RST                                                                                                   | -                              | 15                       | -      | 15     | ns  |

| t <sub>sa</sub>      | signal acceptance time                           | P1.5/RST pin                                                                                                              | 125                            | -                        | 125    | -      | ns  |

|                      |                                                  | any pin except P1.5/RST                                                                                                   | 50                             | -                        | 50     | -      | ns  |

| External             | clock                                            |                                                                                                                           |                                |                          |        |        |     |

| снсх                 | clock HIGH time                                  | see Figure 17                                                                                                             | 22                             | $T_{cy(clk)} - t_{CLCX}$ | 22     | -      | ns  |

| <sup>t</sup> CLCX    | clock LOW time                                   | see Figure 17                                                                                                             | 22                             | $T_{cy(clk)} - t_{CHCX}$ | 22     | -      | ns  |

| <sup>t</sup> CLCH    | clock rise time                                  | see Figure 17                                                                                                             | -                              | 5                        | -      | 5      | ns  |

| t <sub>CHCL</sub>    | clock fall time                                  | see Figure 17                                                                                                             | -                              | 5                        | -      | 5      | ns  |

| Shift reg            | ister (UART mode 0)                              |                                                                                                                           |                                |                          |        |        |     |

| T <sub>XLXL</sub>    | serial port clock cycle<br>time                  | see <u>Figure 18</u>                                                                                                      | 16T <sub>cy(clk)</sub>         | -                        | 888    | -      | ns  |

| t <sub>QVXH</sub>    | output data set-up to<br>clock rising edge time  | see <u>Figure 18</u>                                                                                                      | 13T <sub>cy(clk)</sub>         | -                        | 722    | -      | ns  |

| t <sub>XHQX</sub>    | output data hold after<br>clock rising edge time | see Figure 18                                                                                                             | -                              | $T_{cy(clk)}$ + 20       | -      | 75     | ns  |

| XHDX                 | input data hold after<br>clock rising edge time  | see Figure 18                                                                                                             | -                              | 0                        | -      | 0      | ns  |

| XHDV                 | input data valid to clock rising edge time       | see Figure 18                                                                                                             | 150                            | -                        | 150    | -      | ns  |

| SPI inter            | face                                             |                                                                                                                           |                                |                          |        |        |     |

| SPI                  | SPI operating frequency                          |                                                                                                                           |                                |                          |        |        |     |

|                      | slave                                            |                                                                                                                           | 0                              | CCLK/6                   | 0      | 3.0    | MH  |

|                      | master                                           |                                                                                                                           | -                              | CCLK/4                   | -      | 4.5    | MH  |

| T <sub>SPICYC</sub>  | SPI cycle time                                   | see Figure 19, 20, 21, 22                                                                                                 |                                |                          |        |        |     |

|                      | slave                                            |                                                                                                                           | <sup>6</sup> ∕ <sub>CCLK</sub> | -                        | 333    | -      | ns  |

|                      | master                                           |                                                                                                                           | 4/ <sub>CCLK</sub>             | -                        | 222    | -      | ns  |

Product data sheet

## **NXP Semiconductors**

# P89LPC970/971/972

#### 8-bit microcontroller with accelerated two-clock 80C51 core

# 11. Other characteristics

# 11.1 Comparator electrical characteristics

#### Table 15. Comparator electrical characteristics

$V_{DD}$  = 2.4 V to 5.5 V, unless otherwise specified.

$T_{amb} = -40$  °C to +85 °C for industrial applications, unless otherwise specified.

| Symbol                | Parameter                        | Conditions           | Min          | Тур | Max          | Unit |

|-----------------------|----------------------------------|----------------------|--------------|-----|--------------|------|

| V <sub>IO</sub>       | input offset voltage             |                      | -            | -   | ±10          | mV   |

| V <sub>IC</sub>       | common-mode input voltage        |                      | 0            | -   | $V_{DD}-0.3$ | V    |

| CMRR                  | common-mode rejection ratio      |                      | <u>[1]</u> - | -   | -50          | dB   |

| t <sub>res(tot)</sub> | total response time              |                      | -            | 250 | 500          | ns   |

| t <sub>(CE-OV)</sub>  | chip enable to output valid time |                      | -            | -   | 10           | μS   |

| ILI                   | input leakage current            | $0 V < V_I < V_{DD}$ | -            | -   | ±1           | μA   |

[1] This parameter is characterized, but not tested in production.

8-bit microcontroller with accelerated two-clock 80C51 core

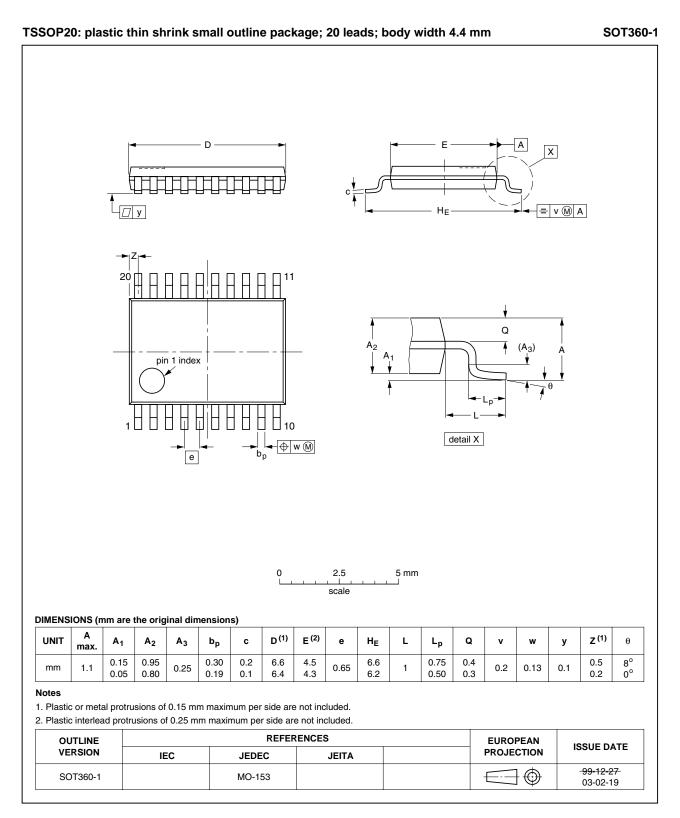

# 12. Package outline

Fig 24. TSSOP20 package outline (SOT360-1)

P89LPC97X Product data sheet

#### 8-bit microcontroller with accelerated two-clock 80C51 core

**Non-automotive qualified products** — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's

# 16. Contact information

own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

# 15.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

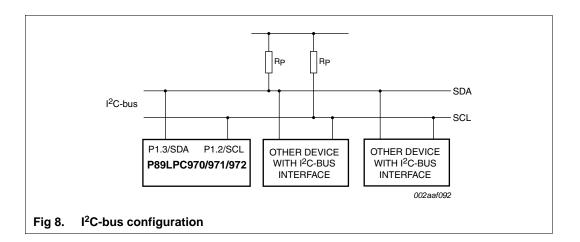

I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

#### For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Product data sheet

8-bit microcontroller with accelerated two-clock 80C51 core

# 17. Contents

| 1        | General description               | 1    | 7.1        |

|----------|-----------------------------------|------|------------|

| 2        | Features and benefits             | 1    | 7.′        |

| 2.1      | Principal features                | 1    | 7.1        |

| 2.2      | Additional features               | 2    | 7.         |

| 3        | Ordering information              | 3    | 7.′<br>7.′ |

| 3.1      | Ordering options                  | 3    | 7.<br>7.   |

| 4        | Block diagram                     | 4    | 7.<br>7.   |

| 5        | Functional diagram                | 5    | 7.         |

| 6        | Pinning information               |      | 7.1        |

| 6.1      | Pinning                           |      | 7.1        |

| 6.2      | Pin description                   |      | 7.′        |

| 7        | Functional description            | . 10 | 7.2        |

| 7.1      | Special function registers        | . 10 | 7.2        |

| 7.2      | Enhanced CPU.                     | . 19 |            |

| 7.3      | Clocks                            | . 19 | 7.2        |

| 7.3.1    | Clock definitions                 |      |            |

| 7.3.2    | CPU clock (OSCCLK)                |      | 7.2        |

| 7.4      | Crystal oscillator option.        | . 19 | 7.2        |

| 7.4.1    | Low speed oscillator option       |      | 7.2        |

| 7.4.2    | Medium speed oscillator option    | . 19 | 7.2        |

| 7.4.3    | High speed oscillator option      |      | 7.2        |

| 7.5      | Clock output                      |      | 7.2        |

| 7.6      | On-chip RC oscillator option      |      | 7.2        |

| 7.7      | Watchdog oscillator option        |      | 7.2        |

| 7.8      | External clock input option       |      | 7.2        |

| 7.9      | Clock source switching on the fly |      | 7.2        |

| 7.10     | CCLK wake-up delay                |      | 7.2        |

| 7.11     | CCLK modification: DIVM register  |      | 7.2        |

| 7.12     | Low power select                  |      | 7.2        |

| 7.13     | Memory organization               |      | _          |

| 7.14     | Data RAM arrangement              |      | 7.2        |

| 7.15     | Interrupts.                       |      | _          |

| 7.15.1   | External interrupt inputs         |      | 7.2        |

| 7.16     | I/O ports                         |      | 7.2        |

| 7.16.1   | Port configurations               |      | 7.2        |

| 7.16.1.1 |                                   |      | 7.2        |

| 7.16.1.2 |                                   |      | 7.2        |

| 7.16.1.3 |                                   |      | 7.2        |

| 7.16.1.4 |                                   |      | 7.2        |

| 7.16.2   | Port 0 analog functions           |      | 7.2        |

| 7.16.3   | Additional port features.         |      | 7.2        |

| 7.16.4   | Pin remap                         |      | 7.2        |

| 7.17     | Power management                  |      | 7.2        |

| 7.17.1   | Brownout detection                |      | 7.2        |

| 7.17.2   | Power-on detection.               |      | 7.2        |

| 7.17.3   | Power reduction modes             |      | 7.2        |

| 7.17.3.1 |                                   |      | 7.2        |

|          |                                   |      |            |

| 17.3.2 | Power-down mode                                     | . 28 |

|--------|-----------------------------------------------------|------|

| 17.3.3 | Total Power-down mode                               |      |

| 17.4   | Regulators                                          |      |

| 18     | Reset                                               |      |

| 18.1   | Reset vector.                                       |      |

| 19     | Timers/counters 0 and 1                             |      |

| 19.1   | Mode 0                                              |      |

| 19.2   | Mode 1                                              |      |

| 19.3   | Mode 2                                              |      |

| 19.3.1 | Mode 3                                              |      |

| 19.3.2 | Mode 6                                              |      |

| 19.4   | Timer overflow toggle output                        |      |

| 20     | Timers/counters 2, 3 and 4                          |      |

| 20.1   | Mode 0: 16-bit timer/counter with                   |      |

| 20.1   | auto-reload.                                        | . 31 |

| 20.2   | Mode 1: 16-bit timer/counter with input             |      |

| _0     | capture                                             | . 31 |

| 20.3   | Mode 2: 16-bit PWM mode                             |      |

| 20.4   | Timer overflow toggle output                        |      |

| 21     | RTC/system timer                                    |      |

| 22     | UART                                                |      |

| 22.1   | Mode 0                                              | -    |

| 22.2   | Mode 1                                              |      |

| 22.3   | Mode 2                                              |      |

| 22.4   | Mode 3                                              | -    |

| 22.5   | Baud rate generator and selection                   |      |

| 22.6   | Framing error                                       | -    |

| 22.7   | Break detect.                                       |      |

| 22.8   | Double buffering.                                   |      |

| 22.9   | Transmit interrupts with double buffering           |      |

|        | enabled (modes 1, 2 and 3)                          | . 33 |

| 22.10  | The 9 <sup>th</sup> bit (bit 8) in double buffering |      |

|        | (modes 1, 2 and 3)                                  | . 33 |

| 23     | $I^2$ C-bus serial interface.                       | . 33 |

| 24     | SPI (Pin remap)                                     |      |

| 24.1   | Typical SPI configurations                          |      |

| 25     | Analog comparators                                  |      |

| 25.1   | Selectable internal reference voltage               |      |

| 25.2   | Comparator interrupt                                |      |

| 25.3   | Comparators and power reduction modes.              | . 39 |

| 26     | KBI                                                 | . 40 |

| 27     | Watchdog timer                                      |      |

| 28     | Additional features                                 |      |

|        | Software reset                                      |      |

| 28.2   | Dual data pointers                                  |      |

| 29     | Flash program memory                                |      |

|        | General description                                 |      |

| 29.2   | Features.                                           |      |

|        |                                                     |      |

#### continued >>